Laboratorium Układów Cyfrowych

Ćwiczenie 3: Układy iteracyjne.

Jarosław Sadowski, Michał Wilkowski,

Telekomunikacja, semestr 5, grupa dziekańska 4

Data wykonania ćwiczenia: 1.12.1999r.

Do wykonania następujące zadania:

Sumator dwóch liczb 8-bitowych.

Y=3X+2Z

Wykrywanie sekwencji trzech zer przedzielonych maksymalnie jedną jedynką.

1. Sumator dwóch liczb 8-bitowych.

Przyjęto następujące oznaczenie sygnałów:

p - przeniesienie z poprzedniego bitu (wejście)

a, b - bity dodawanych liczb

y - bit liczby wyjściowej

p' - przeniesienie na następny bit (wyjście)

Tabela opisująca działanie układu wygląda następująco:

p |

a |

b |

y |

p' |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Bit wejścia przeniesienia dla najmłodszej komórki układu iteracyjnego musi być ustawiony na zero, wyjście przeniesienia z najstarszego bitu jest najstarszym bitem otrzymanej sumy, stąd równanie dekodera jest następujące: y=p.

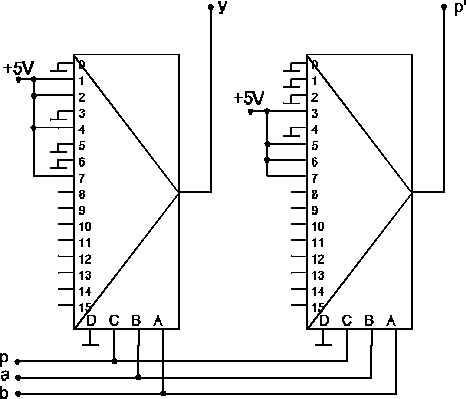

Schemat proponowanego rozwiązania pojedynczej komórki i dekodera jest następujący:

2. Y=3X+2Z

Realizacja układu iteracyjnego realizującego taką funkcję przy użyciu tylko trzech linii łączących poszczególne komórki układu wydaje się być niewykonalne. Połączenia między komórkami należy wykonywać co najmniej czterema liniami, gdyż:

potrzeba jednej linii na przepisywanie stanu poprzedniego bitu liczby X do zrealizowania mnożenia X przez 3

potrzeba jednej linii na przepisywanie stanu poprzedniego bitu liczby Z do zrealizowania mnożenia X przez 2

na skutek sumowania trzech bitów: dwa bity liczby X i jeden bit liczby Z generowany jest sygnał wyjściowy oraz jedno przeniesienie, które też musi być następnie dodane. W sumie dodawane są więc cztery bity, jeśli każdy z nich będzie miał wartość 1 to uzyskamy dwubitowe przeniesienie na starszą pozycję.

Nie znaleziono możliwości innego obejścia tego problemu niż założenie, że do układu wpisywana będzie już podwojona liczba Z (przesunięta o jeden bit), czyli w praktyce zrealizowano układ działający według równania Y=3X+Z.

Przyjęto następujące oznaczenie sygnałów:

x, z - bity liczb wejściowych

y - bit liczby wyjściowej

p1in, p2in - wejścia przeniesienia z poprzedniego bitu

p1out, p2out - wyjścia przeniesienia do następnego bitu.

xin - wejście bitu liczby x przeniesionego z młodszej pozycji

xout - wyjście bitu liczby x na starszą pozycję.

Tabela opisująca działanie układu wygląda następująco:

p2in |

p1in |

xin |

x |

z |

y |

xout |

p2out |

p1out |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

Ponieważ xout jest powtórzeniem x można pominąć ten sygnał przy rozpisywaniu stanów na poszczególne wejścia multiplekserów.

p2in |

p1in |

xin |

x |

y |

p2out |

p1out |

0 |

0 |

0 |

0 |

z |

0 |

0 |

0 |

0 |

0 |

1 |

z\ |

0 |

z |

0 |

0 |

1 |

0 |

z\ |

0 |

z |

0 |

0 |

1 |

1 |

z |

0 |

1 |

0 |

1 |

0 |

0 |

z\ |

0 |

z |

0 |

1 |

0 |

1 |

z |

0 |

1 |

0 |

1 |

1 |

0 |

z |

0 |

1 |

0 |

1 |

1 |

1 |

z\ |

z |

z\ |

1 |

0 |

0 |

0 |

z |

0 |

1 |

1 |

0 |

0 |

1 |

z\ |

z |

z\ |

1 |

0 |

1 |

0 |

z\ |

z |

z\ |

1 |

0 |

1 |

1 |

z |

1 |

0 |

1 |

1 |

0 |

0 |

z\ |

z |

z\ |

1 |

1 |

0 |

1 |

z |

1 |

0 |

1 |

1 |

1 |

0 |

z |

1 |

0 |

1 |

1 |

1 |

1 |

z\ |

1 |

z |

Symbol z\ w powyższej tabeli oznacza negację sygnału z. Cztery ostatnie wiersze tej tabeli nie mają znaczenia praktycznego - układ nigdy nie dojdzie do takiego stanu.

Na wejścia pierwszej komórki należy podać p2in=p1in=xin=0.

Tabelka opisująca działanie dekodera jest następująca:

p2in |

p1in |

xin |

y |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

10 |

1 |

0 |

0 |

10 |

1 |

0 |

1 |

11 |

1 |

1 |

0 |

11 |

1 |

1 |

1 |

100 |

Nawet uwzględniając fakt, że układ nigdy nie znajdzie się w stanie opisanym przez dwa najniższe wiersze powyższej tabeli, do przedstawienia całego możliwego wyniku dla dowolnych liczb wejściowych potrzebujemy dekodowania dwóch bitów a zestaw laboratoryjny umożliwia dekodowanie tylko jednego bitu. Zrealizowanie dekodera jest więc niemożliwe.

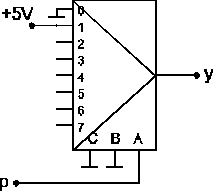

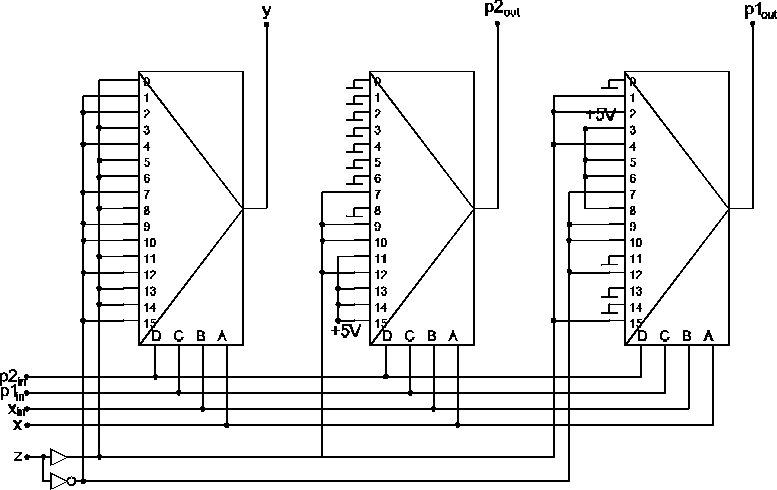

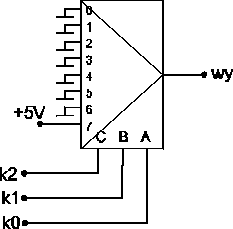

Proponowany schemat jednej komórki układu iteracyjnego:

3. Wykrywanie sekwencji trzech zer przedzielonych maksymalnie jedną jedynką.

Przyjęto następujący format informacji przesyłanych między poszczególnymi komórkami układu iteracyjnego:

Kod |

Opis |

000 |

żaden bit nie pasuje |

001 |

dotychczas pasuje 0 |

010 |

dotychczas pasuje 00 |

011 |

dotychczas pasuje 01 |

100 |

dotychczas pasuje 001 |

101 |

dotychczas pasuje 010 |

110 |

--- kod niewykorzystywany |

111 |

jest właściwa sekwencja wejściowa |

Przy przyjęciu następujących oznaczeń:

x - bity sekwencji wejściowej

k0-k2 - wejścia informacyjne z poprzedniego bitu

k0'-k2' - wyjścia informacyjne do następnego bitu, tabelka opisująca działanie układu jest następująca:

k2 |

k1 |

k0 |

x |

k2' |

k1' |

k0' |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Stan k2-k0 równy 110 nie jest wykorzystywany, można wpisać do tabeli w tamtym miejscu stany dowolne.

Na wejścia k2-k0 układu sprawdzającego stan pierwszego bitu trzeba podać stan 000.

Tabelka działania dekodera jest następująca:

k2 |

k1 |

k0 |

wy |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

Stan logiczny 1 na linii wy oznacza, że w sekwencji wejściowej występuje ciąg trzech zer przedzielonych maksymalnie jedną jedynką.

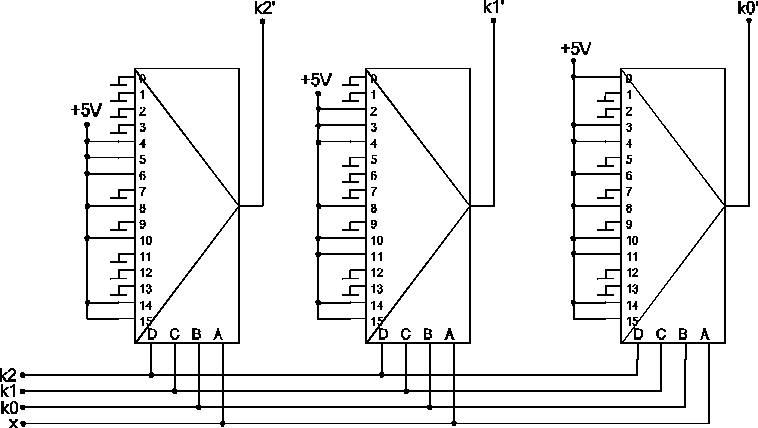

Schematy układu iteracyjnego oraz dekodera wyglądają następująco:

1

3

Wyszukiwarka

Podobne podstrony:

programowalny dzielnik częśtotliwości, Studia, Informatyka, Semestr III, Teoria Układów Cyfrowych, L

sprawko 11, Studia, PWR, 3 semestr, Logika układów cyfrowych, laboratoria

sprawko 3a, Studia, PWR, 3 semestr, Logika układów cyfrowych, laboratoria

sprawko 11a, Studia, PWR, 3 semestr, Logika układów cyfrowych, laboratoria

Badanie cyfrowych bramek logicznych2, Laboratorium układów elektronicznych

sprawko 10, Studia, PWR, 3 semestr, Logika układów cyfrowych, laboratoria

sprawko 10a, Studia, PWR, 3 semestr, Logika układów cyfrowych, laboratoria

sprawko 4, Studia, PWR, 3 semestr, Logika układów cyfrowych, laboratoria

Przetworniki anologowo-cyfrowe, Laboratorium układów elektronicznych

podsekcja radzio, Studia, Informatyka, Semestr III, Teoria Układów Cyfrowych, Laboratorium, lab4

ELEKTRO.4., LABORATORIUM UKŁADÓW ANALOGOWYCH I CYFROWYCH

Wykład XI Metody opisu układów cyfrowych

203 rejestry, Politechnika Wrocławska - Materiały, logika ukladow cyfrowych, sprawozdania

Laboratorium 4, Politechnika Koszalińska, III semestr, Laboratorium techniki cyfrowej

laboratorium z układów logicznych komparator 3K2PVJZOBCA2ZQGNHSNH7M2IUH65NCCO5GUG55A

sterna,logika układów cyfrowych L, Komputerowa synteza automatu z parametrem wewnętrznym

Podstawy ukladow cyfrowych, plik7

PODZIAŁ UKŁADÓW CYFROWYCH ?FINICJE

Laboratorium 6, Politechnika Koszalińska, III semestr, Laboratorium techniki cyfrowej

więcej podobnych podstron