T7 Cyfrowe układy kombinacyjne

Cyfrowe funktory TTL i CMOS - badanie. Metodologia i technika składania układów kombinacyjnych i ich badania.

Przed zajęciami.

A) Zapoznaj się (literatura, wykład) z właściwościami cyfrowymi (tabele prawdy, dopuszczalne poziomy Hi i Lo) i analogowymi (charakterystyki: wejściowe, przejściowe, wyjściowe) wymienionych na początku „Programu ćwiczenia” układów cyfrowych.

B) Do każdego punktu „Programu ćwiczenia” narysuj schemat logiczny. Jeżeli układ wymaga projektu - koniecznie dodaj odpowiednią tabelę prawdy i dowód logiczny według zasad algebry Boole'a.

Program ćwiczenia.

Stosowane w ćwiczeniu układy scalone to z grupy TTL: 7400 (cztery NAND 2-wej), 1 szt.

7404 (sześć NOT), 1 szt.

7486 (cztery EX-OR 2-wej) 1 szt.

oraz z grupy CMOS 74001 (cztery NOR 2-wej) 1 szt.

Tylko te układy możesz wykorzystać do projektu!

Wszystkie uruchamiane i badane układy będą zasilane tylko jednym napięciem, znamionowo: Usup = + 5 V.

A. Badania funktorów:

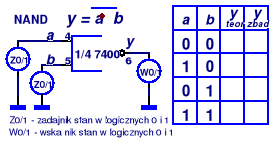

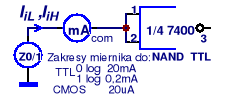

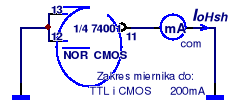

1. Zbadaj zgodność działania z tablicą prawdy funktora NAND (7400 - TTL) - przykład na rys. 1. Zmierz prądy wejściowe w stanie 0 i 1 wejść połączonych razem (rys.2). Zmierz także prąd zwarcia wyjścia do masy w stanie 1 (rys.3).

2. Powtórz badania z pkt.1 dla funktora NOR (74001 - CMOS).

B. Konwersja funktorów; zaprojektuj, połącz i zbadaj działanie logiczne układu:

3. Funktora NOR 2-wej zrobionego z NAND'ów z jednego 7400,

4. Funktora EX-OR 2-wej zrobionego z NAND'ów z jednego 7400,

5. Funktora NAND 3-wejściowy zrobionego z funktorów wymienionych na początku „Programu ćwiczenia”.

C. Realizacja układów kombinacyjnych; zaprojektuj, połącz i zbadaj działanie logiczne układu:

6. Multipleksera 2-wej: wejścia danych X0, X1, wejście sterujące (adresowe) A, wyjście Y.

![]()

7. Demultipleksera 2-wyj: wejście danych X, wejście sterujące (adresowe) A, wyjścia Y0, Y1.

![]()

8. Minimalizacja i realizacja układowa funkcji logicznej (wejścia A, B, C, wyjście Y), zadanej w postaci tabeli prawdy (z tab.1 wybierz kolumnę wg nr twojej grupy!). Minimalizację (np. za pomocą tablicy Karnaugh'a) łatwiej wykonać dla „0” (czyli dla negacji Y) - jest ich mniej. Możesz stosować tylko funktory wymienione na początku „Programu ćwiczenia”.

Wejścia |

Tab.1 Wyjście Y dla grupy nr |

|||||||

A |

B |

C |

1 |

2 |

3 |

4 |

5 |

6 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

_______________________

Rys. 1. Przykład dokumentowania badania

działania funktora logicznego.

Rys. 2. Pomiary wejściowych prądów.

Rys. 3. Pomiar wyjściowego zwarciowego prądu

przy stanie 1 na wyjściu.

Wyszukiwarka

Podobne podstrony:

sprawozdanie na elektre 1, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

T5PEL, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

T4PEL, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

kolo elektronika, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

T2PEL, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

T3PEL, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

T8PEL, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

pytania teoretyczne- kolokwium, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

T6PEL, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

ŚĆIĄGA PEL, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

pel1 w5, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki, wykład

T1PEL, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

WZMACNIACZ WE-sprawozdanie, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

SPRAWOZADANIE- ćw 2, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

KOLPEL1 z08-09, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki

pel1 w3, Automatyka i robotyka air pwr, II SEMESTR, Podstawy elektroniki, wykład

Automatyka SPRAWKO nandy, Automatyka i robotyka air pwr, IV SEMESTR, Podstawy automatyki 2, laborki

nandy, Automatyka i robotyka air pwr, IV SEMESTR, Podstawy automatyki 2, laborki

zadania na kolokwium-programowanie, Automatyka i robotyka air pwr, II SEMESTR, Programowanie w język

więcej podobnych podstron