Politechnika Częstochowska

Wydział Elektryczny

Instytut Elektroniki i Systemów Sterowania

Instrukcja do ćwiczeń laboratoryjnych

TEMAT: Badanie przerzutników

Częstochowa 2010

SPIS TREŚCI

Cel ćwiczenia 3

1 Wstęp teoretyczny 3

1.1 Zasada działania przerzutników 3

1.2 Podstawowe przerzutniki cyfrowe 3

1.3 Konwersja przerzutników 14

2 Opis układu 15

3 Przebieg ćwiczenia 17

3.1 Badanie przerzutnika RS 17

3.2 Badanie przerzutnika typu D 19

3.3 Badanie przerzutnika D- latch 20

3.4 Badanie przerzutnika typu T 21

3.5 Badanie przerzutnika JK 22

3.6 Badanie przerzutnika JK-MS 23

3.7 Badanie przerzutnika Schmitta 24

Pytania kontrolne 26

Literatura 27

Cel ćwiczenia

Celem ćwiczenia jest praktyczne zapoznanie się z zasadami działania przerzutników cyfrowych ich konwersją oraz zastosowaniem w technice cyfrowej.

Wstęp teoretyczny [1,2,3,4]

Zasada działania przerzutników

Podstawowe przerzutniki cyfrowe

Konwersja przerzutników

Opis układu

Przebieg ćwiczenia

Badanie przerzutnika RS

Badanie przerzutnika typu D

Badanie przerzutnika typu D-latch

Badanie przerzutnika typu T

Badanie przerzutnika JK

Badanie przerzutnika JK-MS

Badanie przerzutnika Schmitta

Jakie są różnice pomiędzy przerzutnikiem RS synchronicznym a asynchronicznym oraz przedstawić ich realizację na bramkach logicznych.

Zbudować przerzutnik D z bramek oraz przerzutnika JK.

Zbudować i wyjaśnić działanie przerzutnika D-latch.

Przedstawić różnicę pomiędzy przerzutnikiem JK i JK-MS.

Narysować schemat przerzutnika Schmitta zbudowanego na bramkach oraz wyjaśnić działanie tego przerzutnika.

Konwersja przerzutników na dwójkę liczącą.

Wilkinson: „Układy cyfrowe”, WKŁ, Warszawa 2000

Impulsowe układy generacyjne, nazywane przerzutnikami, wykorzystują zjawisko niestabilności w aktywnych układach elektronicznych w celu uzyskania bardzo szybkiego przerzutu od jednego stanu stabilnego do drugiego. Sygnały elektryczne, takie jak napięcie, istnieją w systemach cyfrowych w jednej z dwóch rozróżnialnych wartości: poziom niski L (ang. Low) oraz poziom wysoki H (ang. High). Przypisanie wartości dwójkowych 0 i 1 tym poziomom jest dowolne. W praktyce zamiast poziomów określa się dwa pola tolerancji, wewnątrz których powinien znajdować się poziom sygnału reprezentującego logiczne 0 i 1.

Przerzutniki działają na podobnej zasadzie jak generatory drgań sinusoidalnych, z tą różnicą, że obwód sprzężenia zwrotnego nie jest selektywny. Podobnie jak w przypadku generatorów, niestabilności można uzyskać w dwojaki sposób: za pomocą sprzężenia zwrotnego lub stosując elementy o ujemnej rezystancji. W przerzutnikach elementy aktywne pracują w zakresie silnych nieliniowości charakterystyk i przybliżania liniowe lub prawie liniowe nie mogą być stosowane.

Przerzutnik RS jest najprostszym rodzajem przerzutnika, który można zbudować z dwóch dwu wejściowych bramek NOR lub NAND. Przerzutnik powstaje dzięki sprzężeniu zwrotnemu wyjść z wejściami. Sprzężenie zwrotne powoduje, iż przerzutnik utrzymuje ostatni stan wyjść Qn-1 po przejściu stanów logicznych na wejściach w stan neutralny.

Przerzutnik asynchroniczny RS składa się z dwóch bramek NOR. Budowę wewnętrzną pokazuje rysunek 1.1:

Rys.1.1. Schemat połączeń przerzutnika RS i jego widok w formie bloku

Działanie układu przerzutnika przedstawiono w tabeli (rys. 1.2).

|

|

|

|

Funkcja |

0 |

0 |

0/1 |

1/0 |

Pamiętanie stanu poprzedniego |

0 |

1 |

1 |

0 |

Ustawienie wyjścia Q |

1 |

0 |

0 |

1 |

Zerowanie wyjścia Q |

1 |

1 |

0 |

0 |

Stan zabroniony |

Rys.1.2. Tabela prawdy przerzutnika RS

Przerzutnik![]()

również należy do rodziny układów asynchronicznych. Układ ten jest odwrotnością przerzutnika RS. W skład jego wchodzą zamiast bramek NOR bramki NAND, co uwidacznia rysunek 1.3, działanie układu przedstawiono w tabeli (rys.1.4):

Rys.1.3. Budowa przerzutnika ![]()

|

|

|

|

Stany pracy |

0 |

0 |

1 |

1 |

Zabroniony |

0 |

1 |

0 |

1 |

Zerowanie wyjścia Q |

1 |

0 |

1 |

0 |

Ustawienie wyjścia Q |

1 |

1 |

0/1 |

1/0 |

Pamiętanie stanu poprzedniego |

Rys.1.4. Tabela przejść przerzutnika

Przerzutnik RS występuje również w formie synchronicznej. W odróżnieniu od układu asynchronicznego dodatkowo pojawia się tu sygnał zegarowy C, którego zadaniem jest synchronizacja przerzutnika z całym układem.

Schemat realizacji przerzutnika synchronicznego pokazano na rysunku 1.5, a symbol graficzny na rys. 1.6.

Rys.1.5.Realizacja przerzutnika synchronicznego RS na bramkach logicznych

Rys.1.6. Symbol graficzny przerzutnika synchronicznego RS

Aby dokładniej przedstawić zależności i zasadę działania przerzutnika zamieszczono przebiegi czasowe (rys.1.7) powyższego układu, a w tabeli (rys.1.8) zawarto rozkład sygnałów wzbudzeń tego elementu.

Rys.1.7. Przebiegi czasowe przerzutnika RS synchronicznego

Rys.1.8. Tabela przełączeń przerzutnika synchronicznego typu RS ; nawiasami oznaczono stany niedozwolone

Przerzutnik D posiada wejście danych D, wejście zegarowe C oraz dwa komplementarne wyjścia Q i ![]()

(rys.1.9). Symbol przerzutnika typu D przedstawia rysunek 1.10, natomiast rysunek 1.11 zawiera tabelę prawdy tego przerzutnika.

Rys.1.9.Realizacja przerzutnika synchronicznego D na bramkach logicznych

Rys.1.10. Symbol przerzutnika typu D

R |

S |

D |

CLK |

Qt+1 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

X |

0 |

Qt |

0 |

0 |

X |

1 |

Qt |

1 |

0 |

X |

X |

0 |

0 |

1 |

X |

X |

1 |

1 |

1 |

Stan zabroniony |

||

Rys.1.11. Tabela przejść dla przerzutnika typu D

W przerzutniku D latch stan wejścia D jest kopiowany na wyjście Q przy wysokim poziomie logicznym na wejściu C. Gdy poziom wejścia C zmieni się na niski, przerzutnik zapamiętuje ostatni stan wyjścia Q. Zmiany na wejściu informacyjnym D nie wpływają już na wyjście Q, które zostało "zatrzaśnięte" zmianą poziomu wejścia C - z tego powodu przerzutniki te noszą często nazwę zatrzask. Na rysunku 1.12 przedstawiono przykłady realizacji przerzutnika D typu Latch.

Rys.1.12. Przykłady realizacji przerzutników D typu latch

Z przerzutnika wyzwalanego zboczem narastającym można uzyskać przerzutnik wyzwalany zboczem opadającym zegara taktującego po dołączeniu negatora na wejście

C (rys.1.13).

Rys.1.13. Schemat przerzutnika wyzwalanego zboczem opadającym sygnału taktującego

Przerzutnik JK posiada dwa wejścia informacyjne J i K, wejście synchronizujące zegar, taktujące „CLK” oraz dwa wyjścia komplementarne: ![]()

i ![]()

. Symbol graficzny tego układu

o wejściu zanegowanym przedstawiono na rysunku 1.14

Rys.1.14. Symbol graficzny przerzutnika typu JK

Zasada działania tego elementu polega na tym, iż z chwila nadejścia impulsu taktującego przerzutnik ten reaguje następujący sposób: gdy na wejściu J jest stan wysoki to na wyjściu otrzymujemy „1”. Gdy na wejściu R podamy „1” wówczas na wyjściu Q powstanie „0”. Poziom wysoki na obydwu wejściach informacyjnych nie jest stanem zabronionym, powoduje on cykliczną zmianę stanów na wyjściu Q - na stan przeciwny do aktualnego, natomiast stan niski na wejściach JK jest stanem pamiętania, czyli nie powoduje zmiany stanu wyjścia. Dokładne działanie tego układu obrazuje tabela (rys.1.15).

R |

S |

J |

K |

CLK |

Qt+1 |

0 |

0 |

0 |

0 |

X |

Qt |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

X |

X |

X |

0 |

0 |

1 |

X |

X |

X |

1 |

1 |

1 |

Stan zabroniony |

|||

Rys.1.15.Tablica przejść dla przerzutnika typu JK

Zgodnie z symbolem graficznym przerzutnik reaguje na zbocze opadające, stany wyjścia

Q zmieniają się wyłącznie zgodnie z zanikiem impulsu zegarowego.

Przerzutnik JK - MS (ang. Master - Slave ) (rys.1.16) jest układem dwutaktowym, czyli działającym w dwóch krokach i potrzebującym obu zboczy impulsu zegarowego do przełączania. Po nadejściu zbocza narastającego informacja z wejść jest wpisywana do przerzutnika, lecz nie zmienia się stan wyjścia. Dopiero nadejście zbocza opadającego powoduje wyłączenie wejść (co izoluje układ od sygnałów zewnętrznych) i przepisanie sygnału na wyjście. Układ jest zbudowany z dwóch przerzutników asynchronicznych:

M (ang. Master), poprzedzonego bramkami sterującymi A1 i A2 oraz S (ang. Slave) sterowanego przez bramki B1 i B2. Jeżeli na wejściu C panuje stan 0, to bramki A1 i A2 są wyłączone i stan wejść informacyjnych nie ma wpływu na działanie tych bramek; można powiedzieć, że do przerzutnika M nie ma dostępu.

Rys.1.16 Schemat ogólny przerzutnika JK - MS

W chwili nadejścia zbocza narastającego informacja z wejść J i K jest wpisana do przerzutnika M, a zamknięty jest dostęp do przerzutnika S (bramki B1 i B2 są wyłączone). Pierwszy takt został zakończony i nic nie może zmienić się w układzie. Dopiero nadejście zbocza opadającego spowoduje wyłączenie bramek wejściowych i włączenie bramek B1 i B2. stan przerzutnika M zostanie przepisany do przerzutnika S.

Funkcje przerzutnika JK są zapisane w tablicy stanów (rys.1.17). Symbol ![]()

(![]()

) oznacza, że dane wyjście przyjmuje stan taki, jaki panował na wyjściu ![]()

(![]()

) przed nadejściem impulsu taktującego. Jeżeli na wejściach J i K występują stany niskie, to podawanie impulsów taktujących nie zmieni stanu przerzutnika (![]()

=![]()

;(![]()

=![]()

). Stan „1” na wejściach J i K wymusza zmianę stanów wyjść przerzutnika na przeciwny (![]()

=![]()

;![]()

=![]()

). Stan wysoki na wejściu J (K = 0) ustawia przerzutnik w stan „1”, a stan wysoki na wejściu K (J = 0) wymusza na wyjściu przerzutnika stan „0”.

Rys.1.17. Tablica stanów przerzutnika JK

Przerzutnik typu T jest częścią (specyficzną konfiguracją) przerzutnika JK. Posiada on jedno wejście informacyjne T wejście taktujące „CLK” oraz wyjścia komplementarne ![]()

i ![]()

(rys.1.18).

Rys.1.18. Symbol graficzny przerzutnika typu T z wejściem zegarowym negowanym

Jeżeli na wejście T podamy stan „1” wówczas zgodnie ze zboczem opadającym impulsu zegarowego przerzutnik zacznie cyklicznie zmieniać stan wyjścia Q na przeciwny. Stan zera logicznego na wejściu T spowoduje zatrzymanie zmian wartości wyjścia Q do kolejnego podania na wejście T jedynki logicznej. Dokładny opis przejść został umieszczony w tabeli (rys.1.19), natomiast przebiegi stanów wyjściowych przedstawiono na rysunku 1.20.

R |

S |

T |

CLK |

Qt+1 |

0 |

0 |

0 |

X |

Qt |

0 |

0 |

1 |

|

|

0 |

1 |

X |

X |

1 |

1 |

0 |

X |

X |

0 |

1 |

1 |

Stan zabroniony |

||

Rys.1.19. Tablica wzbudzeń przerzutnika typu T

Uwaga wejścia R i S działają asynchronicznie i mają one pierwszeństwo przed wejściami informacyjnymi. Nie zawsze ta para występuje, zależy to od rodzaju zastosowanego układu scalonego.

Rys.1.20. Przebieg sygnałów przerzutnika typu T

Zgodnie z tabelą wzbudzeń, przerzutnik typu T zmienia stan wyjścia Q na przeciwny zgodnie z taktami zegarowymi tylko wtedy, kiedy na jego wejściu jest stan wysoki.

Przerzutnik Schmitta należy do grupy układów impulsowych (przełączających). Jest to tak zwany układ progowy, otrzymany poprzez wprowadzenie silnego dodatniego sprzężenia zwrotnego w obwód komparatora. Istnieje wiele rozwiązań przerzutnika Schmitta, wykorzystujący tranzystory, wzmacniacze operacyjne, bramki logiczne i inne. Generalne różnice występują w poziomach napięć w układzie, a także szybkością działania. Jednak mimo to każdy przerzutnik Schmitta reaguje na chwilową wartość napięcia wejściowego,

a nie, jak by się wydawało, na zbocze. Dzięki tej zalecie nie ma znaczenia, jaki sygnał doprowadzimy na wejście.

W tym przerzutniku istnieje pętla histerezy, jest to bardzo korzystne ze wzglądu na możliwość tłumienia zakłóceń, jakie pojawiają się na wejściu przerzutnika. Jeśli napięcie przekroczy wartość UT(+), to układ pozostanie w stanie wysokim i nie zmieni swej wartości pod wpływem jakiegoś dodatkowego napięcia, jakie pojawiłoby się na wejściu układu (taka zmiana wartości pojawiłaby się w zwykłym komparatorze). Zatem dzięki histerezie układ Schmitta doskonale nadaje się do rekonstrukcji odkształconych przebiegów w układach cyfrowych. Takie działanie przerzutnika Schmitta zobrazowano na rysunku 1.21.

Rys.1.21. Oscylogram charakterystyki przejściowej bramki z przerzutnikiem Schmitta `74132

Przerzutnik Schmitta z bramkami TTL przedstawiono na rysunku 1.22.W układzie

z bramkami logicznymi pracującymi jako negatory, przy stanie „0” na wejściu bramki B1 jest w stanie wysokim, a bramka B2,mająca na obu wejściach stan „1” - przyjmuje stan niski na wyjściu. Dopóki napięcie na obu wejściach bramki B1 nie osiągnie napięcia progowego układów TTL (UT ![]()

1,4 V), dopóty bramka pozostanie, zgodnie z tablicą stanów, w stanie „1”.

Rys.1.22. Schemat przerzutnika Schmitta z bramkami

Na jedno z wejść jest podawane napięcie poprzez diodę. Aby na wyjściu tym napięcie wyniosło 1,4 V, na wejściu przerzutnika misi wystąpić napięcie o wartości 2,1 V. jest to próg przełączania przy narastaniu napięcia wejściowego UT(+) = 2,1 V. Stan bramki zacznie się zmieniać i jej napięcie wyjściowe powoli będzie się zmniejszać do wartości 1,4 V, po czym zacznie się przełączanie drugiej bramki. Jej napięcie wyjściowe zacznie wzrastać i poprzez pętlę dodatniego sprzężenia zwrotnego zostanie podane na wejście bramki B1. Przyspieszy to narastanie napięcia wejściowego i w ten sposób nastąpi szybkie przełączenie przerzutnika. Przy zmniejszaniu napięcia wyjściowego bramki B1 zacznie zmieniać stan, gdy napięcie na którymkolwiek z wejść osiągnie 1,4 V. Nastąpi to na wejściu przyłączonym bezpośrednio do wejścia przerzutnika. Proces przełączania będzie następował podobnie jak przy narastaniu napięcia. Wartość napięcia progowego przy zmniejszaniu napięcia wejściowego wynosi UT(-) = 1,4 V. Zatem histereza przełączania tego układu wynosi UH = 0,7 V. Szybkość przełączania przerzutnika Schmitta jest tym większa, im krótszy jest czas przełączania układu. Zależy ona od szybkości bramek użytych do budowy układu. Miarą tej szybkości jest czas narastania impulsów prostokątnych uzyskiwanych na wyjściu układu.

Dwójka licząca. Zadaniem dwójki liczącej jest zmiana stanu wyjściowego po każdym okresie zegara, co jest równoznaczne z podzieleniem częstotliwości zegara przez 2. Dwójkę liczącą możemy uzyskać z przerzutników różnego typu (np. JK, D lub T). Na rysunku 1.23 przedstawiono kilka przykładów dwójki liczącej.

Rys. 1.23 Przykłady konwersji przerzutników na dwójkę liczącą.

Uwaga:

Należy pamiętać, że przerzutnik D użyty do zbudowania dwójki liczącej nie może być wyzwalany poziomem gdyż w takiej konfiguracji przy aktywnym poziomie na wejściu zegarowym na wyjściu otrzymamy drgania o okresie równym podwojonemu czasowi propagacji przerzutnika

Przerzutnik JK jest elementem dającym największe możliwości przekształcania w inne przerzutniki. Związane jest to z istnieniem dwóch wejść informacyjnych. Przykład wykorzystania przerzutnika JK do budowy przerzutników D i T przedstawiono na rysunku 1.24

Rys. 1.24. Przykład konwersji przerzutnika JK w przerzutnik typu T (a) i typu D (b)

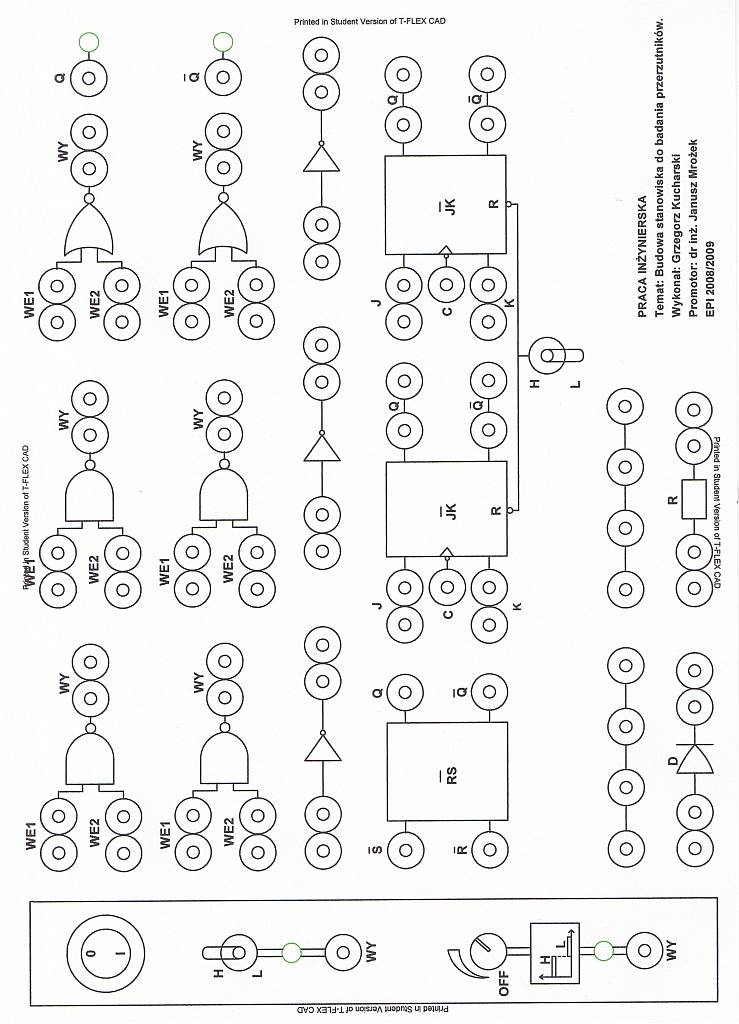

Układ wykonany jest w postaci makiety przedstawionej na rysunku poniżej.

Rysunek 2.1 Ogólny widok płyty czołowej układu

Układ składa się z bramek logicznych NAND, NOR oraz NOT służących do budowy wybranych przerzutników cyfrowych. Oprócz bramek układ zawiera też scalone przerzutniki cyfrowe takie jak RS i JK. Poprzez konwersję tych przerzutników student może przeprowadzić badanie innych przerzutników takich jak D, D-latch oraz przerzutnika typu T.

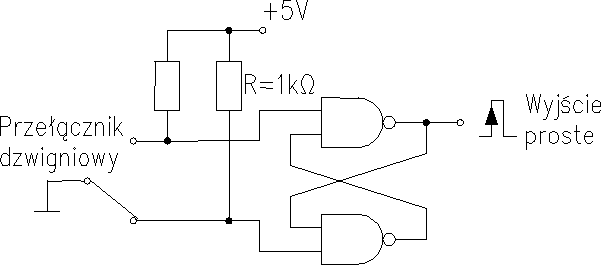

Układ posiada własne zasilanie wewnętrzne w postaci zasilacza stabilizowanego zbudowanego na transformatorze, prostowane napięcie jest stabilizowane na +5V za pomocą stabilizatora 7805. Poprzez zastosowanie zasilania wewnętrznego zostało zminimalizowane zagrożenie podłączenia układu innym napięciem, co mogłoby spowodować uszkodzenie układów. Układ uruchamia się za pomocą włącznika 0/1. Stany logicznej „1” oraz logicznego „0” mogą być zadawane ręcznie jak i automatyczne poprzez podłączenie wejść do układu generatora stanów logicznych zbudowanego z multiwibratora NE 555. Przełącznik posiada styki przełączające współpracujące z elementarnym przerzutnikiem RS, którego wyjście proste jest wyprowadzone i opisane jako „L” i „H”. Zastosowanie przerzutnika RS w impulsatorze eliminuje drgania styków i daje logiczny sygnał na wyjściu o dużej stromości zbocza. Schemat ideowy impulsatora pokazany jest na rysunku 2.2.

Poniżej przerzutników umieszczone są dodatkowe zaciski, dzięki którym można rozdzielić poszczególne stany logiczne. Układ zawiera również elementy dyskretne służące do budowy przerzutnika Schmitta. Są nimi dioda oznaczona litera „D” oraz rezystor „R” o wartości 390Ω. Do łączenia układów należy wykorzystać przewody zakończone wtykami typy „banan”. Cały układ znajduje się w aluminiowej walizce zamykanej na zatrzaski, dzięki temu jest możliwe bezpieczne przechowywanie układu.

Zbudować przerzutnik RS z bramek NOR, wyjścia zbudowanego układu połączyć

z wejściem diody LED oznaczonym odpowiednio ![]()

i ![]()

, podawać na jego wejścia kombinację stanów logicznych, wyniki zapisywać w tablicy stanów.

|

|

|

|

0 |

0 |

|

|

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

|

|

Zbudować przerzutnik ![]()

z bramek NAND, wyjścia zbudowanego układu połączyć

z wejściem diody LED oznaczonym odpowiednio ![]()

i ![]()

, podawać na jego wejścia kombinację stanów logicznych, wyniki zapisywać w tablicy stanów.

|

|

|

|

0 |

0 |

|

|

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

|

|

Wykorzystując bramki NAND i NOR zbudować synchroniczny przerzutnik RS. Wyjścia zbudowanego układu połączyć z wejściem diody LED oznaczonym odpowiednio ![]()

i ![]()

. Podać na wejście zegarowe poziom „L” a na wejścia ustawiające możliwą kombinację poziomów logicznych. Po zapisaniu wyników w tabeli stanów podajemy na wejście zegarowe poziom „H” a na wejścia ustawiające możliwą kombinacje poziomów logicznych, wyniki zapisujemy w tabeli.

|

|

|

|

|

0 |

0 |

0 |

|

|

0 |

1 |

0 |

|

|

0 |

0 |

1 |

|

|

0 |

1 |

1 |

|

|

1 |

0 |

0 |

|

|

1 |

1 |

0 |

|

|

1 |

0 |

1 |

|

|

1 |

1 |

1 |

|

|

Korzystając z dostępnych bramek logicznych zbudować przerzutnik typu D. Wyjścia zbudowanego układu połączyć z wejściem diody LED oznaczonym odpowiednio ![]()

i ![]()

.

Do wejścia zegarowego C podłączyć wyjście taktujące, zmieniać kolejno zadawane stany, odczytane wyniki zapisywać w tabeli.

D |

C |

|

|

0 |

0→1 |

|

|

0 |

1→0 |

|

|

1 |

X |

|

|

1 |

0→1 |

|

|

1 |

1→0 |

|

|

0 |

X |

|

|

0 |

0→1 |

|

|

0 |

1→0 |

|

|

Uwaga !!! Przed rozpoczęciem badania przerzutnika należy na wejściu R ustawić poziom „H”, po podłączeniu wszystkich wyprowadzeń ustawiamy poziom „L” i zaczynamy badanie układu.

Wykonać konwersję przerzutnika JK w przerzutnik D wyzwalany zboczem narastającym. Wyjścia zbudowanego układu połączyć z wejściem diody LED oznaczonym odpowiednio

![]()

i ![]()

. Na wejście ustawiające podawać odpowiednio stany z tabeli poniżej, zaobserwować przy jakim ustawieniu wejścia zegarowego C następuje zmiana poziomu na wyjściach. „x” oznacza brak zmiany stanu wejścia zegarowego względem stanu poprzedniego.

D |

C |

|

|

1 |

1→0 |

|

|

0 |

X |

|

|

0 |

0→1 |

|

|

0 |

1→0 |

|

|

1 |

X |

|

|

1 |

0→1 |

|

|

1 |

1→0 |

|

|

Uwaga !!! Przed rozpoczęciem badania przerzutnika należy na wejściu R ustawić poziom „H”, po podłączeniu wszystkich wyprowadzeń ustawiamy poziom „L” i zaczynamy badanie układu.

Wykonać konwersję przerzutnika JK w przerzutnik T. Wyjścia zbudowanego układu połączyć z wejściem diody LED oznaczonym odpowiednio ![]()

i ![]()

. Na wejście ustawiające podawać odpowiednio stany z tabeli poniżej, zaobserwować w jaki sposób zachowuje się zbudowany układ.

T |

C |

|

|

1 |

0→1 |

1 |

0 |

1 |

1→0 |

1 |

0 |

1 |

0→1 |

0 |

1 |

1 |

1→0 |

0 |

1 |

1 |

0→1 |

1 |

0 |

1 |

1→0 |

1 |

0 |

0 |

0→1 |

1 |

0 |

0 |

1→0 |

1 |

0 |

0 |

0→1 |

1 |

0 |

0 |

1→0 |

1 |

0 |

1 |

0→1 |

0 |

1 |

0 |

1→0 |

0 |

1 |

0 |

0→1 |

0 |

1 |

0 |

1→0 |

0 |

1 |

Uwaga !!! Przed rozpoczęciem badania przerzutnika należy na wejściu R ustawić poziom „H”, po podłączeniu wszystkich wyprowadzeń ustawiamy poziom „L” i zaczynamy badanie układu.

Na wejścia przerzutnika podawać kolejno sygnały zgodne z tabelą z zamieszczoną poniżej , natomiast na wejście zegarowe pełny cykl impulsu. Przy ustawieniu J=1 i K=1 podajemy kolejno trzy pełne impulsy na wejście zegarowe. Wartości na wyjściach zapisujemy w tabeli.

C |

J |

K |

|

|

0→1 |

0 |

0 |

|

|

1→0 |

0 |

0 |

|

|

0→1 |

0 |

1 |

|

|

1→0 |

0 |

1 |

|

|

0→1 |

1 |

0 |

|

|

1→0 |

1 |

0 |

|

|

0→1 |

1 |

1 |

|

|

1→0 |

1 |

1 |

|

|

0→1 |

1 |

1 |

|

|

1→0 |

1 |

1 |

|

|

0→1 |

1 |

1 |

|

|

1→0 |

1 |

1 |

|

|

Uwaga !!! Przed rozpoczęciem badania przerzutnika należy na wejściu R ustawić poziom „H”, po podłączeniu wszystkich wyprowadzeń ustawiamy poziom „L” i zaczynamy badanie układu.

Na wejścia przerzutnika podawać kolejno sygnały zgodne z tabelą z zamieszczoną poniżej, natomiast na wejście zegarowe pełny cykl impulsu. Przy ustawieniu J=1 i K=1 podajemy kolejno trzy pełne impulsy na wejście zegarowe. Wartości na wyjściach zapisujemy w tabeli. Przy badaniu układu zaobserwować, kiedy następuje przepisanie stanu z części MASTER na część SLAVE.

C |

J |

K |

|

|

|

|

0→1 |

0 |

0 |

|

|

|

|

1→0 |

0 |

0 |

|

|

|

|

0→1 |

0 |

1 |

|

|

|

|

1→0 |

0 |

1 |

|

|

|

|

0→1 |

1 |

0 |

|

|

|

|

1→0 |

1 |

0 |

|

|

|

|

0→1 |

1 |

1 |

|

|

|

|

1→0 |

1 |

1 |

|

|

|

|

0→1 |

1 |

1 |

|

|

|

|

1→0 |

1 |

1 |

|

|

|

|

0→1 |

1 |

1 |

|

|

|

|

1→0 |

1 |

1 |

|

|

|

|

Zbudować przerzutnik Schmitta, do tego celu użyć bramek logicznych oraz elementów dyskretnych takich jak dioda D oraz rezystor R. Do zbudowanego układu doprowadzić zasilanie z zewnętrznego zasilacza regulowanego. Na wejściu jak i na wyjściu układu umieścić woltomierz. Zmianę napięcia na wejściu dokonywać od 0V, wyniki pomiarów napięcia na wyjściu zapisywać co 0,1V. Jeśli zaobserwujemy znaczny skok napięcia na wyjściu przerzutnika powtarzamy pomiary z tą różnicą, że odczyt mierników dokonujemy zmniejszając napięcie co 0,1V od momentu znacznego skoku napięcia na wyjściu przerzutnika. Podczas wykonywania pomiarów zaobserwować, przy jakim napięciu wejściowym następują przełączenia układu. Zastanowić się, w jaki sposób można zmienić wartości napięcia, przy jakich następuje przejście jednego stanu wyjścia na drugi. Wyniki pomiarów zapisać w tabeli.

Tabela przełączania z stanu niskiego na wysoki

Uwe[V] |

0 |

0,1 |

0,2 |

… |

|

|

|

Uwy |

|

|

|

|

|

|

|

U przejścia =

Tabela przełączania ze stanu wysokiego na niski

Uwe[V] |

|

|

|

… |

0,2 |

0,1 |

0 |

Uwy |

|

|

|

|

|

|

|

U przejścia =

Pytania sprawdzające:

Literatura:

2. P. Horowitz, W. Hill: „Sztuka elektroniki, cześć druga”, WKŁ, Warszawa 2001

3. C. Zieliński: „Podstawy projektowania układów cyfrowych”, PWN, Warszawa 2003

4. A. Filipkowski: „Układy elektroniczne analogowe i cyfrowe”, WNT. Warszawa 2003

13

aktualizacja dr inż. S. Gryś - 12 października 2010 r.

Wyszukiwarka

Podobne podstrony:

przetwornikiac, AGH WIMIR AiR, Semestr 4, EAP, lab 7

Sprawko1 lab PA Romaszko, AGH WIMIR AiR, Semestr 3, PA, laborki, sprawko lab1 PA

sprlab3PA, AGH WIMIR AiR, Semestr 3, PA, laborki, sprawko lab3 PA

Projekt śruba rzymska 1, AGH WIMIR AiR, Semestr 4, PKM, materiały na projekty, projekt 2

Sprawozdanie kartka, AGH WIMIR AiR, Semestr 3, JPO, lab6 JPO

projekt chwytaka 21, AGH WIMIR AiR, Semestr 6, RP, projekt chwytak, czyjeś, chwytak

IMIR zakres I rok 2011 2012, AGH WIMIR AiR, Semestr 2, fiza, Semestr II

PKM II sciąga (2), AGH WIMIR AiR, Semestr 4, PKM, egzamin, ściągi

normy śrub, AGH WIMIR AiR, Semestr 4, PKM, materiały na projekty, projekt 2

Pytaniamoje, AGH WIMIR AiR, Semestr 5, Sterowanie dyskretne, SD egzamin

PA 01 Sprawozdanie Wec Zajac 22 A, AGH WIMIR AiR, Semestr 3, PA, laborki, sprawko lab1 PA

sprlab6PA, AGH WIMIR AiR, Semestr 3, PA, laborki, sprawko lab6 PA

plan IMIR 2011 2012, AGH WIMIR AiR, Semestr 2, fiza, Semestr II

Sprawko2PO(lab3i4), AGH WIMIR AiR, Semestr 3, JPO, lab2 JPO

pkm (2), AGH WIMIR AiR, Semestr 4, PKM, egzamin, ściągi

FormZgloszP WU, AGH WIMIR AiR, Semestr 7, patent

skibd222, AGH WIMIR AiR, Semestr 5, sieci, Kolos sieci, Kolos, II kolos

sprlab4PA, AGH WIMIR AiR, Semestr 3, PA, laborki, sprawko lab4 PA

więcej podobnych podstron