Image242

4.4.3.4. Liczniki dziesiętne dwukierunkowe

Przykładowe rozwiązanie dekady dwukierunkowej, zliczającej w kodzie 8421, przedstawiono na rys. 4.251. Maksymalna częstotliwość impulsów zliczanych przez dekadę, zbudowaną z układów TTL serii standardowej wynosi 14 MHz.

Schemat logiczny zmodyfikowanej dekady dwukierunkowej przedstawiono na rys. 4.252. Dodatkowe wyprowadzenie Zj (związane z dodatnim kierunkiem zliczania) i Z2 (związane z ujemnym kierunkiem zliczania) są wykorzystywane do sterowania działaniem dekady. Na rysunku 4.253 przedstawiono sposób tworzenia dwukierunkowych liczników wielodekadowych w oparciu o zmodyfikowane dekady dwukierunkowe. Maksymalna częstotliwość impulsów zliczanych dla tych liczników nie powinna przekraczać 11 MHz.

Schemat logiczny dekady dwukierunkowej zliczającej w kodzie Johnsona oraz dwukierunkowej dekady pierścieniowej przedstawiono odpowiednio na rys. 4.254 i 4.255. Maksymalna częstotliwość impulsów zliczanych przez te dekady wynosi 14 MHz.

4.4.3.5. Rejestry liczące

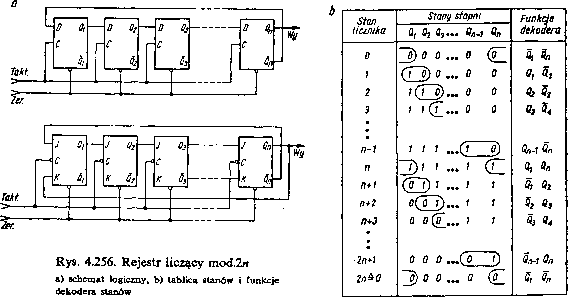

Osobną grupę liczników synchronicznych stanowią liczniki zbudowane w oparciu o rejestr przesuwający zamknięty w pętlę. Jeżeli do pierwszego przerzutnika rejestru przesuwającego jest wpisywana negacja stanu przerzutnika ostatniego, to taki rejestr jest licznikiem o pojemności 2n, gdzie n stanowi liczbę przerzut-

ników w rejestrze. Zasadę budowy tego rodzaju liczników z wykorzystaniem przerzutników typu JK-MS lub typu D przedstawiono na rys. 4.256. Podobnie jak rejestry liczące o pojemności 2n, są realizowane rejestry liczące o pojemności 2n—1. Rejestry takie różnią się od rejestrów o pojemności 2n pętlą sprzężenia. Jeżeli zostanie wyeliminowany np. stan 111 ... 1 licznika zbudowanego

Wyszukiwarka

Podobne podstrony:

Image225 4.4.3.2. Liczniki dwójkowe dwukierunkowe Jako przykład syntezy dwukierunkowego licznika dwó

110 Układy równań liniowych Dziesiąty tydzień - przykłady m Rozwiązania

Image228 Rys. 4.228. Dwójkowy licznik rewersyjny z szeregową propagacją przeniesień4.4.3.3. Liczniki

Image260 jako liczniki dziesiętne. Pojemność licznika składającego się z n dekad liczących wynosi N

Image266 dzie dwójkowym, natomiast w licznikach dziesiętnych liczba N jest nastawiana w kodzie

Image284 Przykłady rozwiązań dwójkowych sumatorów równoległych Na rysunku 4.324 przedstawiono schema

GP przyklad rozwiazanie umowy o prace za porozumieniem stron Rozwiązanie umowy o pracę za porozumien

GP przyklad rozwiazanie umowy o prace z zachowaniem okresu wypowiedzenia TADEX sp. z o.o. &nbs

GP przyklad rozwiazanie umowy w trybie dyscyplinarnym Warszawa, dnia 7 marca 2005 r. TADEX sp. z o.o

Image136 Na rysunku 4.82 przedstawiono przykład rozwiązania pamięci typu RAM, zbudowanej z rejestrów

więcej podobnych podstron