184 185

184

Obecność dwóch wejść zerujących w dekadzie 7490 pozwala w analogiczny aponób skracać cykl tego licznika do takiej liczby stanów, która w zapisie binarnym ma nie więcej niż dwie jedynki. Jednakże, dzięki istnieniu dwóch wejść ustawiających stan 9, można łatwo uzyskać również cykl '/-.etanowy łącząc ^ z SD 1 ^ z S^. **

Opisana w przykładzie metoda skracania cyklu kryje w sobie dwie niedogodności.

Po pierwsze, od pojawienia się stanu P do wyzerowania licznika upływa określony czas (dla licznika 7490 maksymalnie 40 ns). Jest to czas trwania stanu chwilowego, objawiającego się krótkotrwałymi impulsami na niektórych wyjściach licznika (rys. 5.68b). Impulsy te mogą zakłócić pracę dalszych układów i należy je eliminować poprzez strobowanle wyjść.

Po drugie, sygnał zerujący uzyskany z chwilą zdakodowania stanu P zeruje licznik tylko wtedy, gdy czasy zerowania wszystkich jego przerzutni-ków są takie same. Jeżeli choć jeden jego przerzutnlk zareaguje odpowiednio szybciej od pozostałych, to sygnał zerujący, zaniknie i te ostatnie nie zdążą się wyzerować. W praktyce przyjmuje się, że przerzutniki wchodzące w skład tego samego układu scalonego mają identyczne czasy zerowania. Jeżeli jednak licznik rnodP trzeba zbudować z kilku liczników scalonych lub pojedynczych przerzutników, to konieczne są specjalne układy podtrzymujące sygnał zerujący. Ilustruje to poniższy przykład.

Przykład 5.11

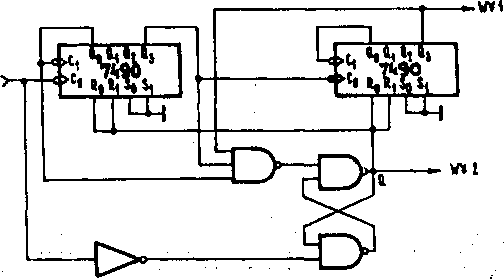

Używając dekad 7^90 chcemy zbudować dzielnik częstotliwości o stosunku podziału 1:89.

Z przebiegów czasowych na rys. 9*668 wynika, że wyjście może pełnić rolę wyjścia sygnału przeniesienia, gdyż pojawia się na nim tylko jeden impuls 1 to taki, który kończy się z chwilą zliczenia dziesięciu impulsów

. Rys. 9*69. Dzielnik częstotliwości 1:89

wejściowych. Łącząc szeregowo dwa liczniki otrzymujemy dzielnik 1:100. Wymagany stosunek podziału zapewnimy zerując liczniki z chwilą wykrycia stanu 9 (Qq = Qj = 1) w liczniku jednostek i jednocześnie etanu 8 (Qj = 1)

o

w liczniku dziesiątek. Elementem wykrywającym Jest bramka NAND, z wejściami której połączone są wymienione trzy wyjścia obu liczników. Zero na wyjściu bramki NAND ustawia przerzutnik RS w stan Q = 1, zerując liczniki (rys. 5.S9). Przerzutnik ten nie zmienia stanu aż do chwili pojawienia się kolejnego Impulsu na wejściu dzielnika, gwarantując w ten sposób wyzerowanie liczników. Wyjściem dzielnika może być którekolwiek z wyjóć WY1,WT2 różniących się czasem trwania Impulsu. Przebiegi na tych wyjściach są wolne od szkodliwych impulsów i nie muszą być strobowane.

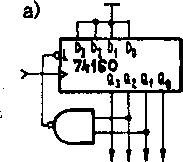

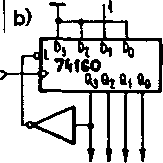

Skracanie cyklu w synchronicznych licznikach MSI

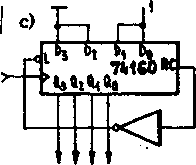

Skracanie cyklu w scalonych licznikach synchronicznych może odbywać się podobnie Jak to opisano wyżej, lecz z uwzględnieniem tego, czy licznik zerowany jest synchronicznie czy asynchronicznie. W przypadku zerowania synchronicznego sygnał zerujący należy wytworzyć w wyniku dekodowania stanu P-1, aby kolejny Impuls wyzerował licznik. Liczniki z zerowaniem synchronicznym nie wymagają układu podtrzymującego sygnał zerujący. Aby uniknąć stosowania tego układu w licznikach z zerowaniem asynchronicznym, można je zerować poprzez równoległe wpisywanie zera, Jeżeli odbywa się ono synchronicznie. V tym przypadku sygnał z detektora stanu P-1 należy podawać na Wejście Load (rys. 5»70a). Poprzez wpisywanie stanu początkowego innego niż zero można uprościć detektor stanu koócowego, jak to pokazano na rys. 5>70b. W szczególności,jako stan końcowy można przyjąć ten, przy którym pojawia się sygnał przeniesienia i tym sygnałem wpisywać odpowiedni stan początkowy (rys. 5.70c).

Rys. 5.70. Różne wersje licznika mod 7 na bazie dekady synchronicznej 74160

Na zakończenie, na rys. 5-71 podajemy krótkie zestawienie liczników produkowanych w serii 74.

Wyszukiwarka

Podobne podstrony:

184 185 184 Obecność dwóch wejść zerujących w dekadzie 7490 pozwala w analogiczny sponób skracać cyk

25930 skanuj0013 (184) słów, zastępując im iniejako • odniesienie;; pozasłowne. Pozwala znaczyć -be

Image412 Do budowy konwerterów równoległych BCD/BIN i BIN/BCD są wykorzystywane układy scalone 184 i

Image414 Zasady implementacji konwerterów BCD/BIN w oparciu o układy 184 oraz konwerterów BIN/BCD w

s 184 185 184 ROZDZIAŁ 6 ZAŁĄCZNIK Ustawa z dnia 26 stycznia 1982 r. - Karta Nauczyciela(tekst jedn.

P1080580 (2) Rys. 185. Automatyczne urządzenie do odmierzania masy serowej (rys. 184) w przekroju pi

str 184 185 nioeuropejskiej od XVI wieku, w Polsce była rzadko używana — wyłącznie w jeździe cudzozi

13897 skanuj0009 (171) 184 Ruch naturalny ludności Urodzenia 185 Zachodzące na początku lat dziewięć

184 185 184 Kliniczne problemy okolic ciała czasu występują tam pola przejaśnień, co jest wyrazem wn

184 185 (2) 184 ODPOWIEDZI twórców, z jednym wyjątkiem. Z93: STRONA. Z94: KOŁO. Należy przejść od ks

więcej podobnych podstron