89947 Untitled42

76

8. Przerwań ją |

przerwania

77

Mikrokontroler nie obsługuje sygnału przerwania, który przyszedł gdy I przerwanie było zablokowane.

Jeżeli do trzeciego cyklu maszynowego procedury przerwania nadejdzie następny sygnał przerwania o wyższym poziomie niż aktualny, to zostanie on obsłużony w pierwszej kolejności. Po wejściu do procedury obsługi przerwany system przerwań zostaje zablokowany Hla innych przerwań, chyba że nadejdzie przerwanie o wyższym priorytecie. Odblokowanie systemu następuje po ro2. kazie RETI. Rozkaz ten ponadto powoduje przepisanie dwóch bajtów ze szcz^a stosu do rejestru rozkazów PC.

Zakończenie podprogramu obsługi przerwania rozkazem RET rów odtworzy zawartość rejestru rozkazów, czyli nastąpi powrót do wyko wania przerwanego programu, ale nie nastąpi odblokowanie systemu przerwań dla następnych przerwań !

7 1 ~ ■ i i——-—i

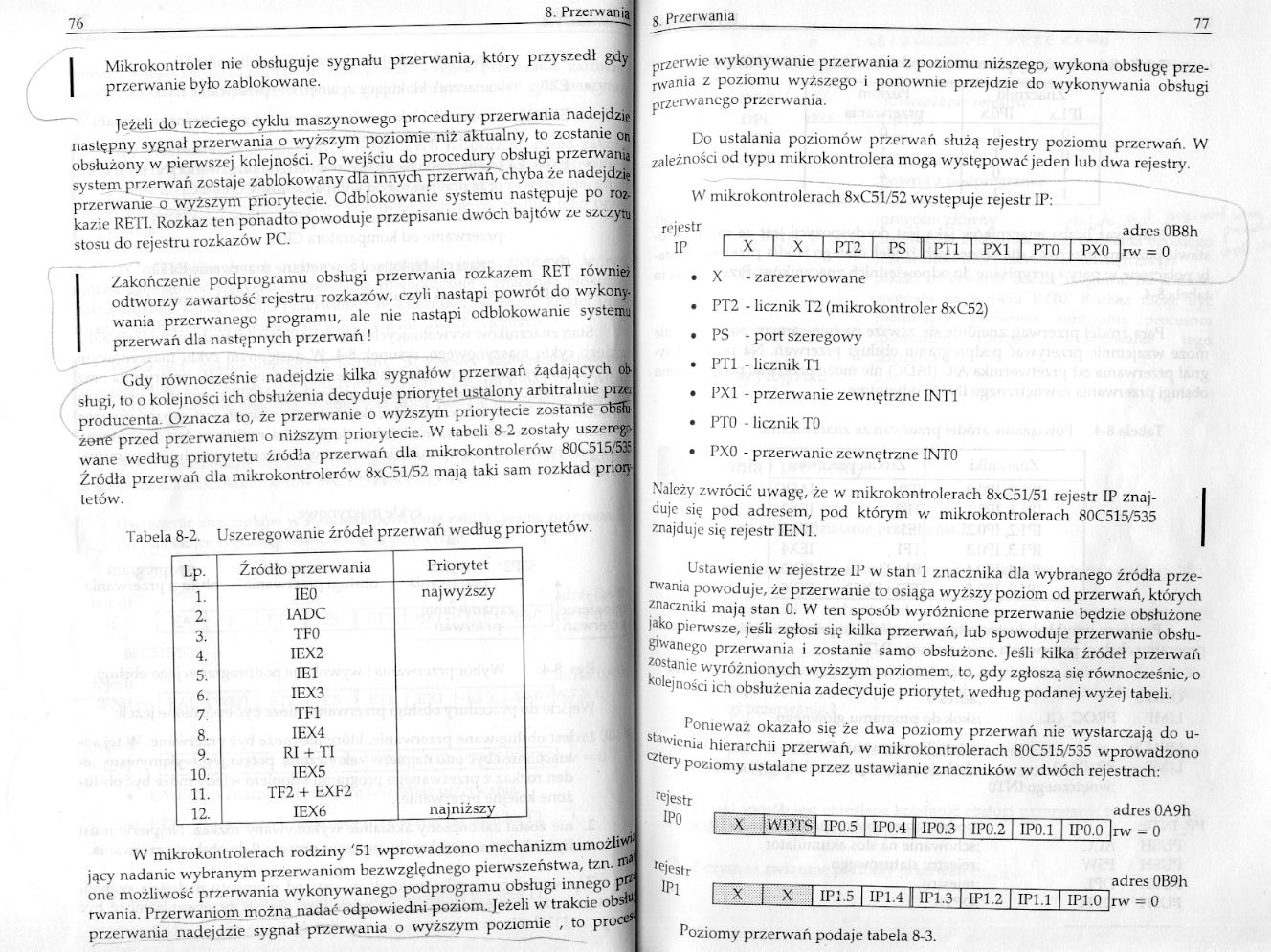

Gdy równocześnie nadejdzie kilka sygnałów przerwań żądających sługi, to o kolejności ich obsłużenia decyduje priorytet ustalony arbitralnie p-producenta Oznacza to, że przerwanie o wyższym priorytecie zostanie ó zorre^przed przerwaniem o niższym priorytecie. W tabeli 8-2 zostały uszerd wane według priorytetu źródła przerwań dla mikrokontrolerów 80C515/53: Źródła przerwań dla mikrokontrolerów 8xC51/52 mają taki sam rozkład priory tetów.

przerwie wykonywanie przerwania z poziomu niższego, wykona obsługę przerwania z poziomu wyższego i ponownie przejdzie do wykonywania obsługi przerwanego przerwania.

Do ustalania poziomów przerwań służą rejestry poziomu przerwań. W zależności od typu mikrokontrolera mogą występować jeden lub dwa rejestry.

W mikrokontrolerach 8xC51/52 występuje rejestr IP:

rejestr

IP

PT2 PS PTI I PX1

PTO

PX0

adres 0B8h rw = 0

Tabela 8-2. Uszeregowanie źródeł przerwań według priorytetów.

|

Lp. |

Źródło przerwania |

Priorytet |

|

1. |

IE0 |

najwyższy |

|

2. |

IADC | |

|

3. |

TFO | |

|

4. |

IEX2 | |

|

5. |

IE1 | |

|

6. |

IEX3 | |

|

7. |

TF1 | |

|

8. |

IEX4 | |

|

9. |

RI + TI | |

|

10. |

IEX5 | |

|

11. |

TF2+ EXF2 | |

|

12. |

IEX6 |

najniższy |

• X - zarezerwowane

• PT2 - licznik T2 (mikrokontroler 8xC52)

• PS - port szeregowy

• PTI - licznik Tl

• PX1 - przerwanie zewnętrzne INT1

• PTO - licznik TO

• PX0 - przerwanie zewnętrzne INTO

Należy zwrócić uwagę, że w mikrokontrolerach 8xC51/51 rejestr IP znajduje się pod adresem, pod którym w mikrokontrolerach 80C515/535 znajduje się rejestr IEN1.

Ustawienie w rejestrze IP w stan 1 znacznika dla wybranego źródła przerwania powoduje, że przerwanie to osiąga wyższy poziom od przerwań, których znaczniki mają stan 0. W ten sposób wyróżnione przerwanie będzie obsłużone jako pierwsze, jeśli zgłosi się kilka przerwań, lub spowoduje przerwanie obsługiwanego przerwania i zostanie samo obsłużone. Jeśli kilka źródeł przerwań etanie wyróżnionych wyższym poziomem, to, gdy zgłoszą się równocześnie, o 0 ejności ich obsłużenia zadecyduje priorytet, według podanej wyżej tabeli.

Ponieważ okazało się że dwa poziomy przerwań nie wystarczają do u-S avv'cr»ia hierarchii przerwań, w mikrokontrolerach 80C515/535 wprowadzono C^tery Poziomy ustalane przez ustawianie znaczników w dwóch rejestrach:

rejestr IPO

adres 0A9h

W mikrokontrolerach rodziny '51 wprowadzono mechanizm urno; jący nadanie wybranym przerwaniom bezwzględnego pierwszeństwa, tzn. one możliwość przerwania wykonywanego podprogramu obsługi innego rwania. Przerwaniom można nadać odpowiedni poziom. Jeżeli w trakcie oł przerwania nadejdzie sygnał przerwania o wyższym poziomie , to prc

—— ~——------ mutra U

X jWDTSI IP0.5 | IP0.4 || IP0.3 | IP0.2 | IP0.1 | IPOO~|rw = 0

— t--—---.-----adres 0B9h

X- 1 X IP1.5 IP1.4 U IP1.3 IP1.2 l lPl.l IP1.0 Irw = 0

Poziomy przerwań podaje tabela 8-3.

Wyszukiwarka

Podobne podstrony:

Untitled39 70 8. Przerwania 8 Przerwania 71 TCON TF1 W mikrokontrolerach rodziny 51 adresy podprogr

Untitled43 78 8. Przerwania Tabela 8-3. Poziomy przerwań w mikrokontrolerach 80C515/535 Znaczniki

Slajd42 (76) Przerwania 1. wewnętrzne 2. zewnętrzne 3.

82679 Untitled41 74 8. Przerwania g. Przerwania 75 ziomu. Dlatego, by układ poprawnie zareagował na

CCF20090702�038 76 Przerwanie immanencji Czy zatem nasza analiza nie powinna wyjść poza literę Husse

Untitled44 80 8. Przerwań OT] -& b r»-1 )<? lko(4ł{*9. Liczniki Liczniki służą do

Untitled Scanned 17 V ^ L i jA*/f h *» &Or<bf7 0 1 * 0Ć^0. n r c *• ‘

Untitled(20) (V*ocn<? ja f i, G)C/Uj O -Aa.cO V/V> ry>rut z >71 dcćcr

więcej podobnych podstron