5 (1174)

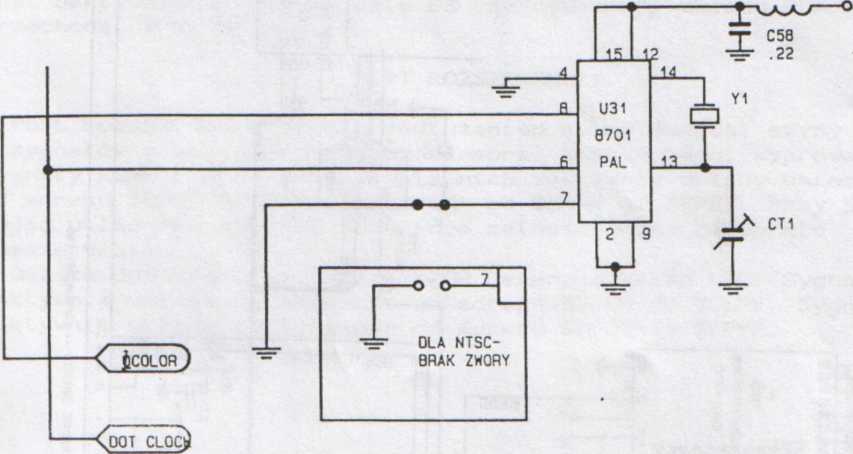

UKŁAD ZEGARA SYSTEMOWEGO MIKROKOMPLiETRA C64-B.

COOTYCZY SCHEMATU 251469“ RYS.4).

Układ zegara systemowego zbudowany jest w oparciu o rezonator kwarcowy Y1 o częstotliwości 16 MHz i układ U31 . Sygnał DOT CLOCK o częstotliwości 8.1818 MHz wyprowadzony Jest na końcówce 6, a sygnał $CLOCK o częstotliwości 14.31818 MHz na końcówce 8.

U 2.2uH CAN

Rys.4. Zegar systemowy C648.

ADRESOWANIE ROM-u I UKŁADÓW WEJŚCIA/WYJŚCIA. PORT ROZSZERZENIA.

Crys.5)

ADRESOWANIE UKŁADÓW WEJSCIA/WYJSCIA.

Układ Ul7 jest programowaną tablicą logiczną CPLA3.

Wyjście F5 układu U17 Ckońcówka 12D oznaczone Jako I/O przechodzi w stan "niski", jeżeli wybrany Jest. którykolwiek układ WE/WY sterowany przez układ Ul5. Poniżej przedstawiona Jest zajętość przestrzeni adresowej przez poszczególne układy WE/WY:

|

VIC IC |

SD000 |

- SD02E |

|

SID IC |

SD400 |

- SD7FF |

|

Color Ram |

SD800 |

- SDBFh |

|

CI Al |

sdcoo |

- SDCOF |

|

CI AS |

SDDOO |

- SDDOF |

|

1/01 |

SDEOO |

- SDEFF |

|

1/02 |

SDFOO |

- SDFFF |

Wyszukiwarka

Podobne podstrony:

4 (309) 119. Naszkicuj koncepcję systemu mikrokomputerowego wykorzystującego układ

Skrypt PKM 1 00135 270 Rozwiązanie Zgodnie z warunkami zadania układ napędowy można przedstawić za p

11 Wprowadzenie jów wejść do systemu. Na rysunku 3 przedstawiono schematyczny sposób zarządzania

skanowanie0059 130 Elektromagnetyzm Przebieg ćwiczenia !. Połączyć układ pomiarowy według schematu n

System alarmowy z automatyką domową. Schemat i typ okablowania. ochronadladomu.pl LAN 4

1. (20) Podstawowy schemat morskiego systemu informacyjnego. Równanie sonaru. Schemat morskiego syst

7A (25) UKŁADY WYJŚCIOWE WIZJI I FONII - ZŁĄCZE 8-MIO KOŃCÓWKOWE Crys.8) DOTYCZY SCHEMATU 251469. Uk

Przyporządkowanie systemów do poszczególnych obszarów.Schemat przyporządkowania poszczególnych zadań

Układy grawitacyjne 61 Rysunek 3.9. Strop zespolony systemu Hambro. wg

System dynamiczny może być schematycznie przedstawiony tak jak na powyższym rysunku. Zachowanie ukła

ASTOR KATALOG SYSTEMÓW STEROWANIA HORNER APG SCHEMATY PODŁĄCZEŃ OUT21 PWM2 OUT1 / PWM1 /+* Supply fo

Mikrokontrolery i mikrosystemy - Z 143. Schemat logiczny, znaczenie linii pamięci FLASH typu NOR o

Mikrokontrolery i mikrosystemy -Z110. Schematyczna budowa układu czasowego w mk oraz jego zasada pra

więcej podobnych podstron