C

CM

MO

OS

S−4

40

00

00

0

47

E

LEKTRONIKA DLA WSZYSTKICH 3/89

K

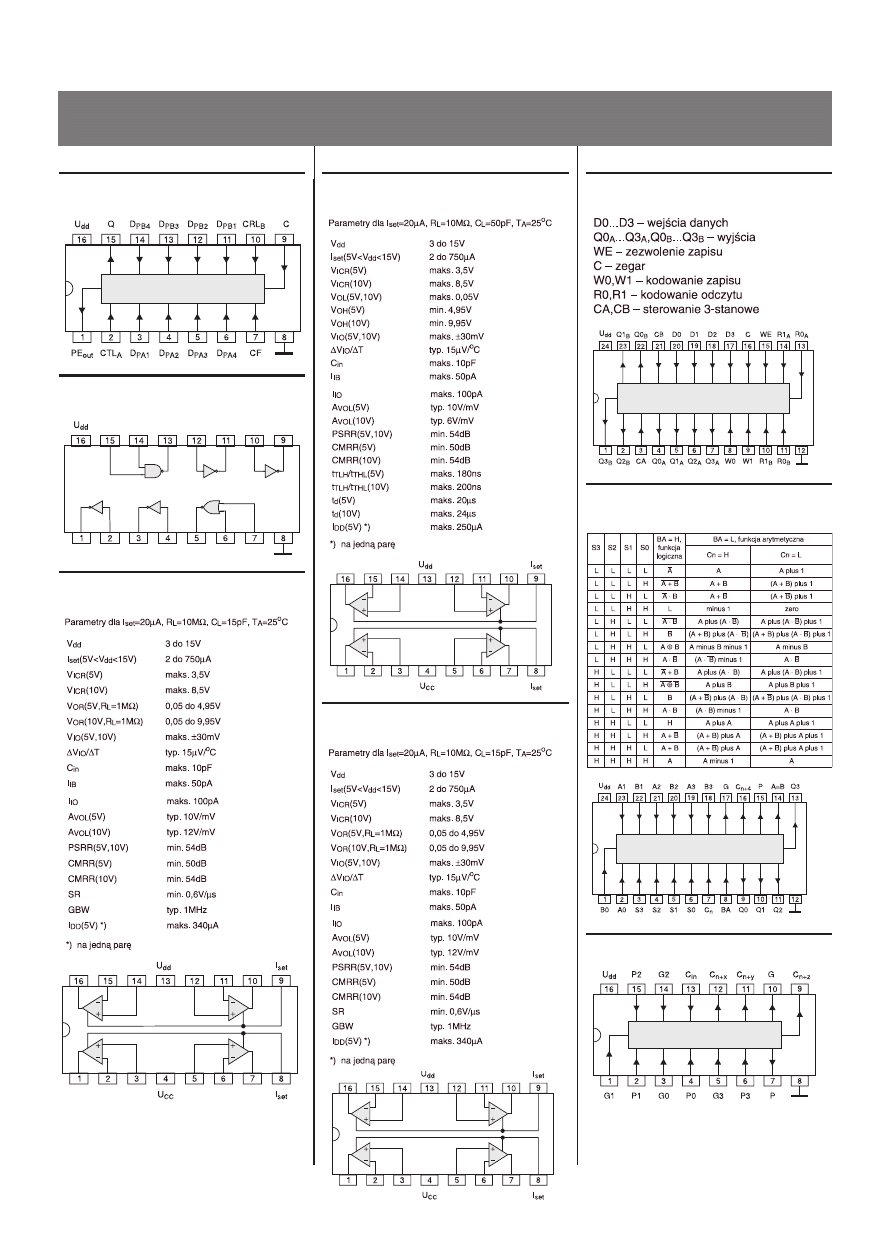

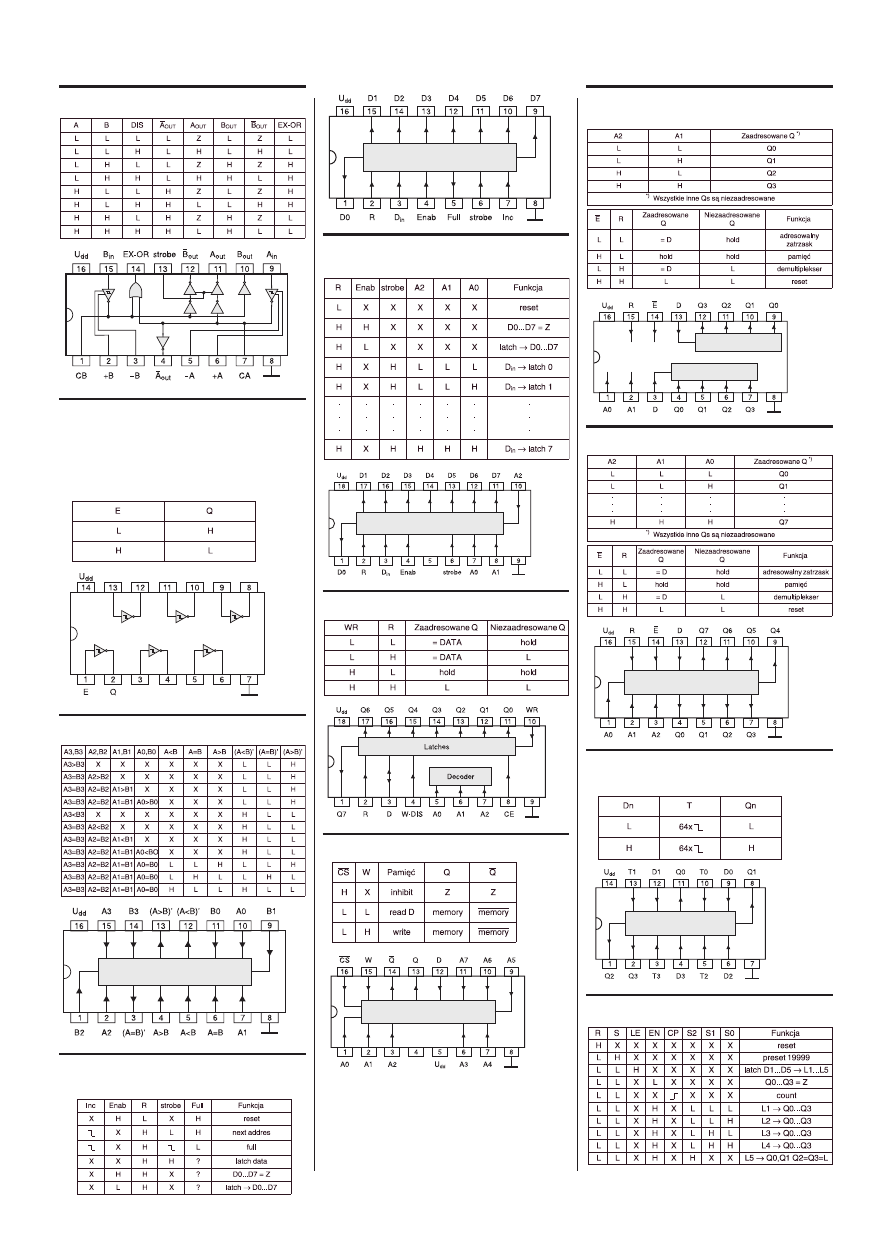

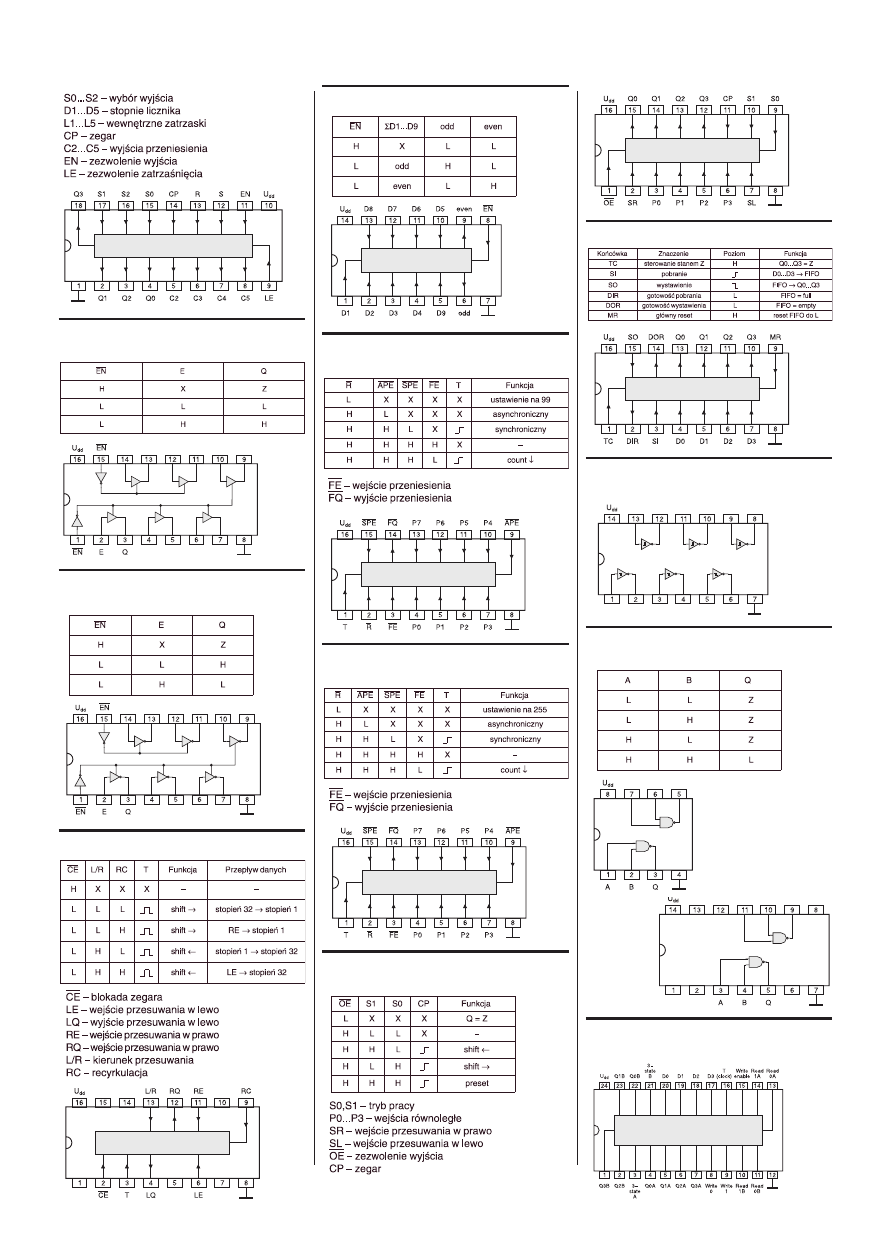

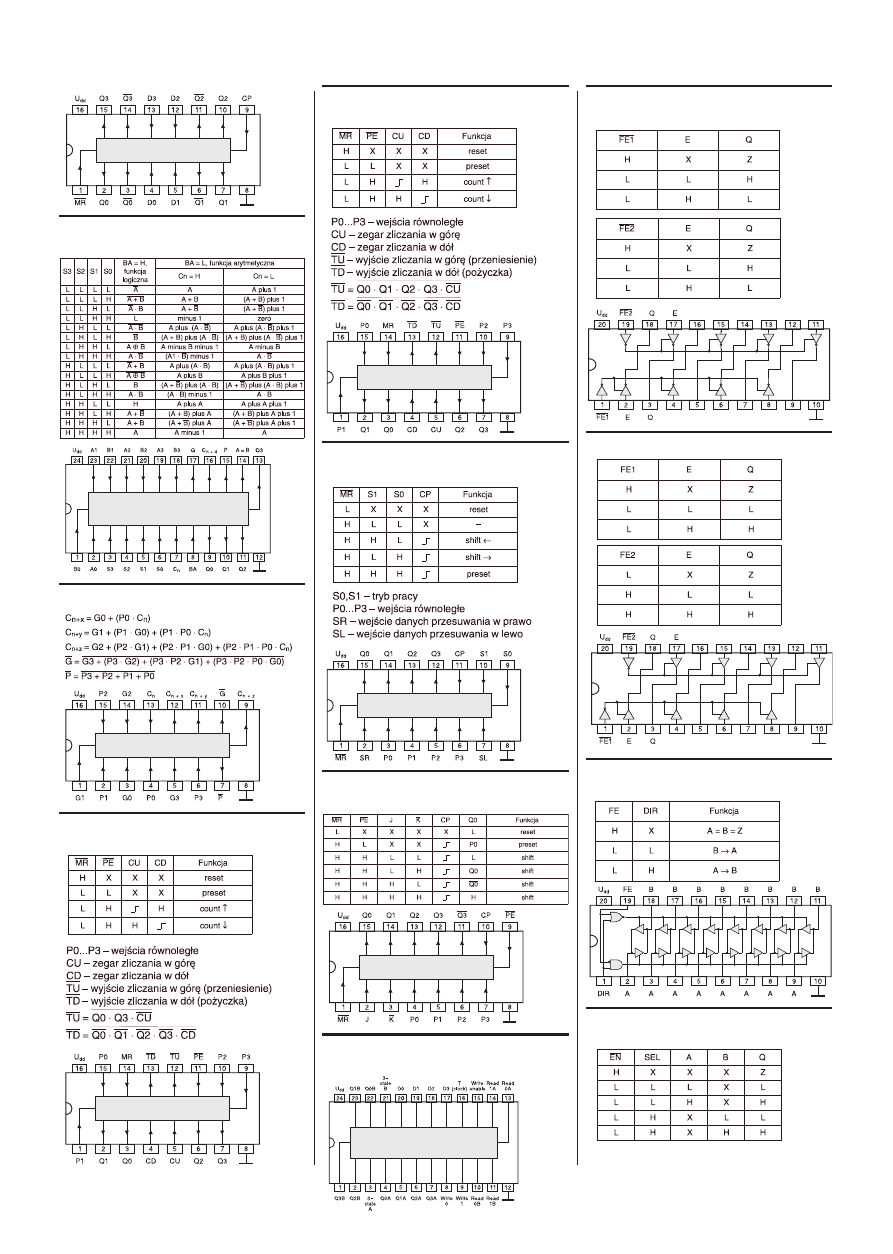

atalog skrócony układów logicznych CMOS serii 4000

4569

P

Po

od

dw

wó

ójjn

ny

y p

prro

og

grra

am

mo

ow

wa

alln

ny

y

4

4−b

biitto

ow

wy

y lliic

czzn

niik

k d

dw

wó

ójjk

ko

ow

wy

y//B

BC

CD

D

4572

K

Ko

om

mb

biin

na

ac

cjja

a b

brra

am

me

ek

k ((N

NA

AN

ND

D,,

N

NO

OR

R,, 4

4×

×N

NO

OT

T))

4573

P

Po

oc

czzw

wó

órrn

ny

y p

prro

og

grra

am

mo

ow

wa

alln

ny

y

w

wzzm

ma

ac

cn

niia

ac

czz o

op

pe

erra

ac

cy

yjjn

ny

y

4574

P

Po

oc

czzw

wó

órrn

ny

y p

prro

og

grra

am

mo

ow

wa

alln

ny

y

k

ko

om

mp

pa

arra

atto

orr

4580

4

4×

×4

4−b

biitto

ow

wy

y rre

ejje

es

sttrr

w

wiie

ello

ob

brra

am

mo

ow

wy

y

4581

4

4−b

biitto

ow

wa

a jje

ed

dn

no

os

sttk

ka

a a

arry

yttm

me

etty

y−

c

czzn

no

o−llo

og

giic

czzn

na

a

4582

G

Ge

en

ne

erra

atto

orr p

prrzze

en

niie

es

siie

en

niia

a

4575

P

Po

oc

czzw

wó

órrn

ny

y p

prro

og

grra

am

mo

ow

wa

alln

ny

y

w

wzzm

ma

ac

cn

niia

ac

czz o

op

pe

erra

ac

cy

yjjn

ny

y

C

CM

MO

OS

S−4

40

00

00

0

E

LEKTRONIKA DLA WSZYSTKICH 3/98

48

4583

P

Po

od

dw

wó

ójjn

ny

y p

prrzze

errzzu

uttn

niik

k S

Sc

ch

hm

miitttta

a

4598

8

8−b

biitto

ow

wy

y a

ad

drre

es

so

ow

wa

alln

ny

y zza

attrrzza

as

sk

k

zzg

go

od

dn

ny

y zz m

ma

ag

giis

sttrra

allą

ą

4599

8

8−b

biitto

ow

wy

y a

ad

drre

es

so

ow

wa

alln

ny

y zza

attrrzza

as

sk

k

4720

2

25

56

6×

×1

1 b

biitt p

pa

am

miię

ęć

ć R

RA

AM

M

4723

P

Po

od

dw

wó

ójjn

ny

y a

ad

drre

es

so

ow

wa

alln

ny

y zza

attrrzza

as

sk

k

4

4−b

biitto

ow

wy

y

4724

8

8−b

biitto

ow

wy

y a

ad

drre

es

so

ow

wa

alln

ny

y zza

attrrzza

as

sk

k

4731

P

Po

oc

czzw

wó

órrn

ny

y 6

64

4−b

biitto

ow

wy

y s

stta

atty

yc

czzn

ny

y

rre

ejje

es

sttrr p

prrzze

es

su

uw

wa

ajją

ąc

cy

y

4737

L

Liic

czzn

niik

k 4

4 1

1//2

2 d

de

ek

ka

ad

dy

y

4584

S

Szze

eś

śc

ciio

ok

krro

ottn

ny

y p

prrzze

errzzu

uttn

niik

k

S

Sc

ch

hm

miitttta

a

4585

4

4−b

biitto

ow

wy

y k

ko

om

mp

pa

arra

atto

orr m

ma

ag

gn

niittu

ud

dy

y

4597

8

8−b

biitto

ow

wy

y lliic

czzn

niik

k//zza

attrrzza

as

sk

k zzg

go

od

dn

ny

y

zz m

ma

ag

giis

sttrra

allą

ą

· Czas propagacji: 200ns przy 5V, 90ns przy 10V

· Łączny pobór prądu: 0,3mA przy 5V, 0,6mA

przy 10V

· Częstotliwość danych: 1MHz

C

CM

MO

OS

S−4

40

00

00

0

49

E

LEKTRONIKA DLA WSZYSTKICH 3/89

40097

S

Szze

eś

śc

ciio

ok

krro

ottn

ny

y b

bu

uffo

orr zz w

wy

yjjś

śc

ciia

a−

m

mii ttrró

ójjs

stta

an

no

ow

wy

ym

mii

40101

9

9−b

biitto

ow

wy

y g

ge

en

ne

erra

atto

orr p

pa

arrzzy

ys

stto

oś

śc

cii

40105

1

16

6×

×4

4 b

biitty

y F

FIIF

FO

O

40106

S

Szze

eś

śc

ciio

ok

krro

ottn

ny

y o

od

dw

wrra

ac

ca

ajją

ąc

cy

y

p

prrzze

errzzu

uttn

niik

k S

Sc

ch

hm

miitttta

a

40107

D

Dw

wiie

e 2

2−w

we

ejjś

śc

ciio

ow

we

e b

brra

am

mk

kii

N

NA

AN

ND

D//b

bu

uffo

orry

y//d

drriiv

ve

erry

y

40108

4

4×

×4

4−b

biitto

ow

wy

y rre

ejje

es

sttrr w

wiie

ello

o−

b

brra

am

mo

ow

wy

y

40102

2

2−d

de

ek

ka

ad

do

ow

wy

y p

prro

og

grra

am

mo

ow

wa

alln

ny

y

lliic

czzn

niik

k B

BC

CD

D w

w d

dó

ółł

40098

S

Szze

eś

śc

ciio

ok

krro

ottn

ny

y iin

nw

we

errtte

err zz w

wy

yjjś

ś−

c

ciia

am

mii ttrró

ójjs

stta

an

no

ow

wy

ym

mii

40100

3

32

2−b

biitto

ow

wy

y rre

ejje

es

sttrr p

prrzze

es

su

uw

wa

ajją

ąc

cy

y

40103

8

8−b

biitto

ow

wy

y p

prro

og

grra

am

mo

ow

wa

alln

ny

y lliic

czzn

niik

k

d

dw

wó

ójjk

ko

ow

wy

y w

w d

dó

ółł

40104

4

4−b

biitto

ow

wy

y d

dw

wu

uk

kiie

erru

un

nk

ko

ow

wy

y

rre

ejje

es

sttrr p

prrzze

es

su

uw

wa

ajją

ąc

cy

y

C

CM

MO

OS

S−4

40

00

00

0

E

LEKTRONIKA DLA WSZYSTKICH 3/98

50

40109

C

Czztte

erro

ok

krro

ottn

ny

y k

ko

on

nw

we

errtte

err

p

po

ozziio

om

mu

u

40147

K

Ko

od

de

err p

pa

arrzzy

ys

stto

oś

śc

cii

40162

S

Sy

yn

nc

ch

hrro

on

niic

czzn

ny

y p

prro

og

grra

am

mo

ow

wa

alln

ny

y

lliic

czzn

niik

k d

dzziie

es

siię

ęttn

ny

y

40160

S

Sy

yn

nc

ch

hrro

on

niic

czzn

ny

y p

prro

og

grra

am

mo

ow

wa

alln

ny

y

lliic

czzn

niik

k d

dzziie

es

siię

ęttn

ny

y

40163

S

Sy

yn

nc

ch

hrro

on

niic

czzn

ny

y p

prro

og

grra

am

mo

ow

wa

alln

ny

y

lliic

czzn

niik

k d

dw

wó

ójjk

ko

ow

wy

y

40161

S

Sy

yn

nc

ch

hrro

on

niic

czzn

ny

y p

prro

og

grra

am

mo

ow

wa

alln

ny

y

lliic

czzn

niik

k d

dw

wó

ójjk

ko

ow

wy

y

40174

S

Szze

eś

śc

ciio

ok

krro

ottn

ny

y p

prrzze

errzzu

uttn

niik

k tty

yp

pu

u D

D

40110

R

Re

ew

we

errs

sy

yjjn

ny

y lliic

czzn

niik

k

d

dzziie

es

siię

ęttn

ny

y//zza

attrrzza

as

sk

k//s

stte

erro

ow

wn

niik

k w

wy

yś

św

wiie

e−

ttlla

ac

czza

a L

LE

ED

D

40117

P

Po

od

dw

wó

ójjn

ny

y 4

4−b

biitto

ow

wy

y o

og

grra

an

niic

czzn

niik

k

m

ma

ag

giis

sttrra

allii ((a

an

ng

g.. T

Te

errm

miin

na

atto

orr))

40175

P

Po

oc

czzw

wó

órrn

ny

y p

prrzze

errzzu

uttn

niik

k tty

yp

pu

u D

D

C

CM

MO

OS

S−4

40

00

00

0

51

E

LEKTRONIKA DLA WSZYSTKICH 3/89

40181

4

4−b

biitto

ow

wa

a jje

ed

dn

no

os

sttk

ka

a a

arry

yttm

me

etty

y−

c

czzn

no

o−llo

og

giic

czzn

na

a

40194

4

4−b

biitto

ow

wy

y d

dw

wu

uk

kiie

erru

un

nk

ko

ow

wy

y

u

un

niiw

we

errs

sa

alln

ny

y rre

ejje

es

sttrr p

prrzze

es

su

uw

wa

ajją

ąc

cy

y

40244

8

8−b

biitto

ow

wy

y d

drriiv

ve

err m

ma

ag

giis

sttrra

allii

40245

8

8−b

biitto

ow

wy

y d

dw

wu

uk

kiie

erru

un

nk

ko

ow

wy

y d

drriiv

ve

err

m

ma

ag

giis

sttrra

allii

40257

P

Po

oc

czzw

wó

órrn

ny

y m

mu

ullttiip

plle

ek

ks

se

err

2

2 n

na

a 1

1−lliin

niię

ę

40240

8

8−b

biitto

ow

wy

y o

od

dw

wrra

ac

ca

ajją

ąc

cy

y d

drriiv

ve

err

m

ma

ag

giis

sttrra

allii

40182

G

Ge

en

ne

erra

atto

orr p

prrzze

en

niie

es

siie

en

niia

a

40195

4

4−b

biitto

ow

wy

y u

un

niiw

we

errs

sa

alln

ny

y rre

ejje

es

sttrr

p

prrzze

es

su

uw

wa

ajją

ąc

cy

y

40208

4

4×

×4

4−b

biitto

ow

wy

y rre

ejje

es

sttrr w

wiie

ello

o−

b

brra

am

mo

ow

wy

y

40192

P

Prro

og

grra

am

mo

ow

wa

alln

ny

y rre

ew

we

errs

sy

yjjn

ny

y

lliic

czzn

niik

k d

dzziie

es

siię

ęttn

ny

y

40193

P

Prro

og

grra

am

mo

ow

wa

alln

ny

y rre

ew

we

errs

sy

yjjn

ny

y

lliic

czzn

niik

k d

dw

wó

ójjk

ko

ow

wy

y

C

CM

MO

OS

S−4

40

00

00

0

E

LEKTRONIKA DLA WSZYSTKICH 3/98

52

40373

8

8−k

krro

ottn

ny

y „

„p

prrzze

ezzrro

oc

czzy

ys

stty

y”

”

zza

attrrzza

as

sk

k

40374

8

8−k

krro

ottn

ny

y p

prrzze

errzzu

uttn

niik

k tty

yp

pu

u D

D

S

Sk

krró

ótty

y n

na

a rry

ys

su

un

nk

ka

ac

ch

h w

wy

yp

prro

ow

wa

ad

dzze

eń

ń

A, B, C, ...

Wejścia liczników, rejestrów przesuwających, dekode−

rów etc; A– najmłodszy bit (LSB)

a, b, c, ...

Wyjścia wyświetlaczy 7−segmentowych, patrz rysunek

poniżej

A0, A1, ...

Wejścia adresujące pamięć, A0 – LSB

BI

Wejścia wygaszające cyfrę

B

out

Wyjście z przeniesieniem ujemnym (pożyczką)

C

Wejście sterujące, ogólnie

CE

Sygnał wybrania układu (ang. Chip Enable)

C

in

Wejście sygnału przeniesienia

CL

Zerowanie, kasowanie

C

out

Wyjście sygnału przeniesienia

CP

Impulsy zegarowe (wejście)

D

Wejście/wyjście danych, ogólnie

D0, D1, ...

Wejścia danych, D0 – LSB

DP

Wyjście kropki dziesiętnej dekodera wyświetlacza 7−

segmentowego

E

Wejście, ogólnie

EN

Wejście uprawniające (ang. Enable) układów z wyjściem

trójstanowym

FE

Wejście uprawniające (ang. Enable Input)

FQ

Wyjście uprawniające (ang. Enable) w układach kaska−

dowych)

J, J1, J2

Wejścia J przerzutników

K, K1, K2

Wejścia K przerzutników

LT

Wejścia kontrolne w dekoderach wyświetlaczy 7−seg−

mentowych

MEM

Pamięć

MR

Zerowanie ogólne (wszystkie układy)

MUX

Multiplekser

Q

Wyjścia, ogólnie

Q0, Q1, ...

Wyjścia danych z dekoderów dziesiętnych

QA, QB, ...

Wyjścia danych., QA – LSB

R

Wejścia zerujące, ogólnie

R0

Wejście zerujące, reset (ustawia zero)

R9

Wejście zerujące, reset (ustawia dziewiątkę)

RBI

Wejście sygnału wygaszającego migotanie wyświetla−

czy 7−segmentowych

RBQ

Wyjście sygnału wygaszającego migotanie (dla układów

kaskadowych)

RD

Wejście sygnału zezwolenia na czytanie (ang. Read

Enable)

S

Wejście ustawiające, ogólnie

Strobe

Wejście sygnału wyzwalającego (strobującego)

T

Wejście sygnału zegarowego)

U

dd

Napięcie zasilania

V/R

Wejście przełączania trybów: liczenie w przód/liczenie

wstecz

W/R

Wejście przełączania trybów: zapis/odczyt

S

Sk

krró

ótty

y w

w tta

ab

be

ella

ac

ch

h s

stta

an

nó

ów

w llo

og

giic

czzn

ny

yc

ch

h

H

Stan logiczny (poziom) wysoki

L

Stan logiczny (poziom) niski

X

Stan logiczny nieokreślony (niski lub wysoki)

Z

Stan logiczny wysokiej impedancji

Przejście z L do H (zbocze narastające)

Przejście z H do L (zbocze opadające)

Impuls o niskim poziomie logicznym

nx

Ciąg n impulsów o wysokim poziomie logicznym

Q=L

Ta kolumna wskazuje wyjście o niskim poziomie;

wszyskie pozostałe wyjścia mają poziom wysoki

+

OR

•

A

ND

⊕

EX−OR

ANOT A

blank

Pusty (wyświetlacz)

counter

Licznik

data

Dane

eve, odd

Nieparzysty, parzysty

hold

Utrzymanie danych

inhibit

Zakaz

latch

Zatrzaśnięcie danych

memory

Zawartość pamięci

memory

Zanegowana zawartość pamięci

remains

Odświeżanie (wyświetlacza)

W

W k

ko

ollu

um

mn

niie

e „

„F

Fu

un

nk

kc

cjja

a”

”

–

Nie jest wykonana jakakolwiek funkcja ani zmieniany ja−

kikolwiek stan

count

Odliczanie co 1

no count

Brak odliczania

shift

Przesuwanie o 1

?

Stan lub funkcja zależy od innych parametrów i stąd nie

jest znana

reset

Zerowanie

preset

Nastawienie, najczęściej na określoną wartość, stoso−

wane do wejść równoległych

latch

Zatrzaśnięcie danych

read

Odczyt danych

write

Zapis danych

nest addres Następny adres

F

Fu

un

nk

kc

cjje

e d

dy

yn

na

am

miic

czzn

ne

e

t

n

Czas/stan poprzedzający pojawienie się impulsu zegaro−

wego

t

n+1

Czas/stan po jednym impulsie zegarowym (jeśli nie po−

dano innej definicji)

Q

n

Stan wyjścia po czasie t

n

Q

n+1

Stan wyjścia po czasie t

n+1

Q

n

Zanegowanie Q

n

Wyszukiwarka

Podobne podstrony:

Uklady scalone CMOS z serii 4000, Elektronika, Noty aplikacyjne

Układy scalone CMOS z serii 4000

Układy scalone CMOS z serii@00

laboratorium z układów logicznych komparator 3K2PVJZOBCA2ZQGNHSNH7M2IUH65NCCO5GUG55A

czesc nr 2 , Laboratorium Układów Logicznych

teoria1, Laboratorium Układów Logicznych

Modelowanie układów logicznych na elementach elektronicznych

modelowanie ukladow logicznych w oparciu o elementy elektroniczne

elementy techniki cyfrowej synteza układów logicznych 4OB6OACWS4KEY2LEMCASGMXNHXCIVHYNTDKCDUQ

czesc nr 1 , Laboratorium Układów Logicznych

cw 1 multiplekser, Laboratorium Układów Logicznych

Modelowanie układów logicznych w oparciu o elementy elektroniczne

Analiza i synteza kombinacyjnych układów logicznych, PWr W9 Energetyka stopień inż, III Semestr, Pod

Algorytmy genetyczne w projektowaniu układów logicznych 2

teoria3, Laboratorium Układów Logicznych

Weryfikacja układów logicznych

czesc nr 3 , Laboratorium Układów Logicznych

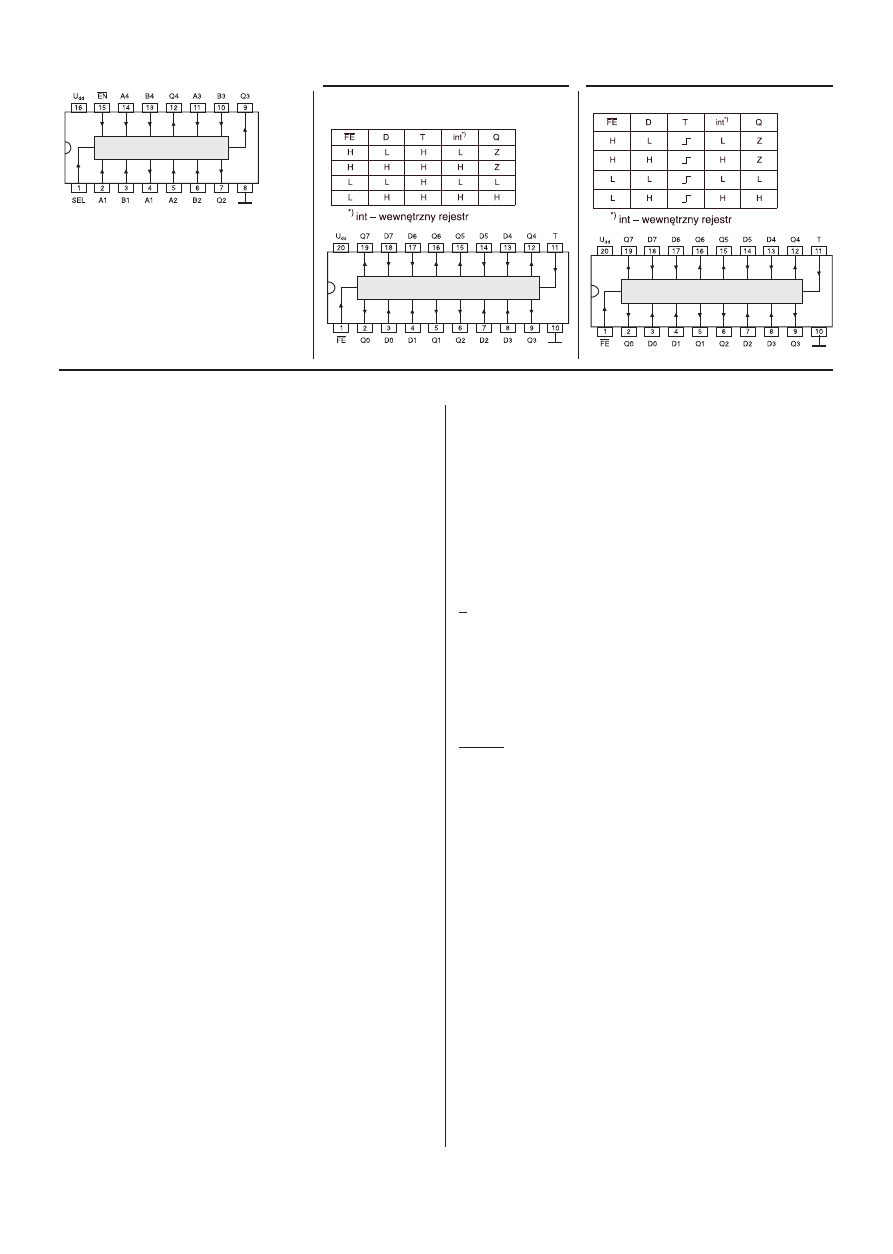

więcej podobnych podstron