Język opisu sprzętu VHDL

Materiały pomocnicze dla przedmiotu

"Technika cyfrowa i mikroprocesorowa" II/III RA

Krzysztof Kołek

Katedra Automatyki, Akademia Górniczo-Hutnicza

Al. Mickiewicza 30, 30-059 Kraków

tel. (0-12) 617-20-97

kko@ia.agh.edu.pl

- 2 -

Język opisu sprzętu VHDL

Spis treści

1. WSTĘP.................................................................................................................................................................5

2. PODSTAWOWE POJĘCIA JĘZYKA VHDL.................................................................................................6

2.1. P

REDEFINIOWANE

TYPY

........................................................................................................................................7

2.2. L

OGIKA

WIELOWARTOŚCIOWA

................................................................................................................................7

2.3. K

OMPONENTY

....................................................................................................................................................8

2.4. P

AKIETY

............................................................................................................................................................9

2.5. P

ODPROGRAMY

...................................................................................................................................................9

2.6. O

PERATORY

.....................................................................................................................................................10

2.7. S

YGNAŁY

,

ZMIENNE

,

STAŁE

................................................................................................................................11

2.8. D

EFINICJA

I

UŻYCIE

TYPÓW

.................................................................................................................................14

2.9. R

ÓWNOLEGŁE

ORAZ

SZEREGOWE

WYKONANIE

INSTRUKCJI

. K

ONCEPCJA

PROCESU

.........................................................15

2.10. Z

AWIESZANIE

WYKONANIA

PROCESU

...................................................................................................................17

2.11. I

NSTRUKCJE

WYKONYWANE

SZEREGOWO

.............................................................................................................19

2.12. C

YKL

"

DELTA

"...............................................................................................................................................21

2.13. A

TRYBUTY

....................................................................................................................................................22

2.14. P

OZOSTAŁE

CECHY

JĘZYKA

...............................................................................................................................23

2.15. P

RZEŁADOWANIE

OPERATORÓW

.........................................................................................................................23

3. STRUKTURALNY OPIS SPRZĘTU..............................................................................................................24

3.1. S

UMATOR

4-

BITOWY

. O

PIS

STRUKTURALNY

..........................................................................................................24

3.2. G

ENERATOR

NUMERÓW

GÓRNIKÓW

. P

ROJEKT

W

POSTACI

SCHEMATU

ELEKTRYCZNEGO

.................................................30

4. BEHAWIORALNY OPIS SPRZĘTU.............................................................................................................34

4.1. W

IELOKROTNE

WYWOŁANIE

PROCESU

...................................................................................................................34

4.2. D

EFINIOWANIE

REJESTRÓW

.................................................................................................................................35

4.3. C

ZTEROBITOWY

REJESTR

Z

RÓWNOLEGŁYM

ŁADOWANIEM

I

ASYNCHRONICZNYM

ZEROWANIEM

........................................37

4.4. C

ZTEROBITOWY

BINARNY

LICZNIK

ASYNCHRONICZNY

..............................................................................................38

4.5. K

ONWERTER

KODU

BCD

NA

KOD

WYŚWIETLACZA

SIEDMIOSEGMENTOWEGO

..............................................................39

4.6. M

ULTIPLEKSER

4

NA

1......................................................................................................................................39

4.7. C

ZTEROBITOWY

REJESTR

PRZESUWAJĄCY

..............................................................................................................40

4.8. C

ZTEROBITOWY

LICZNIK

SYNCHRONICZNY

Z

WEJŚCIEM

ZEZWALAJĄCYM

NA

ZLICZANIE

,

ASYNCHRONICZNYM

ZEROWANIEM

I

SYNCHRONICZNYM

ŁADOWANIEM

................................................................................................................................40

4.9. B

UFOR

TRÓJSTANOWY

........................................................................................................................................41

4.10. F

UNKCJA

KONWERSJI

TYPU

BIT

_

VECTOR

DO

TYPU

INTEGER

....................................................................................41

4.11. A

UTOMAT

O

SKOŃCZONEJ

LICZBIE

STANÓW

..........................................................................................................42

4.12. I

MPLEMENTACJA

UKŁADÓW

Z

RODZINY

TTL.......................................................................................................44

4.12.1. Implementacja układu 7400................................................................................................................44

4.12.2. Implementacja układu 74138..............................................................................................................44

5. WYKAZ FUNKCJI JĘZYKA VHDL.............................................................................................................46

5.1. A

TRYBUTY

.......................................................................................................................................................46

5.2. D

EFINICJA

TABLIC

.............................................................................................................................................47

5.3. I

NSTRUKCJA

CASE

.............................................................................................................................................48

5.4. S

CALANIE

WARTOŚCI

(

ANG

.

AGGREGATE

)..............................................................................................................49

5.5. T

YP

B

IT

..........................................................................................................................................................50

5.6. T

YP

B

IT

_V

ECTOR

............................................................................................................................................50

5.7. T

YP

B

OOLEAN

.................................................................................................................................................51

5.8. T

YP

C

HARACTER

..............................................................................................................................................51

5.9. P

AKIET

............................................................................................................................................................51

6. PRZYKŁADY....................................................................................................................................................52

6.1. K

ONWERTER

LICZBY

BINARNEJ

NA

KOD

BCD. W

YŚWIETLENIE

LICZBY

BCD

NA

WYŚWIETLACZU

7-

SEGMENTOWYM

........54

6.2. C

ZĘSTOTLIWOŚCIOMIERZ

....................................................................................................................................58

Język opisu sprzętu VHDL

- 3 -

6.3. G

ENERATOR

NUMERÓW

GÓRNIKÓW

......................................................................................................................62

6.4. G

ENERATOR

SYGNAŁU

WIZYJNEGO

DLA

MONITORA

MONOCHROMATYCZNEGO

..............................................................68

- 4 -

Język opisu sprzętu VHDL

1.

Wstęp

Język VHDL (skrót pochodzi od dwóch innych skrótów: V - Very High Speed Integrated

Circuit oraz HDL - Hardware Description Language) rozwijany był na początku lat 80-tych do

opisu niezależnych metod opisywania układów elektronicznych przez American Department

of Defence (ang. DoD). Po raz pierwszy został zestandaryzowany w roku 1983, a następnie

standaryzację powtórzono w latach 1987 oraz 1993.

Główne cechy języka VHDL to:

•

równoległość przejawiająca się w możliwości zdefiniowania potrzeby oraz

wykonywania równoległego (jednoczesnego w czasie) przetwarzania różnych porcji

informacji,

•

strukturalność oznaczająca możliwość hierarchicznego opisywania projektów. W

opisie hierarchicznym projekt zbudowany jest z połączonych bloków o mniejszym

stopniu złożoności, które z kolei zbudowane są z prostszych bloków, które

zawierają w sobie jeszcze prostsze bloki i tak dalej aż dochodzimy do bloków

podstawowych, którymi np. w przypadku układów cyfrowych są bramki logiczne.

Strukturalność oznacza możliwość opisu sprzętu od poziomu systemu do poziomu

bramki,

•

"redesign" - typowy projekt cyfrowego układu elektronicznego zawiera w sobie do

80% fragmentów z innych projektów. Nowe projekty nie powstają w pustce.

Projektanci wykorzystują poprzednio zdobyte doświadczenia przenosząc

opracowane i poznane uprzednio rozwiązania do nowych projektów. Proces ten

określa się pochodzącym z języka angielskiego słowem redesign,

•

możliwość wykonywania instrukcji sekwencyjnie (czyli w sposób przeciwstawny

do wykonywania równoległego) oznaczająca możliwość definiowania czynności

wykonywanych jedna po drugiej, w sposób analogiczny jak w tradycyjnych

językach programowania. ,

•

zdolność do jednolitego opisywania struktury układów zbudowanych w oparciu o

różne technologie stwarzająca możliwość przenoszenia projektów pomiędzy

różnymi platformami sprzętowymi,

•

możliwość symulowania projektowanych układów; możliwość tworzenia sekwencji

sygnałów testujących. Istnieje możliwość wbudowania sygnałów testowych w

projekt,

•

"samodokumentowanie" osiągnięte dzięki prostej i przejrzystej strukturze,

•

modelowanie układów z uwzględnieniem upływającego czasu.

Programowanie w języku VHDL może odbywać się na różnych poziomach abstrakcji. Są

to:

•

warstwa topograficzna (ang. layout) specyfikująca połączenia z uwzględnieniem

również zależności czasowych i efektów analogowych. Przykładowo realizuje

opóźnienia propagacji sygnału oraz blokowanie sygnałów poniżej minimalnej

zadanej szerokości,

•

warstwa logiki zawierająca informację o funkcjach, architekturze, technologii i

szczegóły zależności czasowych. Podstawowo opisuje zależności logiczne między

blokami,

Język opisu sprzętu VHDL

- 5 -

•

warstwa RTL (ang. Register Transfer Level) - zawiera opis każdego rejestru oraz

logiki między nimi. Zawiera informacje o architekturze ale nie o technologii.

Zależności czasowe nie są specyfikowane. Istotna jest tylko informacja o zegarach

taktujących,

•

warstwa behawioralna (ang. behavioural) opisująca funkcje projektu. Zawiera tak

dużo informacji o zależnościach czasowych, jak jest to niezbędne do opisaniu

funkcji projektu.

Każdy element opisywany w języku VHDL może posiadać dowolną liczbę definicji w

każdej z omówionych warstw. Umożliwia to skupienie się w różnych fazach projektu na

różnych jego aspektach.

Język przypomina języki programowania typu C lub Pascal jednak jego podstawowym

celem nie jest wykonywanie obliczeń. Zadaniem języka jest wspieranie całości procesu

projektowania układów cyfrowych poczynając od symulacji poprzez modelowanie,

testowanie, implementacje oraz tworzenie dokumentacji. Podstawowym celem języka VHDL

jest "zaprogramowanie" programowalnego układu logicznego niezależnie od technologii

w jakiej ten układ został wytworzony (ASIC, FPGA, PLD, itp.). Dotyczy to również układów

opracowywanych w przyszłości, których parametry nie są jeszcze aktualnie znane.

Podstawowym ograniczeniem języka VHDL jest, iż pierwotnie był projektowany

wyłącznie do systemów cyfrowych. Aktualnie trwają prace nad standaryzacją wersji dla

układów analogowych oraz nad opracowaniem analogowych programowalnych i

konfigurowalnych układów scalonych o podobnym stopniu elastyczności jaki osiągnęły

układy FPGA w technice cyfrowej.

Dostępne oprogramowanie wspomagające użytkowanie języka zwykle automatycznie

tworzy i optymalizuje struktura komórek i połączeń podczas programowanie

programowalnych układów logicznych. Język VHDL wydaje się być szczególnie użyteczny

dla układów FPGA o 10-20 tysiącach komórek. Narzędzia języka HVDL dla układów FPGA

kosztują od 1 do 20 tysięcy USD (w porównaniu z cenami 50-100 tysięcy USD dla układów

ASIC).

Niniejsze opracowanie przedstawia skrótowy opis struktur języka VHDL ukierunkowany

na wykorzystanie do programowania programowalnych układów logicznych firmy XILINX z

wykorzystanie firmowego oprogramowania wspomagany przez pakiet oprogramowanie

ORCAD w wersji 7.11. Należy zwrócić uwagę na występujące różnice między opisem

standardu języka VHDL oraz jego implementacją w programie ORCAD. Praktyczna

implementacja zawiera bowiem istotne ograniczenia w stosunku do ogólnej specyfikacji

języka podyktowane kłopotami w realizacji niektórych cech w oparciu o aktualną technologię.

Specyfikacja języka, będąc bardzo elastyczną, uwzględnia cechy, które aktualnie mogą być

wyłącznie symulowane w sposób programowy (nie jest możliwa ich praktyczna realizacja z

zastosowaniem okładów firmy XILINX) nie należy jednak wykluczyć ich praktycznej

realizacji w oparciu o nowe rozwiązania technologiczne.

2.

Podstawowe pojęcia języka VHDL

- 6 -

Język opisu sprzętu VHDL

Poniżej przedstawiono podstawowe pojęcia występujące w opisie języka VHDL. Należy

pamiętać, iż język VHDL został zaprojektowany jako język opisu sprzętu. Powoduje to istotne

różnice w stosunku do języków programowania ogólnego przeznaczenia. Język VHDL

wykazuje duże podobieństwa składniowe do języków typu Pascal lub C niemniej podobnie

wyglądające instrukcje mogą charakteryzować się dramatycznie odmiennym

zachowaniem. W szczególności dotyczy to zasad określania zależności czasowych oraz pracy

równoległej.

2.1.

Predefiniowane typy

Język VHDL posiada następujące predefiniowane typy danych:

•

BOOLEAN przyjmuje jedną z dwóch wartości: FALSE lub TRUE,

•

BIT jest równe '1' lub '0',

•

BIT_VECTOR ciąg wartości typu BIT np. "000000", "01101". Można użyć do

modelowania magistral,

•

CHARACTER umożliwia używanie znaków alfanumerycznych np. 'a', 'X',

•

STRING definiuje ciągi znaków np. "ABCD", "012ws"

•

INTEGER reprezentuje liczby całkowite,

•

REAL umożliwia zapis liczb zmiennopozycyjnych.

Powyższe typy powinny być zdefiniowane w pakiecie STANDARD wchodzącym w

skład języka. Definicja pewnych typów może być zależna od implementacji lub nie

występować. Dotyczy to na przykład typu REAL, który ze względu na problemy

implementacyjne nie zawsze jest dostępny.

2.2.

Logika wielowartościowa

Logika wielowartościowa posiada więcej typów niż tylko zero i jedynka logiczna.

Pakiet Std_Logic_1164 wchodzący w skład języka VHDL zawiera definicję typów std_logic

(typ "resolved") oraz std_ulogic (typ "unresolved") o następujących wartościach wraz z

operującymi na nich funkcjami:

'U'

- wartość nigdy dotychczas nie została określona,

'X'

- wartość była znana ale aktualnie nie można podać jej konkretnej wartości;

sygnał "strong drive",

'0'

- sygnał logicznego 0 typu "strong drive",

'1'

- sygnał logicznej 1 typu "strong drive",

'Z'

- stan wysokiej impedancji; sygnał nie posiada "driver"-a,

'W'

- wartość była znana ale aktualnie nie można podać jej konkretnej wartości;

sygnał "weak drive"; rzadko używany,

'L'

- sygnał logicznego 0 typu "weak drive",

'H'

- sygnał logicznej 1 typu "weak drive",

'-'

- wartość sygnału nie ma znaczenia.

Pakiet zawiera również definicje typów Std_logic_vector oraz Std_ulogic_vector.

Język opisu sprzętu VHDL

- 7 -

Pakiet Std_logic zawarty jest w bibliotece IEEE. Poniższe instrukcje czynią elementy

zdefiniowane w pakiecie Std_logic dostępnymi w projekcie:

library IEEE;

-- Uczyń bibliotekę dostępną

use IEEE.Std_Logic_1164.all; -- Całość biblioteki dostępna

Jest możliwe podstawianie elementów typu std_ulogic do std_logic i vice-versa.

2.3.

Komponenty

Opis komponentów składowych projektu wykonywany jest za pomocą dyrektywy

ENTITY opisującej sprzęg w strukturze hierarchicznej, bez definiowania zachowania. Jest

odpowiednikiem symbolu na schemacie. Przykładowy opis komponenty przedstawiony jest

poniżej.

ENTITY halfadd IS

PORT ( a,b : IN BIT;

sum, carry : OUT BIT);

END halfadd;

Blok ENTITY zawiera definicje sygnałów wejściowych i wyjściowych komponentu.

Może również zawierać definicje parametrów i stałych. Opisany blok o nazwie halfadd

posiada dwa wejścia (a oraz b) oraz dwa wyjścia (sum oraz carry). Wszystkie wejścia i

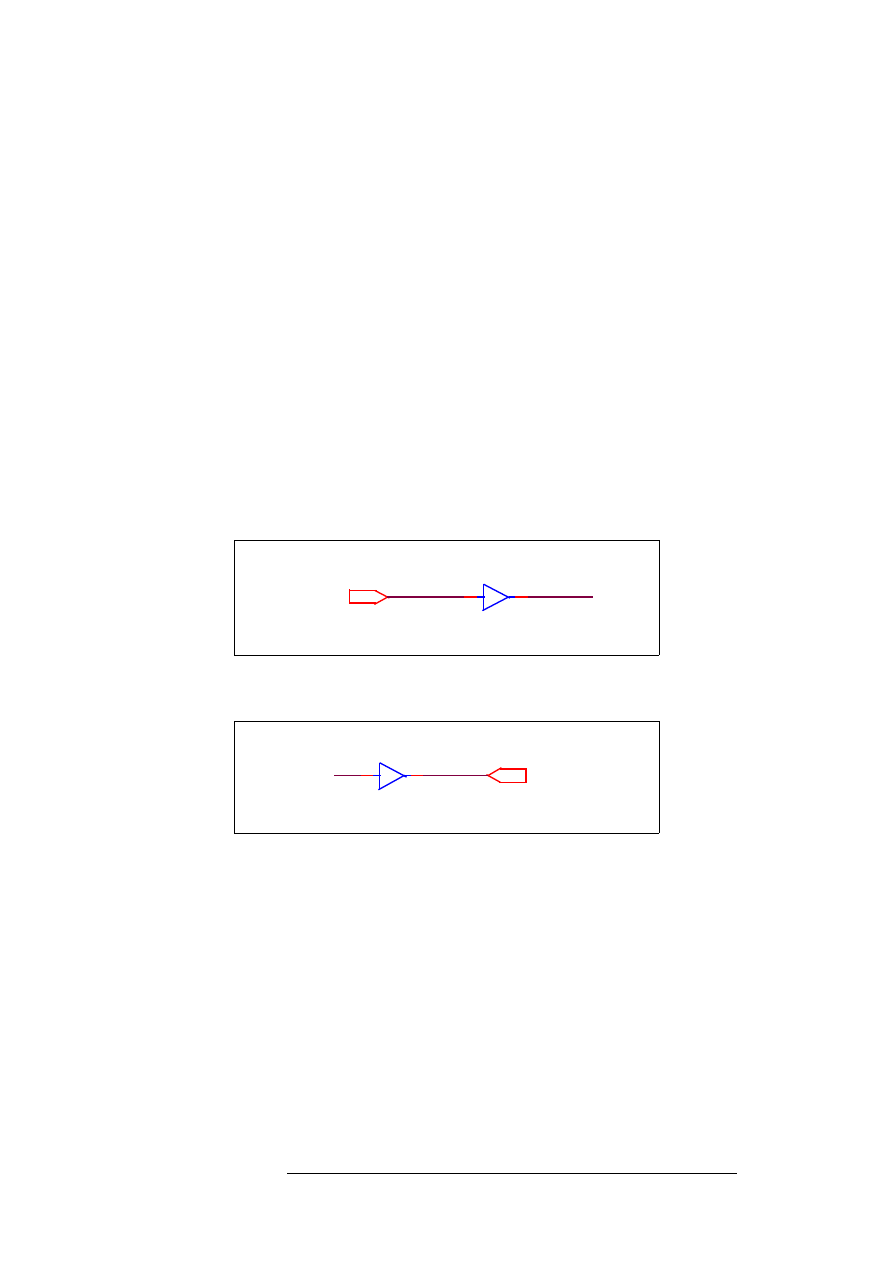

wyjścia są typu BIT. Przedstawiony powyżej przykład odpowiada następującemu blokowi:

halfadd

sum

a

b

carry

Zachowanie komponentu opisane jest w bloku ARCHITEKTURE.

ARCHITECTURE behave OF halfadd IS

BEGIN

sum <= a XOR b;

carry <= a AND b;

END behave;

Po słowie ARCHTECTURE znajduje się zdefiniowana przez użytkownika nazwa. Blok

ARCHTECTURE jest zawsze związany z blokiem ENTITY. Znaki '<=' są symbolami

przypisania nowych wartości do sygnałów. Każdy blok ENTITY może posiadać kilka,

różniących się nazwami, bloków ARCHTECTURE. Umożliwia to opisanie projektu na

różnych poziomach abstrakcji.

- 8 -

Język opisu sprzętu VHDL

2.4.

Pakiety

W języku VHDL można pogrupować komponenty oraz ich właściwości w postaci

pakietów. Pakiet jest zbiorem definicji, które mogą być dostępne przez wiele projektów w tym

samym czasie. Jest odrębną jednostką projektową w VHDL. Występuje na zewnątrz

rozważanych dotychczas jednostek (ENTITY i ARCHITECTURE). Może zawierać definicje

stałych, typy definiowane przez użytkownika, deklaracje komponentów oraz podprogramy

VHDL, które są dzielone pomiędzy różne projekty.

Pakiety definiuje się za pomocą dyrektywy PACKAGE.

Przykładowym pakietem jest Std_Logic_1164 zawierający między innymi definicje

podstawowych typów.

2.5.

Podprogramy

Język VHDL umożliwia definicję zarówno funkcji jak i procedur, które ogólnie zwane są

podprogramami. Przykładem działania funkcji jest transkodowanie, czyli zmiana zapisu

liczby w jednym kodzie na inny (patrz przykład poniżej). Taka sama operacja może zostać

zrealizowana za pomocą procedury (patrz drugi przykład). Różnica polega na zwracane

wartości: procedura nie zwraca żadnej wartości i w związku z tym nie może zostać użyta np.

w instrukcjach przypisania podczas gdy funkcja zwraca wartość określonego typu.

Ewentualne wartości modyfikowane przez procedurę muszą zostać zadeklarowane na jej liście

argumentów jako wyjściowe lub wejściowo/wyjściowe (out lub inout).

function Transcod(Value: in bit_vector(0 to 7)) return bit_vector is

begin

case Value is

when "00000000" => return "01010101";

when "01010101" => return "00000000";

when others => return "11111111";

end case;

end Transcod;

procedure Transcoder_1 (variable Value: inout bit_vector (0 to 7)) is

begin

case Value is

when "00000000" => Value:="01010101";

when "01010101" => Value:="00000000";

when others => Value:="11111111";

end case;

end procedure Transcoder_1;

Język opisu sprzętu VHDL

- 9 -

2.6.

Operatory

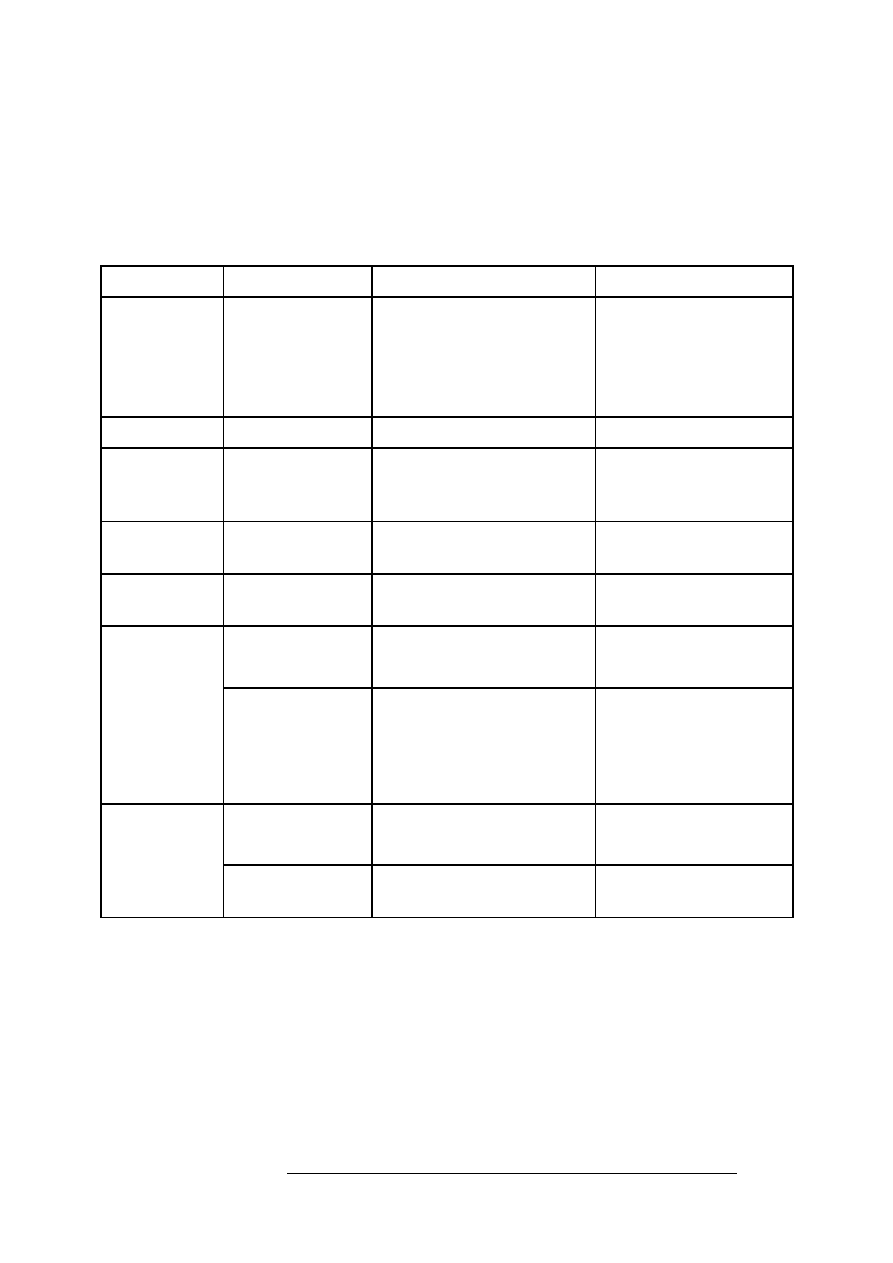

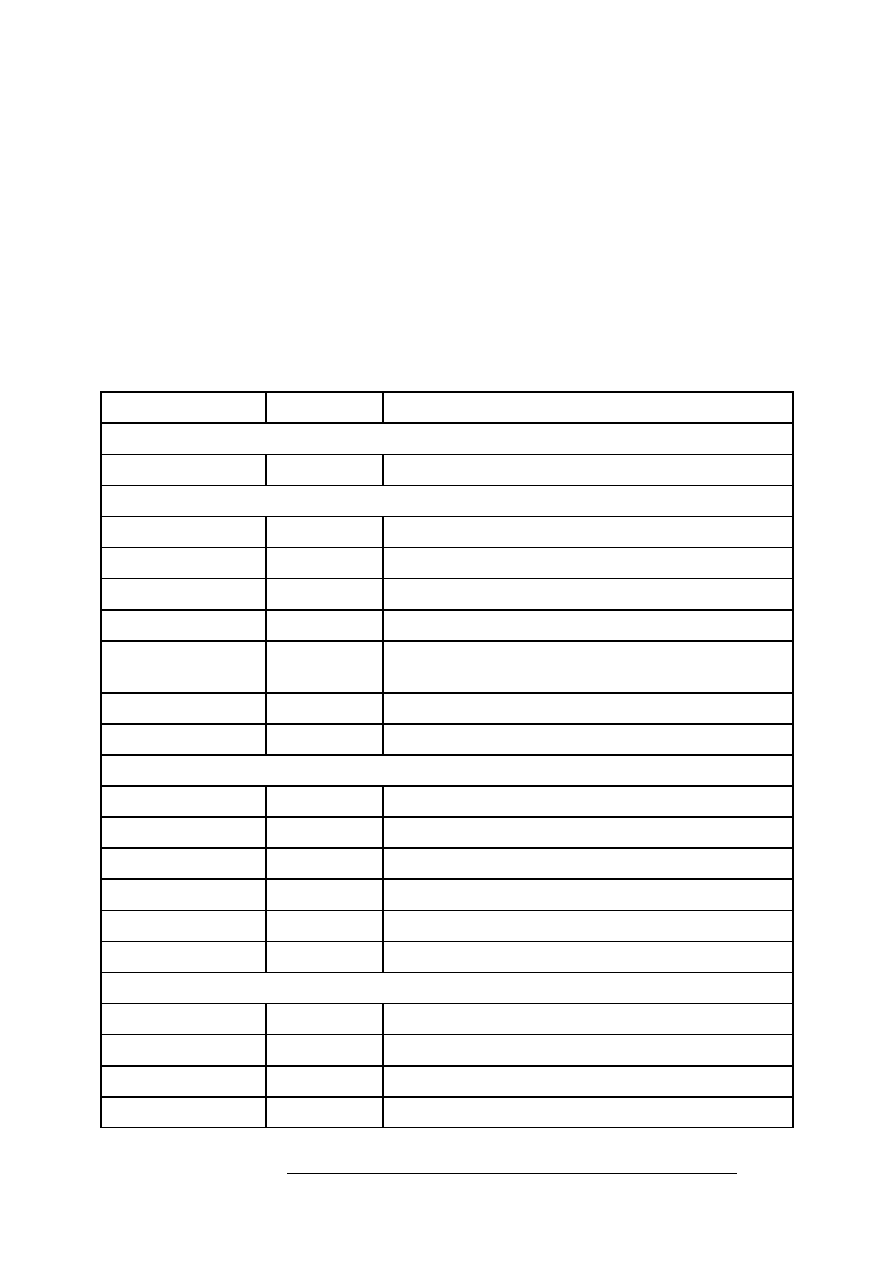

Operatory dostępne w języku VHDL przedstawia poniższa tabela. Przedstawione

operatory działają na standardowych typach wbudowanych w język. Mogą zostać niezależnie

zdefiniowane dla typów definiowanych przez użytkownika.

Operator

Typy operandów

Typ wyniku

Logiczne

AND, OR, NAND,

NOR,

XOR,

XNOR, NOT

BIT lub BOOLEAN

(BIT_VECTOR, STD_LOGIC,

STD_LOGIC_VECTOR,

STD_ULOGIC,

STD_ULOGIC_VECTOR)

BIT lub BOOLEAN

(BIT_VECTOR,

STD_LOGIC,

STD_LOGIC_VECTOR,

STD_ULOGIC,

STD_ULOGIC_VECTOR)

Porównań

=, /=, <, <=, >, >= Wszystkie typu

BOOLEAN

Przesunięć

SLL, SRL, SLA,

SRA, ROL, ROR

Lewostronny: BIT lub

wektor

BOOLEAN;

prawostronny: INTEGER

BOOLEAN

Dodawania

+, -, &

Tablica numeryczna lub

element tablicy

Tego samego typu jak

operandy

Znak

+, -

Numeryczny

Tego samego typu jak

operandy

Mnożenia

*, /

INTEGER, REAL

Tego samego typu jak

operandy

MOD,

REM

(reszta z dzielenia,

różnie działają w

zależności

od

znaku operandu)

INTEGER

Tego samego typu jak

operandy

Inne

ABS

Numeryczny

Tego samego typu jak

operandy

** (potęgowanie) Lewostronny: numeryczny;

prawostronny: INTEGER

Tego samego typu jak

lewostronny operand

Spośród operatorów logicznych wszystkie oprócz NOT posiadają identyczny priorytet.

Operator NOT posiada priorytet wyższy od pozostałych operatorów logicznych.

Dla argumentów typu tablicowego argumenty są wyrównywane w lewo i porównywane.

Powoduje to, że '111' jest większe od '1011'. Oznacza to, że z wektorem nie jest związana

żadna wartość numeryczne. To tylko zbiór elementów tego samego typu.

Podstawowo operatory arytmetyczne zdefiniowane są dla typów integer, real oraz time.

Wykonywanie operacji arytmetycznych dla typów takich jak np. std_logic wymaga

- 10 -

Język opisu sprzętu VHDL

zdefiniowania funkcji definiujących operatory dla takich typów. Jest to możliwe ponieważ

język VHDL umożliwia definiowanie znaczenia operatorów.

Dla operatorów arytmetycznych można wyspecyfikować zakres argumentów i wyniku:

entity ADD is

port(A, B : in integer range 0 to 7;

Z : out integer range 0 to 15);

end ADD;

architecture ARITHMETIC of ADD is

begin

Z <= A + B;

end ARITHMETIC;

Zmienne typu time można mnożyć i dzielić zarówno przez integer jak i real:

signal CLK : std_ulogic;

constant PERIOD : time := 50 ns;

wait for 5 * PERIOD;

wait for PERIOD * 1.5;

CLK <= not CLK after PERIOD/2;

2.7.

Sygnały, zmienne, stałe

Właściwe rozumienie cech oraz zasad użycia sygnałów oraz

zmiennych jest najbardziej istotną cechą języka VHDL.

Sygnały w języku VHDL służą do reprezentacji rzeczywistych połączeń między

elementami projektu. Odpowiadają więc połączeniom pojedynczym lub magistralom. Z

sygnałami związane są opóźnienie w związku z propagacją sygnału oraz zdolność tłumienia

sygnałów o czasie trwania krótszym od zadanego. Operatorem przypisania w stosunku do

sygnałów jest '<='. Przykładowo instrukcja:

z <= a;

powoduje przypisanie do sygnały z wartości sygnału a.

Każdy sygnał ma z sobą związany wzmacniacz będący źródłem wartości sygnału.

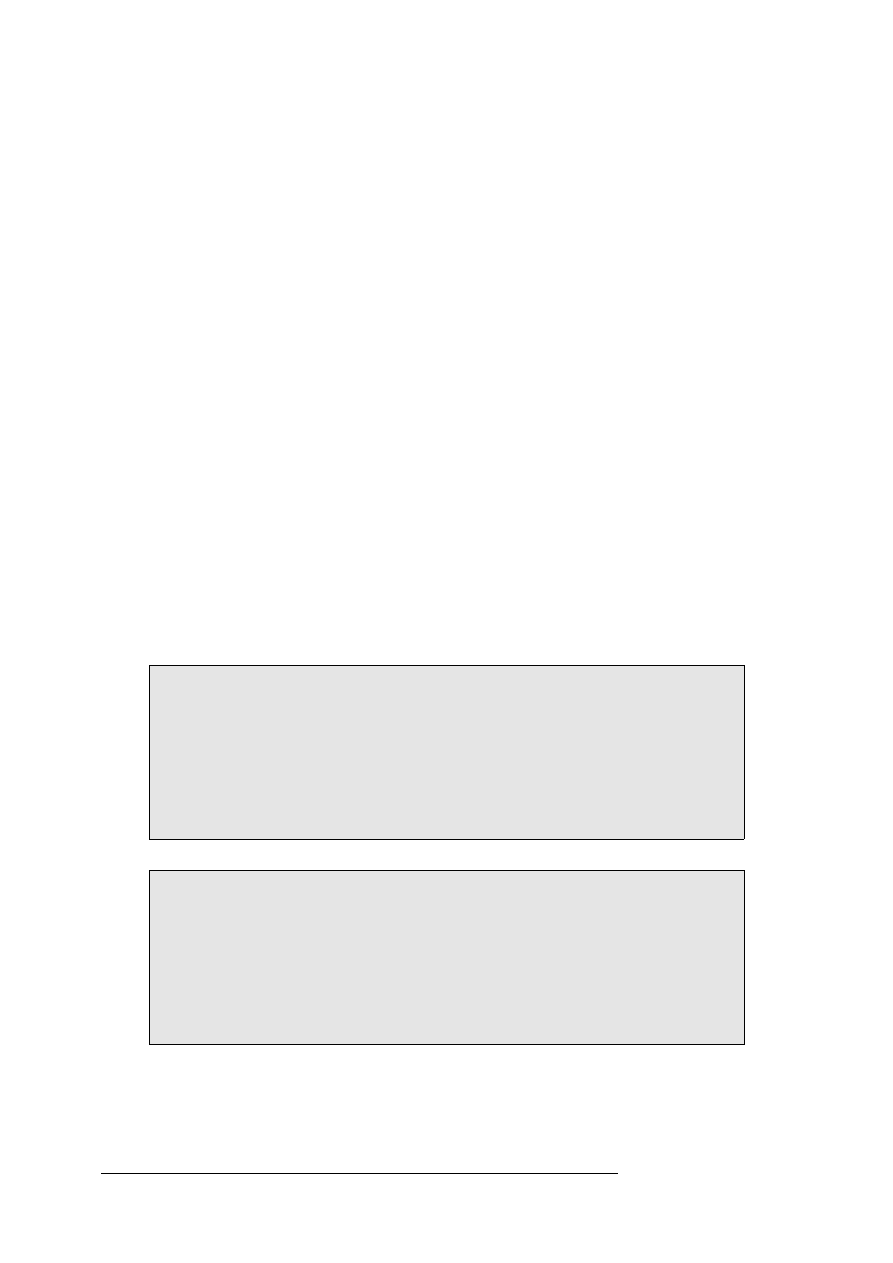

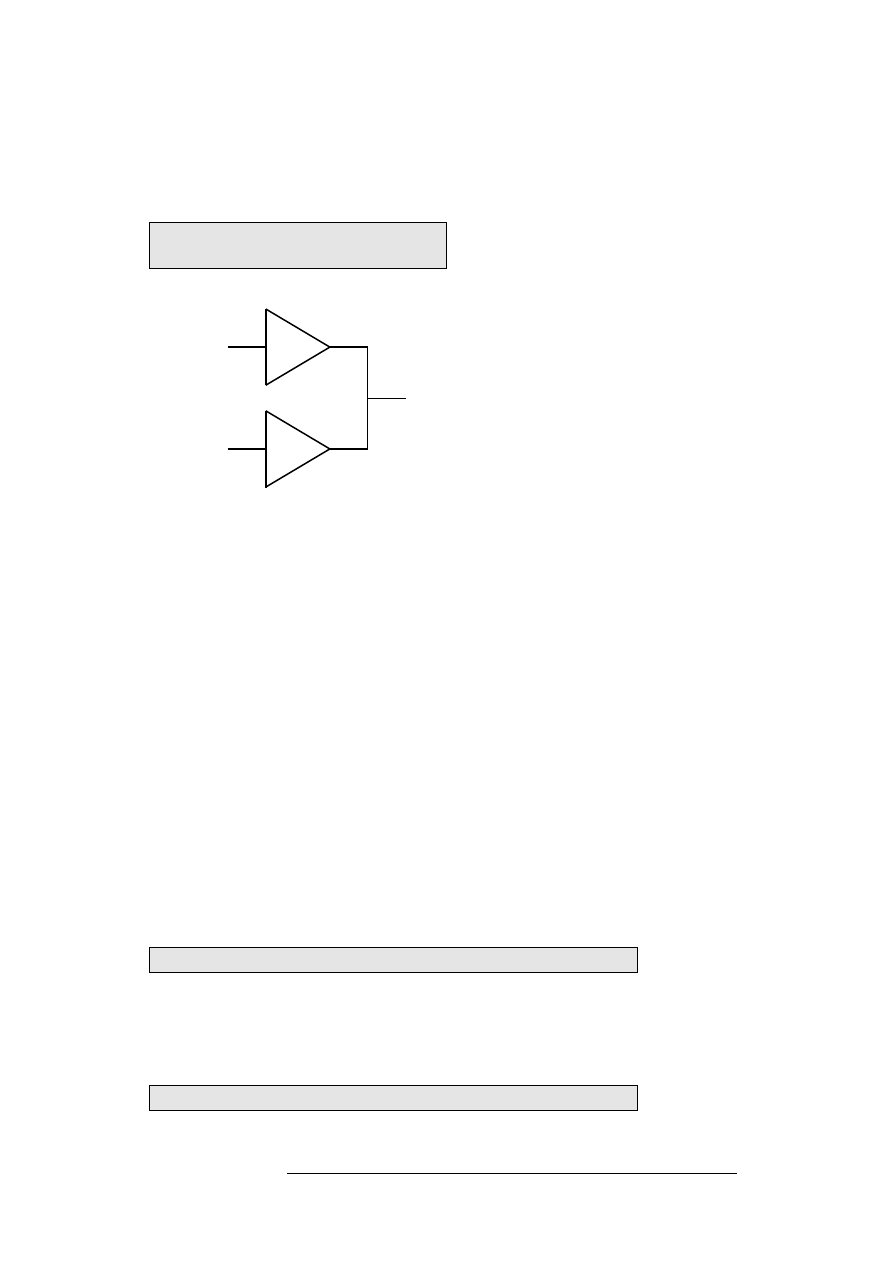

Przedstawione powyżej podstawienie odpowiada sytuacji:

z

a

Język opisu sprzętu VHDL

- 11 -

Podstawienie wartości do sygnału oznacza w rzeczywistości ustawienie wartości

wyjściowej ze wzmacniacza. Jeżeli występuje więcej niż jedno podstawienie do sygnału

wówczas odpowiada to sytuacji gdy pojedynczy sygnał ma kilka związanych z nim

wzmacniaczy. Pamiętając iż instrukcje mogą wykonywać się w sposób równoległy poniższy

ciąg podstawień:

z <= a;

z <= b;

odpowiada sytuacji

z

a

b

Takie rozwiązanie jest zwykle niedopuszczalne. Wielokrotne podstawienie wartości do

sygnału powoduje utworzenie wielu wzmacniaczy będących źródłem wartości sygnału.

Jedynym przypadkiem dopuszczalności, a nawet dużej użyteczności takiego rozwiązania, jest

zdefiniowanie sygnału z jako typu resolved. Oznacza to związanie z sygnałem z specjalnej

funkcji, która określa jaka jest wartość sygnału w przypadku gdy jest on sterowany z dwóch

wzmacniaczy.

W przypadku wielokrotnego podstawiania wartości do tego samego sygnału

wykonywanego sekwencyjnie wykona się wyłącznie ostatnie podstawienie. Każde

sekwencyjnie podstawienie wartości do sygnału "anuluje" poprzednie sekwencyjne

podstawienia. Wszystkie takie podstawienia wpływają na wyjście tego samego wzmacniacza

sygnału.

Podstawienia do sygnału w różnych sekwencyjnych fragmentach programu wykonywane

jest równolegle i produkuje wielokrotne wzmacniacze dla podstawianego sygnału. W takim

przypadku niezbędnym jest zdefiniowanie funkcji określającej wartość sygnału.

Przypisując wartość do sygnału można określić uzależnienia czasowe związane z taką

operacją. Przypisania sygnałów mogą posiadać zdefiniowane opóźnienia typu inertial lub

transport. Dodatkowo opóźnienie typu inertial może posiadac wyspecyfikowany parametr

reject.

Podstawienie do zmiennej wykonywane jest za pomocą operatora <=. Instrukcja:

z <= a AFTER 5 NS;

powoduje przypisanie wartości sygnału a do sygnału z po 5 nanosekundach. Dodatkowo

impulsy o długości poniżej 5 nanosekund pojawiające się w sygnale a nie powodują zmian

wartości sygnału z.

Podstawienie

z <= REJECT 3 NS INERTIAL a AFTER 5 NS;

- 12 -

Język opisu sprzętu VHDL

wprowadza opóźnienie 5 nanosekund i wycina impulsy o długości poniżej 3 nanosekund.

Odpowiada to linii sygnałowej o zadanym opóźnieniu i ograniczonym paśmie.

Podstawienie

z <= TRANSPORT a AFTER 5 NS;

powoduje opóźnienie sygnału o 5 nanosekund. Dowolnie krótki impuls jest przenoszony.

Odpowiada to linii o nieskończonym widmie i może np. posłużyć do modelowania linii

opóźniających.

Podstawienie

z <= '1' AFTER 3 NS, '0' AFTER 7 NS, '1' AFTER 17 NS;

tworzy falę 1->0->1 zmieniającą wartości w chwilach czasu 3 ns, 7 ns oraz 17 ns.

Wszystkie podstawienia sygnałów wewnątrz bloku

ARCHITECTURE wykonywane są w sposób równoległy.

Zmienne służą do zapamiętywania wartości chwilowych i w odróżnieniu od sygnałów nie

mają bezpośredniego odniesienia w sprzęcie. Zmienne języka VHDL mogą być używane w

sposób podobny do zmiennych klasycznych języków programowania.

Operatorem przypisania dla zmiennych jest ':='. Przykładowo:

z := a;

Stałe służą do deklaracji wartości określonych typów.

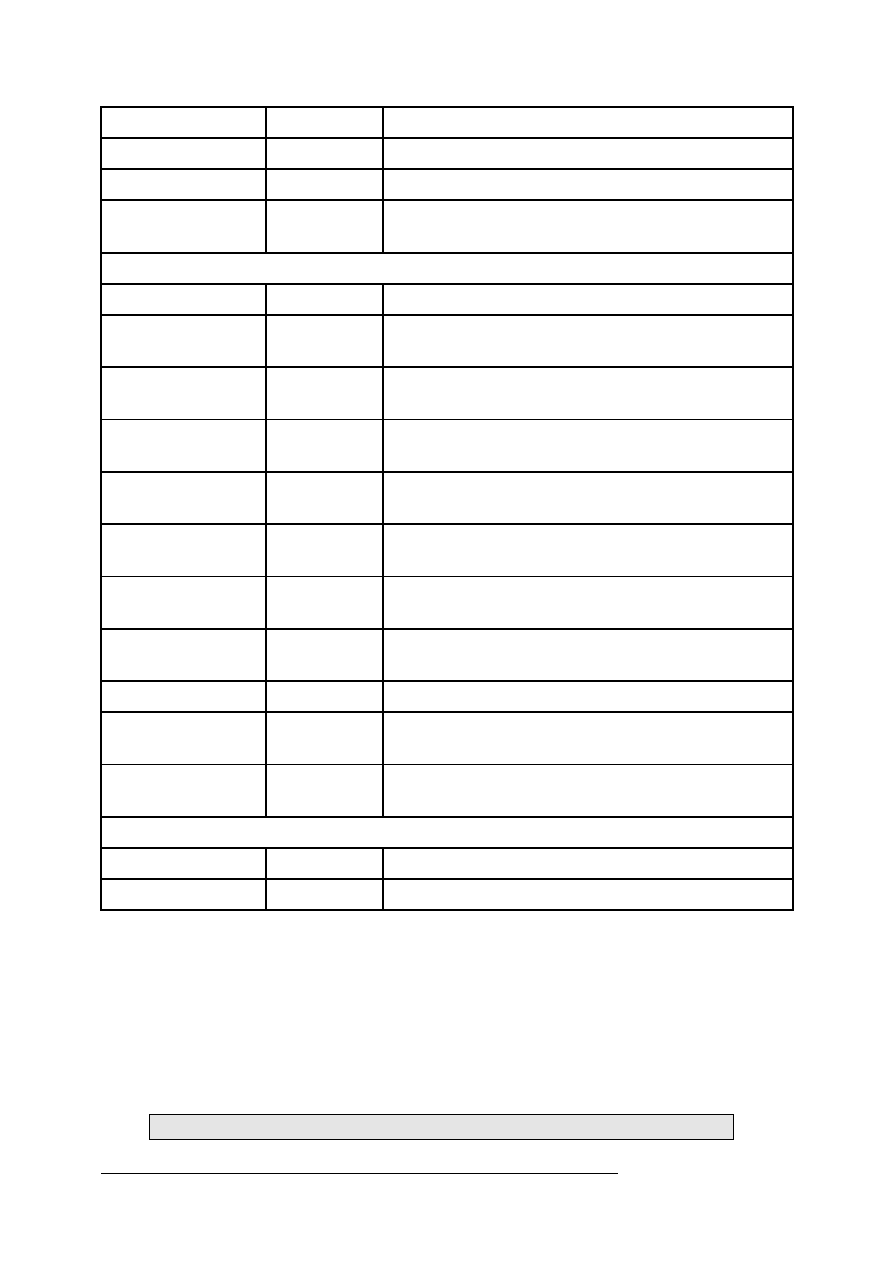

Zasady deklarowania, przypisywania i używania sygnałów, zmiennych oraz stałych zależą

od tego czy wykonywane są w sekwencyjnej czy w równoległej części programu VHDL.

Odpowiednie zasady przedstawia poniższa tabela.

Instrukcje wykonywane równolegle

Instrukcje wykonywane szeregowo

Deklaracja Przypisanie

Użycie

Deklaracja Przypisanie

Użycie

Sygnał

TAK

TAK

TAK

NIE

TAK

TAK

Zmienna

NIE

NIE

TAK

TAK

TAK

TAK

Stała

TAK

---

TAK

TAK

---

TAK

Zmienne zachowują swoją wartość między wywołaniami procesu.

Język opisu sprzętu VHDL

- 13 -

Jest możliwe podstawianie sygnałów do zmiennych i odwrotnie choć ciągle

obowiązuje zasada zgodności typów.

Zakresem ważności zmiennych jest TYLKO proces wewnątrz którego są zdefiniowane.

Aby ich wartości wysłać na zewnątrz procesu należy je przypisać do sygnałów.

Obiekty typu variable są zmieniane natychmiast, są więc używane do przechowywania

zmiennych tymczasowych posiadających wpływ na wykonanie procesu. Typowo, wejściowe

sygnały przypisujemy do zmiennych (variable), wykonujemy są wszelkie obliczenia, a ich

wyniki przypisujemy do sygnałów wyjściowych.

2.8.

Definicja i użycie typów

W języku VHDL występują typy definiowane przez użytkownika. Mają one charakter

typu wyliczeniowego. Typy definiuje się wewnątrz bloków typu package, architecture lub

process.

Przykładowa definicja typu wygląda w sposób następujący:

type MY_STATE is (RESET, IDLE, RW_CYCLE, INT_CYCLE);

...

signal STATE : MY_STATE;

...

STATE <= RESET;

Do sygnału danego typu można przypisać tylko wartość tego typu.

Zwykle elementy typów kodowane są na najmniejszej licznie bitów niezbędnych do

zakodowania wszystkich elementów typu choć sposób kodowania zależy od implementacji

języka.

Obiekty można przypisywać jeżeli są tego samego typu i tego samego rozmiaru:

signal Z_BUS:bit_vector(3 downto 0);

signal C_BUS:bit_vector(1 to 4);

Z_BUS <= C_BUS;

Z_BUS(3 downto 2) <= "00";

C_BUS(2 to 4) <= Z_BUS(3 downto 1);

Konkatenacja sygnałów w magistrale wykonywana jest za pomocą operatora &.

Agregacja sygnałów również tworzy magistrale, ale jest przeprowadzana poprzez objęcie

nawiasami oddzielonych przecinkiem elementów składowych:

signal Z_BUS : bit_vector(3 downto 0);

signal A, B, C, D : bit;

signal BYTE : bit_vector(7 downto 0);

- 14 -

Język opisu sprzętu VHDL

Z_BUS <= A & B & C & D;

BYTE <= Z_BUS & Z_BUS;

Z_BUS <= (A, B, C, D);

-- equivalent to:

Z_BUS(3) <= A;

Z_BUS(2) <= B;

Z_BUS(1) <= C;

Z_BUS(0) <= D;

Specyfikacja pozycji może nastąpić przez wpis wartości na odpowiedniej pozycji

pozycję lub poprzez podanie indeksu:

X <= (3=>'1', 1 downto 0=>'1', 2 => B);

Operator others umożliwia przypisanie wartości do niezdefiniowanych elementów:

X <= (3=>'1', 1=>'0', others => B);

Każdy sygnał, zmienna i stała muszą mieć określony typ.

2.9.

Równoległe oraz szeregowe wykonanie instrukcji. Koncepcja

procesu

Równoległe (ang. conrurrent) wykonywane instrukcji odbywa się wewnątrz architektury,

jednak na zewnątrz zdefiniowanych wewnątrz architektury procesów. Instrukcje wykonują się

równolegle w tym samym czasie. Zachowanie instrukcji wykonywanych równolegle nie

zależy od kolejności w jakiej są zapisane. Np. instrukcje:

X <= A + B;

Z <= C + X;

oraz instrukcje:

Z <= C + X;

X <= A + B;

dają TEN SAM REZULTAT. Rezultat obu operacji służy do policzenia wartości sygnału Z.

Najlepiej widać to na poniższym schemacie przedstawiającym przepływ danych:

Język opisu sprzętu VHDL

- 15 -

+

+

Z

C

X

B

A

Pewne instrukcje mogą nie mieć sensu wówczas gdy wykonywane są szeregowo. Np.

X <= X + A;

opisuje sumator bez dodatkowego rejestru. Jest to więc logika kombinacyjna i jej realizacja

sprzętowa wymagałaby następującej struktury:

+

X

X

A

Utworzona pętla algebraiczna uniemożliwia obliczenie wartości sygnału X.

Podczas pisanie programu w języku VHDL należy myśleć w

sposób "zorientowany na sprzęt".

Instrukcje wykonują się sekwencyjnie wówczas gdy zostaną umieszczone wewnątrz

procesu. Przykładowy proces przedstawiono poniżej:

MUX: process (A, B, SEL)

begin

if SEL = '1' then

Z <= A;

else

Z <= B;

end if;

end process MUX;

Ciało procesu zdefiniowane jest między słowami kluczowymi process oraz end process.

MUX jest opcjonalną nazwą procesu. Po słowie process znajduje się lista inicjalizacyjna.

Umieszczenie sygnału w liście inicjalizacyjnej powoduje, że proces będzie podlegał

wykonaniu gdy zmieni się stan dowolnego sygnału z listy. W przeciwnym przypadku ciało

procesu nie jest wykonywane. Typowo wewnątrz procesu zmieniane są wartości sygnałów.

Jeżeli takie sygnały znajdują się na listach inicjalizacyjnych innych procesów jest to sposobem

na "wywoływanie" jednych procesów przez inne.

Rozważmy przykład procesu realizującego funkcję multipleksera przedstawiony

powyżej. Jeżeli sygnał SEL zostanie usunięty z listy inicjalizacyjnej wówczas zmiana sygnału

- 16 -

Język opisu sprzętu VHDL

SEL nie spowoduje zmiany wartości sygnału Z. Tylko zmiany A i B są w stanie wpłynąć na Z.

Nie pracuje to wówczas jako poprawny multiplekser. Lista inicjalizacyjna powinna

ZAWSZE być KOMPLETNA.

Instrukcje wewnątrz procesu wykonywane są sekwencyjnie - "jedna po drugiej".

Definicja procesu musi znajdować się w ciele architektury. Wewnątrz architektury może

znajdować się dowolna liczba procesów:

architecture A of E is

begin

-- concurrent statements

P1 : process

begin

-- sequential statements

end process P1;

-- concurrent statements

P2 : process

begin

-- sequential statements

end process P2;

-- concurrent statements

end A;

Instrukcje wewnątrz procesów wykonywane są sekwencyjnie, ale procesy wykonują się w

sposób równoległy. Oprócz procesów architektura może zawierać inne wykonywane

równolegle instrukcje.

Sygnały zmieniane wewnątrz procesu uzyskują nową wartość dopiero po

zakończeniu procesu. Zapobiega to podstawianiu wartości tymczasowych podczas

wykorzystywania sygnałów po lewej stronie znaku przypisania. Jeżeli zachodzi potrzeba

wykorzystania wartości tymczasowych należy używać zmiennych. Zmienne, w odróżnieniu od

sygnałów, zmieniają swoje wartości natychmiast, bez oczekiwania na zakończenie procesu.

Te same instrukcje mogą posiadać różne znaczenie w zależności od tego czy są

wykonywane wewnątrz czy na zewnątrz procesu.

2.10. Zawieszanie wykonania procesu

Zawieszanie wykonania procesu oznacza wstrzymanie jego wykonania na określony

czas lub do czasu zmiany wartości określonych sygnałów.

Występują dwa style zawieszania wykonania procesu w oczekiwaniu na zmiany

sygnałów. Pierwszy wykorzystuje listę inicjalizacyjną:

process (A,B)

begin

if (A='1' or B='1') then

Język opisu sprzętu VHDL

- 17 -

Z <= '1';

else

Z <= '0';

end if;

end process;

Proces podlega wykonaniu tylko wówczas gdy zmianie ulegnie któryś z sygnałów z listy

inicjalizacyjnej po czym zatrzymuje się na końcu. Przedstawiony powyżej przykład jest

równoważny:

process

begin

if (A='1' or B='1') then

Z <= '1';

else

Z <= '0';

end if;

wait on A, B;

end process;

Zdefiniowany proces nie ma listy inicjalizacyjnej. Instrukcja wait on w sposób jawny

specyfikuje sygnały, których zmiana "odwiesi" proces. Proces zatrzymuje się na końcu i

wznawia wykonanie gdy sygnał A lub B zmienią swoją wartość. Proces posiadający listę

aktywacyjną nie może posiadać instrukcji wait.

Występuje kilka odmian instrukcji wait. Pierwsza z nich wstrzymuje wykonanie

procesu na pewien okres czasu:

STIMULUS: process

begin

SEL <= '0';

BUS_B <= "0000";

BUS_A <= "1111";

wait for 10 ns;

SEL <= '1';

wait for 10 ns;

-- etc, etc

end process STIMULUS;

proces wznawia wykonanie po określonym w instrukcji wait for czasie.

Instrukcja wait on wstrzymuje wykonanie w oczekiwaniu na zmianę wartości

sygnałów (zdarzenie zachodzące na sygnałach) wyspecyfikowanych w liście.

W poniższym przykładzie

process

begin

wait until CLK='1';

Q <= D;

- 18 -

Język opisu sprzętu VHDL

end process;

instrukcja wait until czeka na zdarzenie na sygnale na moment gdy warunek jest prawdziwy.

Gdy sygnał zmieni swoją wartość i dodatkowo spełniony jest warunek wykonanie procesu jest

wznawiane.

Instrukcja wait wstrzymuje proces na zawsze. W przedstawionym poniżej przykładzie

proces wykona się wyłącznie raz. Po wykonaniu instrukcji wait proces nie zostanie nigdy

wznowiony:

STIMULUS: process

begin

SEL <= '0';

BUS_B <= "0000";

BUS_A <= "1111";

wait for 10 ns;

SEL <= '1';

wait;

end process STIMULUS;

2.11. Instrukcje wykonywane szeregowo

Instrukcje for (instrukcja pętli z licznikiem), case (instrukcja wyboru jednej z kilku

możliwości) oraz if (instrukcja rozgałęzienia) mogą być wykonywane WYŁĄCZNIE

SEKWENCYJNIE. Oznacza to, że muszą znajdować się wewnątrz procesu.

Najprostsza forma instrukcji if umożliwiająca warunkowe wykonanie grupy instrukcji

ma następującą postać:

if CONDITION then

-- sequential statements

end if;

W celu wykonania jednej z dwóch grup instrukcji należy wykorzystać instrukcję if w postaci:

if CONDITION then

-- sequential statements

else

-- sequential statements

end if;

Wykonanie jednej z kilku grup instrukcji możliwe jest dzięki instrukcji if w postaci:

if CONDITION1 then

-- sequential statements

elsif CONDITION2 then

-- sequential statements

Język opisu sprzętu VHDL

- 19 -

elsif CONDITION3 then

-- sequential statements

else

-- sequential statements

end if;

Tylko pierwszy z warunków posiadający wartość logiczną prawdy służy do wyboru instrukcji

podlegającej wykonaniu (w if może być więcej niż jeden prawdziwy warunek jak w

przykładzie poniżej). Oznacza to występowanie wbudowanego priorytetu występującego

dzięki wyborowi kolejności warunków instrukcji if.

process (A, B, C, X)

begin

if (X = "0000") then

Z <= A;

elsif (X <= "0101") then

Z <= B;

else

Z <= C;

end if;

end process;

Instrukcja case testuje wartość obiektu a następnie wykonuje jedną z grup instrukcji

zależnie od aktualnej wartości obiektu. Ogólny format instrukcji wygląda w sposób

następujący:

case OBJECT is

when VALUE_1 =>

-- statements

when VALUE_2 =>

-- statements

when VALUE_3 =>

--statements

--etc...

end case;

W instrukcji case każda możliwa wartość obiektu MUSI ZOSTAĆ WYSPECYFIOWANA

i musi być wyspecyfikowana TYLKO JEDEN RAZ. Przykład instrukcji case przedstawiono

poniżej:

process (A, B, C, X)

begin

case X is

when 0 to 4 =>

Z <= B;

when 5 =>

- 20 -

Język opisu sprzętu VHDL

Z <= C;

when 7 | 9 =>

Z <= A;

when others =>

Z <= 0;

end case;

end process;

Ogólny format pętli z licznikiem for ma postać:

for I in 0 to 3 loop

-- statements

end loop;

Powoduje iteracyjne wykonanie ciała pętli dla wyspecyfikowanej wartości licznika pętli. Nie

ma potrzeby oddzielnego definiowania licznika pętli. Przykład użycia pętli for przedstawiono

poniżej:

entity EX is

port (A : in std_ulogic_vector(0 to 15);

SEL : in integer range 0 to 15;

Z : out std_ulogic);

end EX;

architecture RTL of EX is

begin

WHAT: process (A, SEL)

begin

for I in 0 to 15 loop

if SEL = I then

Z <= A(I);

end if;

end loop;

end process WHAT;

end RTL;

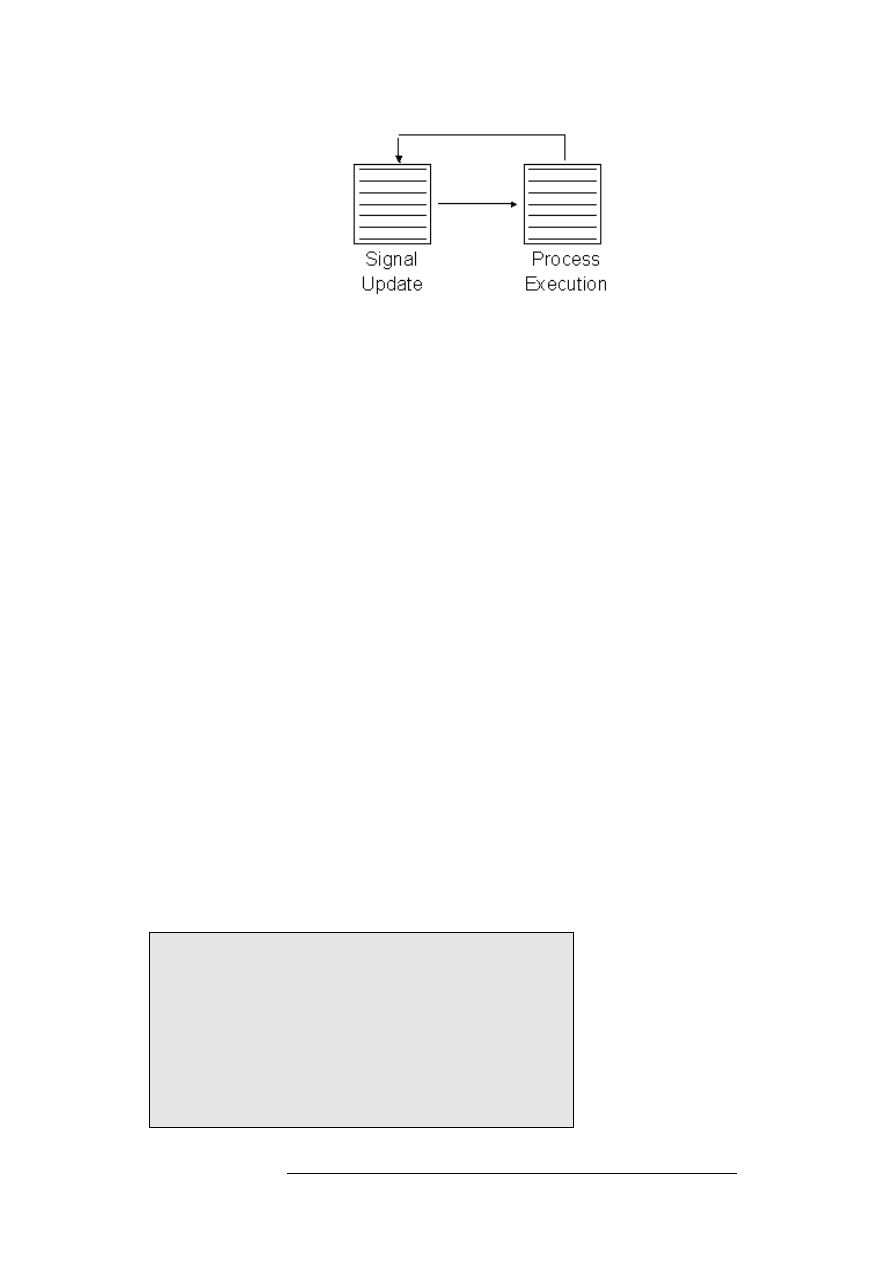

2.12. Cykl "delta"

W każdej chwili czasu podczas wykonywania programu w języku VHDL występują

dwie kolejki:

•

sygnałów do zmiany oraz

•

procesów do wykonania

Język opisu sprzętu VHDL

- 21 -

Pierwsza zawiera listę sygnałów, do których przypisano nowe wartości w procesie i

które czekają na aktualizacje po zakończeniu procesu. Druga zawiera listę procesów, które

czekają na wykonanie w związku ze zmianą wartości sygnałów na ich listach aktywacyjnych.

Jeżeli sygnał jest zmieniany to wszystkie procesy, które posiadają go w liście

aktywacyjnej umieszczane są w kolejce procesów do wykonania. Z kolei każdy proces jest

wykonywany, a uaktualniane sygnały nie są zmieniane natychmiast lecz umieszczane w

kolejce sygnałów do zmiany. Po wykonaniu wszystkich procesów sygnały są uaktualniane.

Jako wynik zmian sygnałów inne procesy mogą zostać umieszczone w kolejce procesów.

Takie cykle przeplatają się wzajemnie

Jeden taki cykl jest zwany cyklem delta.

Wiele cykli delta może być wykonywanych w tym samym czasie symulacji

(wykonania). Wykonanie w danym czasie kończy się wówczas gdy kolejki sygnałów do

zmiany i procesów do wykonania są puste. Następnie przechodzi się do następnego kroku

symulacji/wykonania.

2.13. Atrybuty

Zmienne, funkcje, typy, sygnały oraz stałe posiadają związane z nimi atrybuty, które

ułatwiają programowanie. W rozdziale xxxx zawarto opis wybranych atrybutów. Do atrybutu

odwołuje się zapisując po nazwie obiektu apostrof i podając nazwę atrybutu. Przykładowo,

zapis A'Event oznacza atrybut, który staje się prawdą wówczas gdy nastąpiła zmiana wartości

sygnału A (zdarzenie na sygnale A). Poniżej przedstawiono przykład wykorzystania atrybutów

do liczenia parzystości sygnału o dowolnym rozmiarze.

process (A)

variable TMP : std_ulogic;

begin

TMP := '0';

for I in A'low to A'high loop

TMP := TMP xor A(I);

end loop;

ODD <= TMP;

end process;

- 22 -

Język opisu sprzętu VHDL

Atrybuty A'low oraz A'high oznaczają odpowiednio najniższy i najwyższy indeks

sygnału A.

2.14. Pozostałe cechy języka

Język VHDL nie interpretuje wielkości liter. Elementy języka posiadają takie samo

znaczenie niezależnie od tego czy pisane są małymi czy dużymi literami.

Znakiem komentarze jest podwójny ciąg znaków minus: '--'. Pojawienie się tego ciągu w

programie powoduje, że pozostała część linii programu traktowana jest jako komentarz.

Typowym rozszerzeniem plików zawierających programy w języku VHDL jest vhd.

Kompilatory języka na podstawie plików źródłowych tworzą pliki binarne, które mogą służyć

do symulacji lub programowania układów programowalnych. Najmniejsza kompilowalna

jednostka nosi nazwę projektu.

VHDL traktuje wektor jako zbiór elementów tego samego typu, zgrupowanych razem dla

wygody. Wektor (np. bitów) nie jest równoważny żadnej liczbie. Dlatego nie można

wykonywać na wektorze bitów operacji arytmetycznych, a operacje relacyjne mają sens tylko

wówczas gdy wektory są tej samej długości.

2.15. Przeładowanie operatorów

Przeładowanie operatorów oznacza możliwość zdefiniowania kilku funkcji o tej samej

nazwie ale różnych typach wejść i wyjść. W szczególności oznacza to możliwość

wielokrotnego definiowania operatorów. Zwykle dostawcy oprogramowania dostarczają

pakiety zawierające definicje typowych operatorów dla popularnych typów zmiennych.

Poniżej przedstawiony przykład takiego pakietu.

package P_ARITHMETIC is

subtype slv is std_logic_vector;

function "+"(L:slv; R:slv) return integer;

function "+"(L:slv; R:slv) return slv;

function "+"(L:slv; R:integer) return slv;

function "+"(L:integer; R:slv) return slv;

end P_ARITHMETIC;

use work.P_ARITHMETIC.all;

entity OVERLOADED is

port (A_BUS,B_BUS: in slv (0 to 3);

A_INT,B_INT: in integer;

Y_BUS,Z_BUS: out slv (0 to 3);

Y_INT,Z_INT: out integer);

end OVERLOADED;

Język opisu sprzętu VHDL

- 23 -

3.

Strukturalny opis sprzętu

Strukturalny opis układu cyfrowego polega na opisaniu w języku VHDL elementów

składowych oraz połączeń między nimi. Zwykle definiuje się pewną liczbę elementów

podstawowych (np. podstawowe bramki logiczne) i w oparciu o nie buduje struktury bardziej

złożone. Zachowania funkcjonalne wynikają ze sposobu połączeń elementów składowych. Ich

funkcje nie są nigdzie zapisane w sposób jawny co odróżnia ten sposób zapisu od

behawioralnego opisu sprzętu.

Strukturalny opis sprzętu jest użyteczny np. w sytuacji gdy niezbędne jest oddanie

struktury istniejącego już rozwiązania (układu elektronicznego lub układu scalonego) i znany

jest jego schemat elektroniczny. Wówczas nie wnikając w jego funkcje oraz zależności

czasowe między elementami można za pomocą opisu strukturalnego odzwierciedlić jego

zachowanie w języku VHDL.

Strukturalny sposób opisu sprzętu jest używany głównie przez programy komputerowe do

automatycznej generacji programów w języku VHDL na podstawie np. schematów układów

(np. pochodzących z programu ORCAD). Umieszczenie na wyjściowym schemacie np.

układów średniej skali integracji powoduje, iż program "rozpisuje" je na elementy składowe

(zwykle bramki logiczne) tworząc kompletny strukturalny opis sprzętu umożliwiający jego

praktyczną implementację.

Strukturalny opis sprzętu nie wydaje się być szczególnie efektywny przy opisie układu

wykonywanym przez człowieka. W takim przypadku odpowiedniejszym sposobem wydaje się

być behawioralny opis zachowań. Niemniej podkreślić należy, iż oba sposoby opisu są

zupełne i za pomocą każdego z nich można opisać każdą strukturę logiczną.

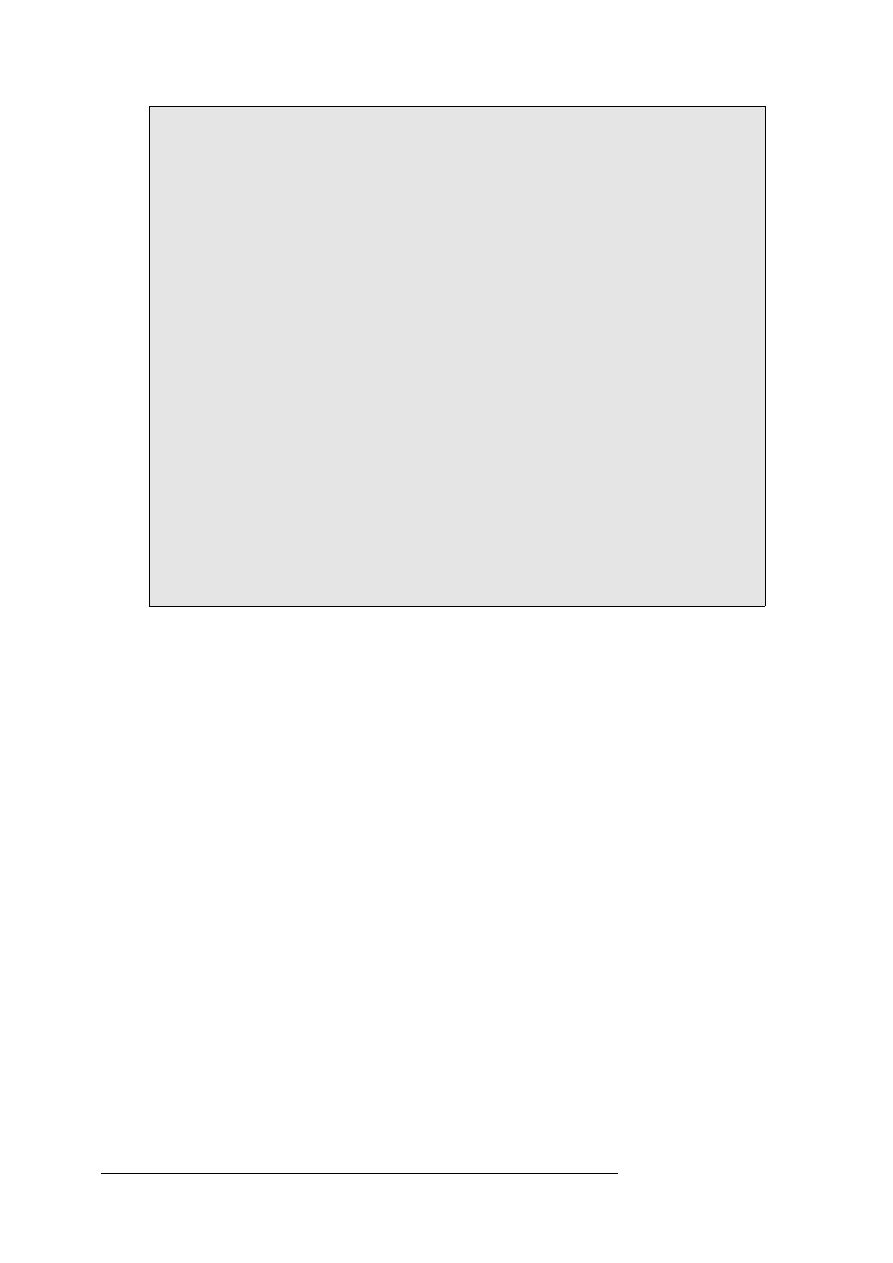

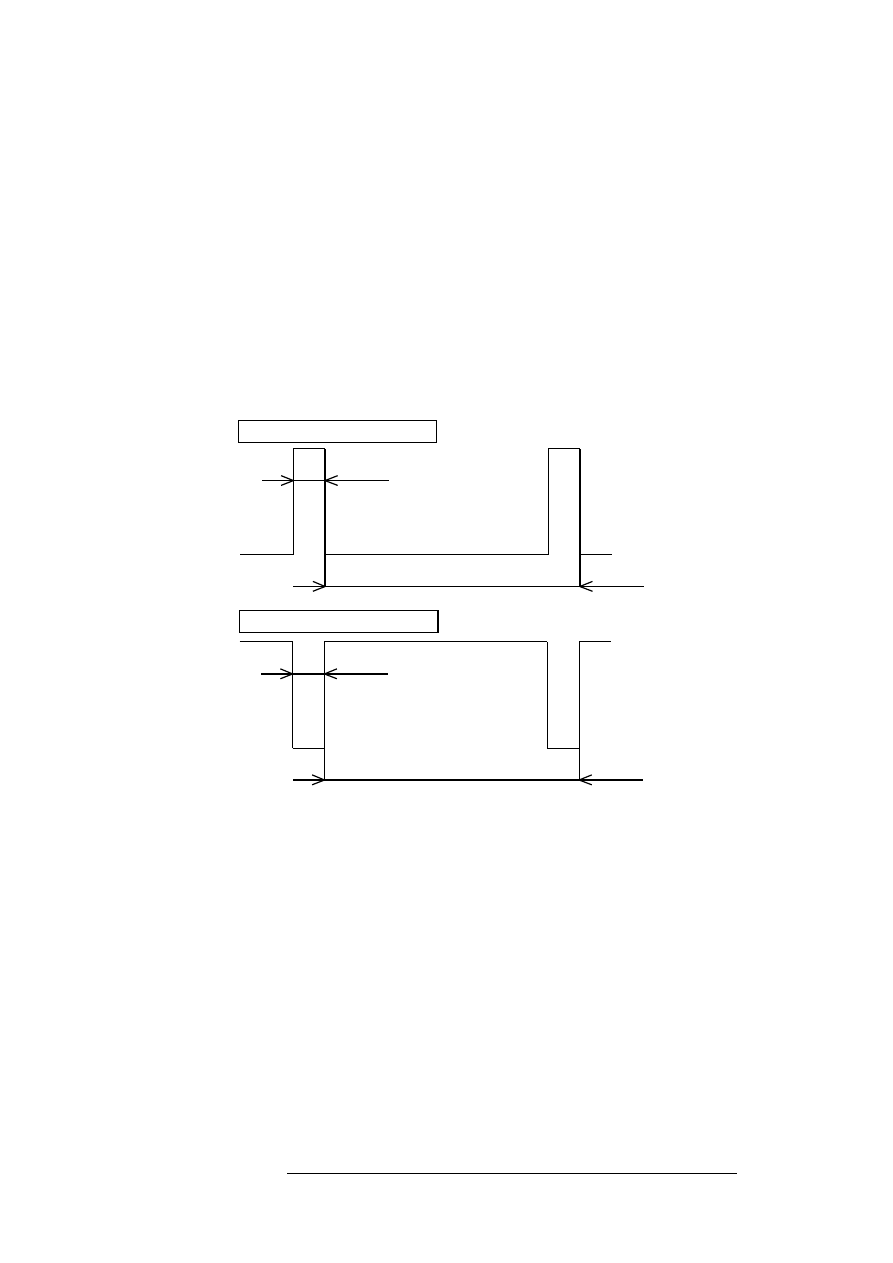

3.1.

Sumator 4-bitowy. Opis strukturalny

Jako przykład realizacji funkcji logicznej opisanej w języku VHDL w sposób strukturalny

przedstawimy 4-bitowy sumator binarny. Sumator 4-bitowy składa się z bloków sumatorów

jednobitowych o strukturze przedstawionej na Rys.3.1. Wejścia do sumatora stanowią dwie

dodawane liczby A

i

i B

i

oraz przeniesienie z poprzedniej pozycji C

i-1

. Wyjściem jest wynik

dodawania S

i

oraz przeniesienie na następną pozycję C

i

.

Si

Ci-

1

Ci

Bi

Ai

A

B

C

C S

i

i

i

i

i

−

1

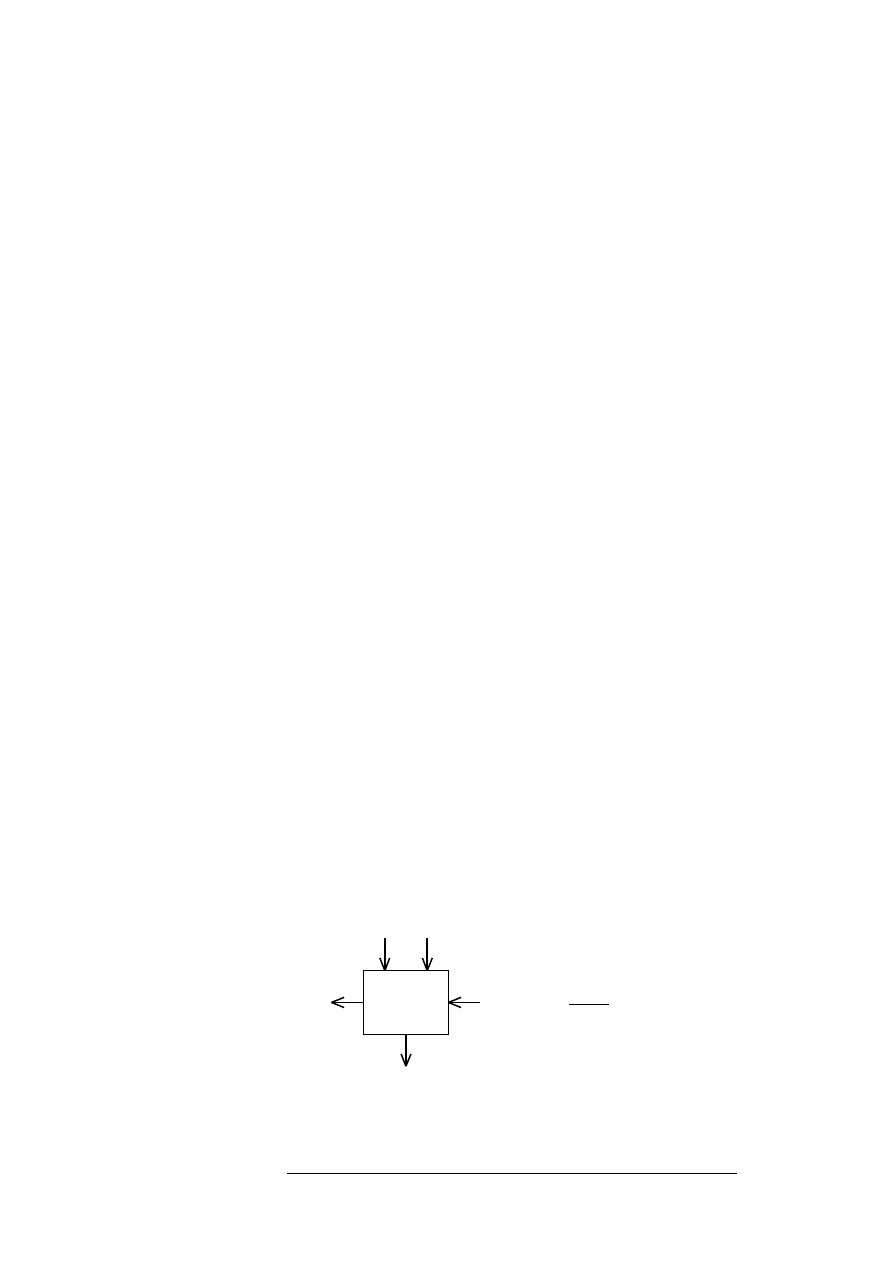

Rys.3.1. Jednobitowy sumator binarny.

- 24 -

Język opisu sprzętu VHDL

Tablice Karnouhg oraz funkcje logiczne dla wyjść przedstawiono poniżej. Odpowiednio

dla wyjścia sumy S

i

jest to:

A

i

B

i

C

i

C

i-1

00

01

11

10

0

0

0

1

0

1

0

1

1

1

Si = A

i

and B

i

or C

i-1

and A

i

or C

i-1

and B

i

=

(A

i

nand B

i

) nand (C

i-1

nand A

i

) nand (C

i-1

nand B

i

)

oraz dla wyjścia przeniesienia na następną pozycję C

i

:

A

i

B

i

S

i

C

i-1`

00

01

11

10

0

0

1

0

1

1

1

0

1

0

C

i

= A

i

xor B

i

xor C

i-1

Sumator 4-bitowy realizowany jest jako kaskadowe połączenie czterech sumatorów

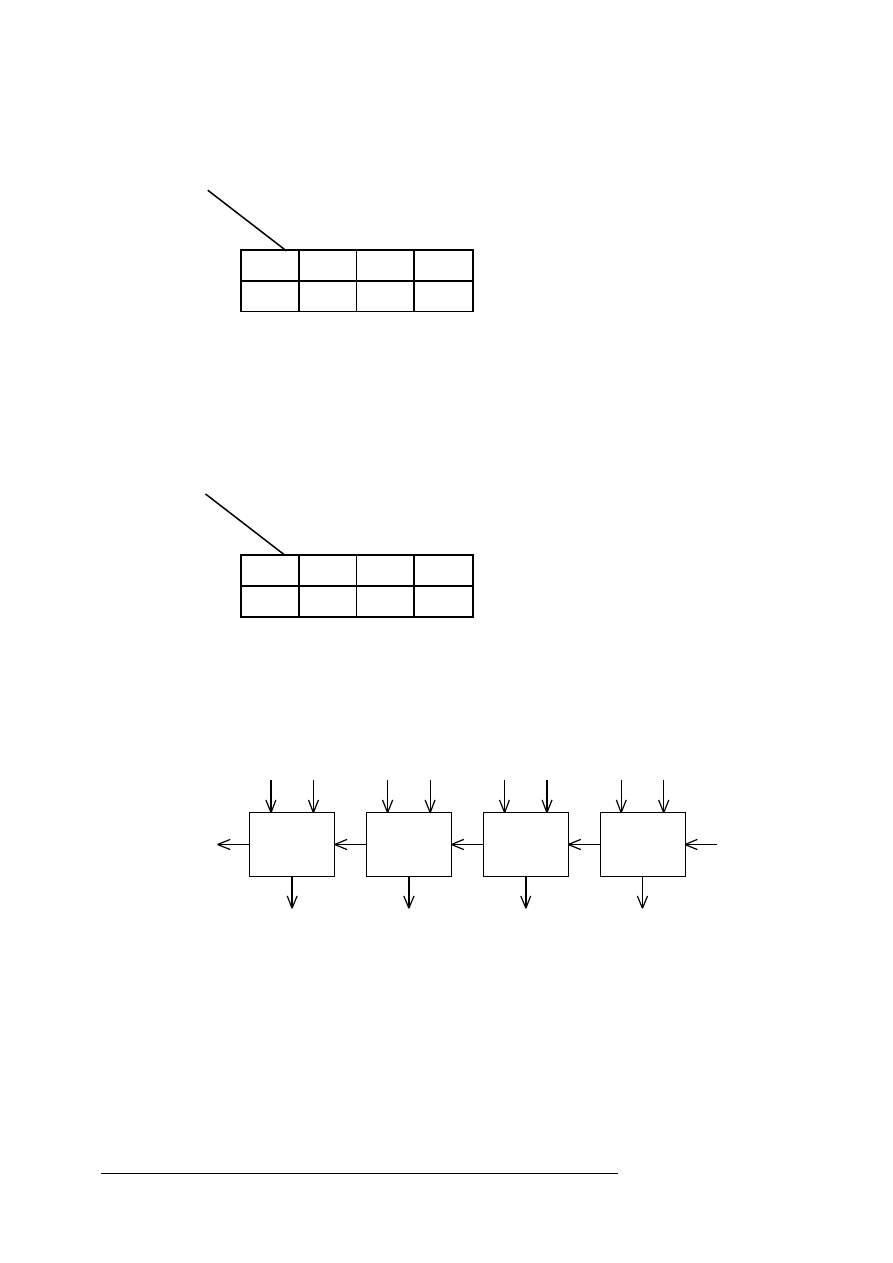

jednobitowych (Rys.3.2).

C2

C3

C4

C0

S4

B4

A4

C1

S3

B3

A3

S2

B2

A2

S1

B1

A1

Rys.3.2. Kaskadowy sumator 4-bitowy.

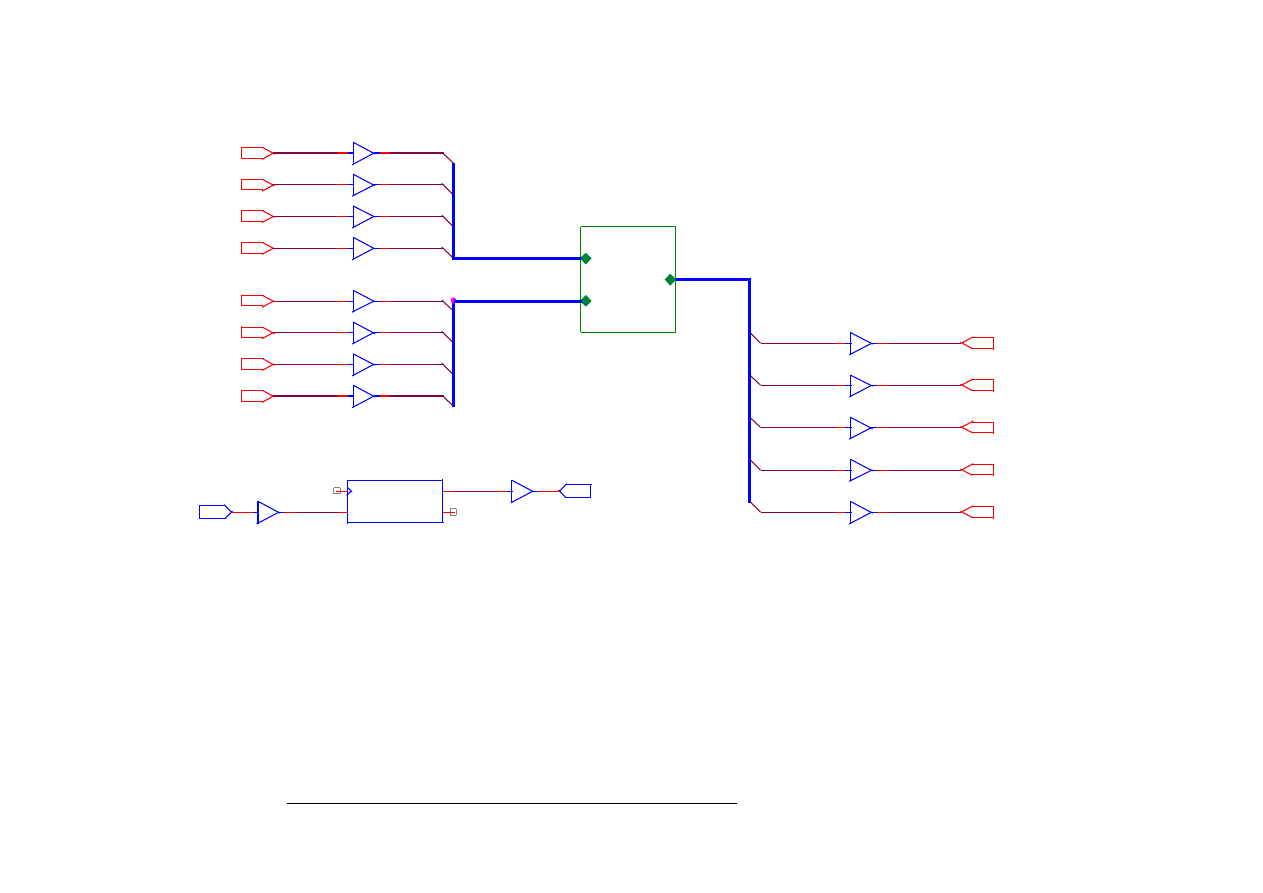

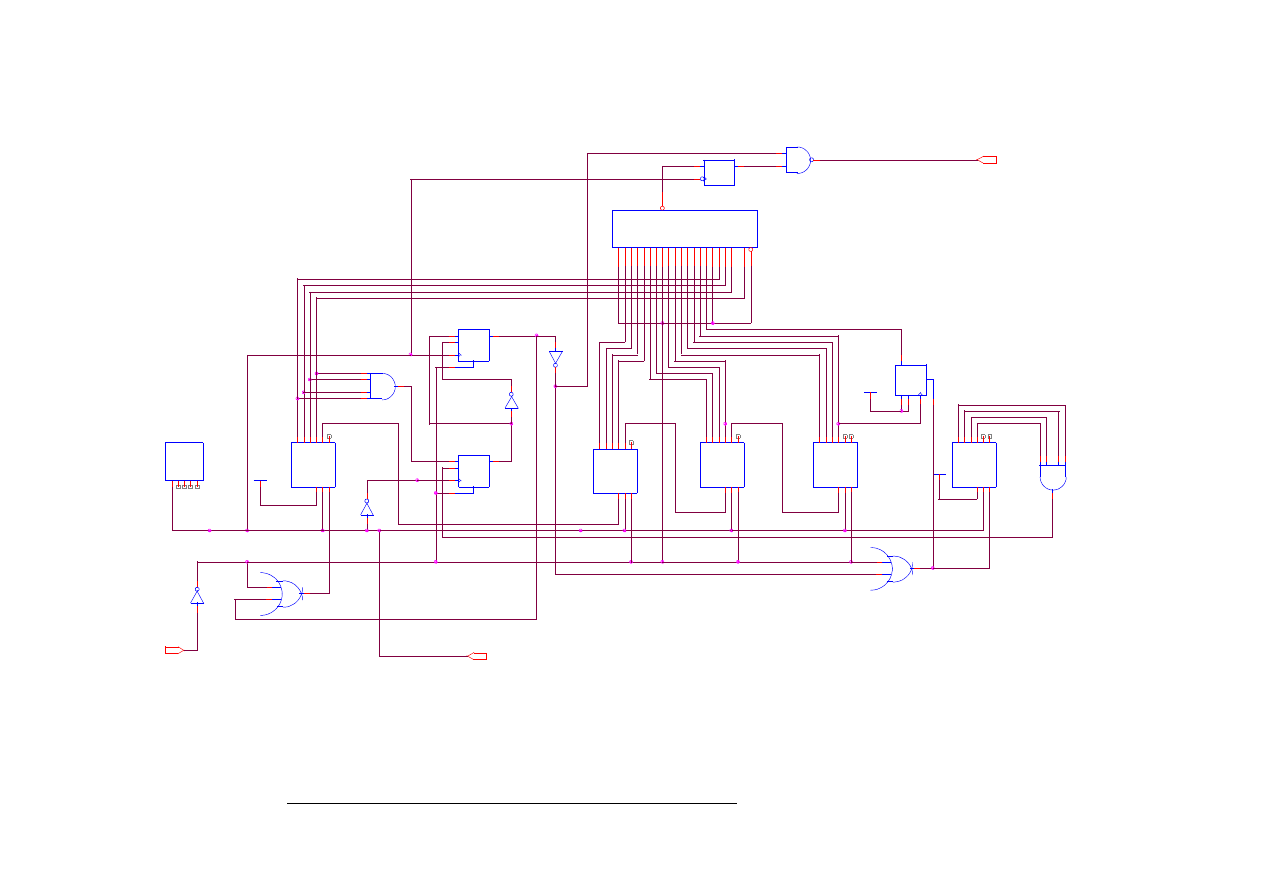

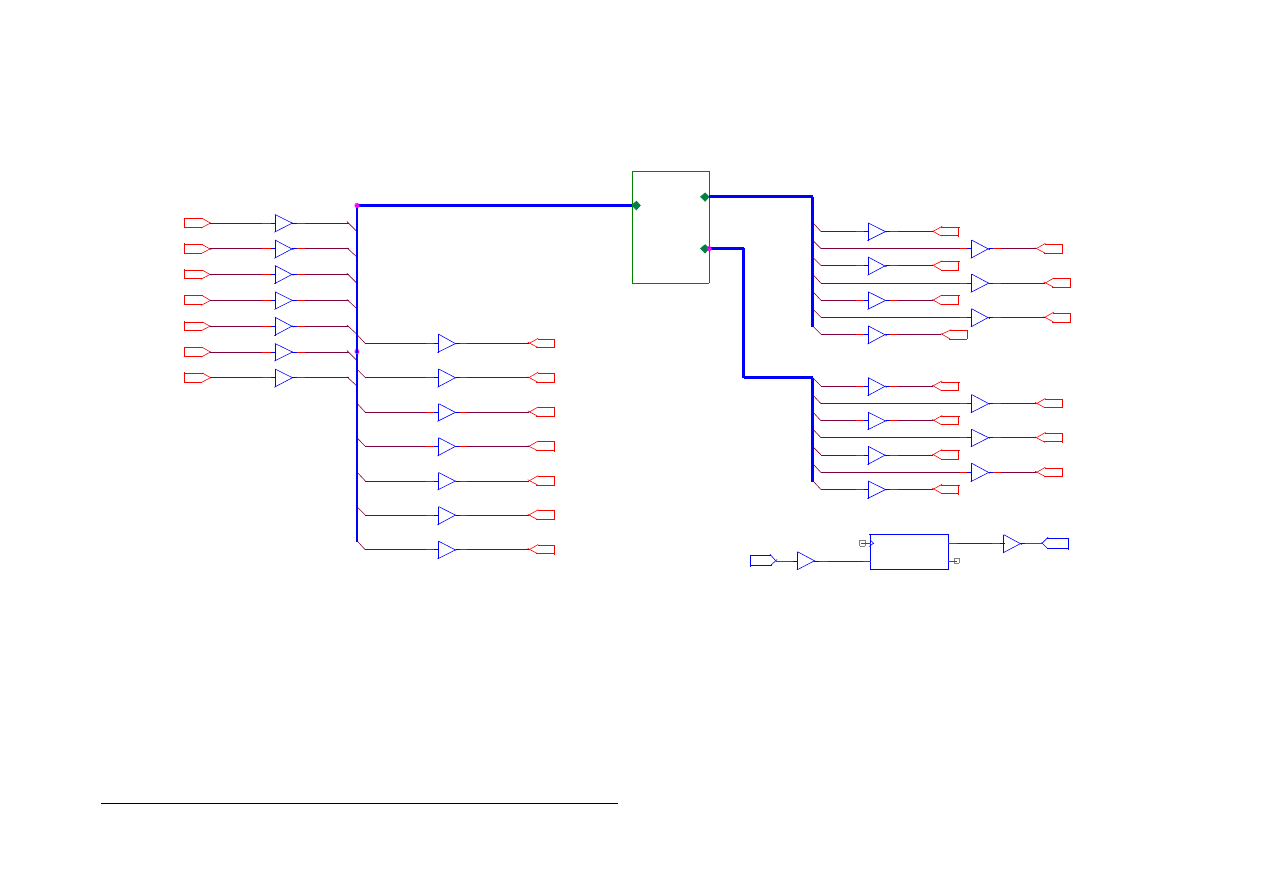

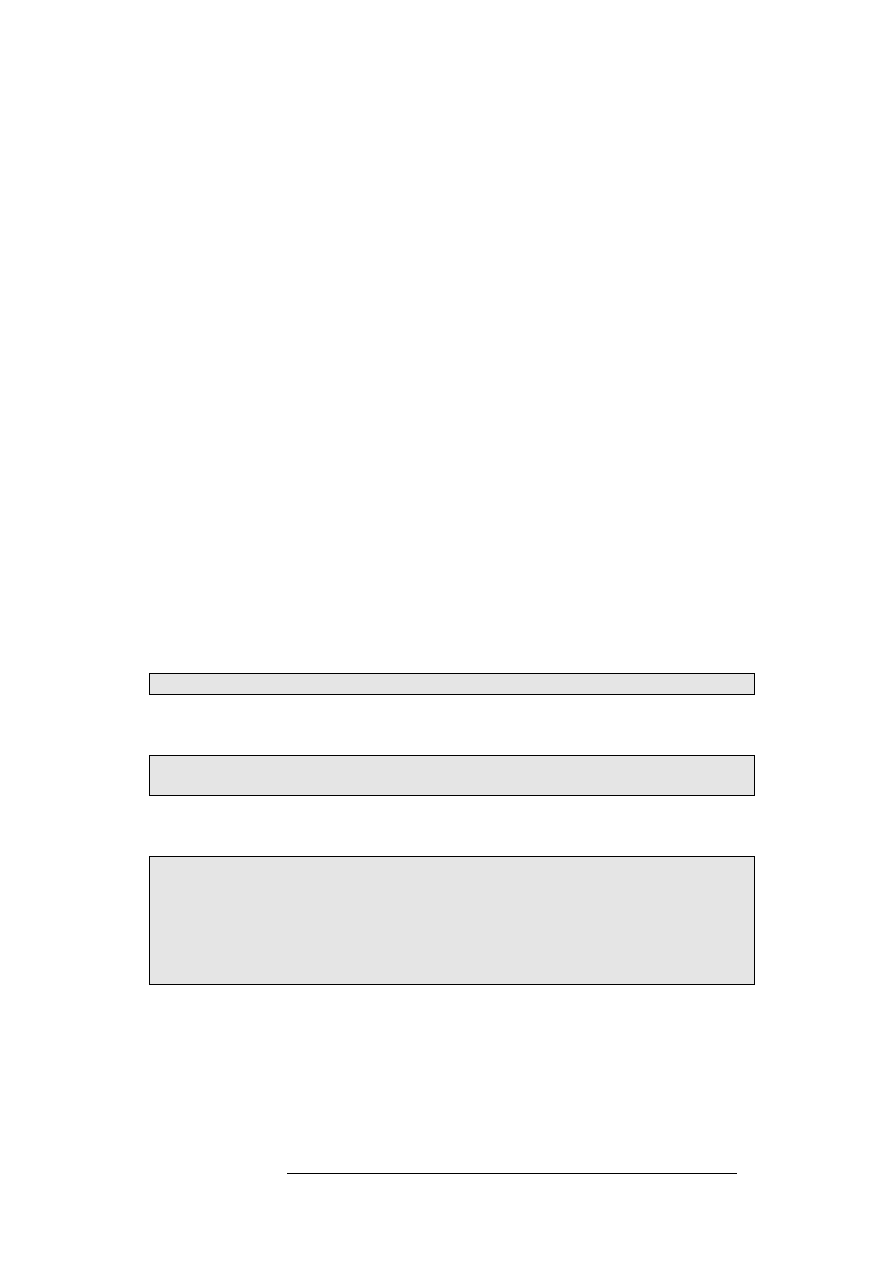

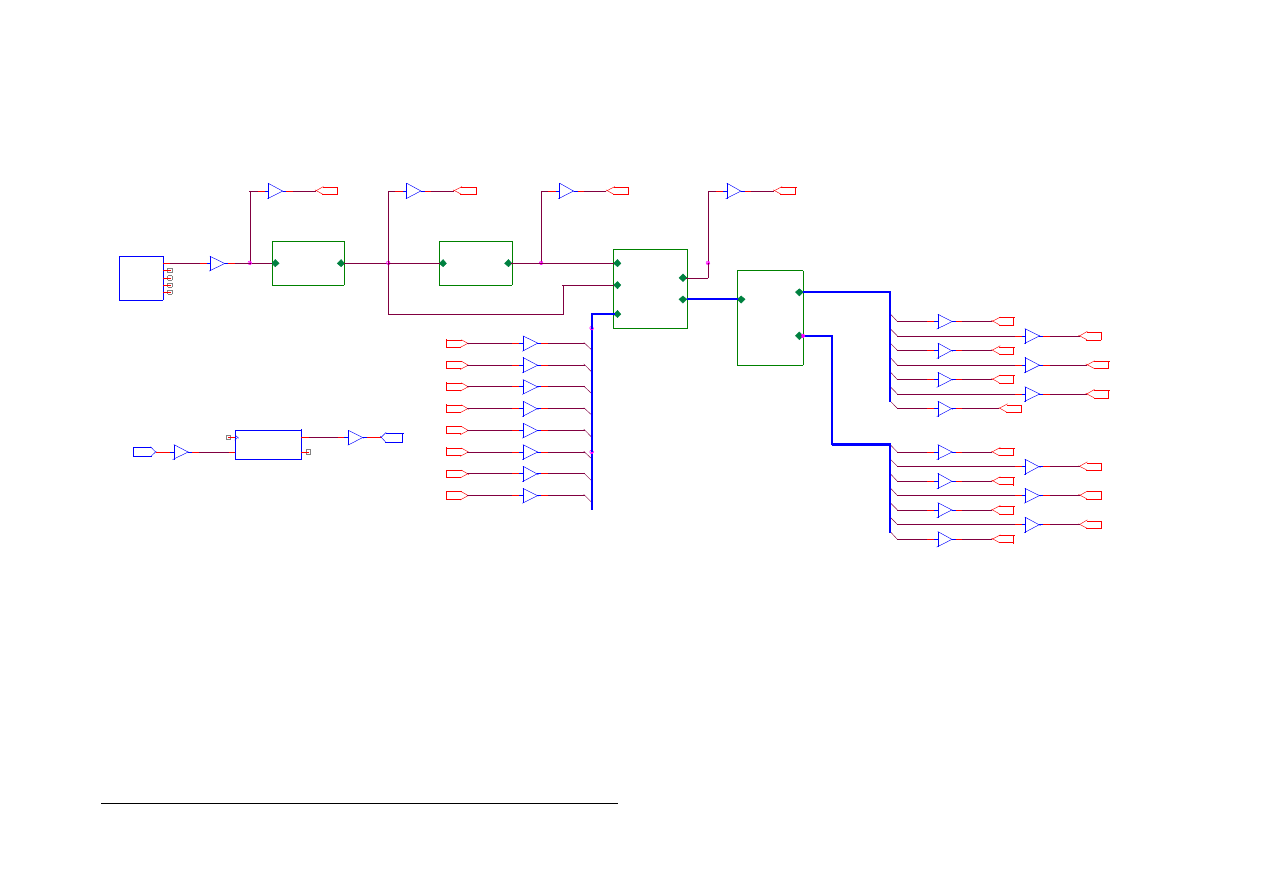

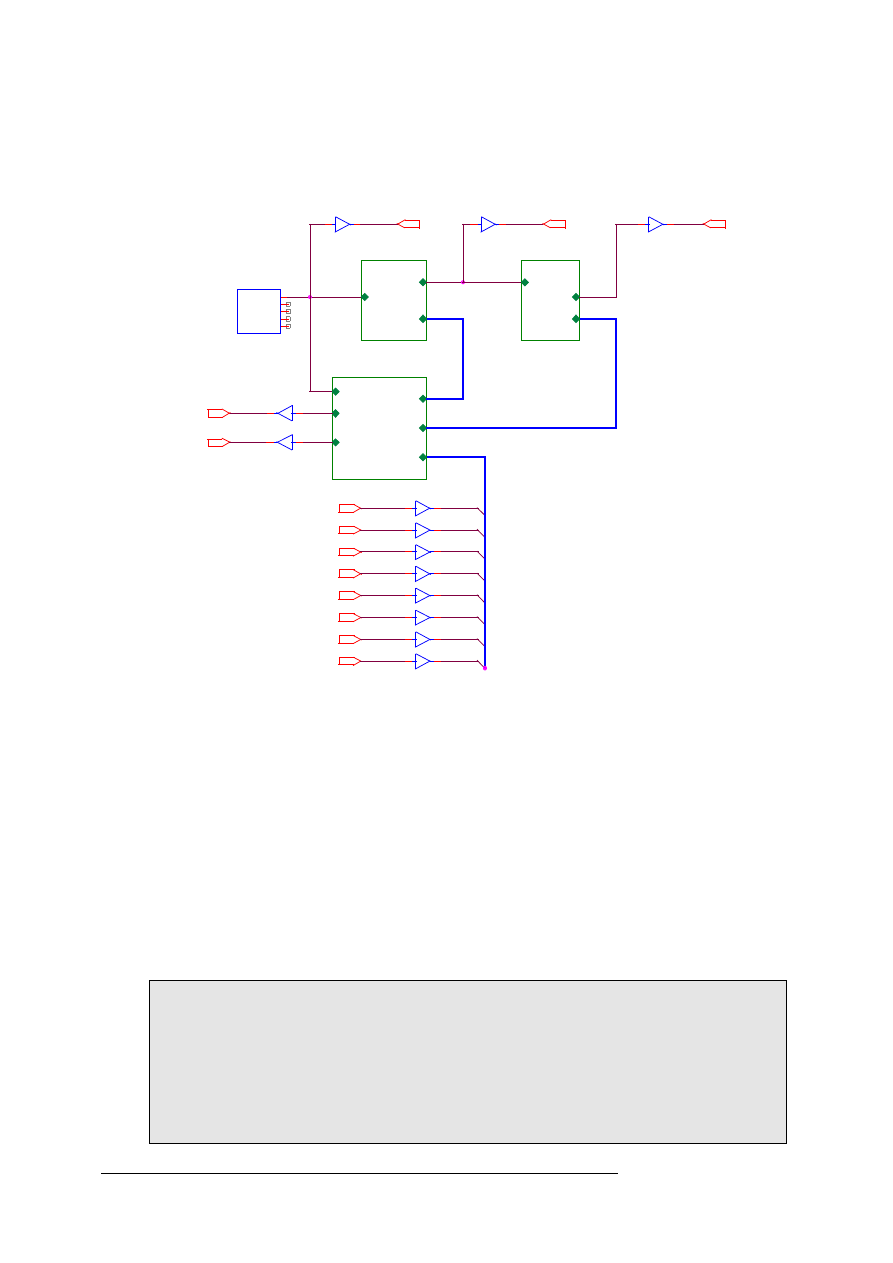

Realizacja omawianej struktury sumatora 4-bitowego w programie ORCAD

przedstawiona została na Rys.3.3. Strukturalny opis sumatora w języku VHDL realizowany

jest w bloku SumLogic. Porty wejściowe SW3_1 do SW3_8 oraz osiem buforów wejściowych

IBUF służą do zadania wartości dwóch 4-bitowych składników. Porty oraz bufory wyjściowe

służą do wyprowadzenia wyniku.

Język opisu sprzętu VHDL

- 25 -

SumLogic

SumLogic

S[4..0]

A[3..0]

B[3..0]

A[3..0]

B[3..0]

S[4..0]

RD

RT

A3

B1

A1

B2

A0

A2

B3

B0

S4

S1

S0

S2

S3

U14

OBUF

U1

IBUF

U17

IBUF

MD0

U16

MD0

MD1

U15

MD1

CLK

TRIG

DATA

RIP

U13

READBACK

U2

IBUF

U3

IBUF

U4

IBUF

U6

IBUF

U8

IBUF

U10

IBUF

U5

IBUF

U12

OBUF

U18

OBUF

U7

OBUF

U11

OBUF

U9

OBUF

SW3_1

SW3_2

SW3_3

SW3_4

SW3_5

SW3_6

SW3_7

SW3_8

LOWER2_PIN

LOWER1_PIN

UPPER0_PIN

LOWER0_PIN

LOWER3_PIN

P19

P20

P23

P24

P25

P26

P27

P28

P57

P62

P61

P65

P66

Rys.3.3. Realizacja 4-bitowego sumatora binarnego w programie ORCAD.

- 26 -

Język opisu sprzętu VHDL

Omawiany przykład zrealizowany został na układzie programowalnym firmy XILINX o

numerze 4008. Etykiety nadane sygnałom za portami wejściowymi oraz przed portami

wyjściowymi o postaci Pxx definiują numery wyprowadzeń układu 4008. Np. P28 definiuje

wyprowadzenie układu o numerze 28.

Blok READBACK wraz z elementami wejściowymi oraz wyjściowymi dodany został w

celu weryfikacji poprawności zapisu danych do układu 4008. Jego obecność jest opcjonalna.

Program w języku VHDL związany z blokiem SumLogic przedstawiono poniżej. Zawiera

on deklarację trójwejściowej bramki XOR xor3, dwuwejściowej bramki NAND nand2 oraz

trójwejściowej bramki NAND nand3. Na ich podstawie zdefiniowano blok sumatora

jednobitowego Sum1Bit. Z kolei ten sumator jednobitowy służy do definicji sumatora

czterobitowego SumLogic.

Strukturalny opis elementu rozpoczyna się od wyspecyfikowania części składowych

deklarowanych za pomocą komendy COMPONENT. Po słowie kluczowym COMPONENT

następuje nazwa komponentu, a po słowie kluczowym PORT specyfikacja wejść oraz wyjść

komponentu wraz z podaniem ich typów. Dyrektywy postaci:

FOR ALL : xor3gate USE ENTITY xor3;

określają jaki blok ENTITY związany jest z deklarowanymi komponentami. Dyrektywy PORT

MAP przypisują odpowiednie sygnały do odpowiednich wejść oraz wyjść poszczególnych

komponentów. Przykładowo dla deklaracji bloku ENTITY:

ENTITY xor3 is

PORT (

I1

: IN STD_LOGIC;

I2

: IN STD_LOGIC;

I3

: IN STD_LOGIC;

O

: OUT STD_LOGIC ) ;

END xor3;

komendy:

COMPONENT xor3gate PORT (

I1

: IN STD_LOGIC;

I2

: IN STD_LOGIC;

I3

: IN STD_LOGIC;

O

: OUT STD_LOGIC ) ; END COMPONENT;

FOR ALL : xor3gate USE ENTITY xor3;

--

--

st1 : xor3gate PORT MAP ( A, B, Ci, Co ); -- Co

przyporządkowują komponent xor3gate do bloku ENTITY xor3 oraz wiążą z bramką st1

sygnały A, B, Ci oraz Co w taki sposób, że sygnały A, B oraz Ci są wejściami i odpowiadają

Język opisu sprzętu VHDL

- 27 -

sygnałom I1, I2 oraz I3 oraz sygnał Co jest wyjściem odpowiadającym wyjściu O bloku

ENTITY o nazwie xor3.

Kompletna implementacja bloku SumLogic przedstawiona została poniżej.

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.numeric_std.all;

ENTITY xor3 is

PORT (

I1

: IN STD_LOGIC;

I2

: IN STD_LOGIC;

I3

: IN STD_LOGIC;

O

: OUT STD_LOGIC ) ;

END xor3;

ARCHITECTURE behavior_xor3 OF xor3 IS

BEGIN

O <= I1 xor I2 xor I3;

END behavior_xor3;

Use ieee.std_logic_1164.all;

Use ieee.numeric_std.all;

ENTITY nand2 is

PORT (

I1

: IN STD_LOGIC;

I2

: IN STD_LOGIC;

O

: OUT STD_LOGIC ) ;

END nand2;

ARCHITECTURE behavior_nand2 OF nand2 IS

BEGIN

O <= not (I1 and I2);

END behavior_nand2;

Use ieee.std_logic_1164.all;

Use ieee.numeric_std.all;

ENTITY nand3 is

PORT (

I1

: IN STD_LOGIC;

I2

: IN STD_LOGIC;

I3

: IN STD_LOGIC;

O

: OUT STD_LOGIC ) ;

END nand3;

ARCHITECTURE behavior_nand3 OF nand3 IS

BEGIN

O <= not (I1 and I2 and I3);

END behavior_nand3;

Use ieee.std_logic_1164.all;

Use ieee.numeric_std.all;

ENTITY Sum1Bit is

- 28 -

Język opisu sprzętu VHDL

PORT (

A

: IN STD_LOGIC;

B

: IN STD_LOGIC;

Ci

: IN STD_LOGIC;

S

: OUT STD_LOGIC;

Co

: OUT STD_LOGIC ) ;

END Sum1Bit;

ARCHITECTURE behavior_Sum1Bit OF Sum1Bit IS

COMPONENT xor3gate PORT (

I1

: IN STD_LOGIC;

I2

: IN STD_LOGIC;

I3

: IN STD_LOGIC;

O

: OUT STD_LOGIC ) ; END COMPONENT;

COMPONENT nand2gate PORT (

I1

: IN STD_LOGIC;

I2

: IN STD_LOGIC;

O

: OUT STD_LOGIC ) ; END COMPONENT;

COMPONENT nand3gate PORT (

I1

: IN STD_LOGIC;

I2

: IN STD_LOGIC;

I3

: IN STD_LOGIC;

O

: OUT STD_LOGIC ) ; END COMPONENT;

FOR ALL : xor3gate USE ENTITY xor3;

FOR ALL : nand2gate USE ENTITY nand2;

FOR ALL : nand3gate USE ENTITY nand3;

SIGNAL t1, t2, t3 : STD_LOGIC;

BEGIN

st1 : xor3gate PORT MAP ( A, B, Ci, Co ); -- Co

st2 : nand2gate PORT MAP ( A, B, t1 );

st3 : nand2gate PORT MAP ( A, Ci, t2 );

st4 : nand2gate PORT MAP ( B, Ci, t3 );

st5 : nand3gate PORT MAP ( t1, t2, t3, S ); -- S

END behavior_Sum1Bit;

Use ieee.std_logic_1164.all;

Use ieee.numeric_std.all;

ENTITY SumLogic is

PORT (

S

: OUT STD_LOGIC_VECTOR (4 DOWNTO 0);

A

: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

B

: IN STD_LOGIC_VECTOR (3 DOWNTO 0));

END SumLogic;

ARCHITECTURE behavior OF SumLogic IS

COMPONENT S1B

PORT (

A

: IN STD_LOGIC;

B

: IN STD_LOGIC;

Ci

: IN STD_LOGIC;

S

: OUT STD_LOGIC;

Co

: OUT STD_LOGIC ) ; END COMPONENT;

FOR ALL : S1B USE ENTITY Sum1Bit;

SIGNAL C0, C1, C2, C3, C4 : STD_LOGIC;

Język opisu sprzętu VHDL

- 29 -

BEGIN

C0 <= '0';

st1 : S1B PORT MAP ( A(0), B(0), C0, S(0),C1 );

st2 : S1B PORT MAP ( A(1), B(1), C1, S(1),C2 );

st3 : S1B PORT MAP ( A(2), B(2), C2, S(2),C3 );

st4 : S1B PORT MAP ( A(3), B(3), C3, S(3),C4 );

S(4) <= C4;

END behavior;

Ze względu na niską efektywność tworzenia układów logicznych opisywanych w sposób

strukturalny ten sposób opisu nie będzie omawiany w dalszej części niniejszej publikacji.

Niemniej należy mieć świadomość, że wobec faktu automatycznej generacji przez program

ORCAD opisów w języku VHDL wprowadzonych schematów znajomość zasad

strukturalnego opisu logiki może okazać się niezbędna.

3.2.

Generator numerów górników. Projekt w postaci schematu

elektrycznego

Jednym ze sposobów zaprogramowanie programowalnych układów logicznych jest

narysowanie schematu elektronicznego projektowanego układu. W sposobie tym pośrednio

wykorzystywany jest strukturalny opis sprzętu bowiem program ORCAD z wprowadzonego

schematu w sposób automatyczny generuje program w języku VHDL, który z kolei jest

podstawą do wygenerowania ciągu bitowego programującego programowalny układ logiczny.

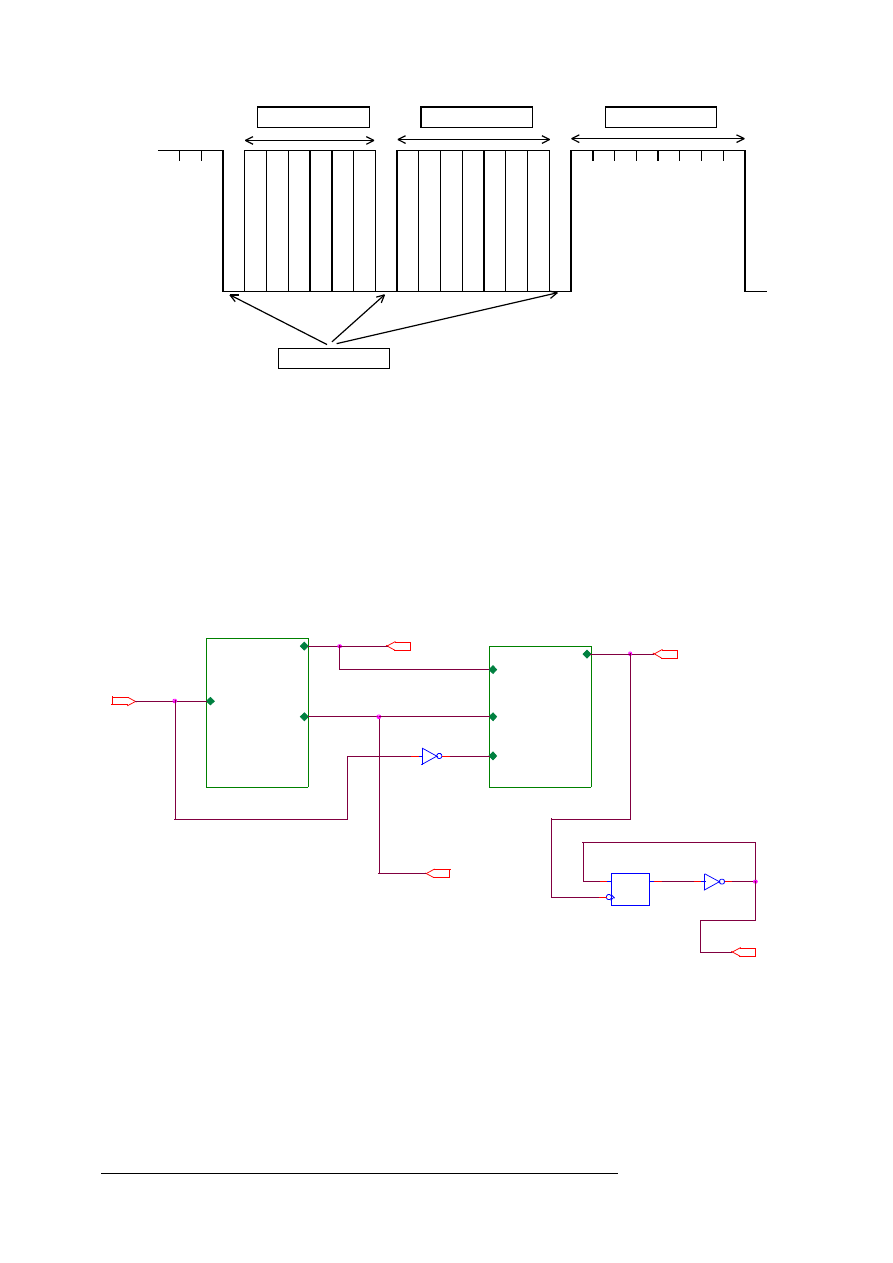

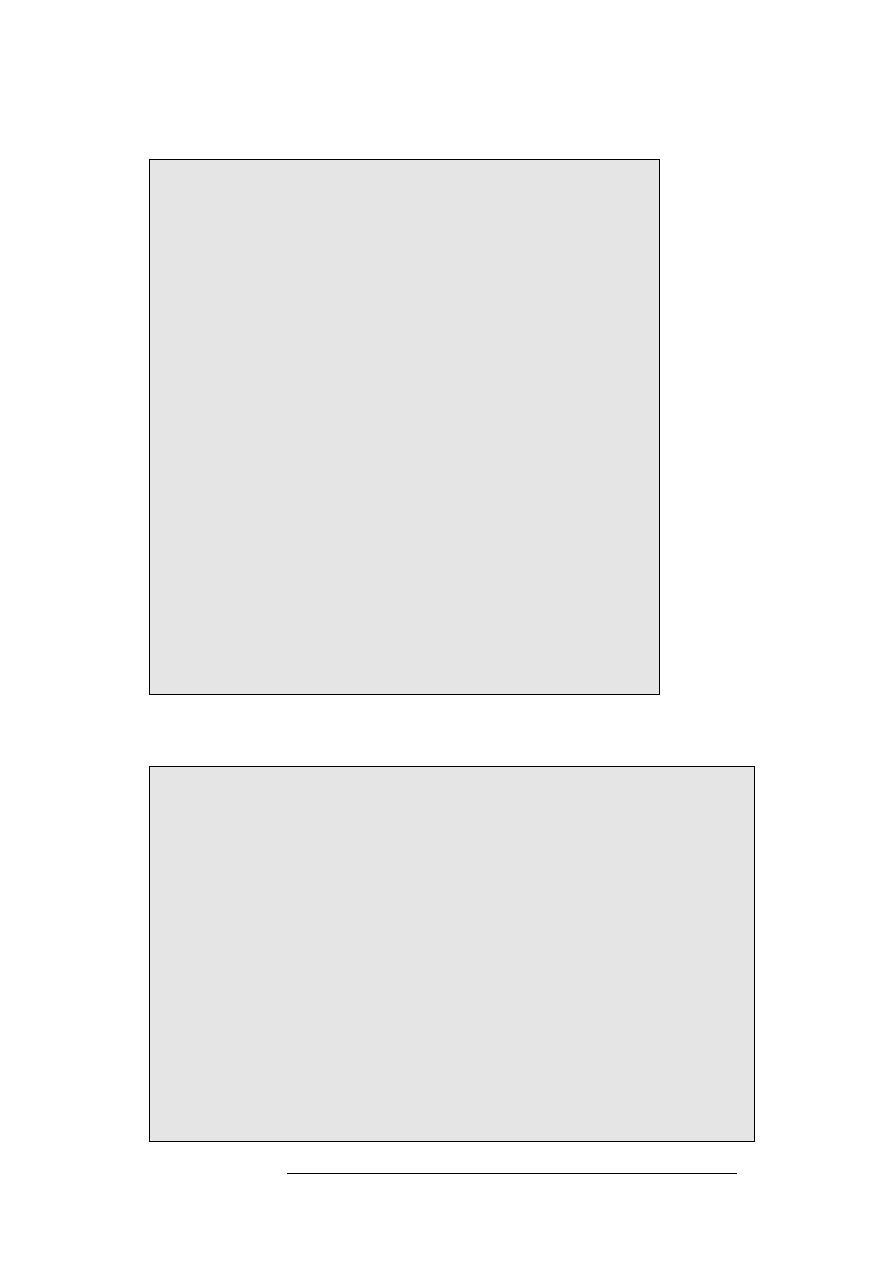

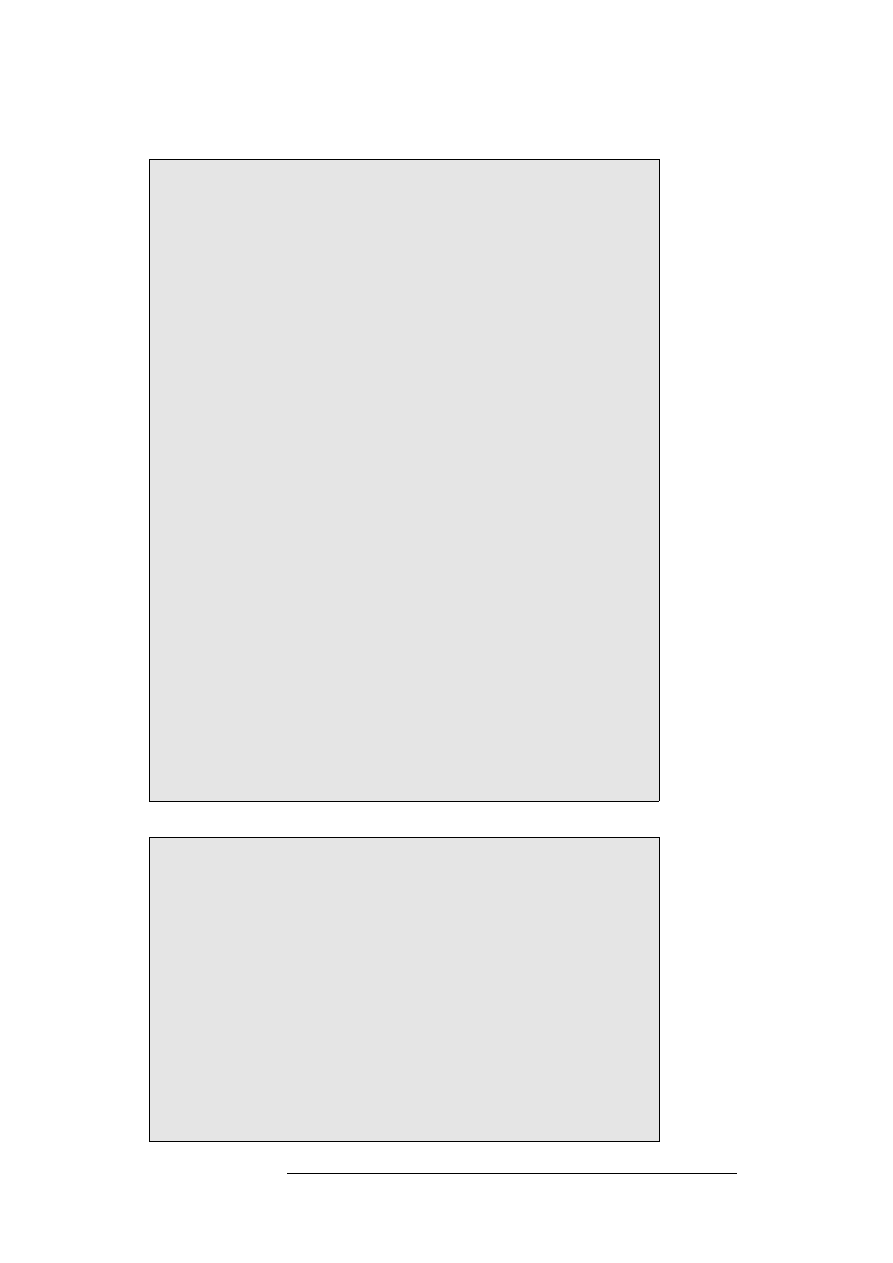

Poniżej omówiono aplikację, której celem była lokalizacja położenia górników w

kopalni. System lokalizacji składa się z nadajników rozmieszczonych w chodnikach kopalni

oraz z odbiorników przenoszonych przez każdego górnika. Każdy z nadajników nadaje

kolejno wszystkie kombinacje 13-bitowych numerów w formacie przedstawionym na Rys.3.4.

Każdy z odbiorników jednoznacznie związany z określonym górnikiem posiada "zaszyty" w

sobie unikalny numer 13-bitowy. Jeżeli odbiornik znajdzie się w strefie pracy nadajnika

wysyła potwierdzenie umożliwiające lokalizacje konkretnego górnika. Schematy ideowe

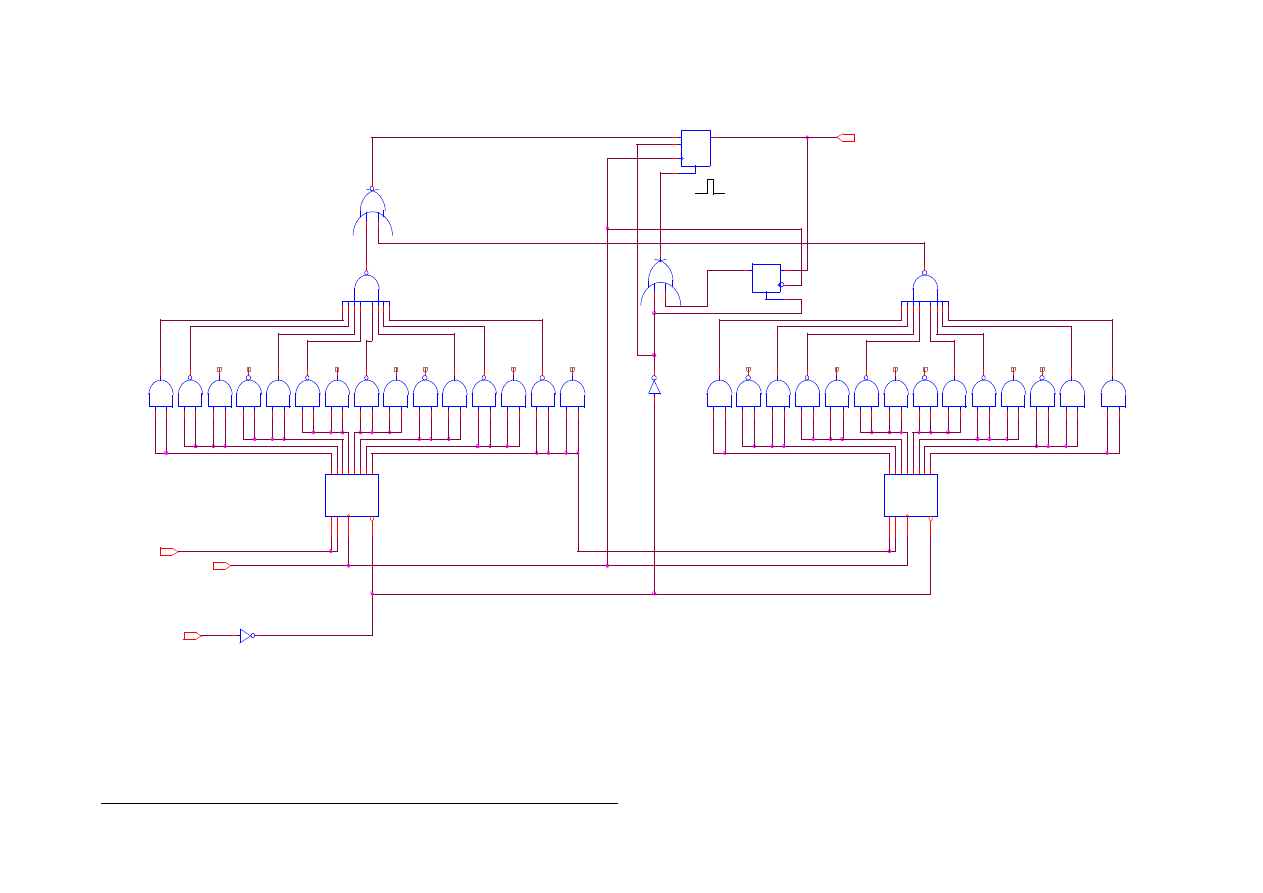

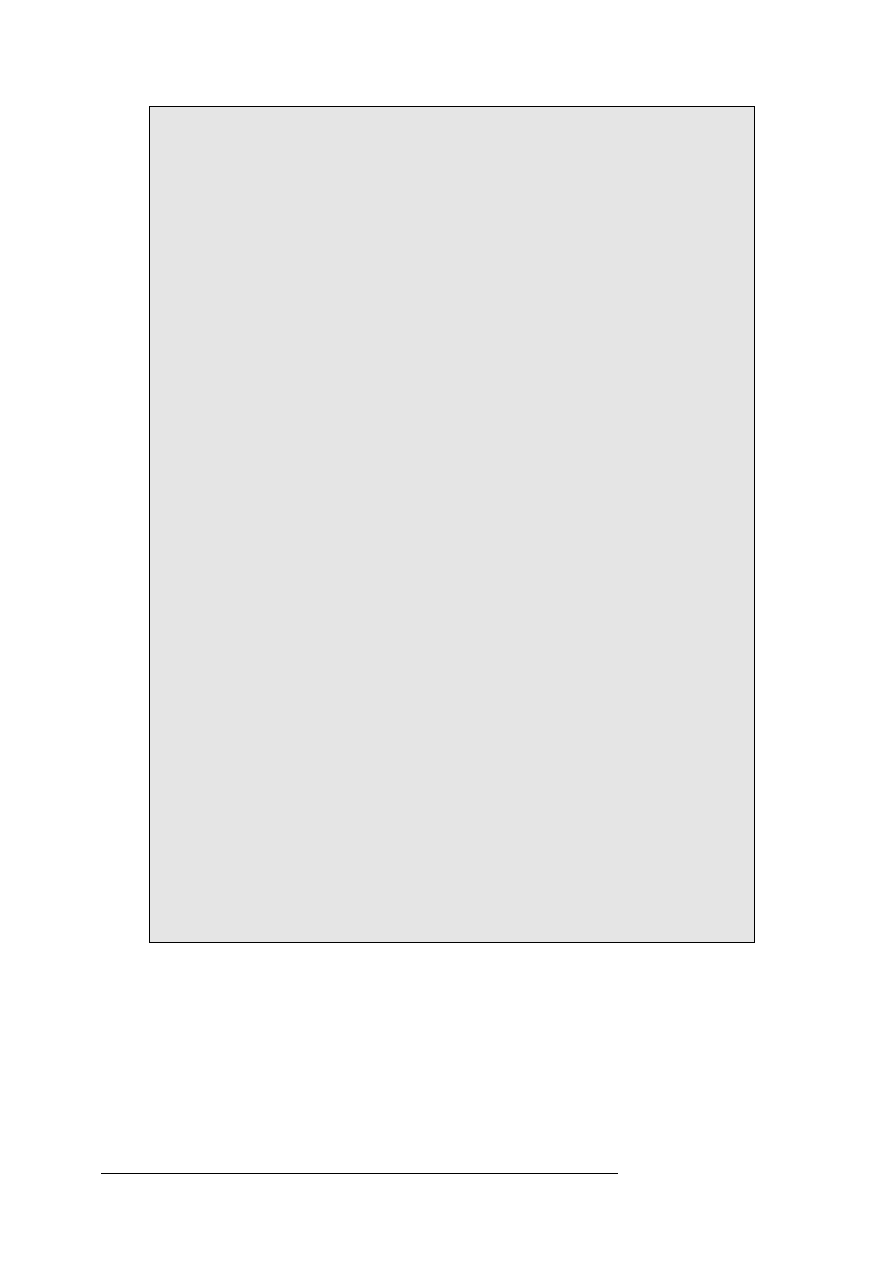

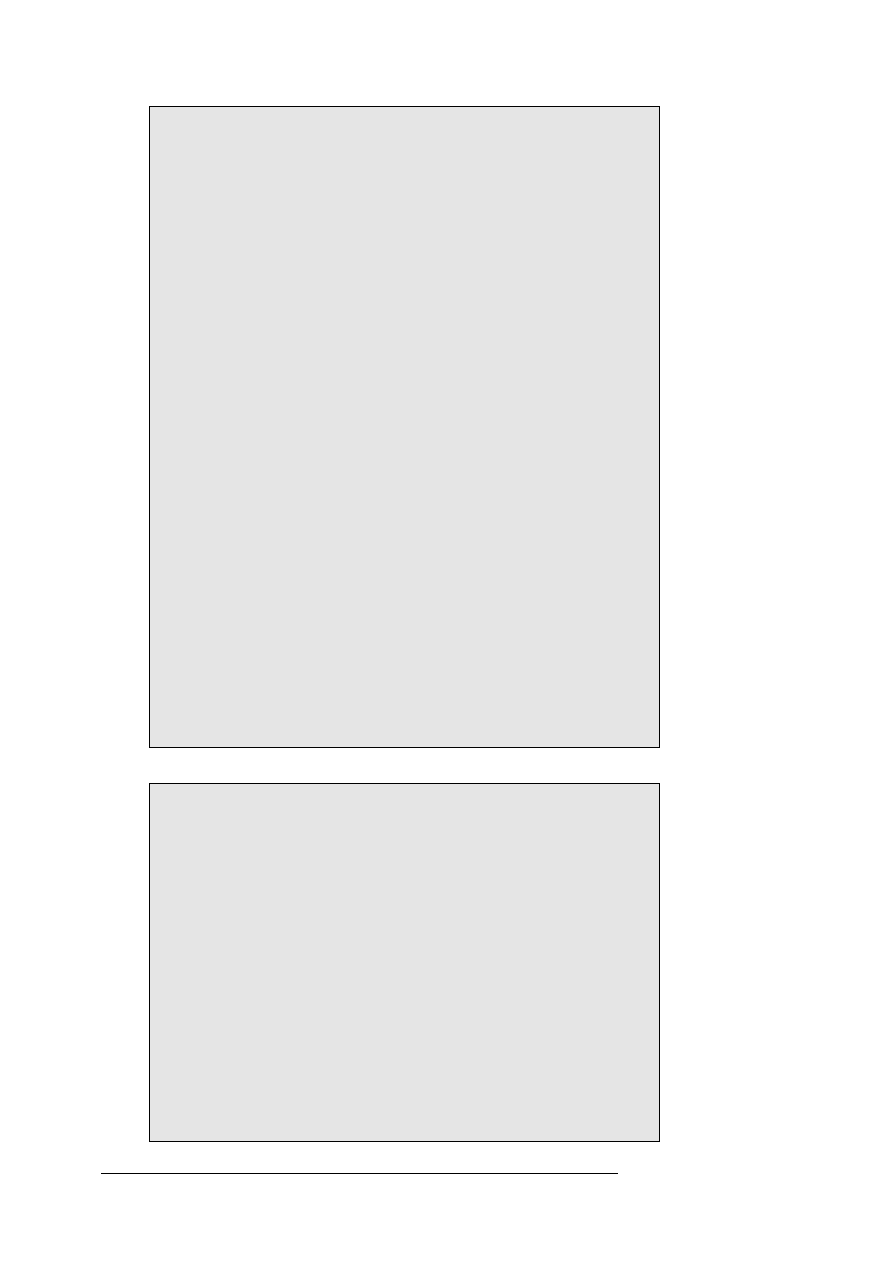

układu nadajnika oraz odbiornika przedstawiono na Rys.3.5, Rys.3.6 oraz Rys.3.7.

Realizacja poprzez wprowadzenie schematu elektronicznego układu była w tym

przypadku szczególnie efektywna bowiem znany był schemat elektroniczny poprawnie

pracującego układu. W dalszej części opracowania przedstawiony zostanie układu nadajnika

oraz odbiornika zrealizowany poprzez behawioralny opis funkcji w języku VHDL.

- 30 -

Język opisu sprzętu VHDL

Bity przerwy

7 bitów numeru

6 bitów numeru

Bity o wartości '0'

Rys.3.4. Format numeru.

Warto zauważyć, iż pierwotna realizacja układu wykonana w oparciu o układy TTL oraz

CMOS średniej skali integracji wymagała wykorzystania po kilkanaście układów zarówno po

stronie odbiornika jak i nadajnika. Wykorzystując układy programowalne firmy XILINX

można do układu 4003 "wpisać" zarówno nadajnik jak i odbiornik wykorzystując tylko około

50% pojemności układu. Dodatkowymi zaletami są niezwykła elastyczność

przeprogramowania układu oraz redukcja zużycia mocy szczególnie istotna w przypadku

zasilania bateryjnego.

Nadajnik1

Nadajnik

Reset

Numer

Nad_Clock

Odbior

Odbior

Odb_reset

Odb_Numer

Jest_nr

Odb_Clock

U24

INV

D

Q

C

U25

FD_1

U26

INV

SW5

Numer

Out70

JEST

Clock

P18

P14

P70

P68

P67

Rys.3.5. Blokowy schemat układu nadajnika oraz odbiornika.

Język opisu sprzętu VHDL

- 31 -

INT_RESET

NUMER

INPUT

U7

AND4

U22

OR2

U19

VCC

Q

J

K

CLR

C

U16

FJKC

U20

INV

Q

J

K

CLR

C

U4

FJKC

U9

INV

U5

INV

U18

VCC

U21

OR2

U3

X74_150

E0E1E2E3E4E5E6E7E8E9E10

E11

E12

E13

E14

E15

A B C

D G

W

U1

NAND2

U14

CB4CE

CEC CLR

Q0Q1Q2Q3

CEO

TC

U13

CB4CE

CEC CLR

Q0Q1Q2Q3

CEO

TC

U12

CB4CE

CEC CLR

Q0Q1Q2Q3

CEO

TC

U15

CB4CE

CEC CLR

Q0Q1Q2Q3

CEO

TC

U11

CB4CE

CEC CLR

Q0Q1Q2Q3

CEO

TC

Q

J K

CLR

C

U6

FJKC

U8

VCC

U17

AND4

D

Q

C

U2

FD_1

U10

OSC4

F8M

F500K

F16K

F490

F15

U23

INV

Reset

Numer

Nad_Clock

Rys.3.6. Schemat ideowy nadajnika numerów.

- 32 -

Język opisu sprzętu VHDL

CLOCK

NUMER_OK

U44

NAND2

U46

NAND2

U57

AND2

U56

NAND2

U63

X74_164

A B CK

CLR

QA

QB

QC

QD

QE

QF

QG

QH

U60

NAND2

U55

AND2

U45

AND2

U42

NAND2

U48

INV

U39

AND2

U49

AND2

U34

NAND2

U36

NAND2

U31

NAND8

U51

AND2

U33

AND2

U62

AND2

U61

AND2

U54

NAND2

U52

NAND2

Q

J

K

CLR

C

U27

FJKC

U28

NOR2

U35

AND2

U38

NAND2

U53

AND2

U50

NAND2

U37

AND2

U32

NAND8

U40

NAND2

U59

AND2

U65

INV

U43

AND2

U47

AND2

U64

X74_164

A B CK

CLR

QA

QB

QC

QD

QE

QF

QG

QH

U41

AND2

U58

NAND2

U29

OR2

D

Q

CLRC

U30

FDC_1

Odb_reset

Odb_Numer

Jest_nr

Odb_Clock

Rys.3.7. Schemat ideowy odbiornika numerów umożliwiający detekcje konkretnego numeru.

Język opisu sprzętu VHDL

- 33 -

4.

Behawioralny opis sprzętu

Behawioralny opis sprzętu polega na opisie w języku VHDL funkcji układu, a nie

struktury połączeń elementów. Zamiast używać instrukcji definiujących komponenty oraz

połączenia między nimi używa się operatorów, instrukcji podstawienia, definicji procesów,

instrukcji pętli, rozgałęzień itp. Opis behawioralny przypomina zapis algorytmu w takich

językach programowania jak C lub Pascal.

Poniżej przedstawiono opis behawioralny funkcji sumatora jednobitowego omawianego

w poprzednim rozdziale. Warto zwrócić uwagę na znacznie bardziej zwarty i czytelny zapis

wewnątrz bloku ARCHITEKTURE w porównaniu z opisem strukturalnym.

ENTITY Sum1Bit is

PORT (

A

: IN STD_LOGIC;

B

: IN STD_LOGIC;

Ci

: IN STD_LOGIC;

S

: OUT STD_LOGIC;

Co

: OUT STD_LOGIC ) ;

END Sum1Bit;

ARCHITECTURE behavior_Sum1Bit OF Sum1Bit IS

BEGIN

S <= ( A and B ) or ( A and Ci ) or ( B and Ci );

Co <= A xor B xor Ci;

END behavior_Sum1Bit;

Poniżej przedstawiono wybrane techniki programowania używane podczas

behawioralnego opisu zachowania układów cyfrowych.

4.1.

Wielokrotne wywołanie procesu

Rozważmy przykład:

EXAMPLE: process (A, B, M)

begin

Y <= A;

M <= B;

Z <= M;

end process EXAMPLE;

- 34 -

Język opisu sprzętu VHDL

Występuje tutaj przypisanie do sygnału M oraz sygnał M znajduje się jednocześnie na

liście aktywacyjnej procesu. W instrukcji M <= B; sygnał M nie zmienia się ponieważ zmiany

następują dopiero po zakończeniu procesu. W związku z tym nie nastąpi zmiana wartości

sygnału Z (ściśle mówiąc nowa wartość sygnału Z będzie równa wartości sygnału B). Gdy

proces się zakończy M jest zmieniane na wartość B, ale Z zmienia wartość na poprzednią

wartość M. Ale M się zmieniło i M jest na liście aktywacyjnej więc proces jest powtórnie

wywoływany. To spowoduje zmianę wartości sygnału Z. Jest to więc sposób na wielokrotne

wywołanie procesu.

4.2.

Definiowanie rejestrów

Poniższy program opisuje przerzutnik typu D wyzwalany narastającym zboczem:

entity FLOP is

port (D, CLK : in std_ulogic;

Q : out std_ulogic);

end FLOP;

architecture A of FLOP is

begin

process

begin

wait until CLK'event and CLK='1';

Q <= D;

end process;

end A;

Wyjście Q jest uaktualniane tylko wówczas gdy CLK się zmieniło i gdy jest '1' czyli w

odpowiedzi na narastające zbocze. Proces jest taktowany sygnałem zegarowym CLK.

Narastającego zbocze może zostać również wykryte za pomocą następującej sekwencji

instrukcji:

process (CLK)

begin

if (CLK'event and CLK='1') then

Q <= D;

end if;

end process;

lub za pomocą:

library IEEE;

use IEEE.Std_Logic_1164.all;

...

process

begin

Język opisu sprzętu VHDL

- 35 -

wait until RISING_EDGE(CLK);

Q <= D;

end process;

Ostatni sposób nie zawsze jest dostępny.

Przerzutnik przezroczysty typu "latch" może zostać zaimplementowany w następujący

sposób:

process (EN, D)

begin

if (EN = '1') then

Q <= D;

end if;

end process;

Gdy EN=1 to przerzutnik jest przezroczysty, gdy nie to podtrzymuje poprzednią

wartość. Jest to tzw. "incomplete assigment" występujący wówczas gdy wartość jest

przypisana do zmiennej w jednej części instrukcji if, a w innej nie.

Poniżej przedstawiono implementacje wybranych typów przerzutników. Są to kolejno:

•

przerzutnik typu D z asynchronicznym wejściem zerującym,

•

przerzutnik typu D z synchronicznym wejściem zerującym,

•

przerzutnik typu D wyzwalany zboczem narastającym,

•

przerzutnik D typu latch,

•

przerzutnik D typu latch z asynchronicznym wejściem zerującym.

-- D F/F with asynchronous Reset

-- CLK: in STD_LOGIC;

-- RESET: in STD_LOGIC;

-- DIN: in STD_LOGIC;

-- DOUT: out STD_LOGIC;

process (CLK, RESET)

begin

if RESET='1' then --asynchronous RESET active High

DOUT <= '0';

elsif (CLK'event and CLK='1') then --CLK rising edge

DOUT <= DIN;

end if;

end process;

-- D F/F with synchronous Reset

-- CLK: in STD_LOGIC;

-- RESET: in STD_LOGIC;

-- DIN: in STD_LOGIC;

-- DOUT: out STD_LOGIC;

process (CLK)

begin

if CLK'event and CLK='1' then --CLK rising edge

if RESET='1' then

--synchronous RESET active High

- 36 -

Język opisu sprzętu VHDL

DOUT <= '0';

else

DOUT <= DIN;

end if;

end if;

end process;

-- D Flip-Flop

-- CLK: in STD_LOGIC;

-- DIN: in STD_LOGIC;

-- DOUT: out STD_LOGIC;

process (CLK)

begin

if CLK'event and CLK='1' then --CLK rising edge

DOUT <= DIN;

end if;

end process;

-- D Latch

-- GATE: in STD_LOGIC;

-- DIN: in STD_LOGIC;

-- DOUT: out STD_LOGIC;

process (GATE, DIN)

begin

if GATE='1' then --GATE active High

DOUT <= DIN;

end if;

end process;

-- D Latch with Reset

-- GATE: in STD_LOGIC;

-- RESET: in STD_LOGIC;

-- DIN: in STD_LOGIC;

-- DOUT: out STD_LOGIC;

process (GATE, DIN, RESET)

begin

if RESET='1' then --RESET active High

DOUT <= '0';

elsif GATE='1' then --GATE active High

DOUT <= DIN;

end if;

end process;

4.3.

Czterobitowy rejestr z równoległym ładowaniem i

asynchronicznym zerowaniem

Przykład rejestru czterobitowego z równoległym ładowaniem i asynchronicznym

zerowaniem przedstawiono poniżej.

-- 4-bit parallel load register with asynchronous reset

Język opisu sprzętu VHDL

- 37 -

-- CLK: in STD_LOGIC;

-- ASYNC: in STD_LOGIC;

-- LOAD: in STD_LOGIC;

-- DIN: in STD_LOGIC_VECTOR(3 downto 0);

-- DOUT: out STD_LOGIC_VECTOR(3 downto 0);

process (CLK, ASYNC)

begin

if ASYNC='1' then

DOUT <= "0000";

elsif CLK='1' and CLK'event then

if LOAD='1' then

DOUT <= DIN;

end if;

end if;

end process;

4.4.

Czterobitowy binarny licznik asynchroniczny

Poniżej przedstawiono implementację czterobitowego binarnego licznika

asynchronicznego.

-- 4-bit asynchronous binary counter

-- CLK: in STD_LOGIC;

-- RESET: in STD_LOGIC;

-- COUNT: out STD_LOGIC_VECTOR(3 downto 0);

-- The declaration of the auxiliary signal COUNTER must be inserted in

-- the architecture declarative part.

-- The output port "COUNT" cannot appear on the right side of assignment

-- statements.

signal COUNTER: STD_LOGIC_VECTOR(3 downto 0);

process (CLK, COUNTER, RESET)

begin

if RESET='1' then

COUNTER <= "0000";

else

if CLK'event and CLK='1' then

COUNTER(0) <= not COUNTER(0);

end if;

if COUNTER(0)'event and COUNTER(0)='0' then

COUNTER(1) <= not COUNTER(1);

end if;

if COUNTER(1)'event and COUNTER(1)='0' then

COUNTER(2) <= not COUNTER(2);

end if;

if COUNTER(2)'event and COUNTER(2)='0' then

COUNTER(3) <= not COUNTER(3);

- 38 -

Język opisu sprzętu VHDL

end if;

end if;

end process;

COUNT <= COUNTER;

4.5.

Konwerter kodu BCD na kod wyświetlacza siedmiosegmentowego

W przypadku układów wykorzystujących wyświetlacze siedmiosegmentowe LED

częstym problemem jest przekodowanie liczby w zakresie od 0 do 9 zapisanej w kodzie BCD

na kod wyświetlacza. Poniżej przedstawione zostało rozwiązanie tego problemu. Ciągi bitowe

zwracane w zmiennej LED sterują poprawnie poszczególnymi segmentami wyświetlacza

jeżeli zostały one podłączone do kolejnych bitów w sposób objaśniony w komentarzu.

--HEX-to-seven-segment decoder

-- HEX:

in

STD_LOGIC_VECTOR (3 downto 0);

-- LED:

out

STD_LOGIC_VECTOR (6 downto 0);

--

-- podlaczenie segmentow wyswietlacza

-- do kolejnych bitow zmiennej LED

-- 0

-- ---

-- 5 | | 1

-- --- <- 6

-- 4 | | 2

-- ---

-- 3

with HEX select

LED<= "1111001" when "0001", --1

"0100100" when "0010", --2

"0110000" when "0011", --3

"0011001" when "0100", --4

"0010010" when "0101", --5

"0000010" when "0110", --6

"1111000" when "0111", --7

"0000000" when "1000", --8

"0010000" when "1001", --9

"0001000" when "1010", --A

"0000011" when "1011", --b

"1000110" when "1100", --C

"0100001" when "1101", --d

"0000110" when "1110", --E

"0001110" when "1111", --F

"1000000" when others; --0

4.6.

Multiplekser 4 na 1

Poniższy przykład realizuje multiplekser o czterech wejściach A, B, C, D oraz jednym

wyjściu MUX_OUT. Sygnał SEL pełni rolę wejścia adresowego.

Język opisu sprzętu VHDL

- 39 -

-- 4 to 1 multiplexer design with case construct

-- SEL: in STD_LOGIC_VECTOR(0 to 1);

-- A, B, C, D:in STD_LOGIC;

-- MUX_OUT: out STD_LOGIC;

process (SEL, A, B, C, D)

begin

case SEL is

when "00" => MUX_OUT <= A;

when "01" => MUX_OUT <= B;

when "10" => MUX_OUT <= C;

when "11" => MUX_OUT <= D;

when others => MUX_OUT <= 'X';

end case;

end process;

4.7.

Czterobitowy rejestr przesuwający

Poniżej przedstawiono realizację czterobitowego rejestru przesuwnego o szeregowym

wejściu oraz o szeregowym wyjściu.

-- 4-bit serial-in and serial-out shift register

-- CLK: in STD_LOGIC;

-- DIN: in STD_LOGIC;

-- DOUT: out STD_LOGIC;

process (CLK)

variable REG: STD_LOGIC_VECTOR(3 downto 0);

begin

if CLK'event and CLK='1' then

REG := DIN & REG(3 downto 1);

end if;

DOUT <= REG(0);

end process;

4.8.

Czterobitowy licznik synchroniczny z wejściem zezwalającym na

zliczanie, asynchronicznym zerowaniem i synchronicznym

ładowaniem

Poniżej widoczna jest implementacja czterobitowego licznika synchronicznego z

wejściem zezwalającym na zliczanie, asynchronicznym zerowaniem i synchronicznym

wpisem równoległym.

-- 4-bit synchronous counter with count enable, asynchronous reset and synchronous load

-- CLK: in STD_LOGIC;

-- RESET: in STD_LOGIC;

-- CE, LOAD, DIR: in STD_LOGIC;

- 40 -

Język opisu sprzętu VHDL

-- DIN: in INTEGER range 0 to 15;

-- COUNT: out INTEGER range 0 to 15;

process (CLK, RESET)

--auxiliary variable COUNTER declaration

--the output port "COUNT" cannot appear on the right side of assignment

-- statements

variable COUNTER: INTEGER range 0 to 15;

begin

if RESET='1' then

COUNTER := 0;

elsif CLK='1' and CLK'event then

if LOAD='1' then

COUNTER := DIN;

else

if CE='1' then

if DIR='1' then

if COUNTER = 15 then

COUNTER := 0;

else

COUNTER := COUNTER + 1;

end if;

else

if COUNTER = 0 then

COUNTER := 15;

else

COUNTER := COUNTER - 1;

end if;

end if;

end if;

end if;

end if;

COUNT <= COUNTER;

end process;

4.9.

Bufor trójstanowy

Poniżej przedstawiono przykład realizacji bufora trójstanowego.

-- Tristate Buffer

-- ENABLE: in STD_LOGIC;

-- DIN: in STD_LOGIC;

-- DOUT: out STD_LOGIC;

DOUT <= DIN when ENABLE='1' else 'Z';

4.10. Funkcja konwersji typu bit_vector do typu integer

Język opisu sprzętu VHDL

- 41 -

W języku VHDL ciągi bitów nie reprezentują sobą żadnej wartości. Poniżej

przedstawiono przykład funkcji, która przyjmuje jako argument wektor bitowy i zwraca

odpowiadającą mu w kodzie binarnym liczbę całkowitą.

function bit_vec2int(A : BIT_VECTOR) return integer is

variable RESULT: integer:=0;

variable TMP: integer:=1;

begin

if A'length = 0

then return RESULT;

end if;

for i in A'reverse_range loop

if a(i)='1'

then RESULT:=RESULT+TMP;

end if;

TMP:=TMP*2;

end loop;

return RESULT;

end;

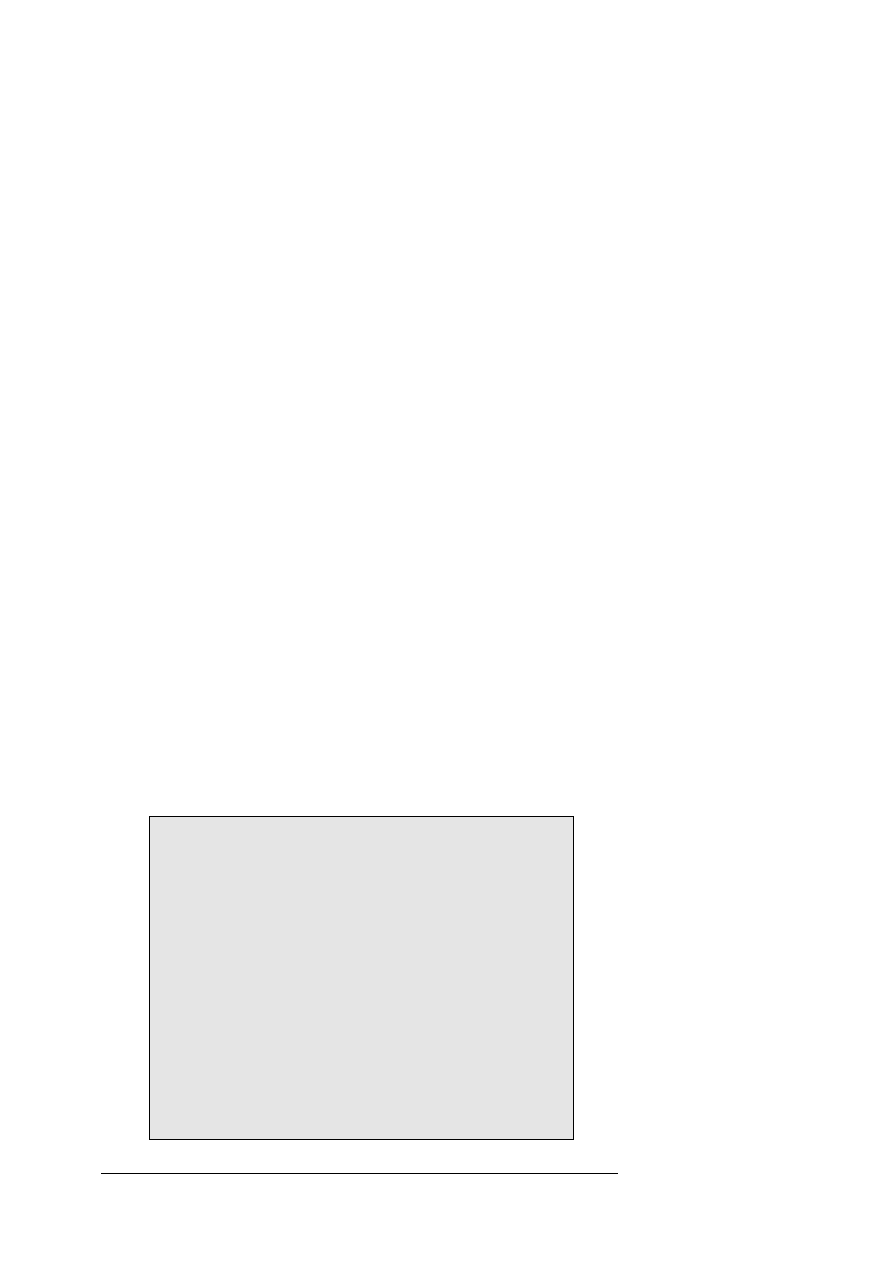

4.11. Automat o skończonej liczbie stanów

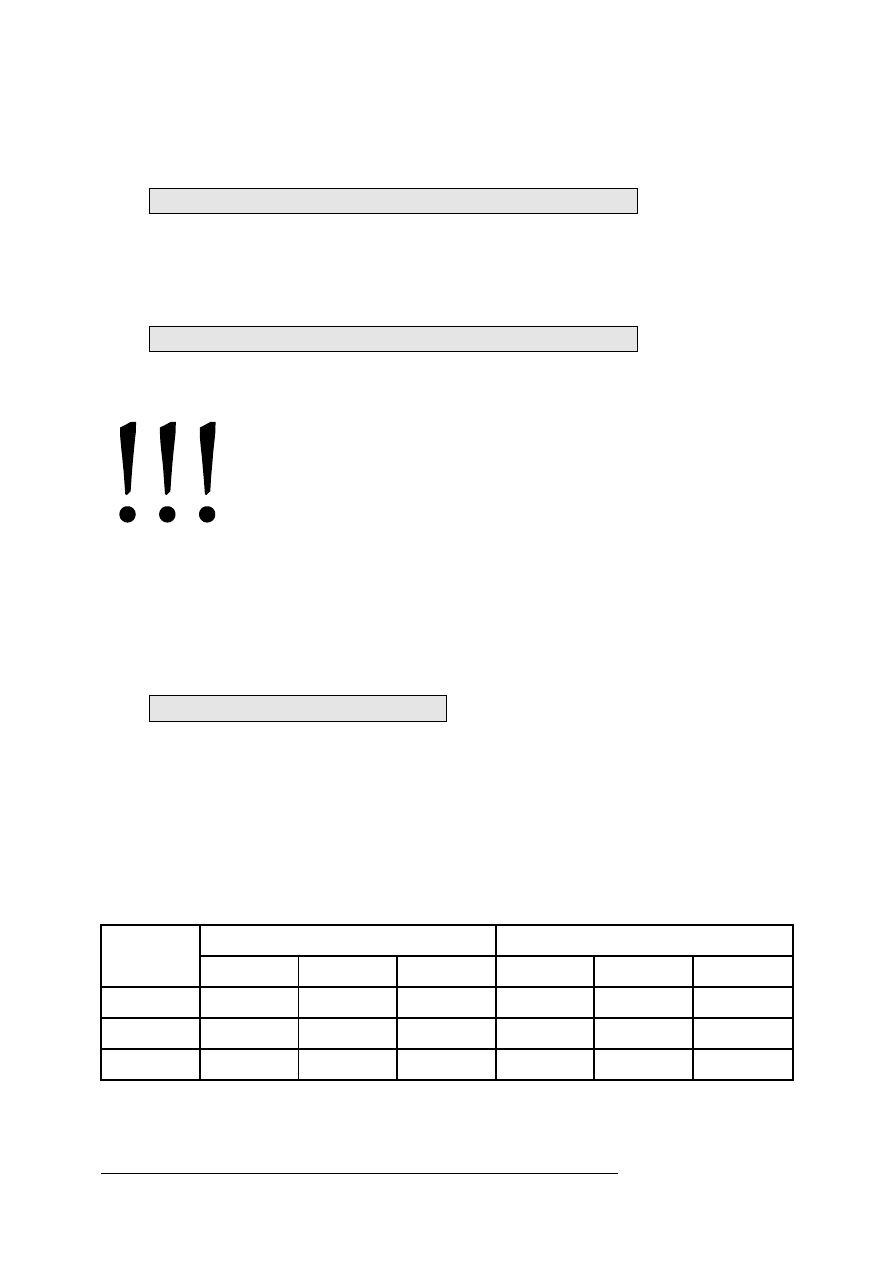

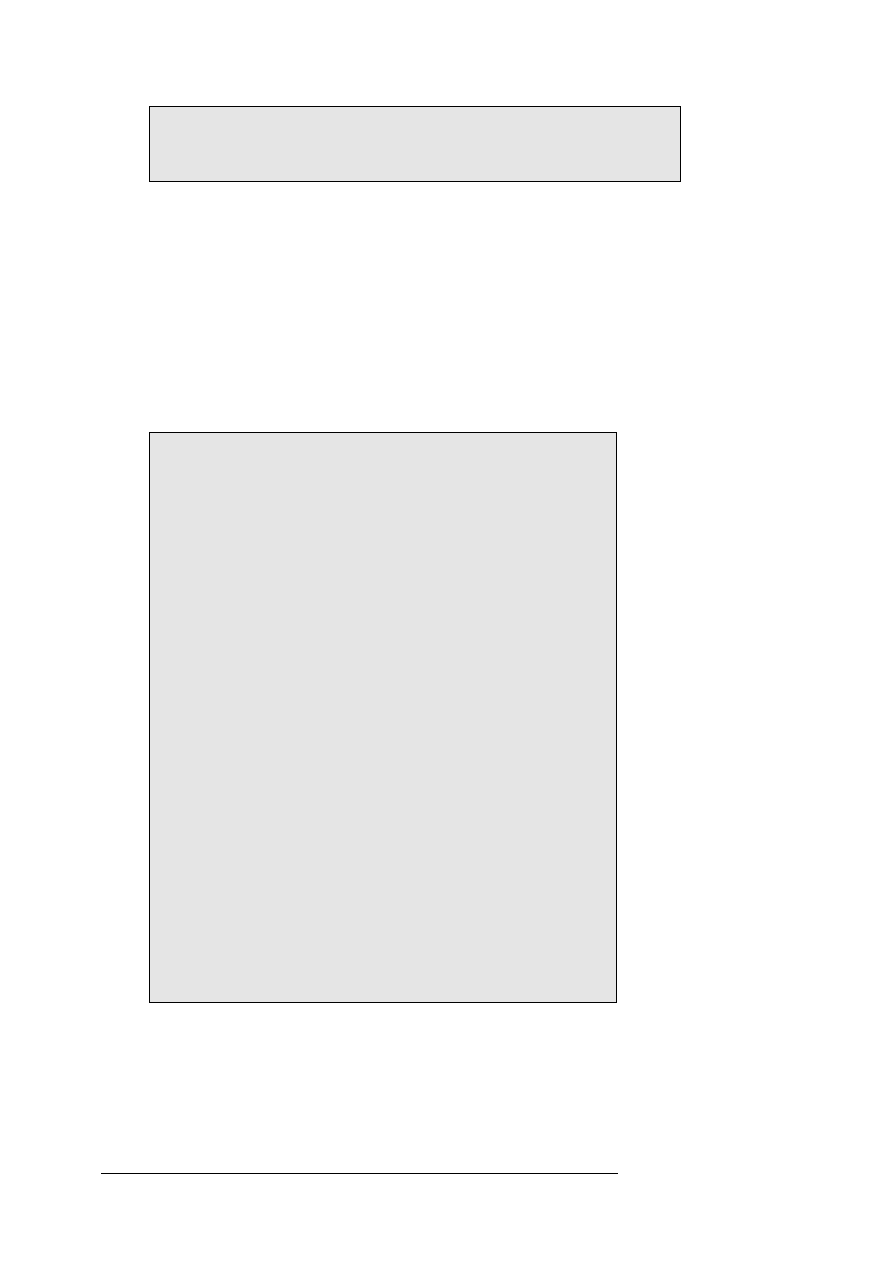

Automat o skończonej liczbie stanów( FSM - ang. Finite State Machine) składa się ze

skończonej, określonej liczby stanów oraz operacji definiujących przejścia miedzy stanami.

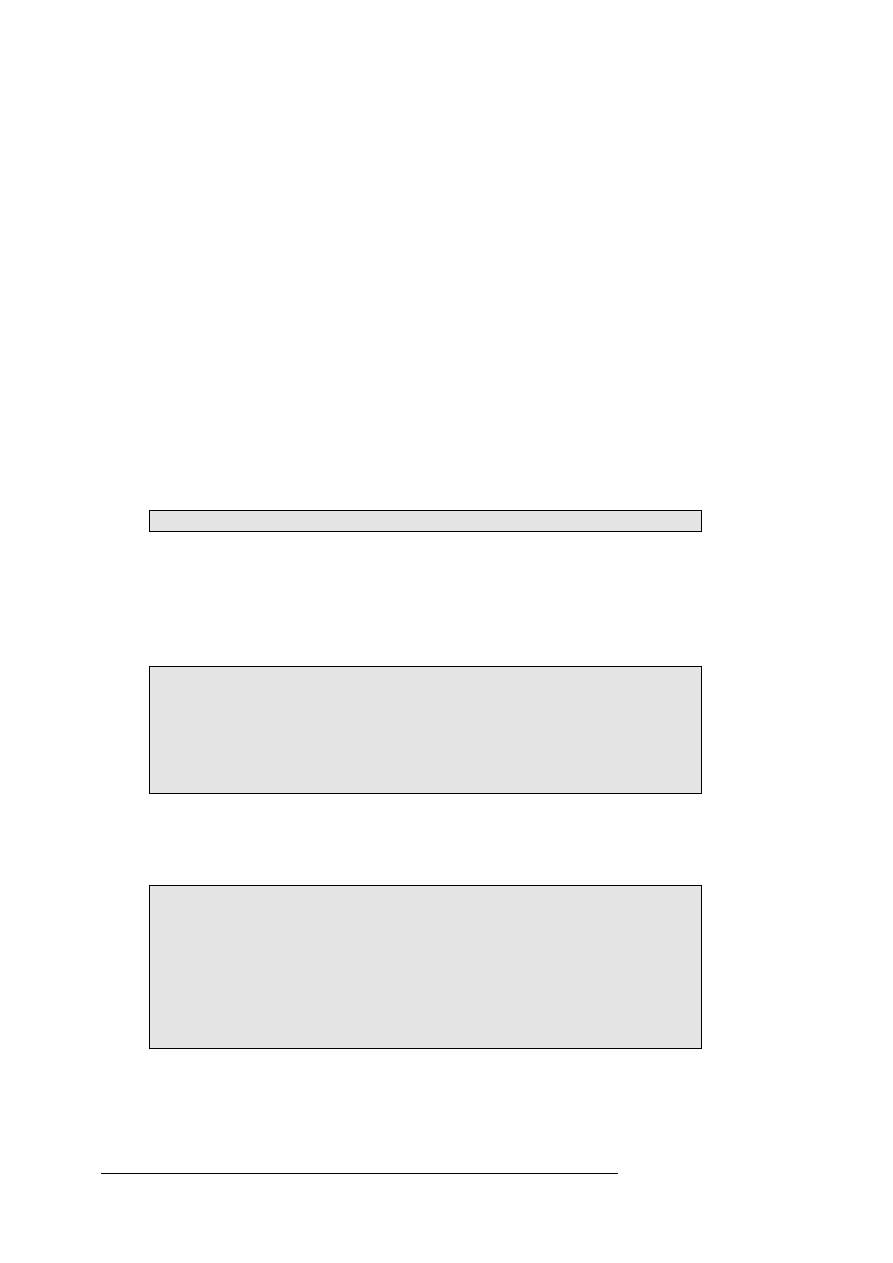

Ogólna struktura maszyny stanowej przedstawiona jest na rysunku poniżej:

Rejestr

Stanu

Wyjście

Następny

Stan

Zegar

Rys.4.1. Struktura automatu FSM.

Zdefiniujmy FSM posiadającą cztery stany typu definiowanego przez użytkownika:

architecture RTL of FSM is

type T_STATE is (IDLE, RW_CYCLE, INT_CYCLE, DMA_CYCLE);

signal NEXT_STATE, STATE : T_STATE;

begin

...

- 42 -

Język opisu sprzętu VHDL

Zdefiniowane są trzy sygnały wejściowe: RW,INT_REQ oraz DMA_REQ. Ogólny format

maszyny FSM wygląda w sposób następujący:

NS: process(STATE,RW,INT_REQ,DMA_REQ)

begin

case STATE is

when IDLE =>

-- statements

when RW_CYCLE =>

-- statements

when INT_CYCLE =>

-- statements

when DMA_CYCLE =>

-- statements

end case;

end process NS;

Szczegółowa implementacja może posiadać postać:

NS: process(STATE,RW,INT_REQ,DMA_REQ)

begin

NEXT_STATE <= STATE;

case STATE is

when IDLE =>

if (INT_REQ = '1') then

NEXT_STATE <= INT_CYCLE;

elsif (DMA_REQ = '1') then

NEXT_STATE <= DMA_CYCLE;

end if;

when RW_CYCLE =>

-- statements

...

end process NS;

Proces NS jest czuły na wejścia oraz sygnał stanu. Każda gałąź case definiuje nową wartość

stanu.

Implementacja rejestru stanu może przybrać postać:

REG : process (CLK, RST)

begin

if RST = '1' then

STATE <= IDLE;

elsif CLK'event and CLK ='1' then

STATE <= NEXT_STATE;

end if;

end process REG;

Język opisu sprzętu VHDL

- 43 -

4.12. Implementacja układów z rodziny TTL

Poniżej przedstawiono dwa przykłady realizacji w języku VHDL układów rodziny

TTL. Zwykle każda implementacja języka zawiera odpowiednią bibliotekę definiującą funkcje

najbardziej popularnych układów scalonych z rodzin TTL oraz CMOS.

4.12.1.

Implementacja układu 7400

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \74S00\ IS PORT(

I0_A : IN std_logic;

I0_B : IN std_logic;

I0_C : IN std_logic;

I0_D : IN std_logic;

I1_A : IN std_logic;

I1_B : IN std_logic;

I1_C : IN std_logic;

I1_D : IN std_logic;

O_A : OUT std_logic;

O_B : OUT std_logic;

O_C : OUT std_logic;

O_D : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END \74S00\;

ARCHITECTURE model OF \74S00\ IS

BEGIN

O_A <= NOT ( I0_A AND I1_A ) AFTER 5 ns;

O_B <= NOT ( I0_B AND I1_B ) AFTER 5 ns;