Laboratorium 4– Zegar

1. Zegar

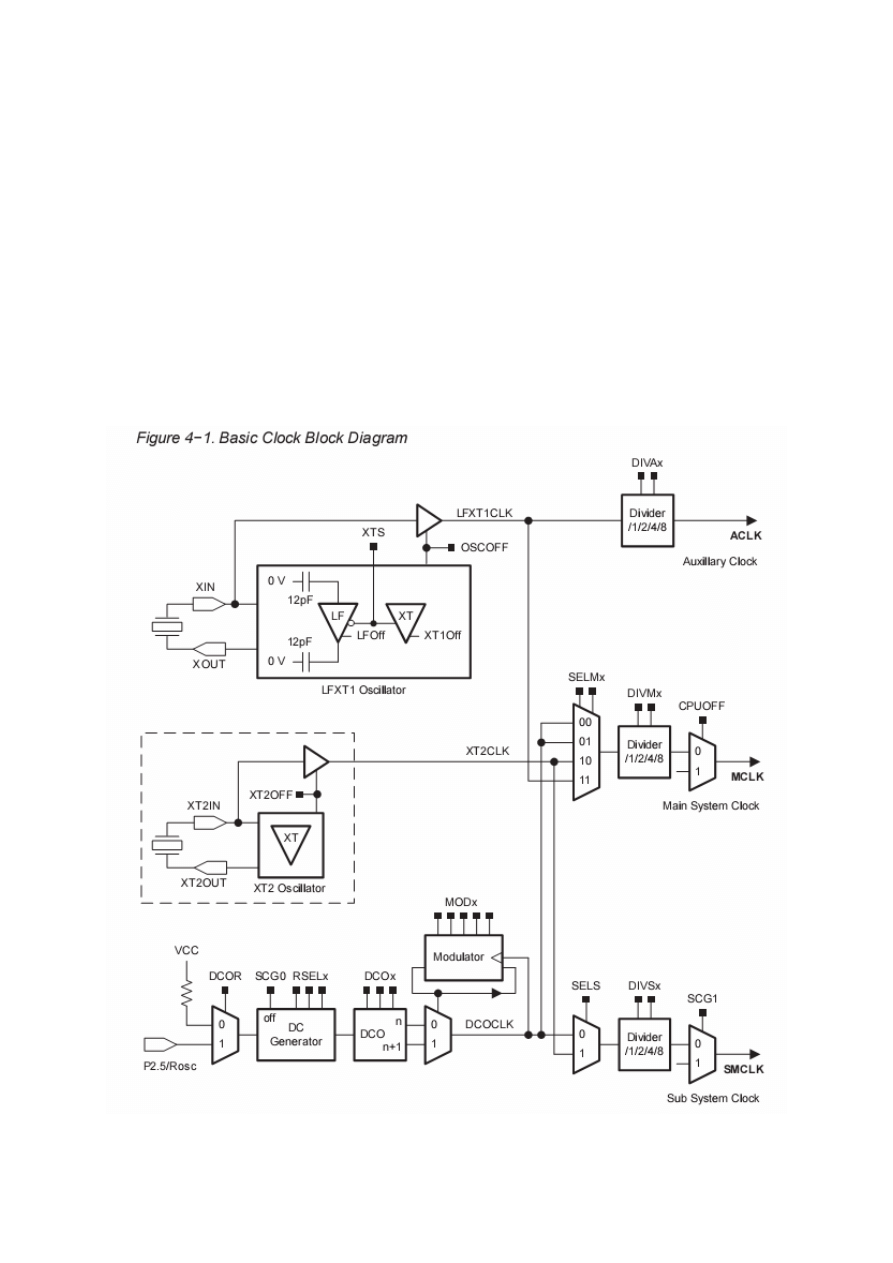

5.1. Basic Clock Module

Podstawą czasu w układzie MSP430 może być jeden z zegarów:

• LFXT1CLK (Low Frequency/High Frequency Oscillator ) – może on być użyty z

niskoczęstotliwościowym kwarcem 32678Hz, bądź z rezonatorami z zakresu 450kHz- 8MHz

(tryb pracy wysokoczęstotliwościowej)

• XT2CLK (High Frequency Oscillator) jest używany opcjonalnie może być zasilany

standardowym kwarcem, bądź rezonatorami z zakresu 450kHz- 8MHz

• DCO- wewnętrzny zegar taktujący posiadający charakterystykę RC

Poszczególne komponenty mikrokontrolera mogą być sterowane zegarami :

• ACLK (Auxilary Clock) –zegar pomocniczy jego źródłem jest LFXT1CLK

• MCLK (Main Clock) – zegar używany przez CPU oraz system, jego źródłem może być

LFXT1CLK, bądź XT2CLK, bądź DCO.

• SMCLK (Sub-main Clock)- jest przeznaczony do współpracy z urządzeniami

peryferyjnymi, jego źródłem może być :LFXT1CLK, bądź XT2CLK, bądź DCO.

Po restarcie standardowo zegar procesora jest ustawiany na DCO. DCO generuje

częstotliwość około 800 kHz, jednak jest to częstotliwość niezbyt stabilna.

Aby ustawić taktowanie z rezonatora kwarcowego 8MHz wbudowanego w EasyWeb, należy

wybrać źródło zegara podstawowego Basic Clock na taktowanie przez LFXT1CLK,

Operacje, które należy wykonać są następujące:

1. Włączenie oscylatora

2. Wyczyszczenie flagi OFIFG

3. Odczekanie około 50µs

4. Sprawdzenie stanu flagi OFIFG jeśli jest nadal ustawiona to powtórzenie

kroków 1-4

5. Zmiana taktowania zegarów w rejestrze BCSCTL2

Przykładowy kod realizujący ustawienie zegara podstawowego może być następujący:

// Basic Clock Module ustawiamy na ACLK(zegar 8 MHz )

BCSCTL1 |= XTS; //ACLK = LFXT1 = HF XTAL 8MHz

do

{

IFG1 &= ~OFIFG; // Czyszczenie flgi OSCFault

for (i = 0xFF; i > 0; i--); // odczekanie

}

while ((IFG1 & OFIFG) == OFIFG); // dopóki OSCFault jest ci

ą

gle ustawiona

BCSCTL1 |= DIVA_0; // ACLK=8 MHz – bez podzielników

BCSCTL2 |= SELM0 | SELM1; // MCLK= LFTX1 =ACLK

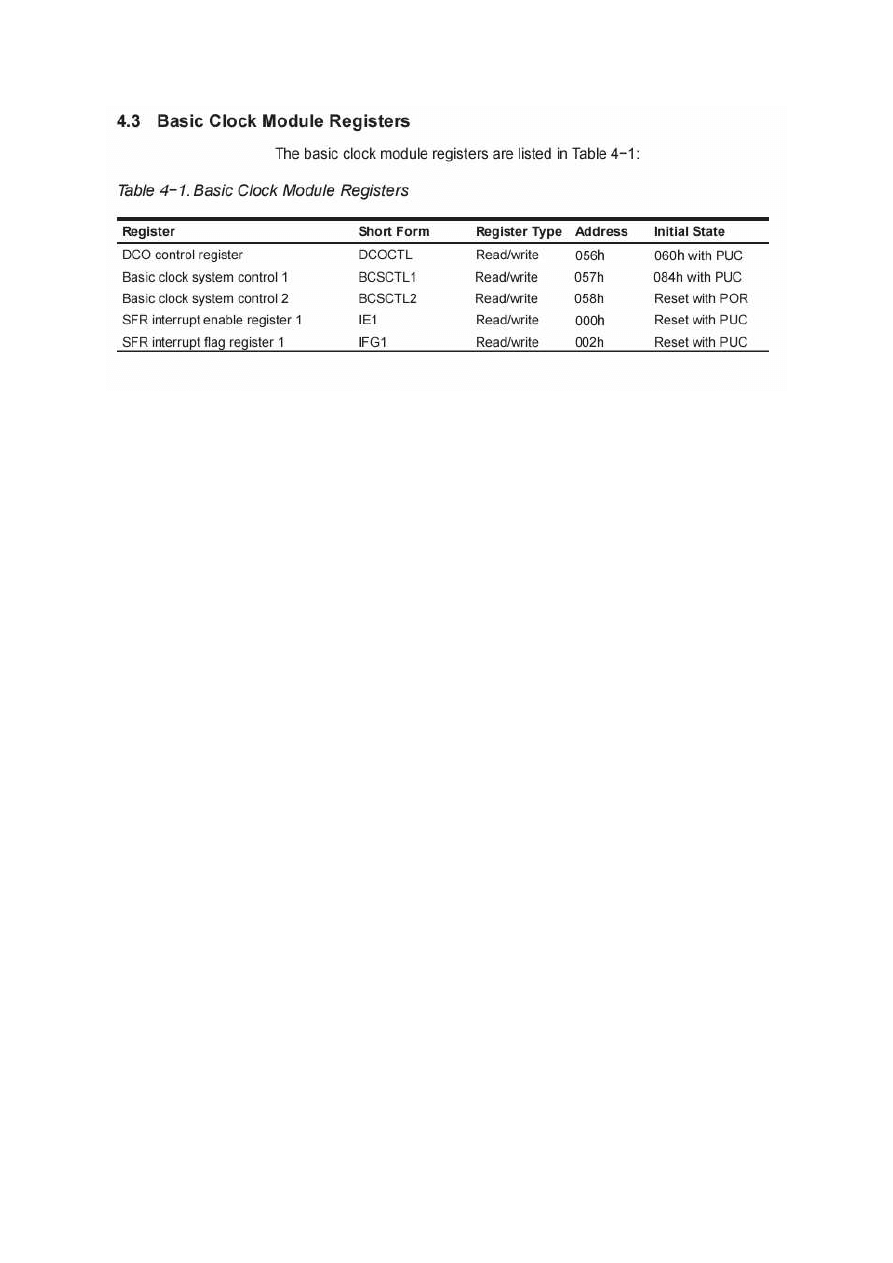

Inne ustawienia podstawowego zegara można wpisać do rejestrów Basic CLock Module:

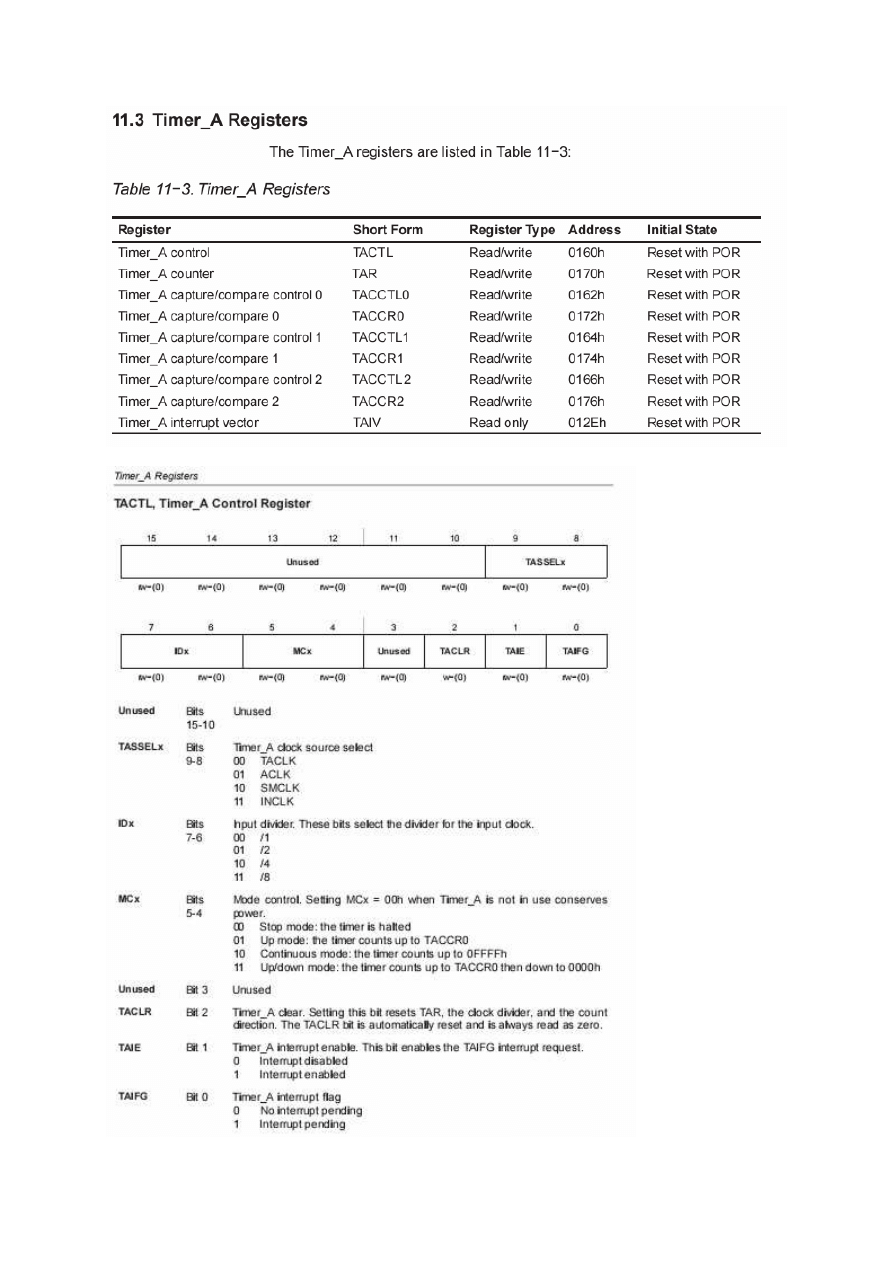

5.2. Timer A

TimerA może być inkrementowany bądź dekrementowany, ma to miejsce z

każdym narastającym zboczem zegara. Może być programowo czytany oraz

zapisywany. Dodatkowo w przypadku wystąpienia przepełnienia jest generowane

przerwanie. Źródłem zegara taktującego TimerA mogą być

(TACLK,ACLK,SMCLK,INCLK), dodatkowo istnieje możliwość podziału

częstotliwości sygnału taktującego przez 1,2,4,8. TimerA ma możliwość pracowania

w czterech trybach pracy, za ich ustawienie odpowiada znacznik MCx w rejestrze

TACTL.

Są to tryby pracy:

• Stop – MC=00 – Timer jest zatrzymany

• Up – MC=01 – Timer cyklicznie liczy od zera do wartości zapisanej w

rejestrze TACCR0

• Continuous- MC-10- Timer cyklicznie liczy od zera do wartości 0xffff

• Up/Down – MC=11- Timer cyklicznie inkrementuje od zera do wartości

zapisanej w rejestrze TACCR0 , a dekrementuje od wartości w rejestrze

TACCR0 do zera

Tryb Compare jest stosowany do generowania sygnałów wyjściowych PWM, oraz

do generowania przerwań w określonym odstępie czasowy. Przerwanie jest

generowane w przypadku gdy wartość w rejestrze TAR zostanie doliczona do

wartości w rejestrze TACCRx.

Aktywacja układu TimerA polega na przyporządkowaniu mu odpowiedniego zegara,

ustawieniu podzielników i włączeniu przerwań.

Ustawienia dokonujemy poprzez rejestry układu Timer A:

Najważniejsze dane wpisujemy do rejestru TACTL

Poniżej przykładowy kod realizujący ustawienie Timera A do pracy z przerwaniami :

TACTL = TASSEL_1 + MC_1 +ID_2; // Wybieram ACLK, ACLK/4=2MHz,tryb Up

CCTL0 = CCIE; // wł

ą

czenie przerwa

ń

od CCR0

CCR0=2000; // Przerwanie generowane co 1 ms

Procedura obsługi przerwania od Timer A

// procedura obsługi przerwania od TimerA

#pragma vector=TIMERA0_VECTOR

__interrupt void Timer_A (void)

{

++licznik;

P2OUT ^=BIT1; //zapal diod

ę

}

Zadania

1.

Napisać program wyświetlający sekundy od 0 do 60, bazując na układzie Timer A.

Ustawić źródło częstotliwości zegara podstawowego (Basic Clock Module) na ACLK,

1 MHz. Ustawić źródło zegara Timer A na częstotliwość 250 kHz. Program ma

działać w oparciu o przerwania generowane co 100 ms.

2.

Napisać program realizujący zegar wyświetlający bieżący czas (godzina: minuta:

sekunda). Zegar ma działać na układzie Timer A.

3.

Uzupełnić funkcjonalności zegara o możliwość ustawienia czasu za pomocą

wbudowanej klawiatury.

4.

Uzupełnić funkcjonalności zegara o stoper pracujący z rozdzielczością 0.01 sekundy.

5.

Uzupełnić funkcjonalności zegara o budzik z możliwością zdefiniowania kilku

alarmów. Wykorzystać wbudowany Buzzer do generowania dźwięku.

6.

Umożliwić ustawienie załączania przekaźników w wybranym czasie i na wybrany

okres (jako rozszerzenie funkcjonalności budzika)

7.

Zrealizować zegar na układzie Timer B

Wyszukiwarka

Podobne podstrony:

Kontrola badań laboratoryjnych

badania laboratoryjne 6

ROZRÓD Badanie terenowe i laboratoryjne mleka

Diagnostyka laboratoryjna chorób serca i mięśni poprzecz (2)

Diagnostyka laboratoryjna zaburzen gospodarki lek 2010

medycyna laboratoryjna

Medycyna laboratoryjna 12 13

7) Laboratoria EMG i MMG na pziomach sily i ko

3 1 5 CCNA1 Laboratorium pl

laboratorium2

C++ zegar

Laboratorium 7

więcej podobnych podstron