Systemy operacyjne – Rodzaje pamięci

Strona 1

Organizacja pamięci wewnętrznej komputerów

1. Własności systemów pamięci

2. Hierarchia pamięci.

3. Półprzewodnikowa pamięć główna

4. Pamięć cache.

5. Pamięć wirtualna.

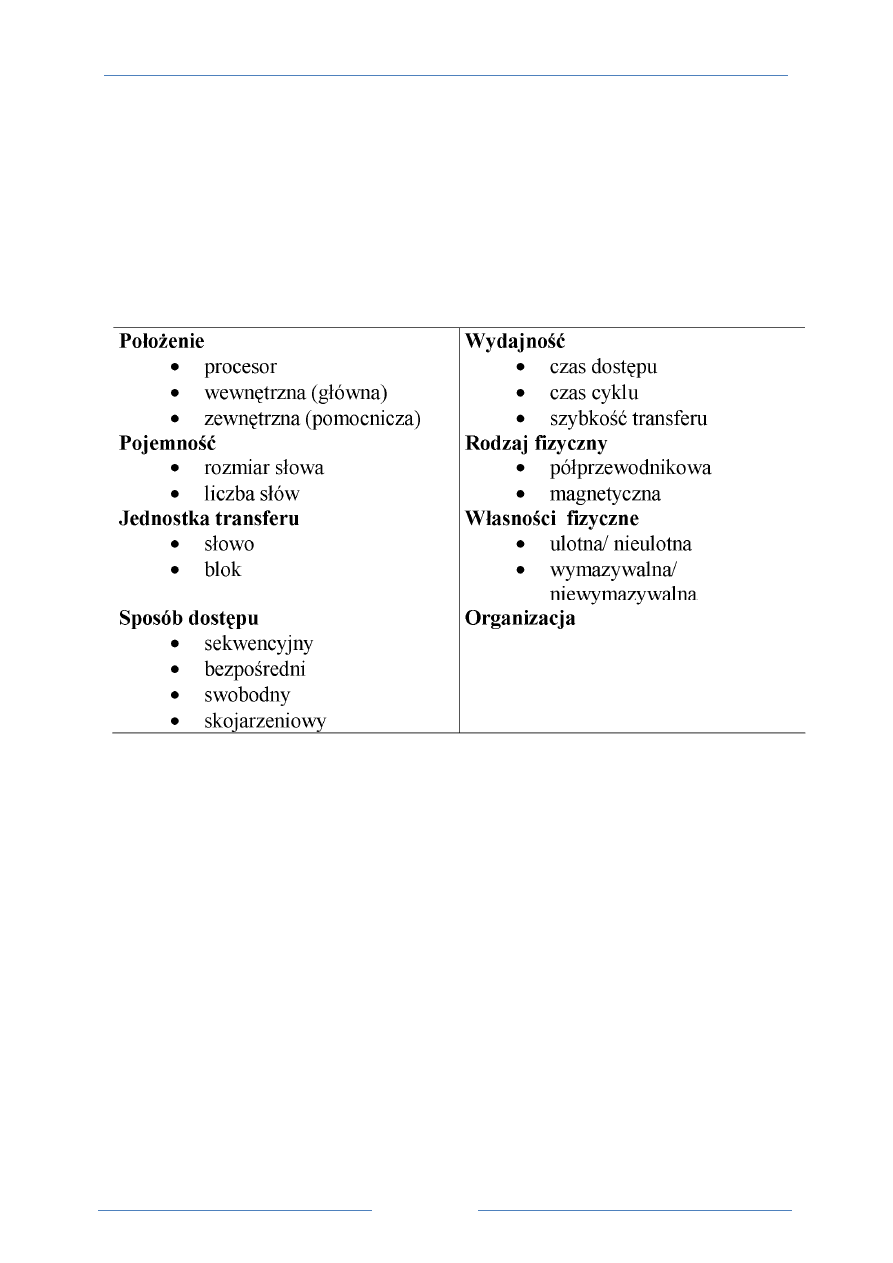

Własności systemów pamięci

Systemy operacyjne – Rodzaje pamięci

Strona 2

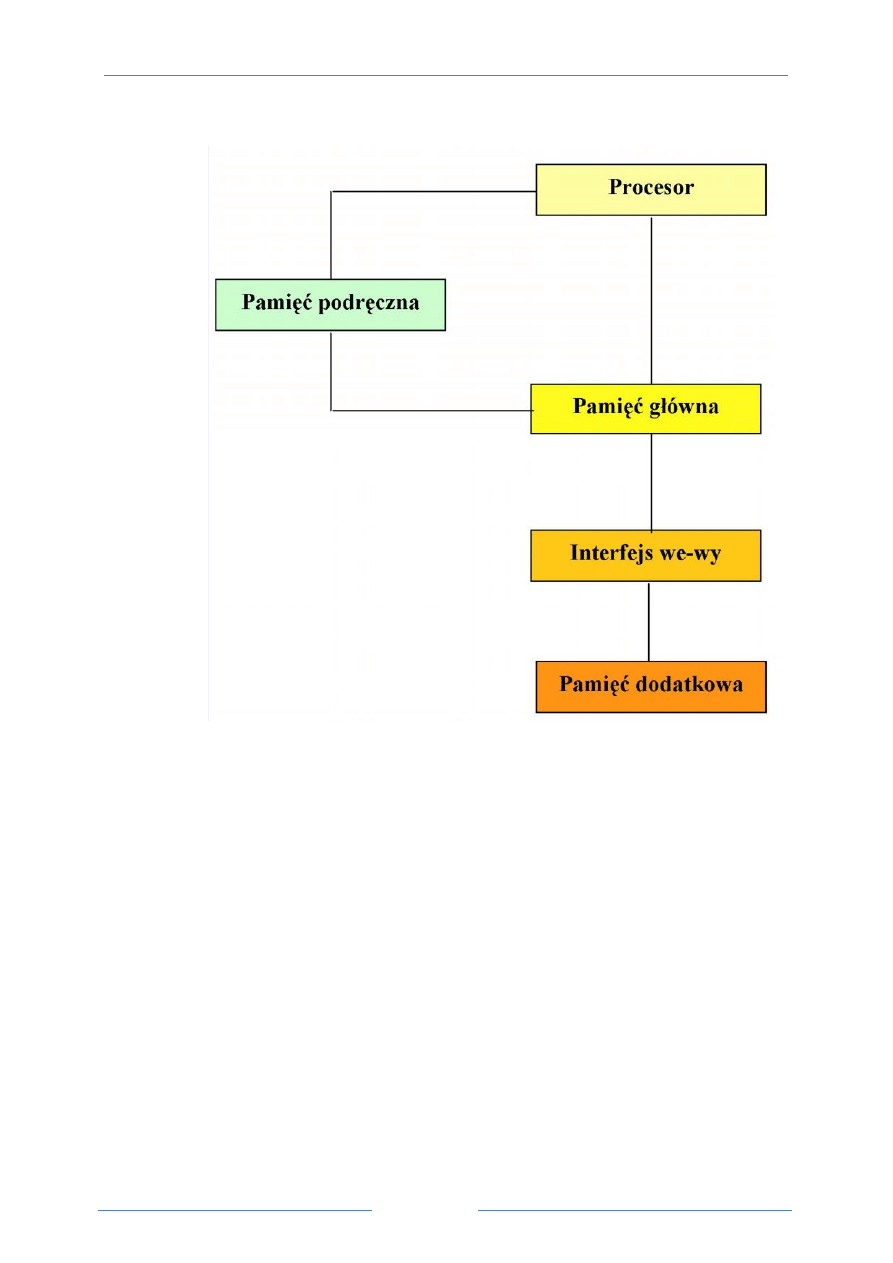

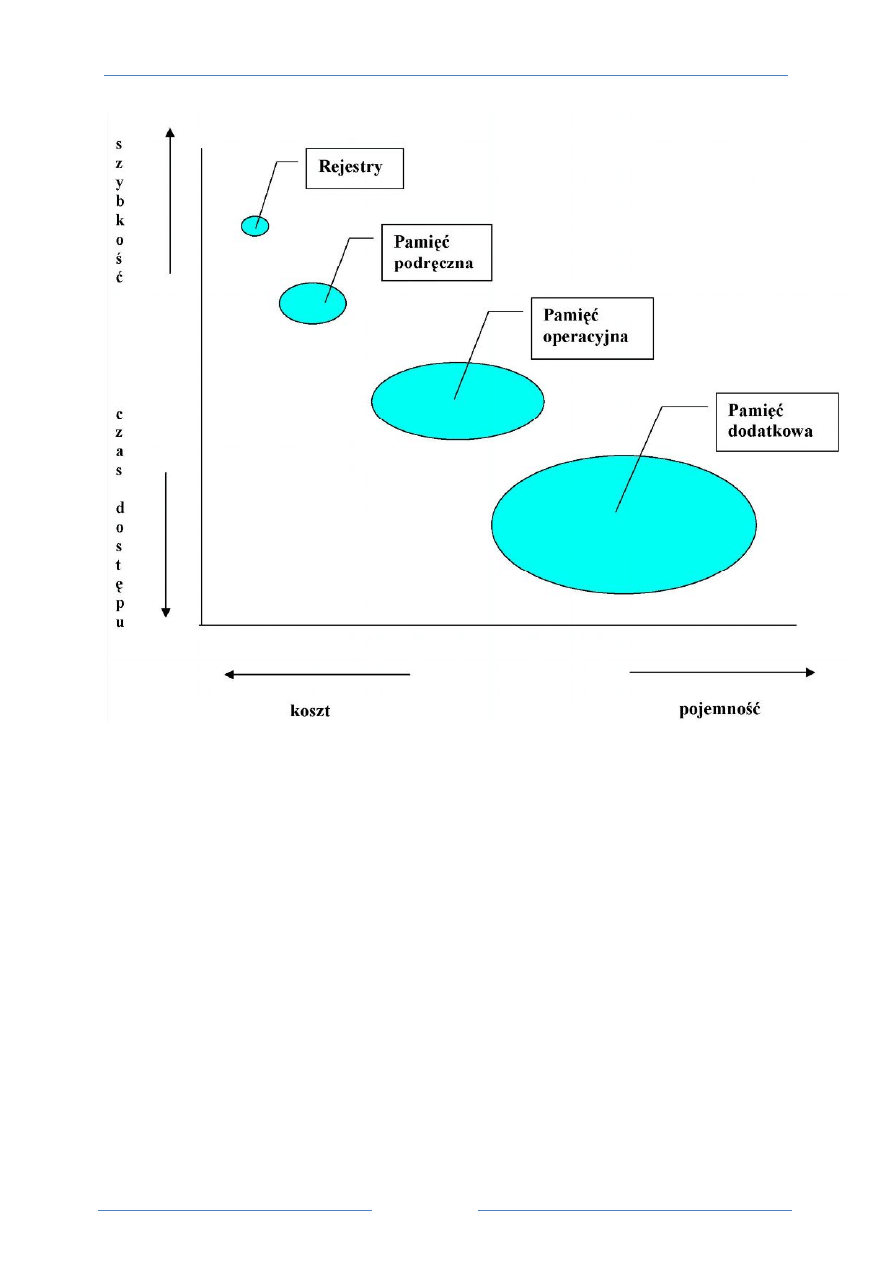

Hierarchia pamięci składa się z kilku poziomów przechowywania. Każdy

poziom charakteryzuje się inną szybkością działania i pojemnością,

Do wytworzenia elementów pamięci wykorzystuje się różne technologie:

- umożliwiającą szybki dostęp do danych (technologia półprzewodnikowa),

- technologie wykorzystywane do wytworzenia powierzchni magnetycznych i

optycznych dla elementów zewnętrznych, oddalonych od procesora.

Jeśli rozpatrujemy dostępne technologie, to możemy zauważyć następujące

zależności:

□ mniejszy czas dostępu - większy koszt na bit,

□ większa pojemność - mniejszy koszt na bit,

□ większa pojemność - większy czas dostępu.

Hierarchia pamięci:

Systemy operacyjne – Rodzaje pamięci

Strona 3

1. Rejestry wewnętrzne procesora (pamięć procesora) - implementowana

jako zbiór szybkich rejestrów, zajmuje najwyższy poziom hierarchii;

2. Pamięć podręczna „cache” umiejscowiona jest między procesorem a

pamięcią operacyjną, a do jej realizacji używa się zwykle droższych

układów pamięci statycznej;

3. Pamięć operacyjna jest największym obszarem pamięci, dostępnym

bezpośrednio dla procesora. W celu obniżenia kosztu pamięć operacyjna

jest realizowana z wykorzystaniem układów pamięci dynamicznej.

4. Pamięć wirtualna (nierzeczywista), wolniejsza, odwzorowywana

zwykle na pamięciach zewnętrznych, typowo na dyskach twardych.

Przesłania PAO/PW są zwykle kontrolowane przez system operacyjny

i wspomagane sprzętowo przez specjalne mechanizmy, wbudowane w

procesory

Systemy operacyjne – Rodzaje pamięci

Strona 4

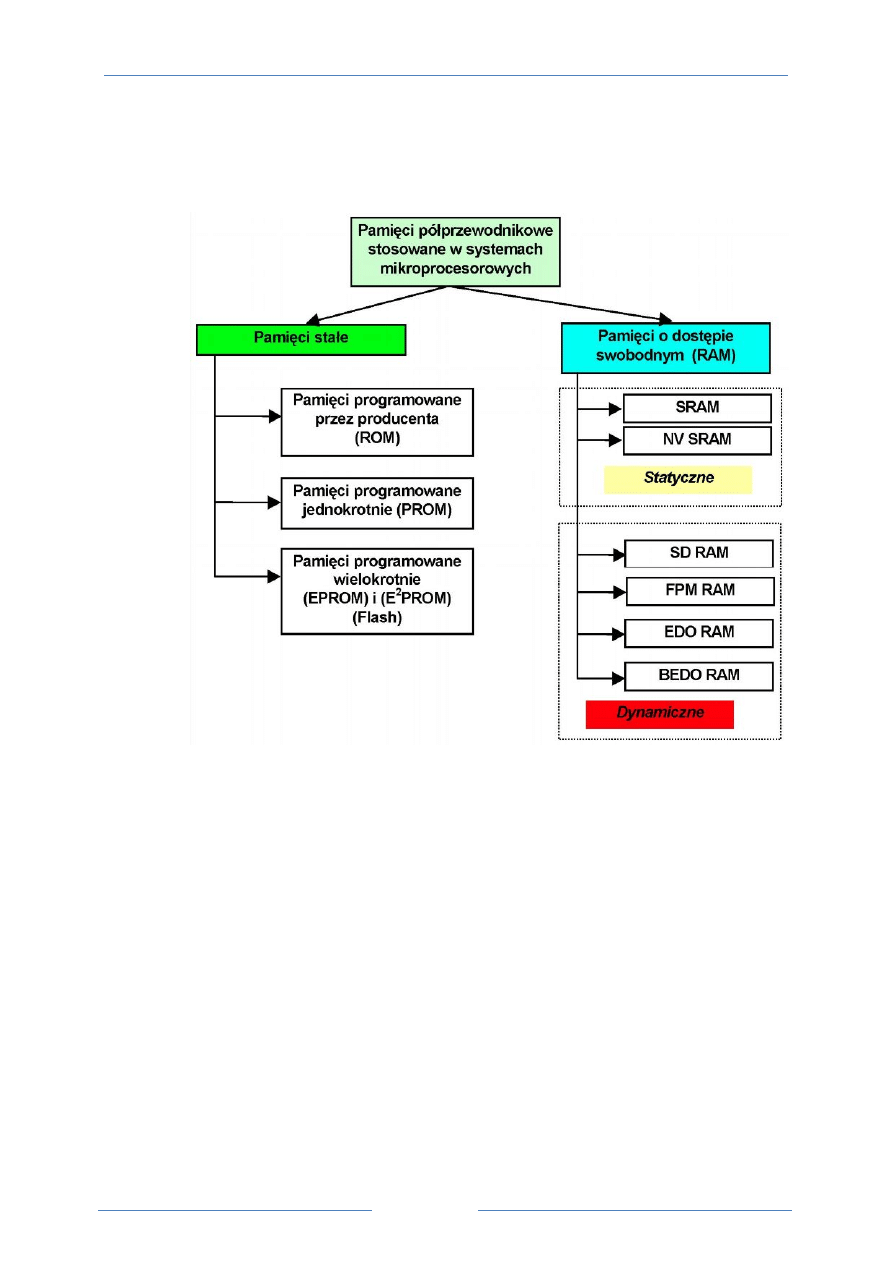

Dynamiczna pamięć RAM jest wykonana z komórek, które przechowują dane

podobnie, jak kondensatory przechowują ładunek elektryczny. Obecność lub

brak ładunku w kondensatorze mogą być interpretowane jako binarne 1 i 0.

Dynamiczne pamięci RAM wymagają okresowego odświeżania ładunku w celu

zachowania danych.

W statycznych pamięciach RAM wartości binarne są przechowywane za

pomocą przerzutników. Statyczne pamięci RAM zachowują dane tak długo, jak

długo są zasilane.

Półprzewodnikowa pamięć główna

Podział pamięci półprzewodnikowych

Systemy operacyjne – Rodzaje pamięci

Strona 5

NV SRAM - jest to pamięć firmy Intel. Pamięć po wyłączeniu zasilania nie traci zawartości.

Uzyskano to dzi

ę

ki zastosowaniu w jednym układzie dwóch rodzajów pami

ę

ci : SRAM oraz

EEPROM. W czasie normalnej pracy jest ona widoczna jako normalna pami

ę

ć typu SRAM.

W momencie zaniku zasilania odpowiednim sygnałem podanym przez mikroprocesor cała

zawartość pami

ę

ci RAM jest przepisywana do pami

ę

ci EEPROM. Po powrocie napięcia

zasilania zawartość pami

ę

ci EEPROM jest ponownie przepisywana do SRAM. Producent

gwarantuje 10000 cykli.

EDO RAM - jest to typ pamięci, w której jeszcze gdy dane są odczytywane może zostać

wystawiony adres następnej komórki. Przyspiesza to znacznie odczyt kolejnych komórek

pamięci. Teoretyczny przyrost prędkości do 20% w porównaniu z pamięciami FPM RAM.

Zysk w praktyce maleje do kilku procent ponieważ danych nie można nakładkować przy

zapisie.

BEDO RAM - jest to pamięć stanowiąca połączenie technik „burst” i EDO RAM. Zamiast

jednego adresu odczytywane jest jednocześnie cztery. Na magistrali adresowej adres pojawia

się tylko na początku cyklu odczytu, co wydatnie skraca średni czas dostępu.

FPM RAM {Fast Page Mode)- jest to pamięć pracująca na zasadzie adresowania

stronicowego. Stronicowanie jest technika, zwiększenia wydajności pamięci, poprzez

podzielenie jej na strony mające długość od 512 bajtów do kilku kilobajtów. Zwykłe odczyty

i zapisy danych w pamięci wymagają, wybrania wiersza i kolumny, co zabiera dodatkowy

czas. Stronicowanie polega na udostępnianiu komórek z tego samego wiersza, dzięki czemu

należy zmieniać tylko adres kolumny.

SDRAM {Synchronous Dynamic RAM) - jest to pamięć dynamiczna w której odczyt

poszczególnych komórek następuje synchronicznie, zgodnie z taktami zegara CPU. Układy te

są zsynchronizowane z magistralę systemowa, (100 MHz i szybsze).

RDRAM {Rambus DRAM) - jest pamięcią opartą na zupełnie innych rozwiązaniach. Dzięki

podwojeniu znajdującej się w układzie magistrali danych i zwiększeniu częstotliwości pracy

do 800 MHz, umożliwia uzyskanie przepustowości rzędu 1,6 GB/s.

DDR SDRAM {Double Data Rate) SDRAM jest rozwinięciem projektu standardowych

układów SDRAM, w którym dane przesyłane są z dwa razy większą szybkością, Poza

zwiększeniem częstotliwości taktowania, pamięci DDR osiągają, podwojenie wydajności

dzięki wykonywaniu 2 transferów podczas jednego taktu zegara (przy narastającym i

opadającym zboczu).

Obudowy pamięci:

SIMM - moduły pamięci na karcie ze 32-stykami. Szyna danych ma 8-bitów. Obecnie nie

stosowane.

DIMM - moduły pamięci na karcie ze 168-stykami. Pracują, z szyną adresową, o szerokości 64-

bitów.

Moduł PS/2 - moduły pamięci na karcie ze 72-stykami. Pracują, z szyną adresowa, o

szerokości 32-bitow. Stosowane w pamięciach typu EDO RAM i FPM RAM. Nazwa

pochodzi od pierwotnego zastosowania tego rodzajów modułów pamięci w komputerach PS/2

IBM.

UWAGA!!!

Wymień inne obudowy pamięci

Systemy operacyjne – Rodzaje pamięci

Strona 6

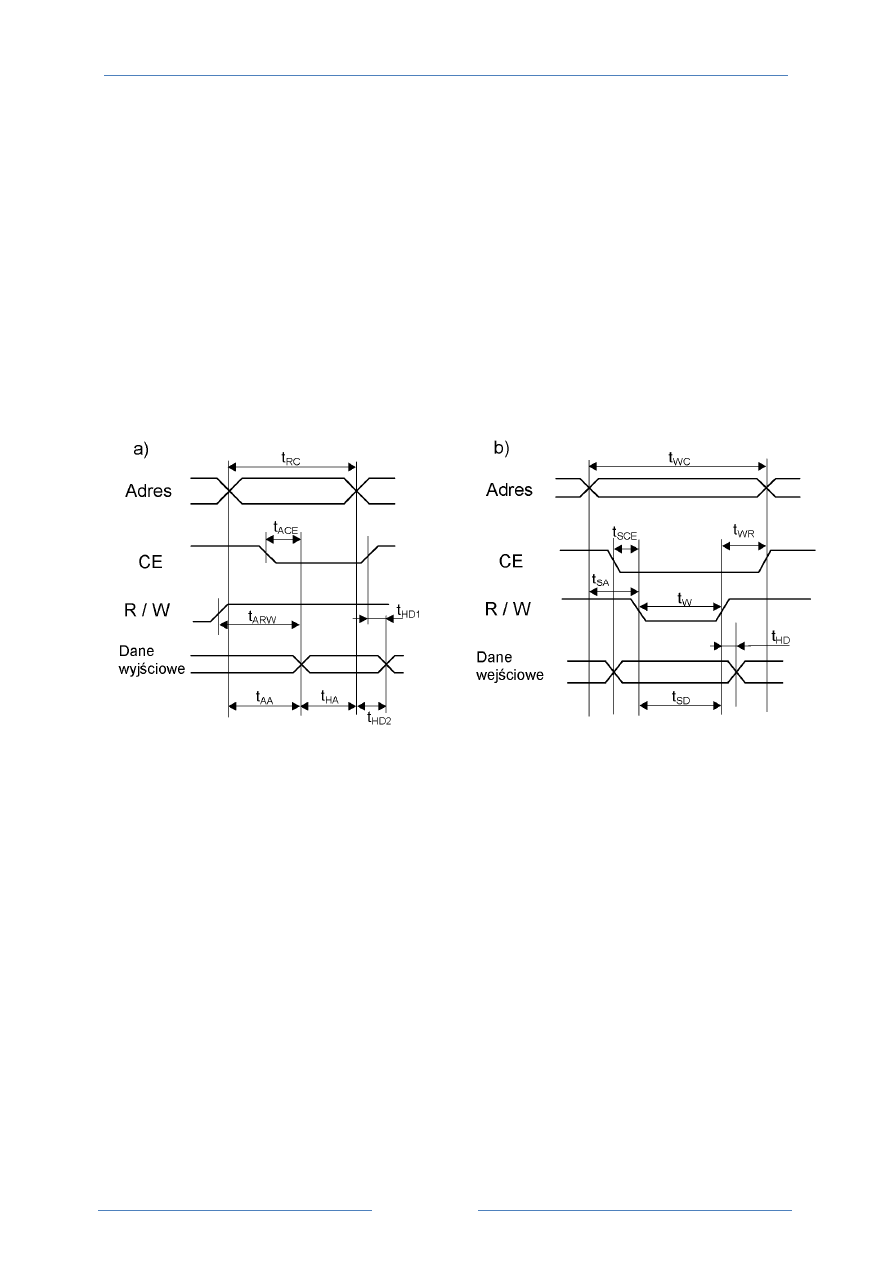

Podstawowe parametry pamięci:

• pojemność;

• organizacja logiczna;

• pobór mocy na bit.

Podstawowe parametry dynamiczne:

• czas cyklu odczytu t

RC

;

• czas dostępu t

A

;

* czas dostępu od wejść adresowych tAA lub t

SA

;

* czas dostępu od wejść wybierania układu pamięci t

ACE

lub t

SA

;

* czas dostępu od wejść sygnału odczytu t

ARW

;

• cykl czasu zapisu twc;

• czas odzyskiwania właściwości po sygnale zapisu twR;

• czas regeneracji (odświeżania) - dla pamięci dynamicznych.

Parametry dynamiczne pamięci dla cyklu odczytu (a) oraz cyklu zapisu (b).

Systemy operacyjne – Rodzaje pamięci

Strona 7

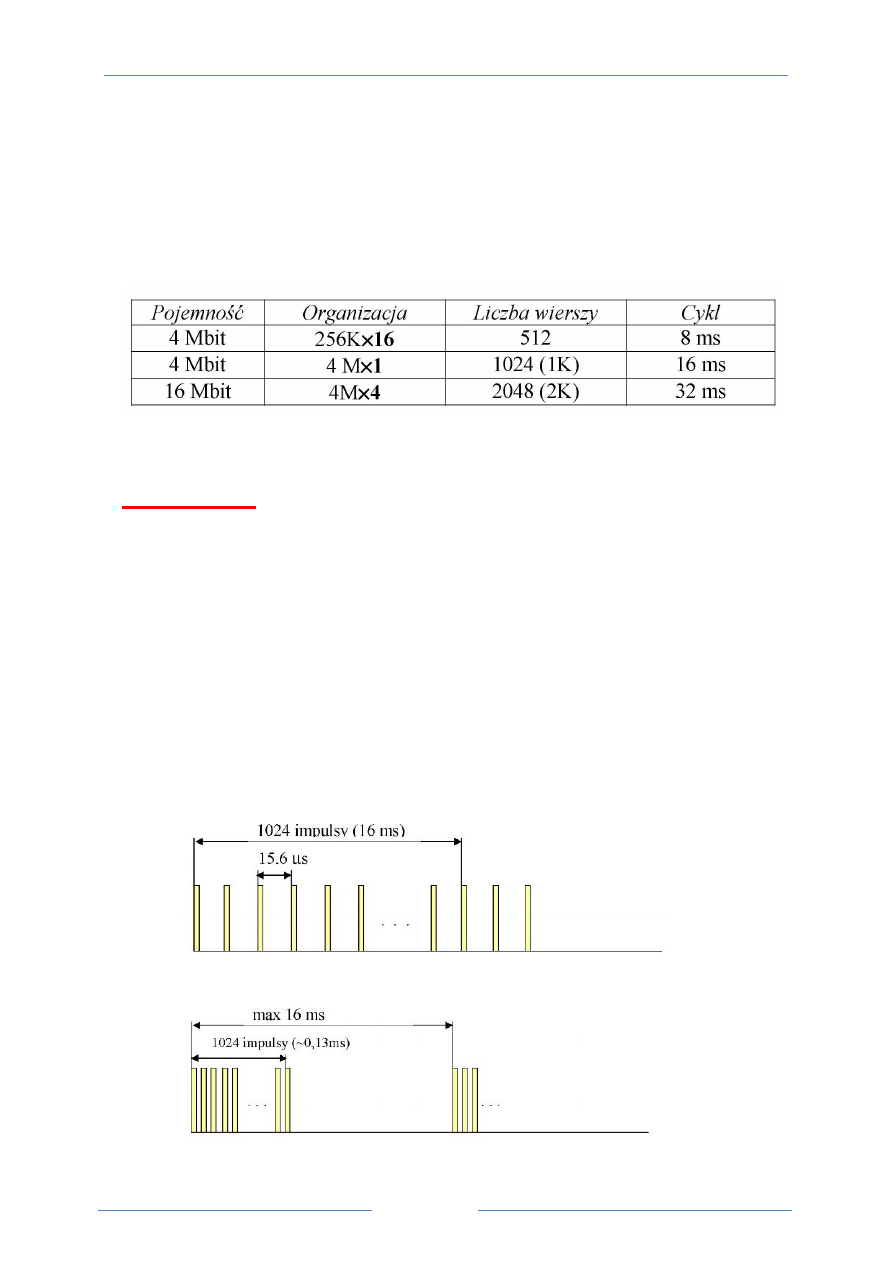

Odświeżanie

Odświeżanie sprowadza się do pobudzenia (zaadresowania) linii wiersza,

przy czy odświeżeniu ulegają wszystkie komórki należące do tego wiersza.

Konieczne jest wprowadzenie mechanizmu generującego regularnie impulsy

odświeżające przebiegające kolejno wszystkie wiersze nie rzadziej niż raz na

okres czasu nazywany cyklem odświeżania (Refresh Time).

Typowe wartości cyklu odświeżania

UWAGA!!!

Proszę znaleźć powyższe dane dla wyższych wartości

pamięci – 64Mbit, 128Mbit, 256Mbit, 512Mbit itp.

Podział cyklu odświeżania na odcinki czasowe równej wielkości daje w wyniku

okres przebiegu zegarowego (Refresh Rate) wymaganego do spełnienia wymogu

czasowego narzuconego przez cykl odświeżania

Pojedyncze impulsy odświeżające można zgrupować w jeden pakiet (Burst

Refresh) lub też rozłożyć równomiernie (Distributed Refresh) w obszarze okna

czasowego wyznaczonego przez cykl odświeżania.

Rozkład impulsów odświeżania

Distributed refresh

Burst refresh

Systemy operacyjne – Rodzaje pamięci

Strona 8

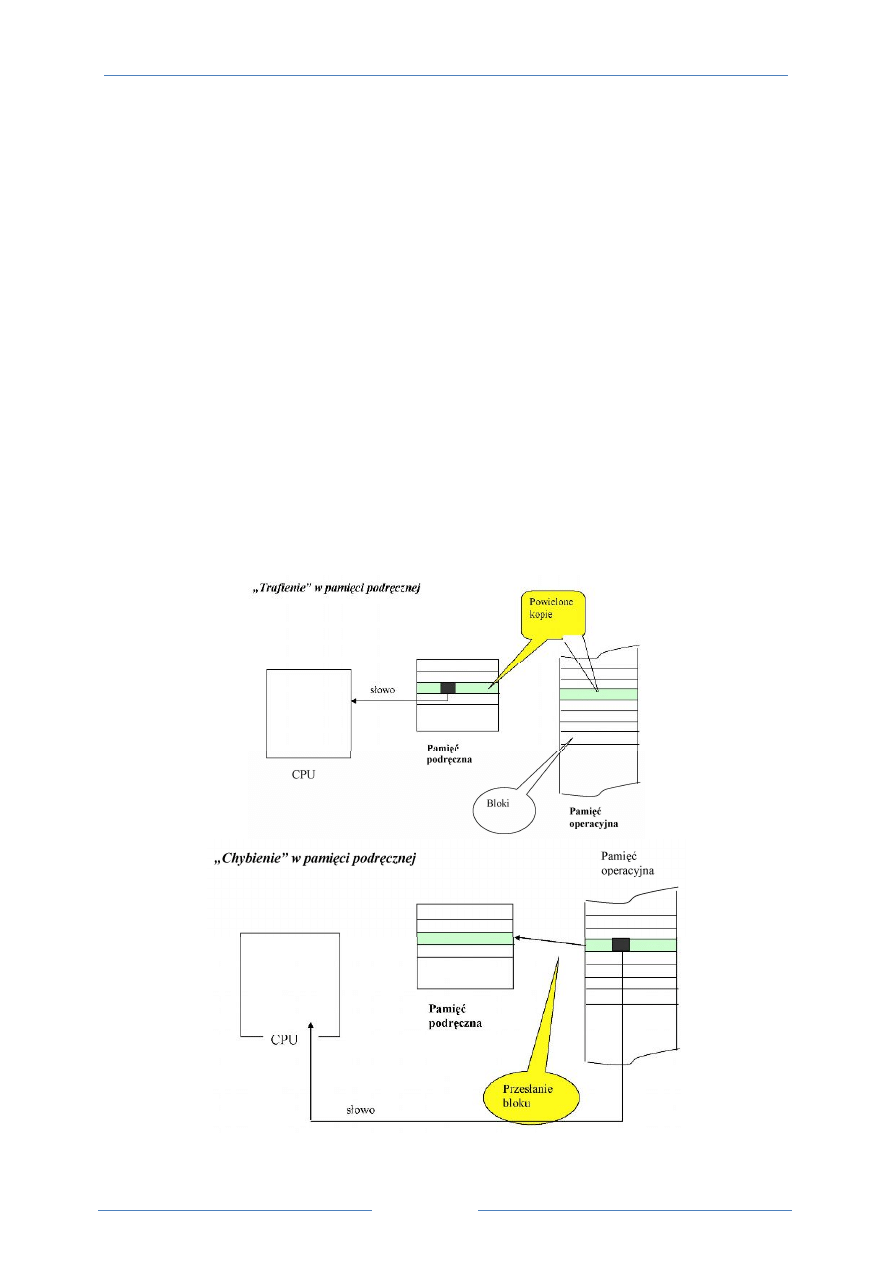

Pamięć podręczna (cache):

Logicznie pamięć cache jest umieszczona między procesorem a PAO i dostarcza

procesorowi względnie szybko danych. Pamięć podręczna poszerza wąskie

gardło powstające w wyniku różnic szybkości działania procesora i pamięci

głównej, korzystając z własności zachowania programu zwanej zasadą

lokalności.

Zasada lokalności

Programy mają tendencję do ponownego używania danych i rozkazów, które

były niedawno używane. Rozkazy i dane używane w krótkim odstępie czasu są

zwykle położone także blisko siebie w pamięci (lokalność przestrzenna).

Zasada działania

Półprzewodnikowa pamięć podręczna zawiera ograniczona, liczbę obszarów

albo wierszy służących do przechowywania bloków z pamięci głównej. Każdy

blok ma typowo wielkość od 4 - 16 slow. W czasie wykonywania programu

procesor zamiast czytać rozkazy czy dane bezpośrednio z pamięci głównej,

szuka ich najpierw w pamięci podręcznej. Jeśli słowo zostaje znalezione, to

sygnalizowane jest „trafienie" i słowo przesyłane jest do procesora.

Systemy operacyjne – Rodzaje pamięci

Strona 9

Struktura cache:

1. pamięć danych właściwych (tzn. instrukcji lub danych z PAO)

2. pamięć adresów komórek, których zawartość jest przechowywana w części

danych właściwych

3. pamięć znaczków, przeznaczonych dla wspomagania zarządzaniem pamięcią

cache np. wyznaczaniem, którą zawartość można usunąć w przypadku

zapełnienia pamięci cache i konieczności wprowadzenia nowych danych

4. jednostka zarządzana pamięcią, m.in. porównująca adresy odwołań i

przechowywanych kopii zawartości komórek PAO oraz podejmująca decyzje

o usunięciu przy zapełnieniu cache. Konieczne jest zapewnienie sterowania

przez sprzęt, a nie oprogramowanie, gdyż dla wykonania odczytu z pamięci

należałoby odczytać z pamięci podprogram obsługujący odczyt z pamięci itd.

Partie, związane z pamięcią cache:

odwzorowanie bezpośrednie, blokowo-asocjacyjne, zbiorowo-asocjacyjne, w

pełni asocjacyjne, współczynnik trafień (hit ratio), współczynnik chybień,

algorytmy wymiany stron, zapis mQtodq, write-through, write-back, bity

ważności, wieloportowość – są związane z organizacja_komputer6w, ale przy

omawianiu architektury także się pojawiają

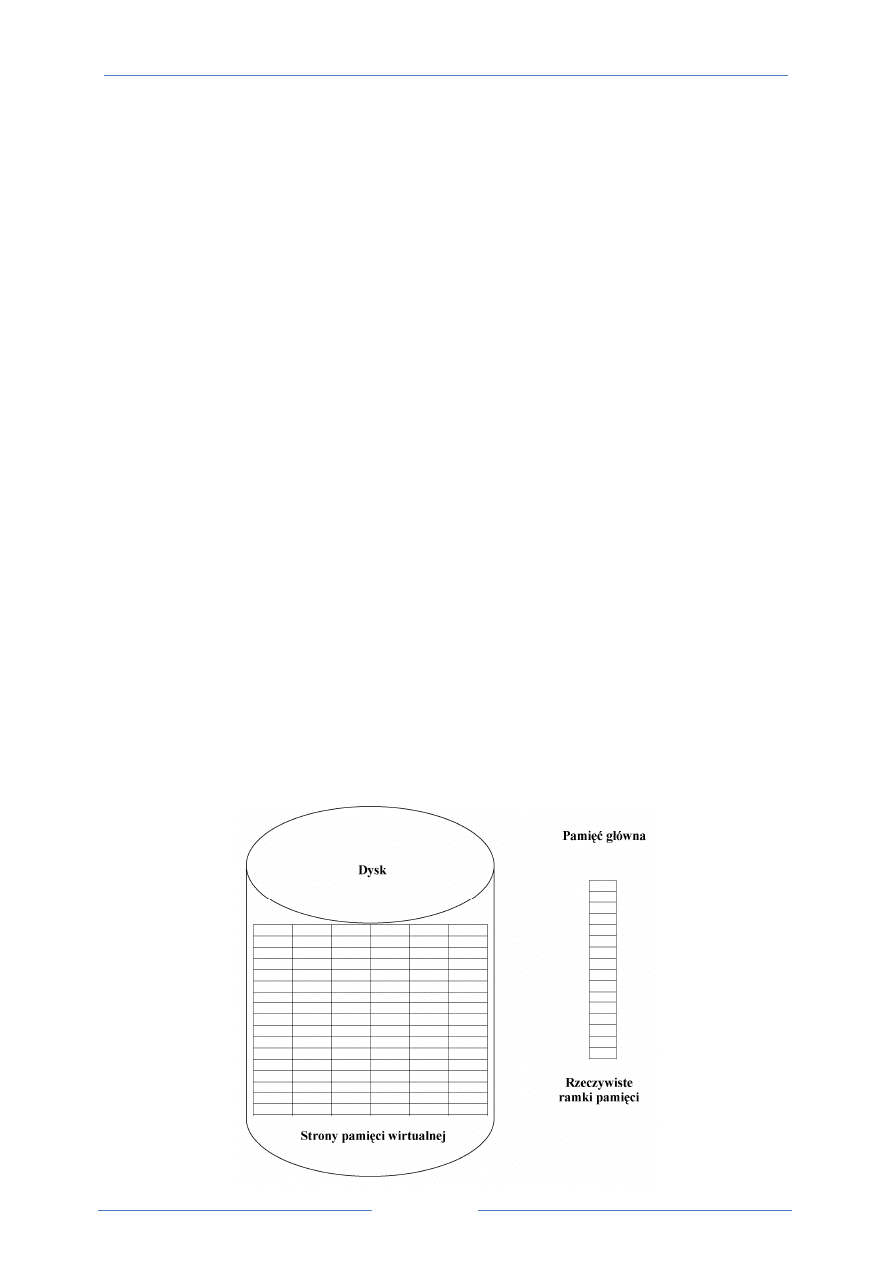

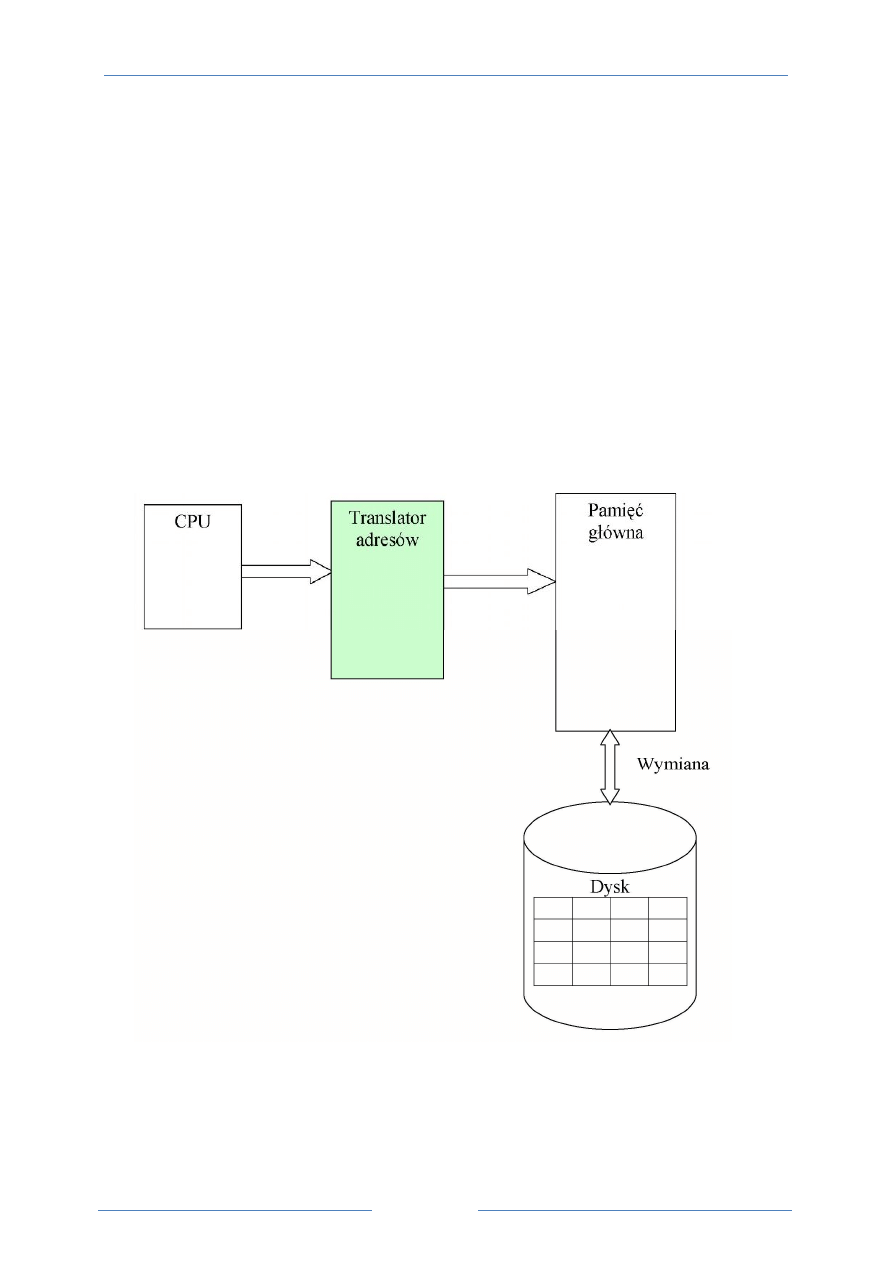

Pamięć wirtualna

Przy wykorzystaniu tej techniki adresy generowane przez procesor nie są

używane do bezpośredniego dostępu do pamięci, ale są przekształcane w

prawdziwe adresy, które mogą wskazywać na pamięć główną, dodatkowa, albo

kombinację ich obu. W pamięci operacyjnej odwzorowane są tylko te części

programu, które są aktualnie niezbędne do wykonania, reszta pozostaje na dysku

do czasu aż będzie potrzebna.

Systemy operacyjne – Rodzaje pamięci

Strona 10

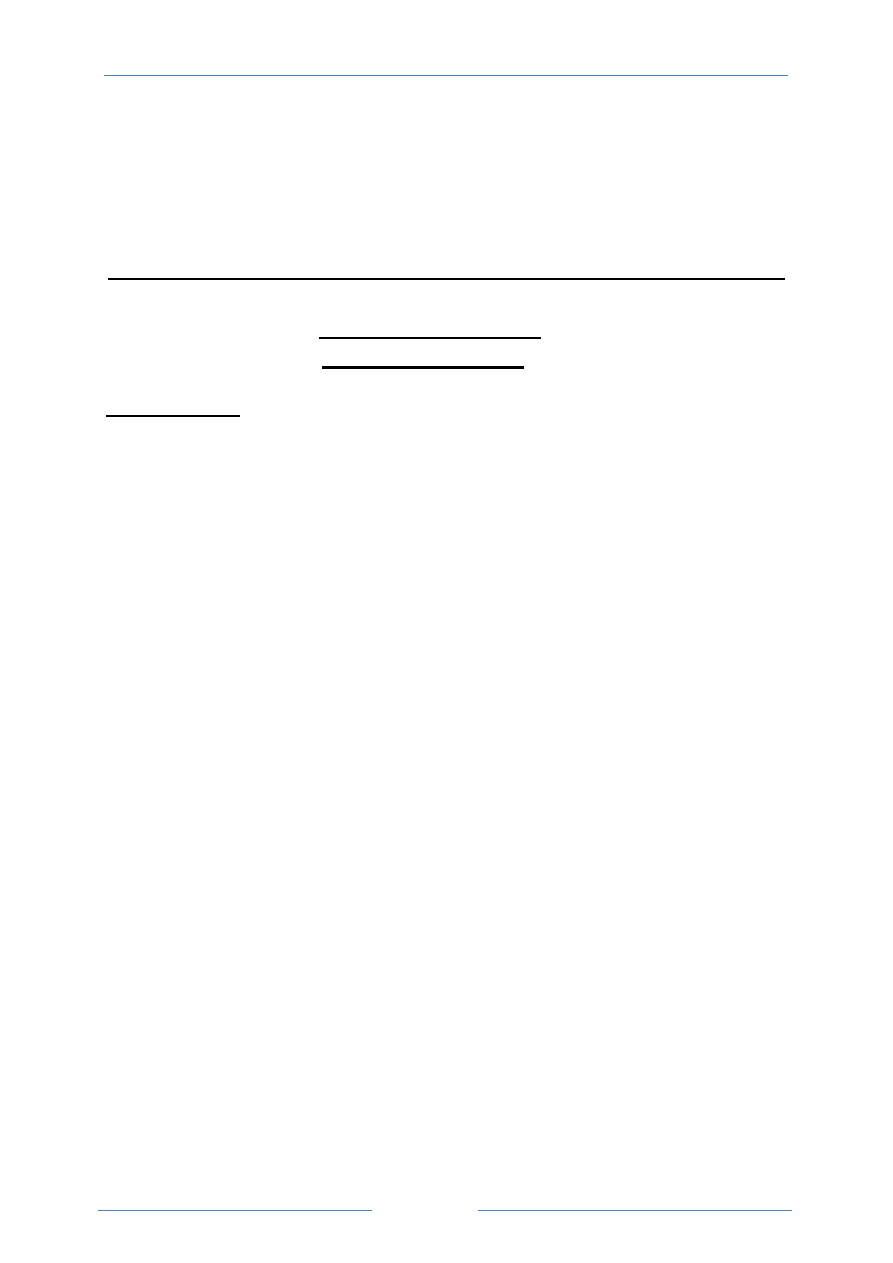

Koncepcja pamięci wirtualnej bierze się z faktu, że dla właściwego

wykonania programu prawdopodobnie niezbędne jest przechowywanie w PAO

tylko pewnej jego części - instrukcji i danych, które w najbliższym czasie

będą. przetwarzane. W przypadku niedoboru PAO w stosunku do wymagań

programu, niepotrzebne w danym okresie czasu fragmenty kodu i danych

mogą. być przechowywane w tańszej i bardziej pojemnej, ale o rząd wielkości

wolniejszej pamięci zewnętrznej, zwykle na dysku twardym. Zjawisko to, w

przypadku wykonywania przez komputer tylko jednego programu, było

nazywane nakładkowaniem i pozostawiane na głowie programisty, ale wraz z

pojawieniem się systemów wielodostępnych i wieloprogramowych,

zarządzaniem wymiana. fragmentów kodu i danych różnych zadań między

PAO i dyskiem musiał się zająć system operacyjny.

W czasie działania programu przesyłanie fragmentów kodu i danych do i z

pamięci głównej jest kontrolowane przez część systemu operacyjnego zwana.

system zarzqdzania pamięcią.

Systemy operacyjne – Rodzaje pamięci

Strona 11

Pamięć wirtualna jest mechanizmem jakościowo różnym od omawianych

poprzednio (pamiqci cache). Aby pokazać pamięć cache, należałoby wskazać

kilka (w skrajnych przypadkach jeden) układów VLSI, realizujących wspólnie

zadanie podawania procesorowi często używanych danych i rozkazów szybciej,

niż jest to w stanie zrobić pamięć operacyjna.

Pamięć wirtualna jest zespołem zarówno elementów sprzętu

(rejestrów procesora, elementów pamięci operacyjnej, elementów

pamięci dyskowej), jak i oprogramowania - zarządzanie pamięcią

wirtualną realizuje system operacvjny.

Opis działania:

- zadanie odwołuje się do komórki PAO, generując adres logiczny;

- MMU tłumaczy adres logiczny na fizyczny : adres początku bloku + offset w

ramach bloku;

- MMU sprawdza, czy zadany blok znajduje się w PAO (najpierw w TLB,

potem w tablicy bloków w PAO)

- jeśli tak, obsługa odczytu/ zapisu;

- jeśli nie, zawieszane jest wykonywanie bieżącego zadania i generowany

jest wyjątek, obsługiwany przez jądro SO ; sprawdzana jest możliwość

sprowadzenia zadanej strony z dysku do „wolnego” obszaru w PAO, jeśli

nie ma wolnego, należy wyznaczyć jakiś do usunięcia, sprawdzić, czy

usuwany był modyfikowany w stosunku do kopii odczytanej poprzednio z

dysku, jeśli modyfikowany, zapisać nową postać usuwanego, wczytać

zadany obszar do PAO i wznowić wykonanie zawieszonego zadania;

Wspomaganie mechanizmu PW musi być realizowane na 3 poziomach

1.

jądra systemu operacyjnego

: obsługa braku zadanych bloków (page fault),

procedury umieszczania bloków w wolnej PAO, procedury wymiany

bloków;

2.

jednostki zarządzania pami

ę

cią

: przechowywanie i interpretacja bitów

sterujących

- valid/ invalid bit czy ramka zawiera kopię bloku z dysku, czy

informację nieaktualna_

- dirty bit. blok był modyfikowany po odczycie z dysku

- read/ write bit. strona do odczytu, zapisu ę

- licznik dostępów. dla implementacji algorytmów wymiany

- generacja sygnałów do SO błąd pamięci, błąd strony, zapis do bloku o

atrybucie „tylko do odczytu”;

3.

procesora

: instrukcje muszą być restartowalne zarówno przy próbie

pobrania instrukcji jak i jej argumentów, wprowadza się dodatkowe

instrukcje i rejestry do obsługi PW.

Systemy operacyjne – Rodzaje pamięci

Strona 12

Wydajność:

efektywny czas dostępu = ( 1 - współcz. chybień ) x czas dostępu PAO +

współcz. chybień x czas obsługi chybienia

PYTANIE

Jaki będzie efektywny czas dostępu jeżeli czas dostępu PAO wynosi 10 ns,

obsługa błędu strony (chybienia) wymaga 25 ms , a współczynnik chybień =

1/10000?

Zarządzanie pamięcią wirtualną w systemie Windows NT

Proces zarządzania stronami w systemie Windows NT (t.j. decydowanie,

które strony wirtualne mają być umieszczone w RAM, a które mają znajdować

się w pliku stronicowania) nazywany jest stronicowaniem na żądanie

(demand paging).

Systemy operacyjne – Rodzaje pamięci

Strona 13

Zaletv pamięci wirtualnei:

- większa logiczna przestrzeń adresowa dla programu, mogąca przekraczać

rozmiar fizycznie zainstalowanej pamięci (Windows i swap file),

- stopień wieloprogramowości na danym komputerze może być zwiększony,

- dzięki przemyślanej strukturze i umieszczeniu zarządzania w jądrze systemu

operacyjnego, procesy przydziału/ wymiany /zwalniania są przezroczyste dla

programisty -> mniej błędów.

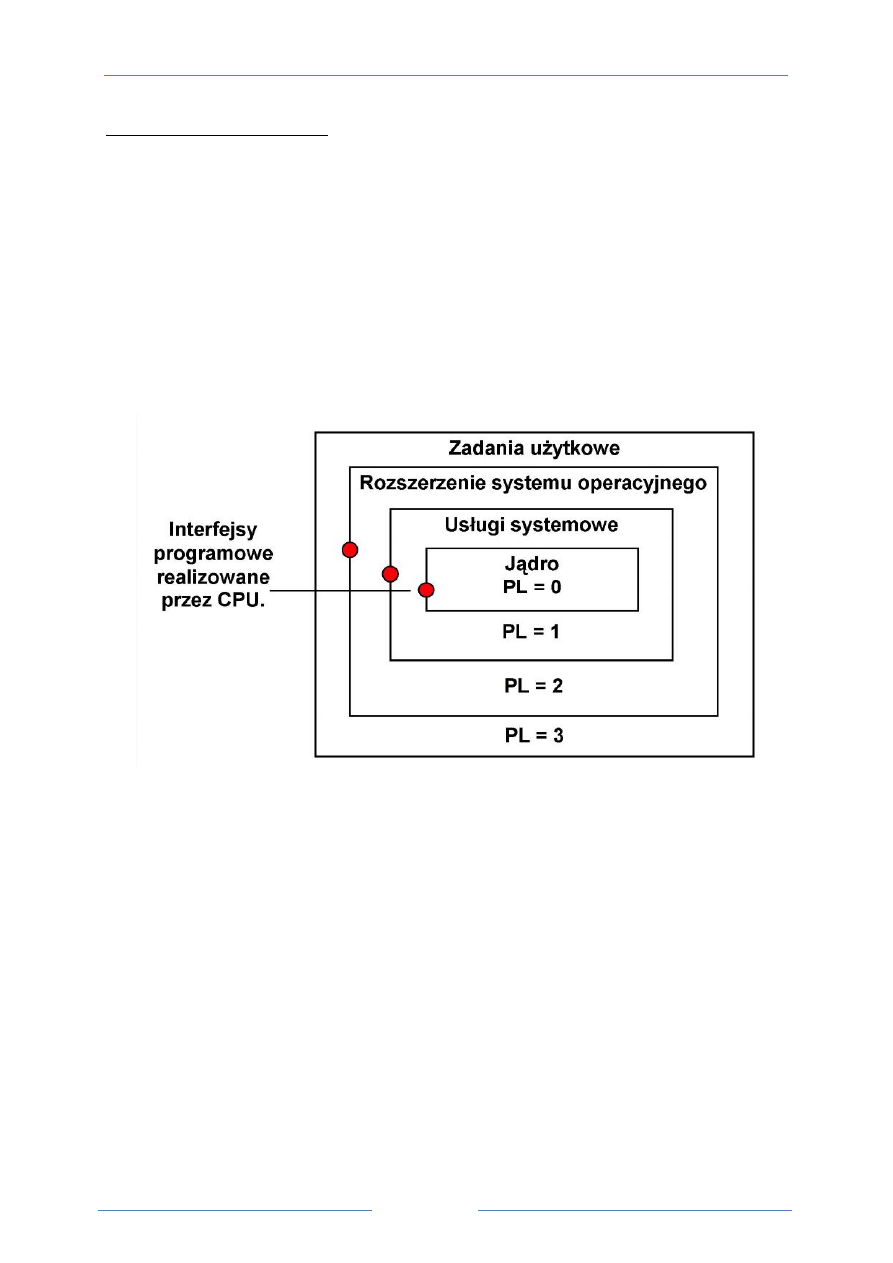

Tryb wirtualny procesorów, ochrona zasobów:

Mechanizmy ochrony.

Ochrona zasobów polega na wprowadzeniu czterech poziomów

uprzywilejowania. Hierarchię poziomów uprzywilejowania przedstawia rys.:

Hierarchiczny system poziomów uprzywilejowania.

Poziomy te stanowią rozszerzenie stosowanej powszechnie w

minikomputerach struktury systemowego i użytkowego poziomu

uprzywilejowania. Poszczególne poziomy uprzywilejowania PL ponumerowane

są od 0 do 3. Poziom oznaczony cyfrą zero jest najbardziej uprzywilejowany.

Wprowadzenie czterech poziomów uprzywilejowania umożliwia stosowanie

mechanizmów ochrony również wewnątrz zadań programowych.

Systemy operacyjne – Rodzaje pamięci

Strona 14

W wirtualnej przestrzeni adresowej każdego zadania mogą być zawarte

procedury systemowe, procedury obsługi przerwań i inne procedury

programowe. Atrybut poziomu uprzywilejowania jest przypisywany zadaniom

programowym, deskryptorom i selektorom.

Poziom uprzywilejowania zadania wpływa na rodzaj rozkazów jakie mogę

być wykonywane i na zestaw deskryptorów, który może być wykorzystany

przez zadanie.

Bieżący poziom uprzywilejowania CPL (ang. Current Privilege Level) jest

określany przez poziom uprzywilejowania aktualnie realizowanego zadania

programowego; określają, go dwa najmniej znaczące bity rejestru segmentu

(selektora) CS.

Poziom ten może być zmieniony tylko przez odwołanie do mechanizmów

przekazania sterowania. Poziom uprzywilejowania deskryptora DPL określa

zestaw zadań, które mogą odwoływać się do danego deskryptora. Aby zadanie

mogło uzyskać dostęp do deskryptora numer CPL nie może być większy od

DPL. Żądany poziom uprzywilejowania RPL określany przez selektor, może

być wykorzystany do obniżenia poziomu uprzywilejowania zadania. Mechanizm

ten zapewnia, że wywoływane procedury o wysokim poziomie

uprzywilejowania nie będą miały dostęp do struktur danych umieszczonych na

wyższym poziomie uprzywilejowania, niż procedura wywołująca.

Drugim sposobem ochrony jest separacja zadań. Polega ona na tym, że każde

zadanie dysponuje własną przestrzenią adresowa, Zrealizowane jest to za

pomocą tabeli translacji. Każde zadanie posiada własną, lokalną, tablicę

deskryptorów - LDTR. Dzięki temu różne zadania pomimo tego, że posługują,

się tym samym adresem wirtualnym, odwołują, się do rożnych obszarów

pamięci, wynikających z zawartości ich lokalnych tabel deskryptorów.

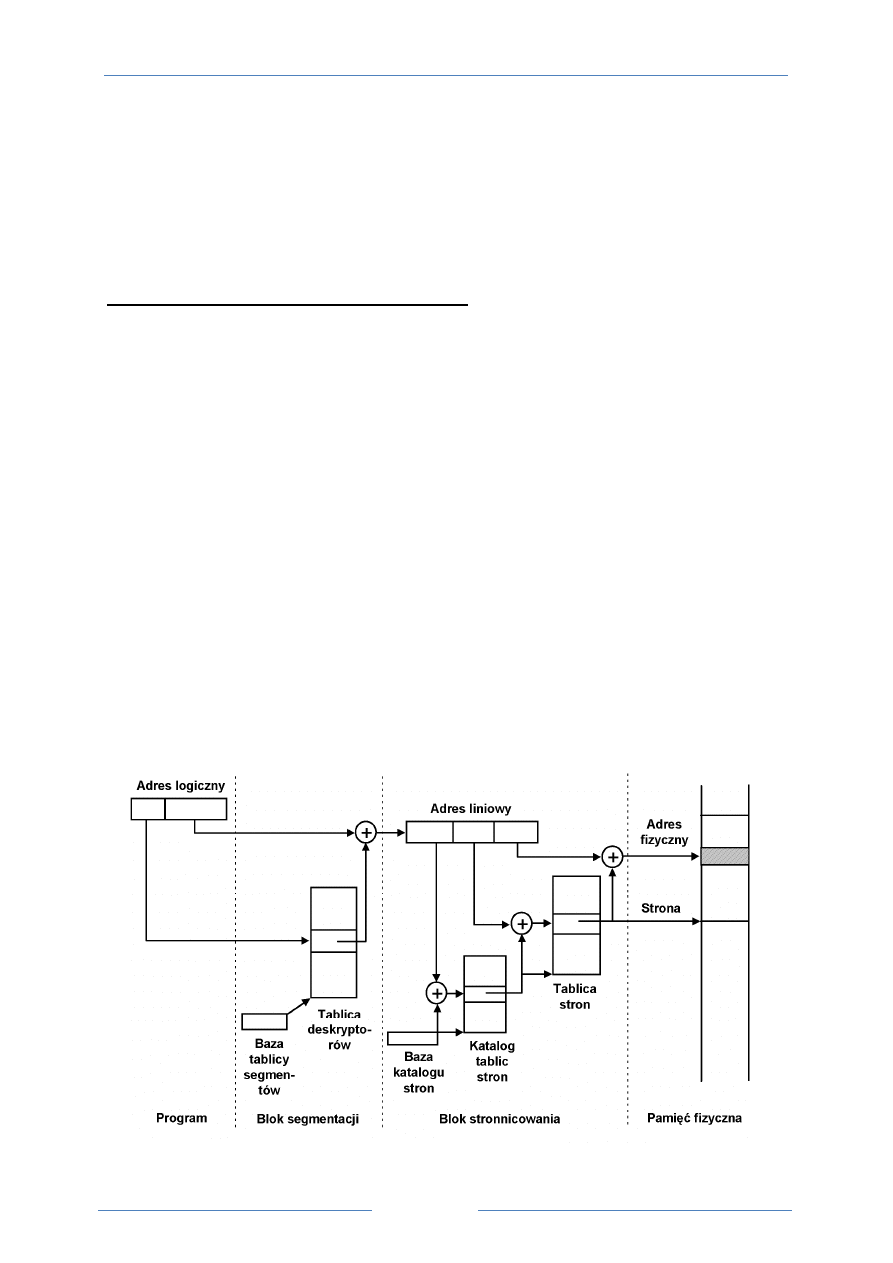

Mechanizm translacji adresów

Wyszukiwarka

Podobne podstrony:

Organizacja pamięci komputerów, szkola, systemy operacyjne, klasa 1

Organizacja pamięci

03 uklad sterowania magistrale i organizacja pamieci

03 organizacja pamięciid 4188 ppt

Organizacja pamięci

Architektura i organizacja komuterów W5 Pamięć wewnętrzna

Architektura i organizacja komuterów W6 Pamięć zewnętrzna

Architektura i organizacja komuterów W7 Pamięć zewnętrzn

Architektura i organizacja komuterów W6 Pamięć wewnętrzn

Architektura i organizacja komuterów W5 Pamięć wewnętrzna

03 Odświeżanie pamięci DRAMid 4244 ppt

9 Ch organiczna WĘGLOWODANY

organizacja i metodyka pracy sluzby bhp

wykład 12 pamięć

Jedność budowy organizmów żywych1

Organizacja kąpieliska

więcej podobnych podstron