Interfejsy

Czyli

„ciekawe jak dużo praw autorskich złamałem..”

Paulo Coelho

MC_OMEN

Wstęp

Żeby w ogóle odnaleźd sens tego przedmiotu należy zapoznad się z definicją – czym jest interfejs.

Interfejs jest to urządzenie elektroniczne lub optyczne służące do komunikacji między dwoma różnymi urządzeniami.

Znając już podstawową definicje możemy przejśd do faktu czym się będziemy tutaj zajmowad.

Czyli kolokwialnie rzecz biorąc, jak połączyd kabelkami jakieś urządzenia, aby jedno rozumiało drugie.

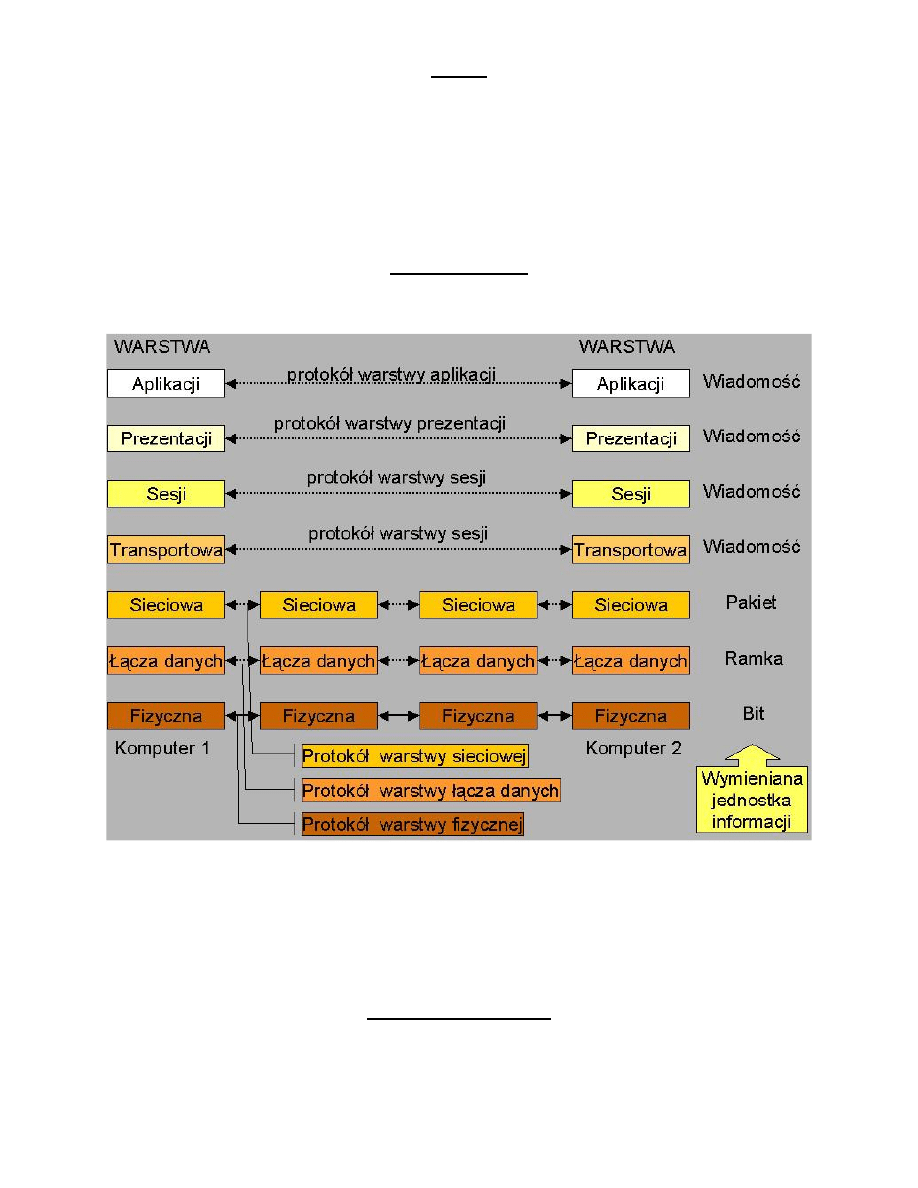

MODEL ISO/OSI

Zaczniemy może od modelu ISO/OSI czyli modelu odniesienia łączenia systemów otwartych.

Teraz rodzi się pytanie co to jest protokół.

Protokół jest to umowny język komunikacji pomiędzy modelami. Czyli „jakiego języka” muszą używad aby się

zrozumied.

Na modelu ISO/OSI najważniejsze są dla nas 3 pierwsze warstwy(od dołu), a właściwie najbardziej to fizyczna warstwa.

Opis modelu ISO/OSI

Fundamentem, na którym zbudowany jest model referencyjny OSI, jest jego warstwa fizyczna. Określa ona wszystkie

składniki sieci niezbędne do obsługi elektrycznego, optycznego, radiowego wysyłania i odbierania sygnałów. Warstwa

fizyczna, w postaci określonej przez Model Referencyjny OSI, składa się ze wszystkich procesów, mechanizmów,

elektroniki oraz protokołów, które potrzebne są urządzeniu obliczającemu w celu wysłania i odbierania binarnych

strumieni danych. W specyfikacji warstwy fizycznej technologii LAN zamieszczone są oczekiwania odnośnie wydajności

nośnika łączącego komunikujące się ze sobą urządzenia. Model jednak nie określa samego rodzaju nośnika.

Warstwa fizyczna - odpowiada za transmisje sygnałów w sieci. Realizuje ona konwersje bitów informacji na

sygnały, które będą przesyłane w kanale z uwzględnieniem maksymalizacji niezawodności przesyłu. W warstwie

fizycznej określa się parametry amplitudowe i czasowe przesyłanego sygnału, fizyczny kształt i rozmiar łączy,

znaczenie ich poszczególnych zestyków i wartości napięd na nich występujących, sposoby nawiązywania

połączenia i jego rozłączania po zakooczeniu transmisji.

Warstwa łącza danych - odpowiedzialna jest za odbiór i konwersję strumienia bitów pochodzących z urządzeo

transmisyjnych w taki sposób, aby nie zawierały one błędów. Warstwa ta postrzega dane jako grupy bitów

zwane ramkami. Warstwa łącza danych tworzy i rozpoznaje granice ramki. Ramka tworzona jest przez dołączenie

do jej początku i kooca grupy specjalnych bitów. Kolejnym zadaniem warstwy jest eliminacja zakłóceo,

powstałych w trakcie transmisji informacji po kanale łączności. Ramki, które zostały przekazane niepoprawnie, są

przesyłane ponownie. Ponadto warstwa łącza danych zapewnia synchronizację szybkości przesyłania danych

oraz umożliwia ich przesyłanie w obu kierunkach.

Warstwa sieciowa - steruje działaniem podsieci transportowej. Jej podstawowe zadania to przesyłanie danych

pomiędzy węzłami sieci wraz z wyznaczaniem trasy przesyłu, określanie charakterystyk sprzęgu węzeł-komputer

obliczeniowy, łączenie bloków informacji w ramki na czas ich przesyłania a następnie stosowny ich podział. W

najprostszym przypadku określanie drogi transmisji pakietu informacji odbywa się w oparciu o stałe tablice

opisane w sieci. Istnieje również możliwośd dynamicznego określania trasy na bazie bieżących obciążeo linii

łączności. Stosując drugie rozwiązanie mamy możliwośd uniknięcia przeciążeo sieci na trasach, na których

pokrywają się drogi wielu pakietów.

Warstwa transportowa - podstawową funkcją tej warstwy jest obsługa danych przyjmowanych z warstwy sesji.

Obejmuje ona opcjonalne dzielenie danych na mniejsze jednostki, przekazywanie zblokowanych danych

warstwie sieciowej, otwieranie połączenia stosownego typu i prędkości, realizacja przesyłania danych,

zamykanie połączenia. Ponadto mechanizmy wbudowane w warstwę transportową pozwalają rozdzielad

logicznie szybkie kanały łączności pomiędzy kilka połączeo sieciowych.

Warstwa sesji - określenie parametrów sprzężenia użytkowników realizowane jest za pośrednictwem warstwy

sesji. Po nawiązaniu stosownego połączenia warstwa sesji pełni szereg funkcji zarządzających, związanych m. in.

z taryfikacją usług w sieci. W celu otwarcia połączenia pomiędzy komputerami (sesji łączności) poza podaniem

stosownych adresów warstwa sprawdza, czy obie warstwy (nadawcy i odbiorcy) mogą otworzyd połączenie.

Następnie obie komunikujące się strony muszą wybrad opcje obowiązujące w czasie trwania sesji. Dotyczy to na

przykład rodzaju połączenia (simpleks, dupleks) i reakcji warstwy na zerwanie połączenia (rezygnacja, ponowne

odtworzenie). Przy projektowaniu warstwy zwraca się uwagę na zapewnienie bezpieczeostwa przesyłanych

danych. Przykładowo, jeżeli zostanie przerwane połączenie, którego zadaniem była aktualizacja bazy danych, to

w rezultacie tego zawartośd bazy może okazad się niespójna.

Warstwa prezentacji - jej zadaniem jest obsługa formatów danych. Odpowiada za kodowanie i dekodowanie

zestawów znaków oraz wybór algorytmów, które do tego będą użyte. Przykładową funkcją realizowaną przez

warstwę jest kompresja przesyłanych danych, pozwalająca na zwiększenie szybkości transmisji informacji.

Ponadto warstwa udostępnia mechanizmy kodowania danych w celu ich utajniania oraz konwersję kodów w

celu zapewnienia ich mobilności.

Warstwa aplikacji - zapewnia programom użytkowym usługi komunikacyjne. Określa ona formaty wymienianych

danych i opisuje reakcje systemu na podstawowe operacje komunikacyjne. Warstwa stara się stworzyd wrażenie

przezroczystości sieci. Jest to szczególnie ważne w przypadku obsługi rozproszonych baz danych, w których

użytkownik nie powinien wiedzied, gdzie zlokalizowane są wykorzystywane przez niego dane lub gdzie

realizowany jest jego proces obliczeniowy

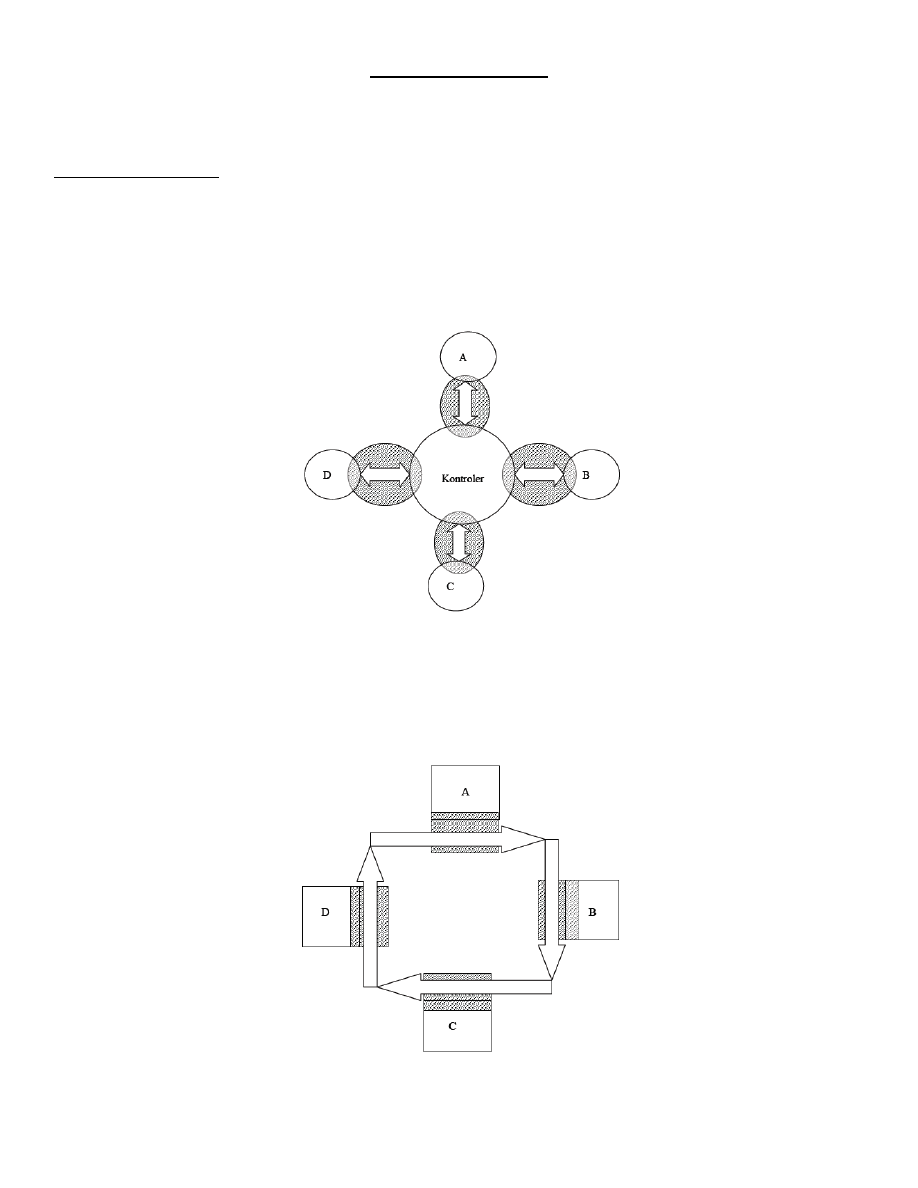

Łączenie interfejsów

Interfejsy możemy nie tylko łączyd bezpośrednio „wtyczka do gniazdka”, ale w określonych topologiach które

przedstawiam poniżej.

TOPOLOGIE POŁĄCZEŃ :

Gwiazda

1. Ograniczona liczba połączeo

2. Typowym interfejsem działającym w takiej konfiguracji jest RS-232

3. Przepustowośd szybko się kooczy

4. Schemat:

Pętla

1. Zawodna

2. Wolna

3. Można dowolnie powiększad

4. Schemat:

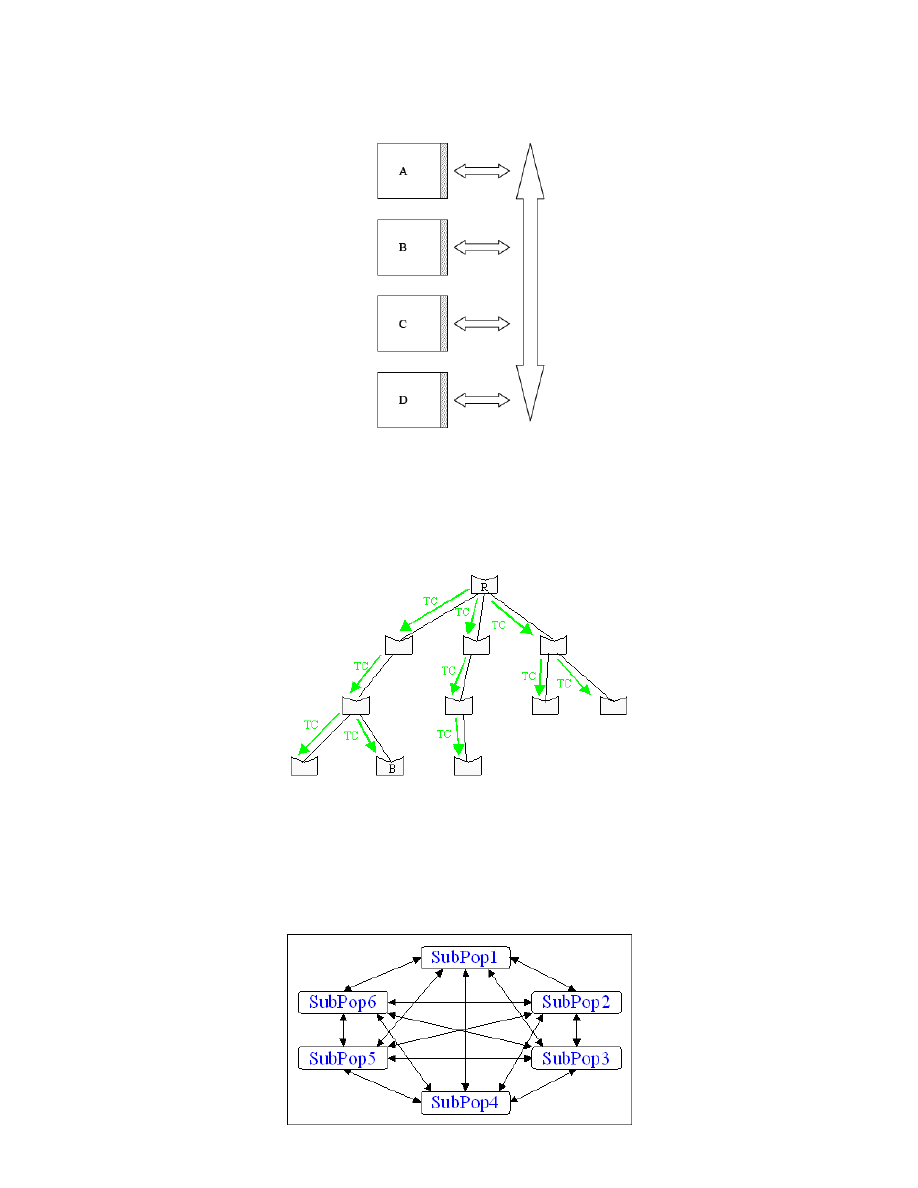

Linia (magistrala)

1. Urządzenia mogą porozumiewad sięmiędzy sobą

2. Można powiększad

3. Szybko działa

4. Schemat:

Drzewo

1. Dzieli przepustowośd

2. Typowe dla USB

3. Schemat:

„Siatkowa”

1. Każde urządzenie jest połączone z każdym

2. Typowe dla interfejsów bezprzewodowych

3. Dużo połączeo

4. Schemat:

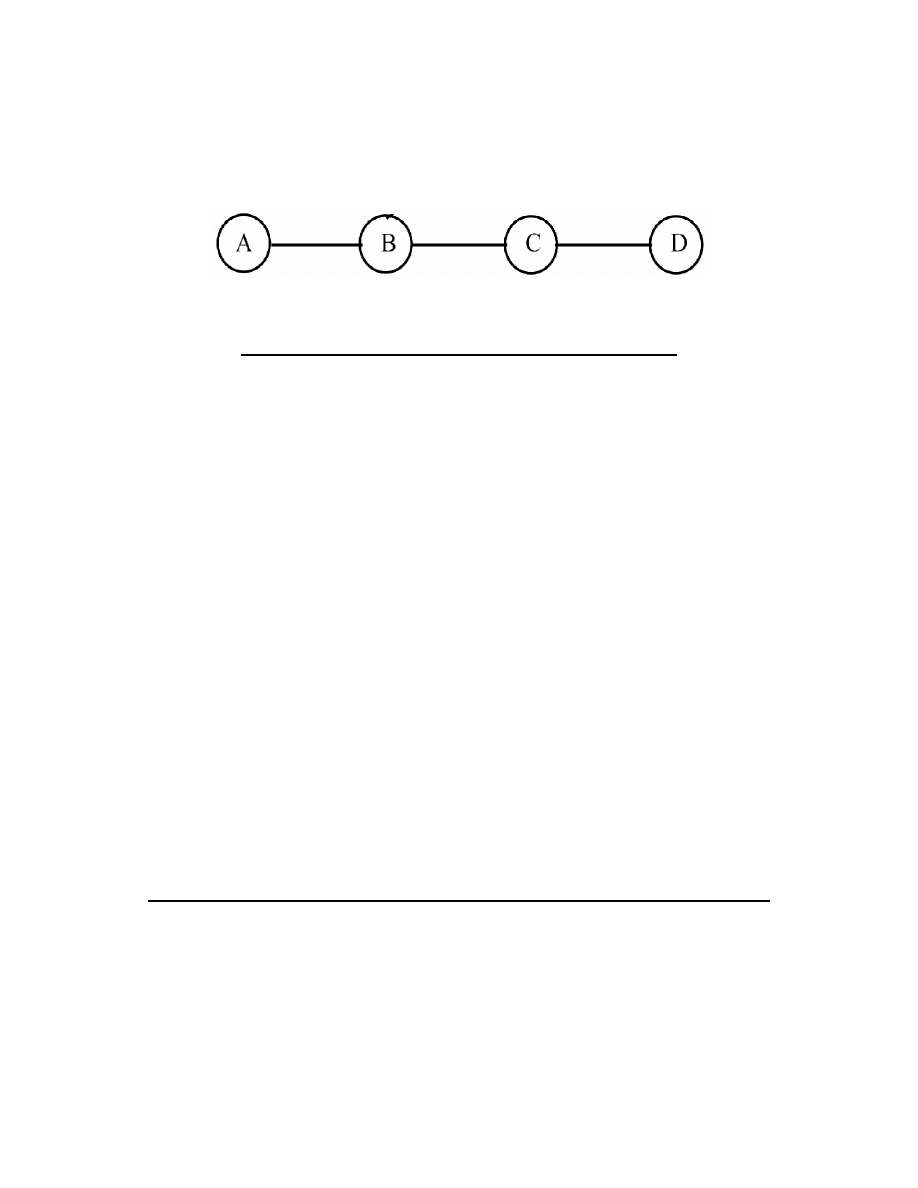

Łaocuch (base chain)

1. Każde urządzenie może współpracowad z dwoma innymi

2. Np. fire-wire : kamerka -> nagrywarka -> TV

3. Np. LPT : PC->Skaner->Drukarka

4. Schemat:

Interfejsy ze względu na „styl” przesyłania danych

Interfejsy możemy podzielid ze względu na styl przesyłu danych na równoległe i szeregowe.

W interfejsach szeregowych:

Wysyłany i odbierany jest bit po bicie

Nie zawęża to do używania tylko jednego kabla

Przykłady : RS-232 (one-wire) ; USB (2 kable) ; PCI – Express

W interfejsach równoległych:

Wysyłamy i odbieramy kilka bitów równocześnie, zazwyczaj jest to wielokrotnośd liczby 2

Np. LPT , PCI

Występuje problem propagacji oraz problem związany z jednakową prędkością przesyłu/odbioru

Skoro znamy podział stylu przesyłu, warto zagłębid się i przeanalizowad możliwości przesyłu od kierunku, a wtedy

wyróżniamy:

Simpleks - jednokierunkowa, przekazywaniu danych tylko od DTE1 do DTE2 lub tylko odwrotnie, np. drukarka z

komputerem

Półdupleks – dwukierunkowa, nie jednoczesna - umożliwia naprzemienne przesyłanie danych w obydwóch

kierunkach. Wysyłane jest zapytanie i czekanie na odpowiedź, jeżeli nastąpi odpowiedź – dane są wysyłane

Dupleks – dwukierunkowa jednoczesna - umożliwia jednoczesne przesyłanie danych w obydwóch kierunkach.

Jest to najszybszy i najlepszy sposób.

Podział ze względu na rodzaj transmisji (Synchoniczne, Asynchroniczne)

Teraz możemy przejśd do faktu synchronizmu, czyli czy wysyłamy wiadomośd wobec jakiegoś wspólnego sygnału czy nie.

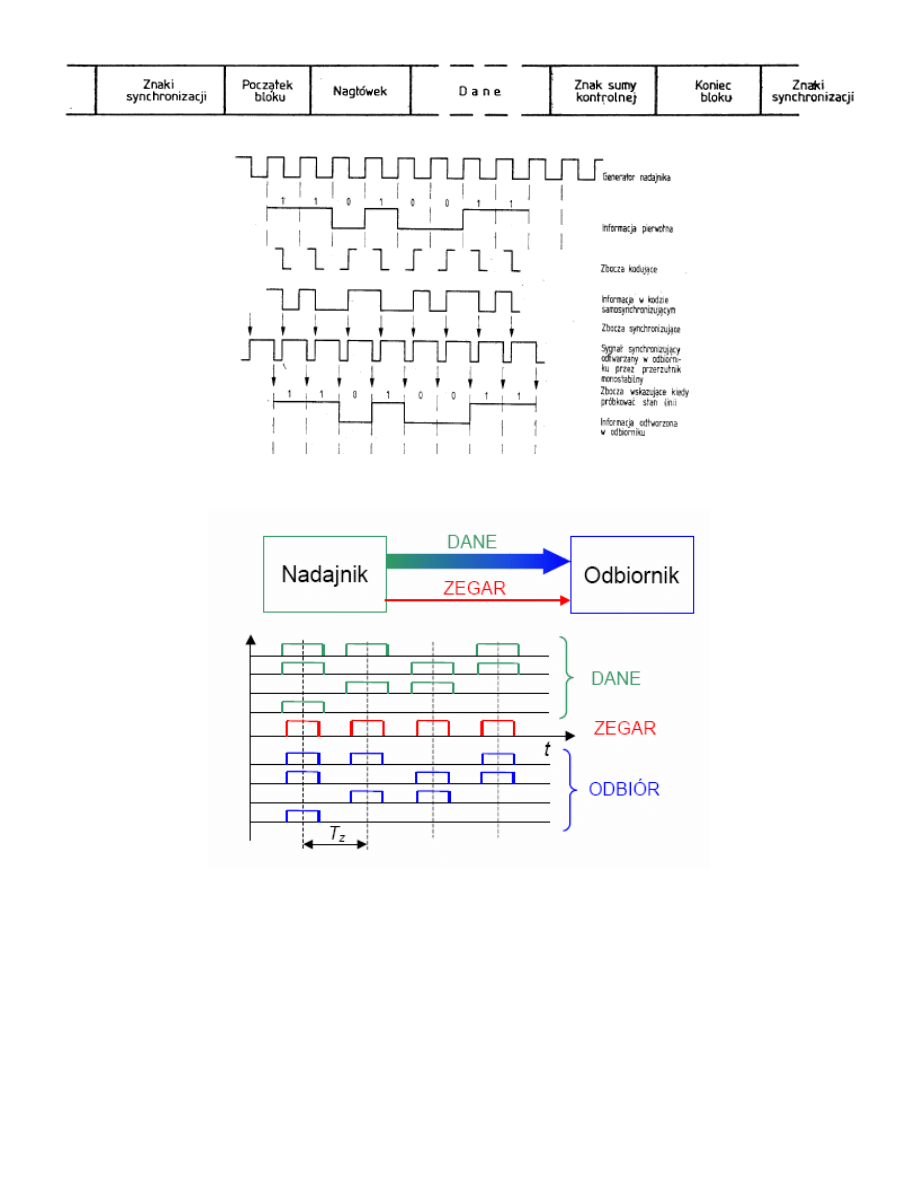

TRANSMISJA SYNCHRONICZNA - nadawanie i odbieranie poszczególnych znaków słowa odbywa się w określonych

przedziałach czasu, np. synchronicznie z taktem zegara. Zaletą jej jest prostota, wadami koniecznośd jednakowej i stałej

szybkości nadawania i odbioru informacji przez jednostki funkcjonalne systemu, brak pewności, czy nadana informacja

została odebrana przez odbiorcę, wrażliwośd na zakłócenia impulsowe na linii synchronizacji.

Przy transmisji synchronicznej zegar nadajnika bezpośrednio synchronizuje odbiornik i nie ma potrzeby stosowania bitu

startu. Dane zwykle przekazuje się w postaci większych bloków zawierających dodatkowe informacje kontrolne.

TRANSMISJA ASYNCHRONICZNA – poszczególne znaki lub słowa wysyłane mogą byd w dowolnych odstępach

czasowych, ale dzięki sygnalizowaniu początku i kooca transmisji każdego słowa następuje synchronizacja nadawania i

odbioru w uczestniczących w transmisji jednostkach systemu.

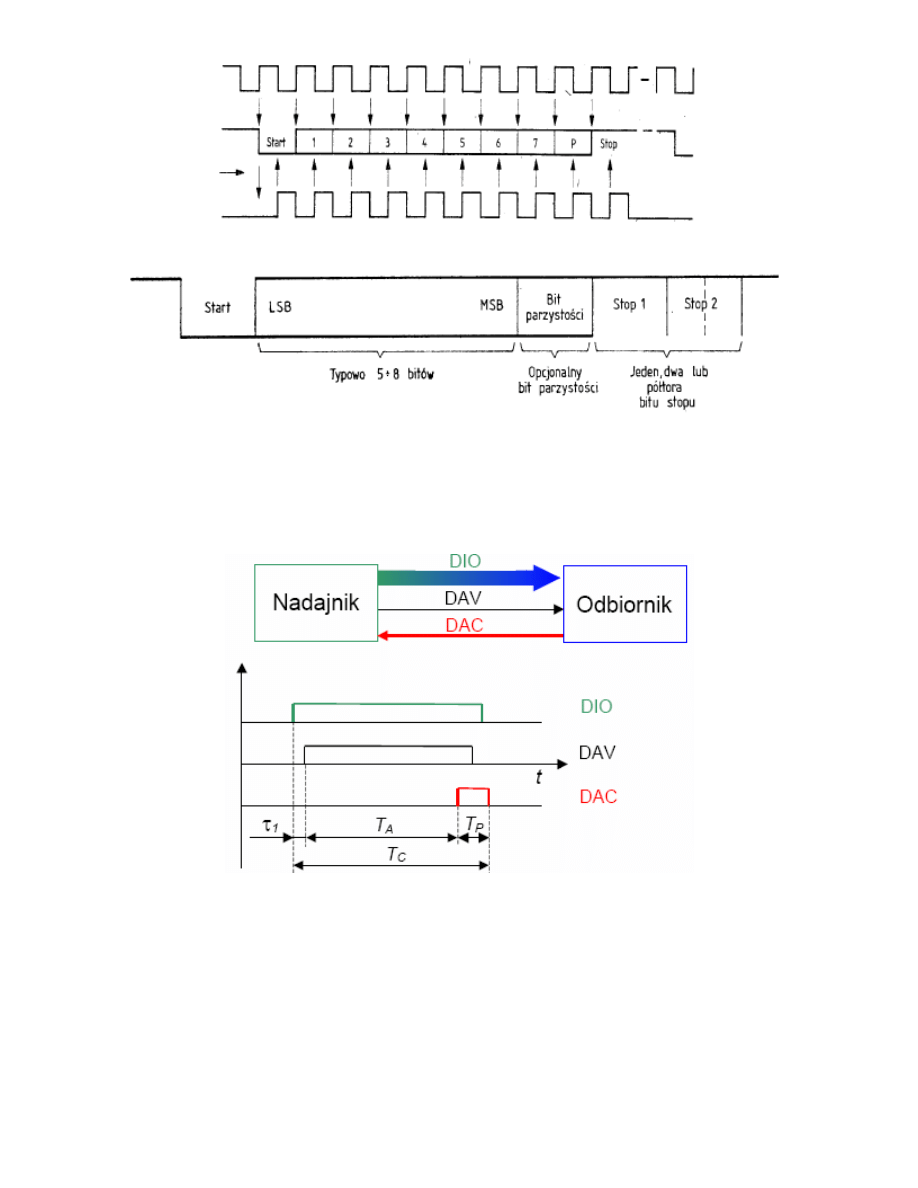

Przy zastosowaniu transmisji asynchronicznej (start-stop) nadajnik umieszcza przed ciągiem danych bit startu.

Odbiornik wykrywa ten bit i synchronizuje się tak, by prawidłowo odczytad poszczególne bity. By było to możliwe

odbiornik musi mied informację z jaką prędkością nadaje nadajnik.

Oprócz bitów danych (zwykle 5 do 8) przekazuje się często bit parzystości, który umożliwia wykrycie zakłóceo w

transmisji

Odmiany transmisji asynchronicznej:

metoda „XON-XOFF” (bez potwierdzenia) stosowana w transmisji szeregowej,

przesyłanie z potwierdzeniem (handshake) dwuprzewodowym,

przesyłanie z potwierdzeniem (handshake) trójprzewodowym.

Opis działania Handshake

Linie kontroli współpracy (handshake):

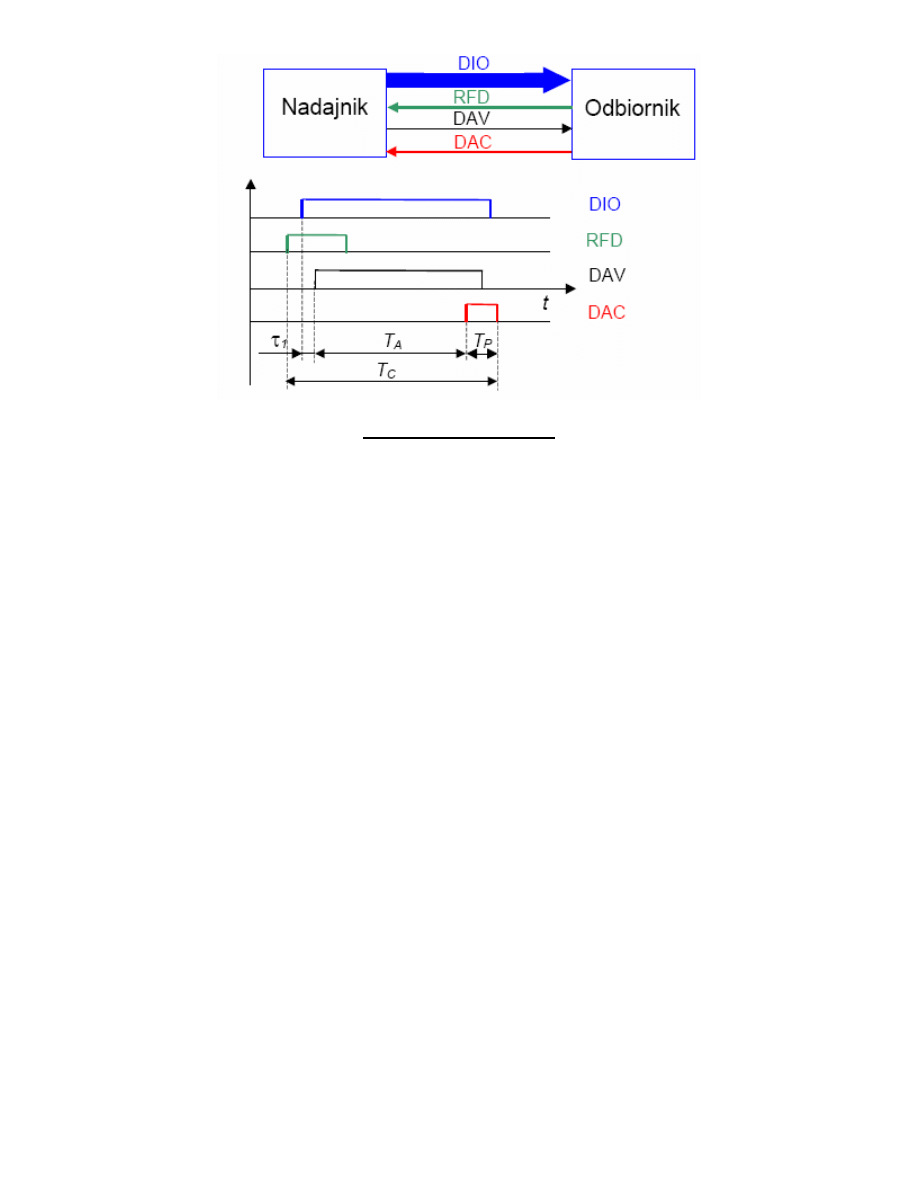

Trzy linie asynchronicznie kontrolują transfer danych pomiędzy urządze-niami na zasadzie dwustronnego potwierdzenia.

Wykorzystanie wszystkich trzech nazywamy trzyliniowym handshake'm. Proces ten gwarantuje, że dane na linii danych

są wysyłane oraz odbierane przez urządzenia bez błędów transmisji i jest on nazywany cyklem synchronizacji.

W zasadzie do wysyłania danych z potwierdzeniem dwustronnym wystarczą dwie linie (DAV, NRFD), czyli handshake

dwuliniowy. Dodanie trzeciej linii (NDAC) przyspiesza transmisję przez umożliwienie wcześniejszej zmiany danych przez

nadajnik, czyli nowe dane na magistrali już się stabilizują, podczas gdy odbiorniki jeszcze przetwarzają dane poprzednie.

Przy kontroli dwuliniowej dane mogą byd umieszczone na magistrali dopiero po zasygnalizowaniu gotowości wszystkich

odbiorników.

DAV (Data Valid) - dane ważne.

Nadajnik wprowadza stan aktywny na tej linii gdy na magistrali znajdują się ustabilizowane dane. Podczas zmiany danych

i w trakcie trwania stanu nieustalonego na liniach DIO nadajnik musi utrzymad linie DAV w stanie nieaktywnym.

NRFD (Not Ready For Data) - odbiorcy nie są gotowi do odebrania informacji.

Odbiornik wprowadza tą linię w stan aktywny, gdy nie jest przygotowany do odbierania danych, natomiast nadajnik nie

może sygnalizowad nowych danych na magistrali pomimo, że mogą one tam występowad. Gdy na linii NRFD jest stan

nieaktywny, znaczy to, że wszystkie odbiorniki są gotowe do przyjmowania danych, a nadajnik może zasygnalizowad na

linii DAV ważnośd danych.

NDAC (Not Data Accept) - dane nie zostały przyjęte.

Stan aktywny oznacza, że jest w systemie przynajmniej jeden odbiornik, który nie wykorzystał informacji z magistrali, w

związku z czym nadajnik musi utrzymad dane do czasu aż sytuacja ta się nie zmieni. Gdy linia jest nieaktywna, nadajnik

może wysyład nowe dane.

Zasada działania handshake'u trzyliniowego.

Proces transmisji danych rozpoczyna się od sprawdzenia przez nadajnik stanu gotowości odbiorników (t1). Jeśli

urządzenia są gotowe (linia NRFD), to nadajnik wysyła bajt na szynę danych (t2) oraz zgłasza jego ważnośd, wysterowując

odpowiednio linie ważności bajtu (t3). Odbiorniki po stwierdzeniu ważności bajtu, likwidują stan swojej gotowości (t4) i

przystępują do odbioru, czyli wpisania bajtu do swoich buforów wewnętrznych. Stan przyjęcia potwierdzają sygnałami

akceptacji (t5-t6), z których tworzony jest globalny sygnał akceptacji, będący iloczynem sygnałów pochodzących od

poszczególnych odbiorników. Nadajnik, stwierdzając akceptacje bajtu, likwiduje sygnał ważności (t7) i przygotowuje do

wysłania kolejny bajt, jednocześnie oczekując na gotowośd odbiorników. Po uzyskaniu stanu gotowości wszystkich

odbiorników (t8-t9) cykl pracy się powtarza. Tym razem współpraca odbiornika przebiega poprawnie, ponieważ nadajnik

nie wyśle bajtu dopóty, dopóki wszystkie odbiorniki nie uzyskają gotowości. Nadajnik nie usunie również bajtu z szyny

DIO dopóki wszystkie odbiorniki go nie zaakceptują.

Porównanie synchronicznych i asynchronicznych

Transmisja synchroniczna

Transmisja asynchroniczna

Przewidywalny czas transmisji (ustalony)

Może byd mało efektywny

Wszystkie urządzenia muszą pracowad z taką samą

częstotliwością

Czas transmisji może byd bardzo szybki gdy urządzenia są

szybkie

Nie wiadomo ile potrwa transmisja

Bardziej optymalne

Rodzaje transmisji

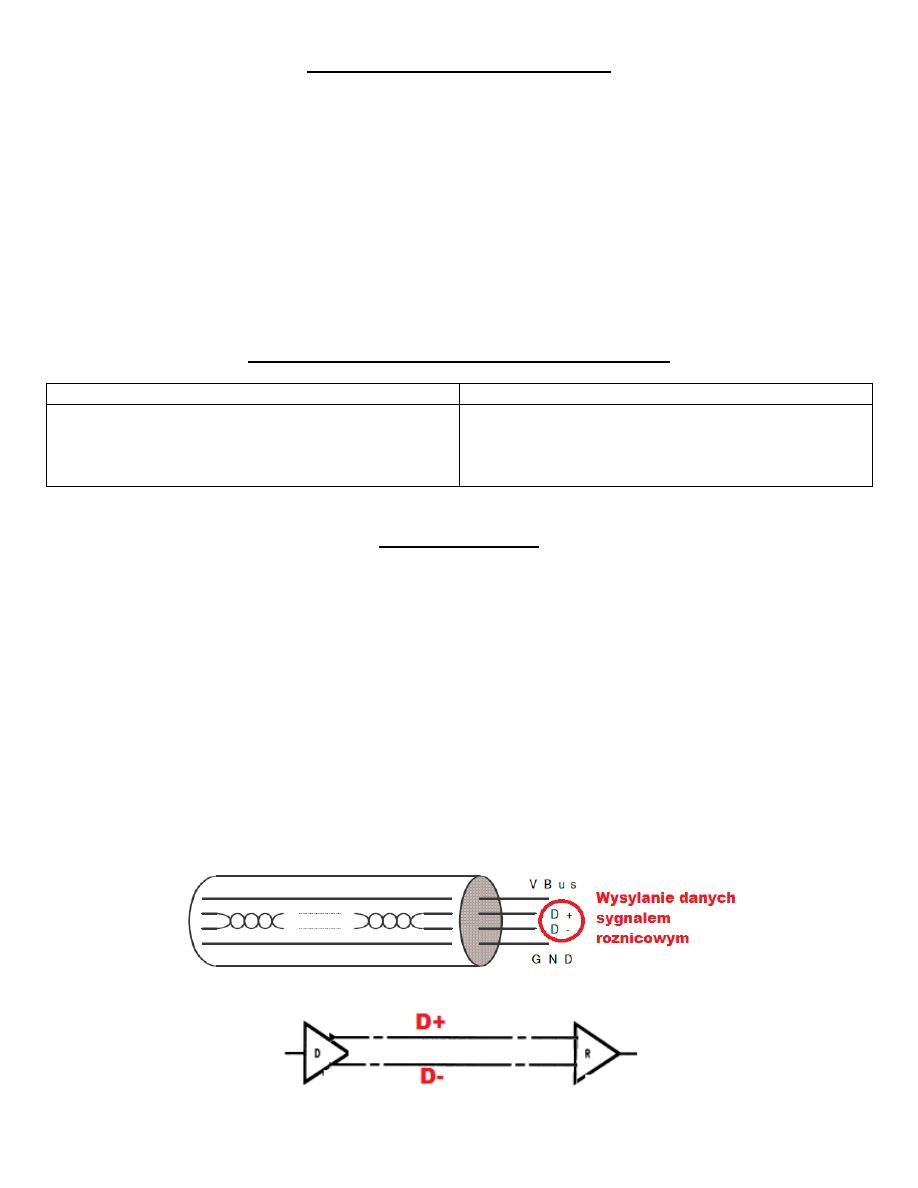

Niesymetryczne – Wszystkie sygnały ustalane są wobec jednego sygnału – HASH

Stan wysoki, niski ustalany wobec GND

1. Tylko 1 dodatkowa linia

2. Transmisja mało odporna na zakłócenia

Różnicowe – 2 linie, liczy się ich różnica

1. Jeśli są zakłócenia to odbiornik je tłumi,

2. Szybsze

3. Lepsze

4. Np. USB, SATA, fire-wire

Konstrukcja różnicowa:

Konstrukcja niesymetryczna:

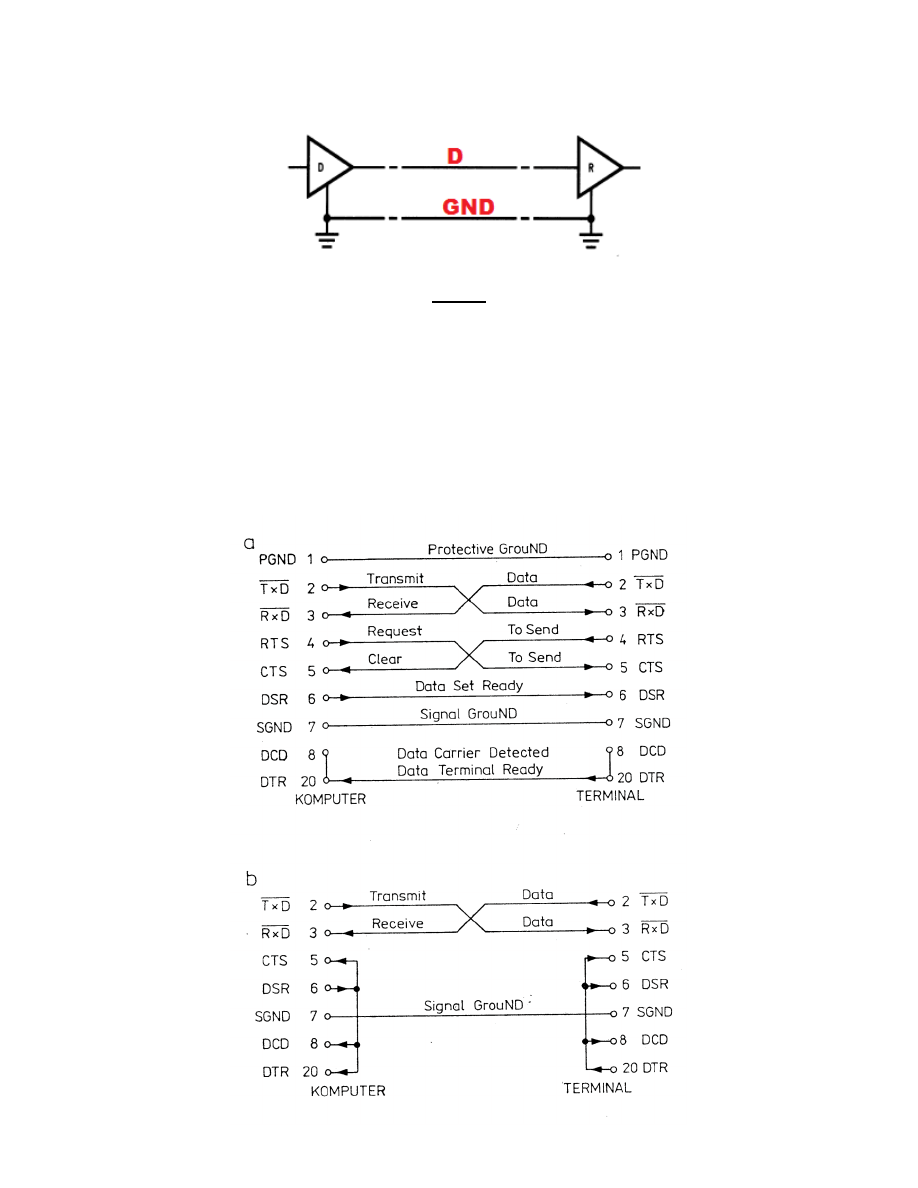

RS232

Interfejs RS232C jest szeregowym interfejsem napięciowym przeznaczonym do połączenia dwóch urządzeo (pierwotnie

modemu i komputera lub terminala. Odległośd urządzeo jest niewielka, interfejs jest mało odporny na zakłócenia. Duża

popularnośd powoduje, że jest często spotykany. W maksymalnie rozbudowanej wersji RS232C zawiera kilkanaście

sygnałów sterujących, ale przeważnie spotyka się realizacje znacznie okrojone.

Zastosowanie interfejsu do połączenia z urządzeniem innym niż modem wymaga zdefiniowania funkcji linii sterujących.

Zwykle pary RTS/CTS lub DTR/DSR używa się do przesyłania potwierdzeo. Przy połączeniu dwóch komputerów stosuje się

połączenia pokazane obok (tak zwany kabel null modem).

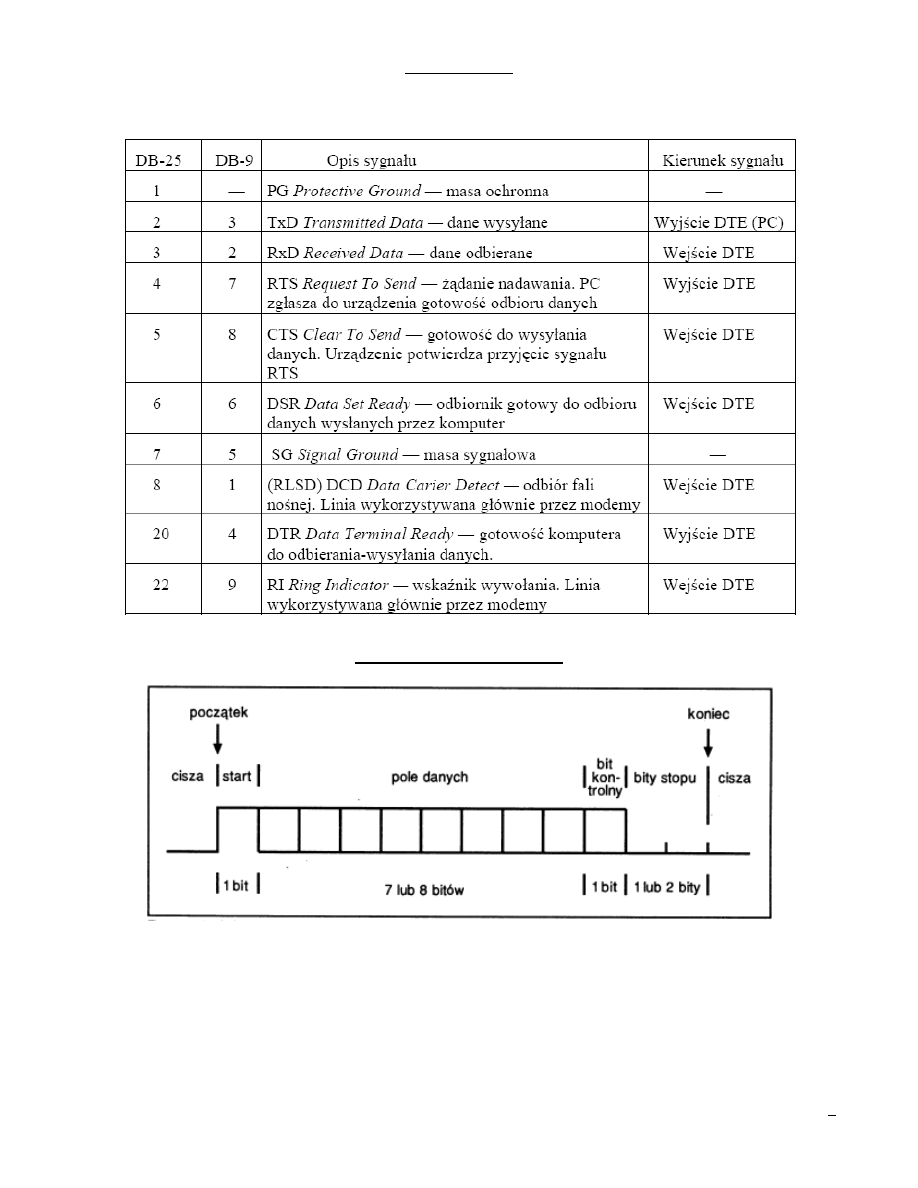

Opis sygnałów

Format wysylanych danych:

Warunki które musi spełnid zarówno nadajnik jak i odbiornik to :

Takie same szerokości ramek

Takie same szybkości

Wadami są :

Zegary są niedokładne

Zagrożenie że dwa razy otrzymamy ten sam bit, najbezpieczniej podczas odbioru celowad w środek ramki tj

Konwersja napięc dla RS-232

-15 – -3 V -> 1 logiczna

+3 - +15 -> 0 logiczne

Do transmisji minimalnie potrzebujemy portów TxD i RxD

Ogólna charakterystyka

Magistrala I2CBUS składa się z dwóch linii, które umożliwiają przesyłanie danych między dowolnymi urządzeniami

podłączonymi do magistrali. Każde z urządzeo rozpoznawane jest przez unikalny adres przesyłany przeważnie na

początku transmisji. Urządzenia mogą byd nadawcami lub odbiorcami, w zależności od pełnionej funkcji w systemie. Na

przykład zwykły sterownik wyświetlacza LCD jest tylko odbiorcą danych, natomiast układy pamięciowe mogą dane

zarówno przyjmowad jak i nadawad. Oprócz podziału na nadajniki i odbiorniki przypisuje się jeszcze urządzeniom pewien

status, przy czym wyróżnia się dwa statusy master i slave. Master to urządzenie, które inicjuje prowadzi transmiję

danych generując sygnały zegarowe. Dowolne poprawnie zaadresowane urządzenie nazywane jest slave.

Interfejs I2CBUS pozwala na podłączenie do magistrali kilku urządzeo os tatusie master. Oznacza to że w systemie może

się znaleźd kilka urządzeo potrafiących przejąd sterowanie sygnałami magistrali. Dobrym przykładem jest układ

składający się z dwóch równorzędnych mikrokomputerów jednoukładowych komunikujących się ze sobą

2 linie: danych SDA(Serial Dataline) i zegarowa SCL(Serial ClockLine),

każde urządzenie ma swój adres

urządzeniami są typu "master" i "slave",

magistrala typu "multi-master" -są metody detekcji kolizji na magistrali jak i procedury arbitrażu, zapobiegające

utracie danych, gdy dwa lub więcej urządzeo typu "master" jednocześnie inicjuje transfer danych,

szeregowa, zorientowana 8-bitowo, dwukierunkowa transmisja danych o przepływności maksymalnej 100 kbit/s

w trybie STANDARD i 400 kbit/s w trybie FAST,

wbudowane filtry eliminujące zakłócenia mogące naruszyd integralnośd danych,

liczba układów scalonych limitowana jest tylko jej maksymalną pojemnością 400 pF.

Funkcjonalnośd interfejsu

funkcjonalnie bloki na schemacie blokowym -szybkie przejście z fazy schematu blokowego do koocowego

schematu ideowego

brak potrzeby projektowania interfejsu magistrali -wbudowany w układ scalony

zintegrowanie adresowania z protokołem transferu danych -całkowite programowe zorientowanie aplikacji

ten sam typ układu scalonego może byd często użyty w różnych aplikacjach

układy scalone mogą byd dodawane lub usuwane z systemu bez używania dodatkowych układów na magistrali

uproszone wykrywanie błędów i diagnostyka magistrali

czas konieczny na stworzenie oprogramowania może byd zredukowany poprzez wykorzystanie bibliotek z

najczęściej używanymi funkcjami

Korzyści

prostota magistrali I2C (tylko 2 linie) minimalizują liczbę połączeo:

o małą liczbę koocówek IC

o mała ilości ścieżek -zmniejsza powierzchnię płytek drukowanych

całkowite zintegrowanie protokołu magistrali I2C eliminuje koniecznośd stosowania dekodera adresowego czy

innych IC

zdolnośd do pracy w trybie "multi-master" ułatwia testowanie,

dostępnośd IC w obudowach typu SO (SmallOutline), VSO (VerySmallOutline) jak również DIP (DualinPackages)

zmniejszają wymaganą powierzchnię płytki drukowanej

CMOS

o mały pobór mocy, duża odpornośd na szumy

o szeroki zakresu napięcia zasilania oraztemperatury pracy

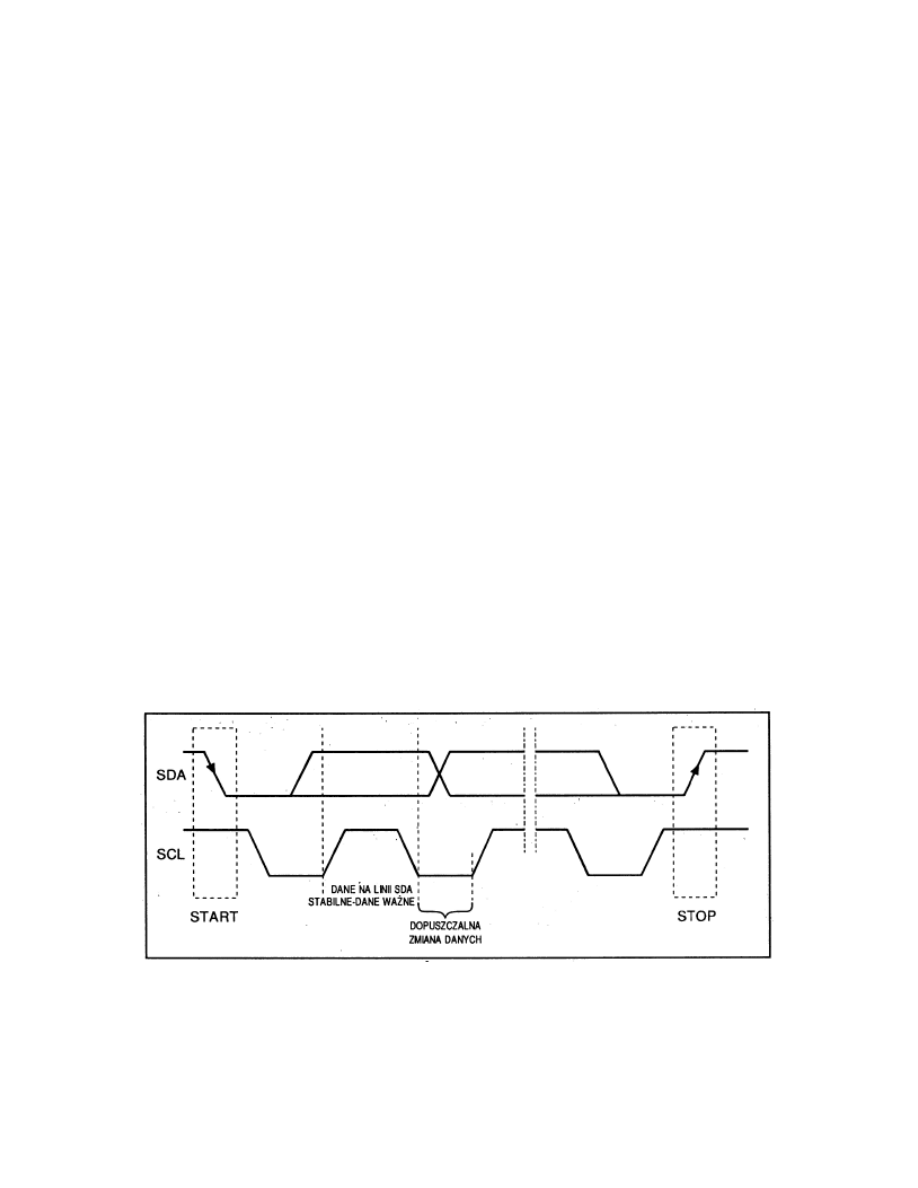

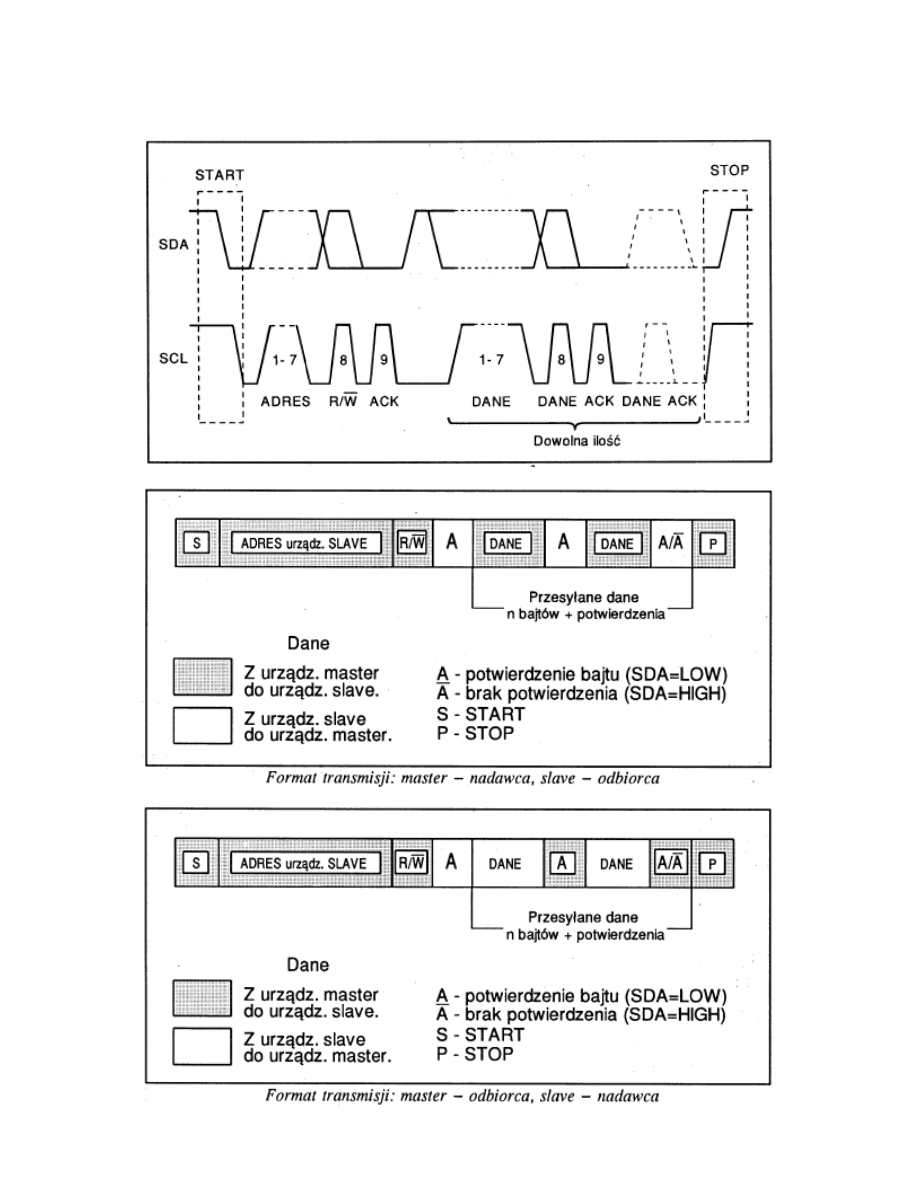

Szeregowa magistrala interfesju I2CBUS składa się z dwóch, dwukierunkowych linii: jednaj dla sygnału danych (Serial

Data – SDA) oraz drugiej dla sygnału zegarowego (Serial Clock – SCL). Dla zapewniania poprawnej wymiany informacji

przez magistralę zdefiniowano następujący protokół:

1. Inicjalizacja transmisji danych może nastąpid tylko wtedy gdy magsitrala nie jest zajęta

2. Podczas transmisji danych, sygnał na linii SDA musi bydstabilny (nie może się zmieniad), gdy stan sygnału na linii

SCL jest wysoki. Zmiany sygnału na linii SDA podczas wysokiego stanu na linii SCL są interpretowane jako sygnały

sterujące (control). W związku z tym określono następujące warunki magistrali :

Magsitrala nie zajęta (Bus Not Busy) – linie SDA i SCL są w stanie wysokim

Start transmisji danych – zmiana stanu linii SDA z wysokiego na niski, dokonana podczas wysokiego

stanu linii SCL

Stop (zatrzymanie) transmisji danych – zmiana stanu na linii SDA, z niskiego na wysoki dokonana podczas

wysokiego stanu linii SCL

Dane ważne (Data Valid) – stany sygnału na linii SDA reprezentują „dane ważne”, gdy (po wystąpieni

warunku startu) pozostająstabilne przez czas trwania stanu wysokiego linii SCL. Zmiana danych w linii

SDA może nastąpid podczas trwania stanu niskiego linii SCL. Na rysunku przedstawiono

sekwnecjęzdarzeo zachodzących podczas transmisji informacji na magistrali I2C. Każda transmisja

inicjowana jest poprzez wystąpienie warunku start i kooczona poprzez wystąpienie warunku stop.

Wykrycie warunków start i stop jest zadaniem sterownika magistrali I2Cbus. Jeżeli nie wykorzystuje sięspecjalizowanego

sterownika należy testowad stan linii SDA przynajmniej dwa razy częściej niż okres sygnału zegara na linii SCL

Znacznikami początku i kooca transmisji są odpowiednio warunki start i stop. Ilośd bitów transmitowanych pomiędzy

startem i stopem nie jest limitowana.

Każdy bajt wysyłany linią SDA ma długośd 8 bitów. Liczba bajtów po rozpoczęciu transmisji do jej zakooczenia jest

dowolna. Każdy wysyłany bajt musi byd potwierdzony przez odbiornik. Dane wysyłane są od najstarszego bitu do

najmłodszego. Jeśli odbiornik nie jest w stanie przyjąd kolejnego kompletnego bajtu, to dla poinformowania nadajnika i

zwolnienia transmisji ustala stan niski na linii zegara SCL. Wznowienie transmisji może nastąpid natychmiast po tym, jak

odbiornik zwolni linię SCL, usuwając z niej stan niski.

Na magistrali I2CBUS niezbędne są potwierdzenia przesyłanych danych które wystawiane są po przesłaniu każdego bitu.

Urządzenie master zobowiązane jest do generowania dodatkowego taktu sygnału zegarowego dla uchwycenia bitu

potwierdzenia. W czasie potwierdzenia, nadajnik ustawia swoje wyjście danych na H,co umożliwia odbiornikowi

wysyłanie potwierdzenia poprzez wymuszenie niskiego stanu na linii SDA. Potwierdzenie pojawia się w czasie trwania

wspomnianego, dodatkowego taktu zegarowego.

Mogą jednak wystąpid sytuacje , w których potwierdzenia nie będą wystawiane. Jeśli odbiornik slave nie potwierdził

wysyłanego do niego adresu własnego (na przykład z powodu wykonywania jakieś funkcji czasu rzeczywistego) lub

któregokoliwek z przesłanych następnie bajtów, to linię SDA powinien pozostawid w stanie wysokim, w urządzenie

master powinno wysład warunek stop.

Jeśli odbiornik master przyjmuje dane to powinien sygnalizowad nadajnikowi koniec danych przez nie potwierdzenie

ostatniego bjtu danych. Nadajnik pozostawia linię SDA w stanie wysokim, umożliwiając urządzeniu master zakooczenie

transmisji warunkiem stop.

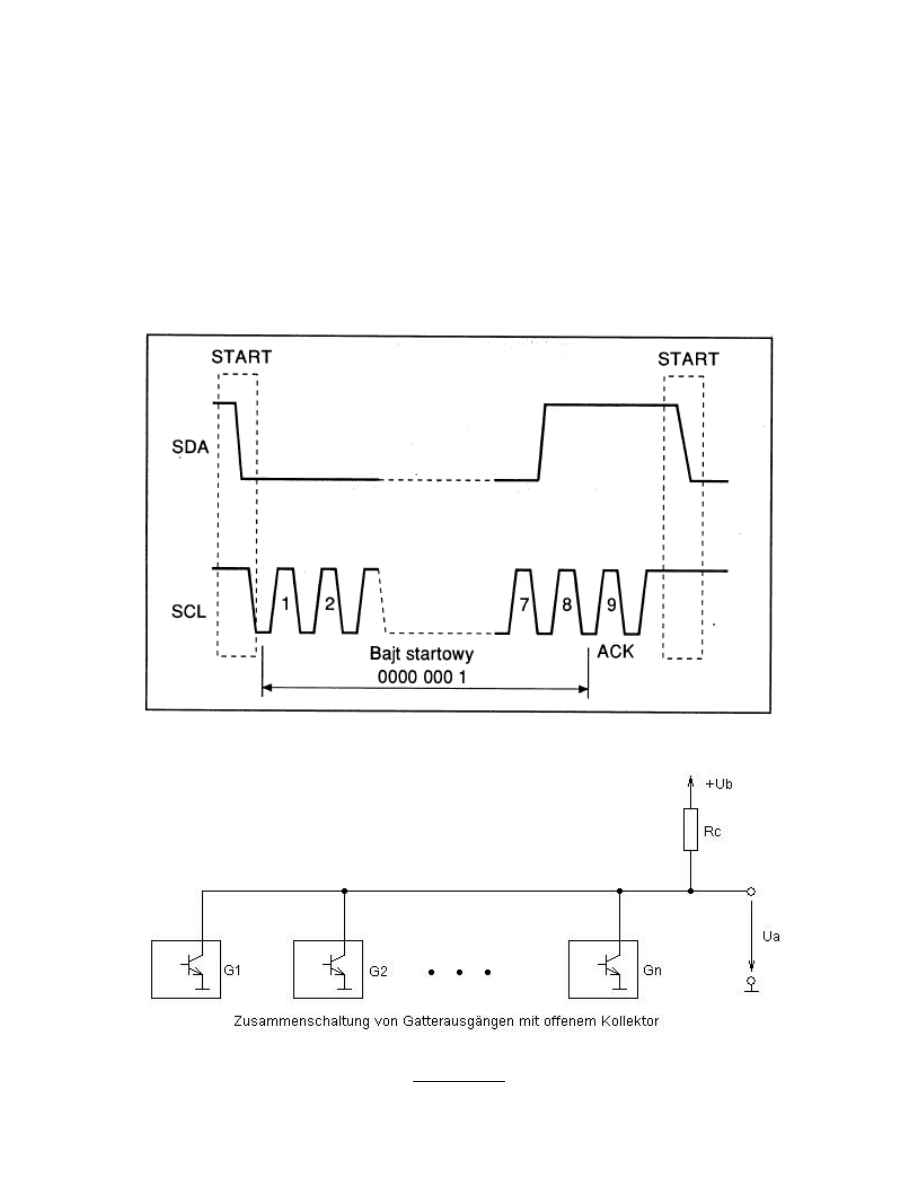

Arbitraż:

W systemie I2CBUS może dojśd do sytuacji, że więcej niż jedno urządzenie zechce przejąd kontrolę nad łączem (byd

masterem). Zdefiniowani więc specjalną procedurę arbitrażową, która wyłania jednego mastera spośród urządzeo

rywalizujących o sterowanie transmisją. Arbitraż oparto na zasadzie kontroli zgodności stanu linii SDA z wartością

logiczną bitu wyprowadzonego przez dane urządzenie. Odczyty stanu linii SDA odbywają się w ściśle określonych

momentach wyznaczanych sygnałem zegarowym.

Trzeba pamiętad, że podczas arbitrażu dwa lub więcej urządzenia wyprowadzają swoje bity na linię danch i może się

zdarzyd, że gdy jedno wyprowadza jedynkę, to drugie wyprowadza zero. Na linii SDA w takim przypadku ustali się stan

niski, ponieważ dla podłączonych do tej linii urządzeo realizuje ona funkcję iloczynu na drucie. Urządzenie które chciało

wyprowadzid jedynkę po stwierdzeniu, że na linii SDA jest zero, wypada z arbitrażu (wyłącza swoje wyjście). Widad więc,

żę przedstawione rozwiązanie preferuje urządzenie, które w czasie arbitrażu wysyła najniższa wartośd binarną.

Dla poprawnego przeprowadzenia arbitrażu konieczna jest synchronizacja sygnałów zegarowych urządzeo, które walczą

o sterowanie transmiją. Wszystkie urządzenia generują swoje własne sygnały sygnały zegarowe na linii SCL umożliwiając

przesył danych oraz potwierdzenia. Dane na linii SDA są ważne tylko dla wysokiego stanu linii zegara. Synchronizację

przesyłu danych uzyskuje się poprzez wykorzystanie funkcji iloczynu na drucie, tym razem realizowanej na linii SCL. Linia

SCL będzie tak długo w stanie niskim, aż wszystkie urządzenia nie zwolnią tej linii. Długośd stanu wysokiego na linii SCL

jest zatem określona przez czas trwania najkrótszego okresu spośród sygnałów zegarowych, a długośd stanu niskiego

przez czas trwania najdłuższego okresu spośród sygnałów zegarowych.

Urządzenie master, które utraciło kontrolę nad mgistralą, może generowad tlyko sygnały zegarowe do kooca bajtu, przy

którym utraciło kontrolę. Arbitraż nie jest dozowolony w trakcie powtwarzanego warunku STOP lub START.

Przebieg transmisji

Transmisje rozpoczyna warunek start, po którym zostaje wysłany siedmiobitowy adres urządzenia slave. Kierunek

przyslu danych określa bit R/W wyprowadzany w następnej kolejności. Zerowa wartośd tego bitu oznacza nadawanie do

urządzenia slave (operacja zapisu), natomiast jeden, oczekiwanie na dane z urządzenia slave (operacja odczytu). Dalej

odbywa się właściwa wymiana danych, potwierdzona przez odbiornik impulsami ACK po skompletowaniu każdego bajtu.

Koniec transmisji wyznacza warunek stop.

Interfejs ten jest używany np. w telewizorach.

Komunikuje się z ukłądami scalonymi lub modułami na małych odległościach w ramach jednego systemu

Połączenie komputera z monitorem

Kontrola wiatraczków w jednostce centralnej

Jest to synchroniczny szeregowy interfejs.

Można łączyd wiele urządzeo (do około 112 – 127 urządzeo)

Każde urządzenie ma 7-bitowy adres

Jest to magistrala typu „multi-master” (kilka urządzeo master)

Master – ma możliwośd inicjowania transmisji

Krótki skrót :

Porcja danych jest 8 bitowa + bit ACK

Transmisja half-duplex w dwóch kierunkach

Urządzenie musi mied przynajmniej prędkośd 100 kbit/s w I wersji

Mogą pracowad z dowolnie wolną prędkością czyli np. 1bit/ dzieo, można również ręcznie sterowad sygnałem

Maksymalny obszar może byd duży lub bardzo duży ale występuje wtedy limit pojemności na linii

Działa w topologii magistralowej

Duża swoboda łączenia urządzeo

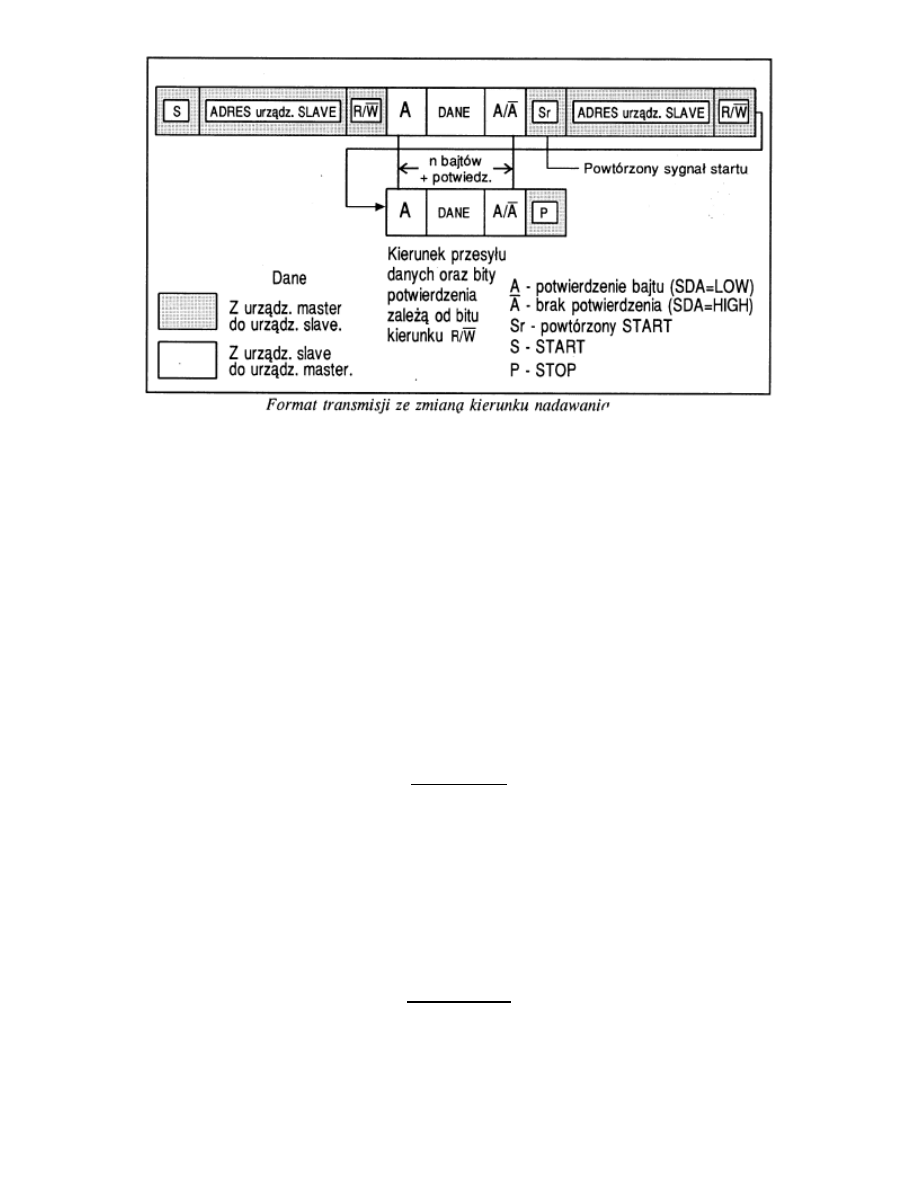

Adresowanie:

Po warunku start rozpoczynającym transmisje, zostaje wysłany bajt, w którym siedem bitów reprezentuje adres

urządzenia slave, a najmniej znaczący bit (LSB) określa kierunek transmisji. Wszystkie urządzenia po wykryciu warunku

start porównując odebrany adres ze swoim adresem sprzętowym. Rozpoznanie adresu własnego oznacza zaadresowanie

urządzenia jako odbiornik slave lub nadajnik slave, w zależności od bitu R/W.

W niektórych urządzeniach adres własny składa się z dwóch części: stałej oraz programowalnej. Taki przypadek

występuje w układach scalonych o niedużej inteligencji, wyposażonych w proste sterowniki interfejsu. Kilka starszych

bitów adresu ( zazwyczaj od 4 do 6 ) jest ustawionych na stałe przez producenta, a pozostałe młodsze bity użytkownik

może zaprogramowad poprzez łączenie ich wyprowadzeo do zasilania lub masy. Ilośd bitów programowalnych ogranicza

ilośd układów tego samego typu ( a więc posiadających identyczną stałą częśd adresu), które mogą byd jednocześnie

podłączone do magistrali. Trzy bity programowalne pozwalają na podłączenie do ośmiu układów tego samego typu.

W niektórych przypadkach wykorzystuje się prioretytezację – im wyższy adres tym ważniejszy.

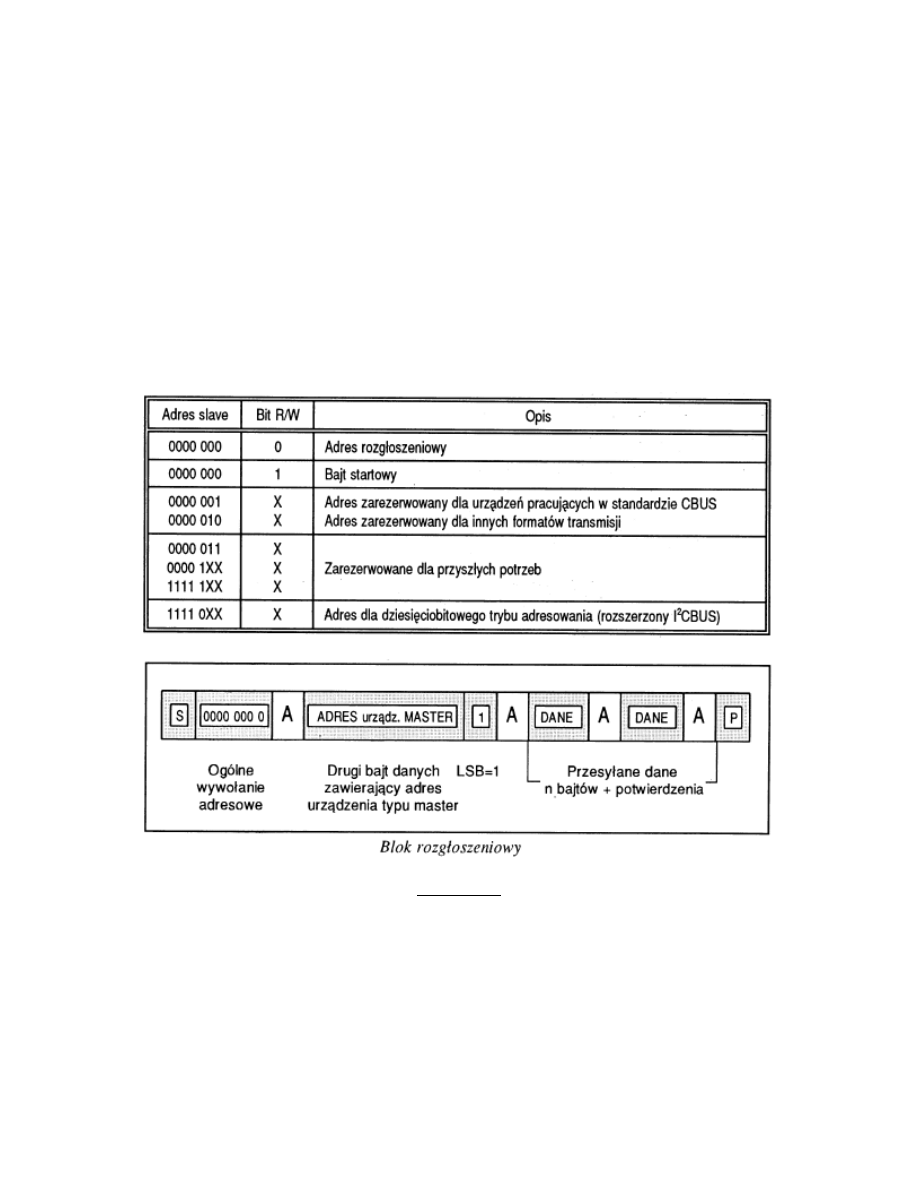

Pewnym wyjątkiem w sposobie adresowania jest adres rozgłoszeniowy (general call), który powoduje zaadresowanie

wszystkich urządzeo w systemie. Adres ten, przynajmniej teoretycznie, powinien byd potwierdzony przez wszystkie

urządzenia. Niektóre urządzenia mogą byd jednak niewrażliwe na ten sposób adresowania. Po adresie rozgłoszeniowym

wysyłany zostaje drugi bajt określający polecenie.

W interfejsie I2CBUS zarezerwowano dwie grupy po osiem adresów do celów przedstawionych w tablicy.

Bajt startu:

Aby odciążyd CPU mikrokontrolerów nie posiadających sprzętowego sterownika interfejsu od próbkowania magistrali z

dużą częstotliwością, wprowadzono specjalną procedurę startową, znacznie dłuższą od nomrlanego warunku start.

Procedura ta składa się z:

Normalnego warunku start (S)

Bajtu startowego 00000001

Impulsu potwierdzenia ACK

Potórzeonego warunku start (Sr)

Po wysłaniu warunku start przez urządzenie master żądające dostępu do magistrali, generowany jest bajt startowy. Inny

mikrokontroler (nie wyposażony w sterownik interfejsu) może próbkowad linię SDA ze stosunkowo małą częstotliwością,

taką jednak aby zdążył wykryd któreś z siedmiu zer bajtu startowego. Po detekcji niskiego poziomu na linii SDA, mk

powinien zmienid szybkośd próbkowania magistrali na wyższą, pozwalająca na rozpoznanie powtórzonego warunku start

(Sr), który jest już normalnym warunkiem synchronizacyjnym.

Sterownik sprzętowy interfejsu I2CBUs zostanie wyzerowany po odebraniu Sr, co oznacza zignorowanie bajtu

startowego.

Po bajcie startowym generowany jest impuls potwierdzenie, lecz nie przez urządzenie odbierające, aprzez sam nadajnik.

Chodzi tu o zachowanie zsady potwierdzania każdego bajtu. Bajt startowy nie może byd potwierdzony przez żadne

urządzenie odbierające.

Schemat połączenia iloczynu logicznego na drucie (wired-and)

Dodatkowo:

W I2C wymyślono bardzo prosty i wygodny sposób nadawania adresów

4 najstarsze bity układu ustalane są przez producenta, cztery kolejne podłączone są do masy lub zasilania (jedna

z możliwości

adresów

Są także układy które mają 4,2 linie do sterowania (sterowanie za pomocą podłączenia nóżek układu scalonego

do masy lub zasilania)

Nowsze wersje przewidują większą szybkośd *Fast mode, High-speed mode]

Przewidziane jest rozszerzenie powierzchni adresowej

1-wire

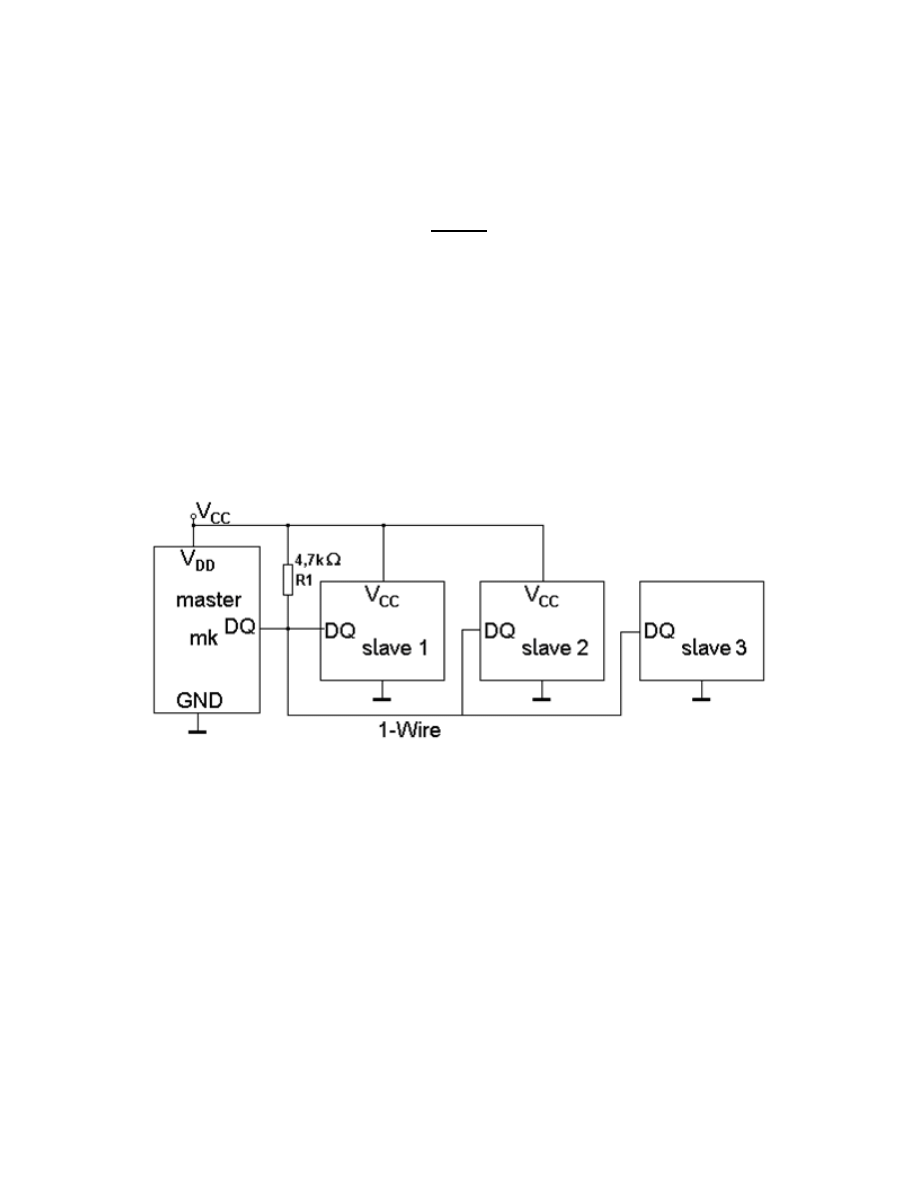

Interfejs 1-Wire został opracowany przez firmę Dallas Semiconductor ( obecnie Dallas – Maxim ). Jest on przeznaczony

do przesyłania informacji pomiędzy układem nadrzędnym master - mikrosterownik a układami podrzędnymi slave (np.

termometry, układy identyfikacji, pamięci SRAM i EEPROM, programowalne klucze). Transmisja odbywa się w obu

kierunkach z wykorzystaniem jednego przewodu sygnałowego (oprócz masy), który jednocześnie może byd wykorzystany

do zasilania układów do niego podłączonych. Dane przesyłane są z prędkością od bliskiej 0 do 16,3 kbps w trybie

standard oraz do 115 kbps w trybie overdrive. Każde z urządzeo podłączonych do magistrali musi mied wyjście typu

otwarty dren, a linia sygnałowa DQ jest połączona do zasilania przez rezystor podciągający o wartości około 5kW. Zatem

w stanie bezczynności linia DQ jest w stanie wysokim. Magistrala nie ma ustalonego formatu danych. Sposób przesyłania

informacji zależy od konfiguracji układów podrzędnych. Zawsze jednak jako pierwszy jest przesyłany bit najmniej

znaczący.

Protokół wymiany danych poprzez magistralę 1-Wire składa się z czterech podstawowych sekwencji:

1. inicjalizacji (zerowanie magistrali),

2. wysłanie (zapis) zera,

3. wysłanie (zapis) jedynki,

4. odczyt bitu.

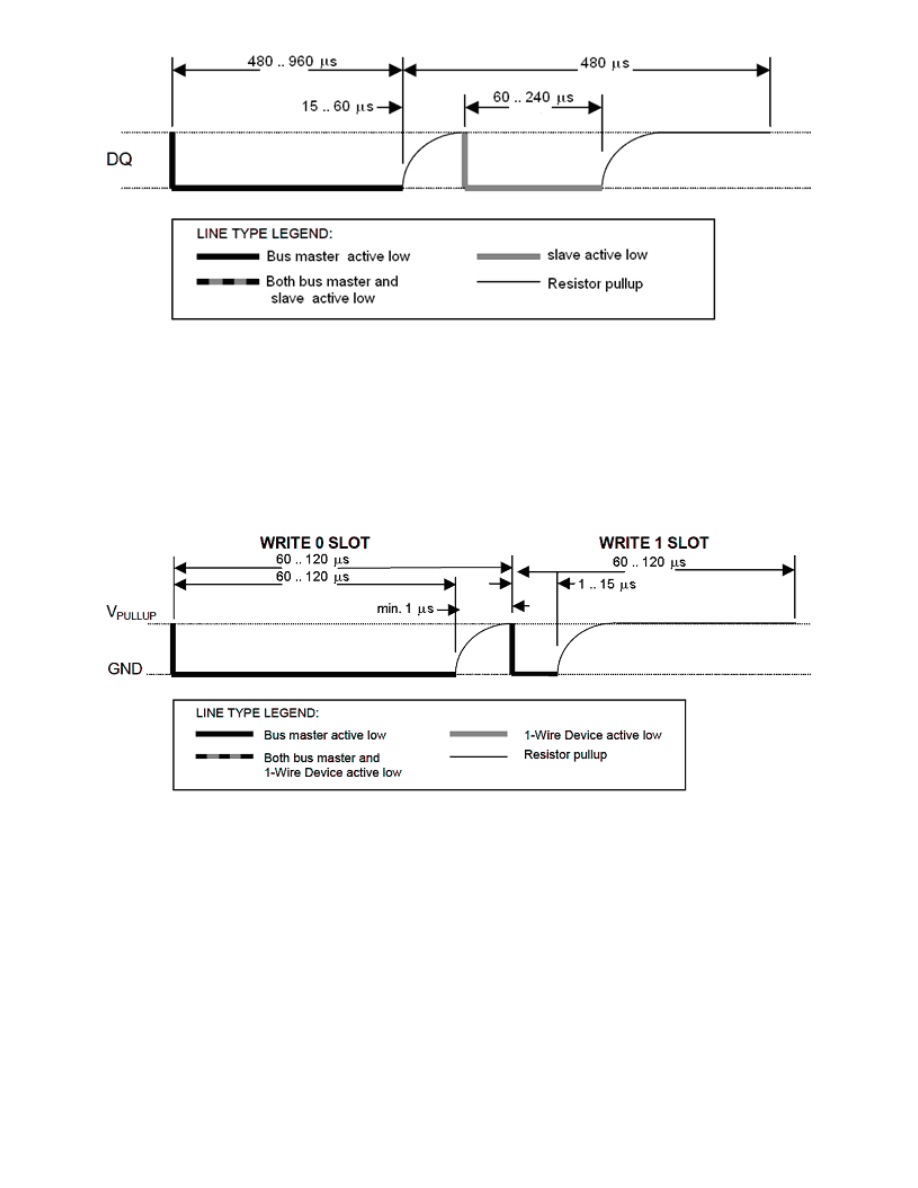

Sekwencja inicjalizacji rozpoczyna się wysłaniem na magistralę przez układ master (mikrosterownik) impulsu zerującego

o czasie trwania 480 .. 960 ms. Po tym czasie układ master przechodzi w stan odbioru i na magistrali pojawia się stan

wysoki. Po zidentyfikowaniu kooca impulsu zerującego układ slave odczekuje 15 .. 60 ms i wystawia na magistralę impuls

obecności (presence pulse) o czasie trwania 60 .. 240 ms. Sekwencja inicjalizacji umożliwia układowi master wykrycie

podłączonych do niej układów slave. Po czasie koniecznym do pełnej inicjalizacji układów podrzędnych możliwe staje się

przeprowadzenie normalnej transmisji danych.

Przebiegi sekwencji inicjalizacji dla magistrali 1-Wire:

Transmisja danych do urządzenia podrzędnego polega na generowaniu serii impulsów o poziomie niskim o odpowiedniej

długości, która definiuje stany logiczne „0” lub „1”. Długośd sekwencji zapisu lub odczytu musi się zmieścid w szczelinie

czasowej (time slot), która wynosi 60 .. 120 ms i jest inicjowana wymuszeniem przez układ master stanu niskiego na

magistrali. Nadanie logicznego „0” polega na wygenerowaniu impulsu o czasie trwania 60 .. 120ms, a następnie na

zwolnieniu magistrali i odczekaniu minimum 1ms przed nadaniem następnego bitu (rys. 3). Dla logicznej „1” generowany

impuls trwa 1 .. 15 ms, a następnie magistrala pozostaje zwolniona na minimum 45 ms ( maksymalnie 105 ms ) (rys. 3).

Transmisja logicznych „0” i „1” na magistrali 1-Wire

Przy emulacji programowej interfejsu 1-Wire, na czas generowania impulsów (zwłaszcza dla „1”) warto wyłączad

wszystkie przerwania mikrosterownika, gdyż wystąpienie przerwania w trakcie generacji impulsu może doprowadzid do

jego wydłużenia poza dopuszczalne granice, a co za tym idzie do zafałszowania transmisji.

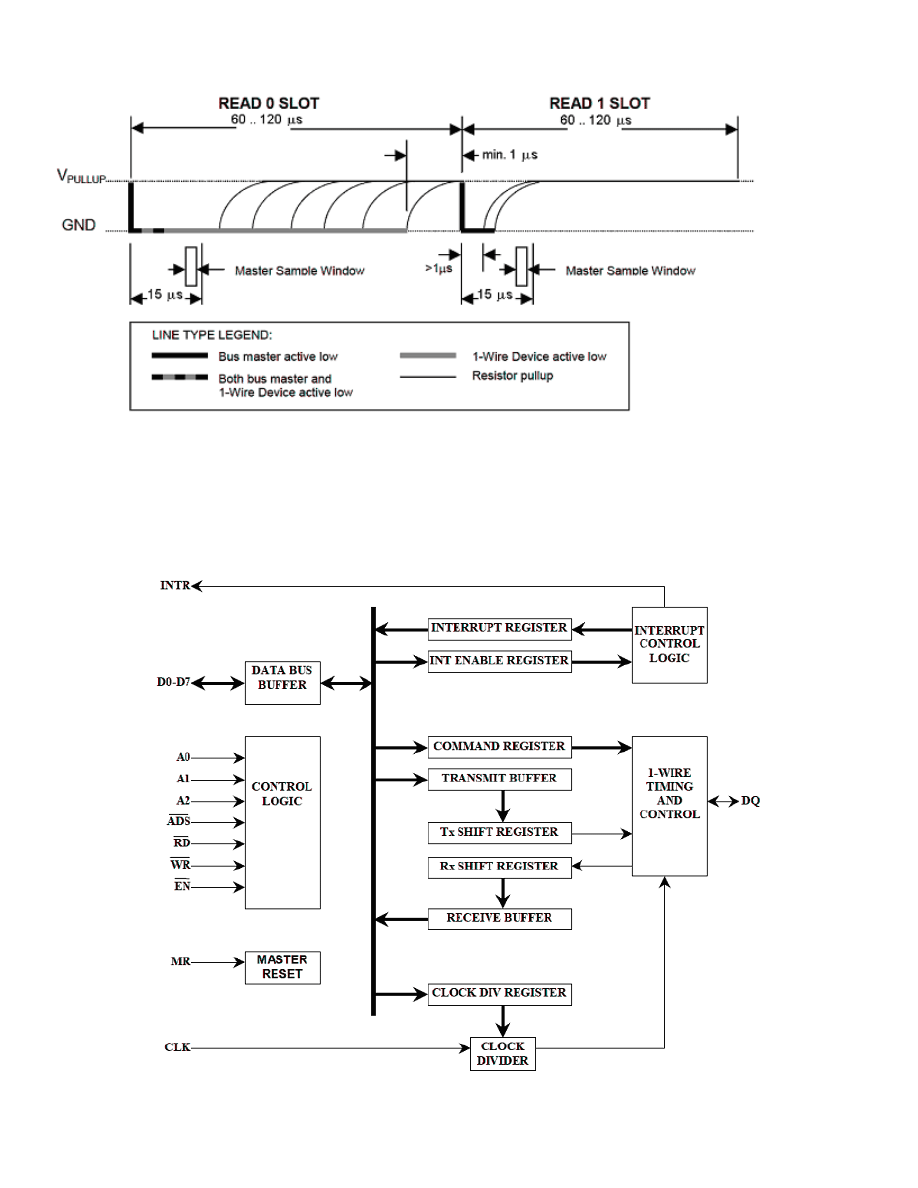

Odczyt wartości bitu przesyłanego przez układ podrzędny polega na generacji przez układ master impulsu o czasie

trwania minimum 1 ms (zazwyczaj stosuje się impulsy 3 .. 5 ms), a następnie na zwolnieniu linii DQ i sprawdzeniu jej

stanu logicznego przed upływem 15 ms od rozpoczęcia sekwencji odczytu (rys. 4). Jeżeli urządzenie podrzędne będzie

transmitowad logiczne „0”, wówczas generowany przez mikrosterownik impuls zostanie przedłużony do czasu trwania co

najmniej 15 ms. Odczyt stanu napięcia na magistrali przed upływem tego czasu da w efekcie poziom niski, czyli

transmitowane „0”. Ponieważ przedłużenie impulsu może trwad dłużej, to po odczytaniu stanu bitu należy odczekad

jeszcze nie krócej niż 45 ms. Jeżeli transmitowany będzie bit „1”, to wówczas urządzenie podrzędne nie przedłuży

impulsu generowanego przez mikrosterownik i odczyt stanu w tym samym czasie co przy transmisji „0” da w efekcie stan

wysoki, czyli transmitowaną logiczną „1”.

Odczyt bitu przez układ master na magistrali 1-Wire

W większości przypadków interfejs 1-Wire implementuje się w mikrosterownikach w sposób programowy. Jednak, ze

względu na rosnącą popularnośd interfejsu wynikającą z faktu, iż składa się on tylko z jednej linii sygnałowej, która może

zasilad urządzenia podrzędne ( o niewielkiej mocy pobieranej ) pojawiają się mikrosterowniki z kontrolerami tego

interfejsu (np. DS80C400). Na rys. 5 pokazano schemat blokowy kontrolera interfejsu 1-Wire.

Schemat blokowy kontrolera interfejsu 1-Wire:

Linia DQ jest wejściem/wyjściem interfejsu 1-Wire. Pozostałe linie przenoszą sygnały wewnętrzne. Magistrala D0-D7

dostarcza dane do poszczególnych rejestrów kontrolera, wybieranych za pomocą sygnałów A0-A2, które są

zatrzaskiwane w układzie kontrolnym przez sygnał /ADS. Aktywny stan na linii /RD powoduje odczyt z wybranego

rejestru, a aktywny sygnał /WR zapis do tego rejestru. Stan niski na linii /EN uaktywnia kontroler. Stan wysoki na linii MR

resetuje kontroler zerując zawartości wszystkich rejestrów i flagi przerwao. Sygnał CLK dzielony przez dzielnik sterowany

rejestrem Clock Div Register taktuje transmisją interfejsu 1-Wire. Na linii INTR pojawia się sygnał przerwania od

kontrolera. Odczytując rejestr Interrupt Register identyfikowana jest przyczyna przerwania. Interfejs steruje się za

pomocą rejestru Command Register. Wysyłanie danej rozpoczyna się po wpisaniu jej do rejestru Transmit Buffer.

Odebraną daną czyta się z rejestru Receive Buffer.

Cechy interfejsu :

Pracuje tylko z 1 linią danych

Urządzenie również musi mied mase

Jest to interfejs szeregowy

Komunikacja half-duplex, dwukierunkowa

Możemy podłączad wiele urządzeo w 2-wire ( w więkoszści interfejsów my nadajemy adres urządzeniom 1-wire-

> jest wyjątkowy ponieważ adres jest nadawany przez producenta, czyli jest unikatowy, wielobiotowy)

Zasilanie po tej samej linii co linia danych ( zasilanie pasożytnicze)

Wiele slave, jedno urządzenie master

Adres jest 64 bitowy, pierwsze 8 bitów to suma kontrolna służaca do sprawdzania poprawności, ostatnie 8 bitów to kod

rodziny, który mówi czy to termomentr czy przetwronik analogowy cyfrowy czy innego rodzaju urządzenie, 48 bitów

unikalne nadawane przez producenta

Gdy układ scalony kosztuje około 5zł, to z metalową obudową koszt wynosi już 80zł

- 1 oraz zero to trochę wysokiego i niskiego sygnału, o tym czy jest to 0 czy 1 decyduje stosunek czasów dolnych

sygnałów

STANDARD :

1-15 us stan niski

Potem 45 us wysoki

Kolejnośd nadawnia przez urządzenia (master -> slave)

1. Resetujemy

2. Wybieramy

3. Komunikujemy

Czyli :

1. Master wykonje reset (niski sygnał)

2. Wykrywanie urządzeo (master czeka na odpowiedź na nadany reset) – sygnał presence

3. Transmisja (komendy)

Komendy :

33H – identyfikacja urządzenia, idealna do szafek na siłowni. W przypadku wielu urządzeo odczytywany adres,

którego nie ma, iloczyn na drucie;

CCH – połaczenie z pastylką która rozponzaje CCH; rozmawiamy z pierwszym lepszym (przeważnie najmłodszym

adresem)

55H – rozmawia z konkretną jedną pastylką

FOH – służy szukaniu wszelkich magistrali, wszelkich dostępnych urządzeo

IEEE 1284 CENTRONICS [LPT]

(opis w artykułach)

notatki:

W komputerze jest to wtyk żeoski, posiada 36 pinów.

Interfejs równoległy, kilka bitów (dokładnie 8 ponieważ koduje on jeden znak) – standard wszystkich drukarek przez

wiele lat.

W standardzie IEEE 1284 zdefiniowano następujące protokoły transmisji danych:

SPP (ang. Standard Parallel Port, znany też pod nazwą Compatibility Mode) – tryb kompatybilności ze złączem

Centronics z możliwością transmisji dwukierunkowej. Port zapewnia najniższy transfer (150 kb/s). Wadą jest

obsługa poprzez przerwania, co jest utrudnione w systemach wielozadaniowych.

Nibble Mode – tryb półbajtowy (czterobitowy), przy transmisji z urządzenia zewnętrznego po liniach statusu.

Prędkośd transmisji nie przekracza 50 kb/s. Odpowiednik portu Bi-tronics wprowadzonego przez Hewlett-

Packard. Jest to komunikacja dwukierunkowa używająca 4 linii do urządzenia i 4 linii z urządzenia ( ważne przy

niezrównoważonej transmisji)

Byte Mode – tryb bajtowy (ośmiobitowy). 8 bitów raz w jednym raz w drugim kierunku według potrzeb, obsługa

buforów i przerwao do 2 MB/s – duża szybkośd

EPP (ang. Enhanced Parallel Port) – najczęściej stosowany tryb. Brak tutaj kanału DMA. Handshake realizowany

jest sprzętowo, co umożliwia działanie w systemie wielozadaniowym (po wywłaszczeniu procesu transmisja

nadal trwa) oraz znacznie ułatwia pracę programistów. Komunikacja jednokierunkowa , a co za tym idzie większa

wydajnośd niż SPP, obsługuje dużo starych nieznanych urządzeo

ECP (ang. Extended Capability Port) – port używa DMA i oferuje najwyższe prędkości (do 2 Mb/s).

Wykorzystywane są bufory FIFO.

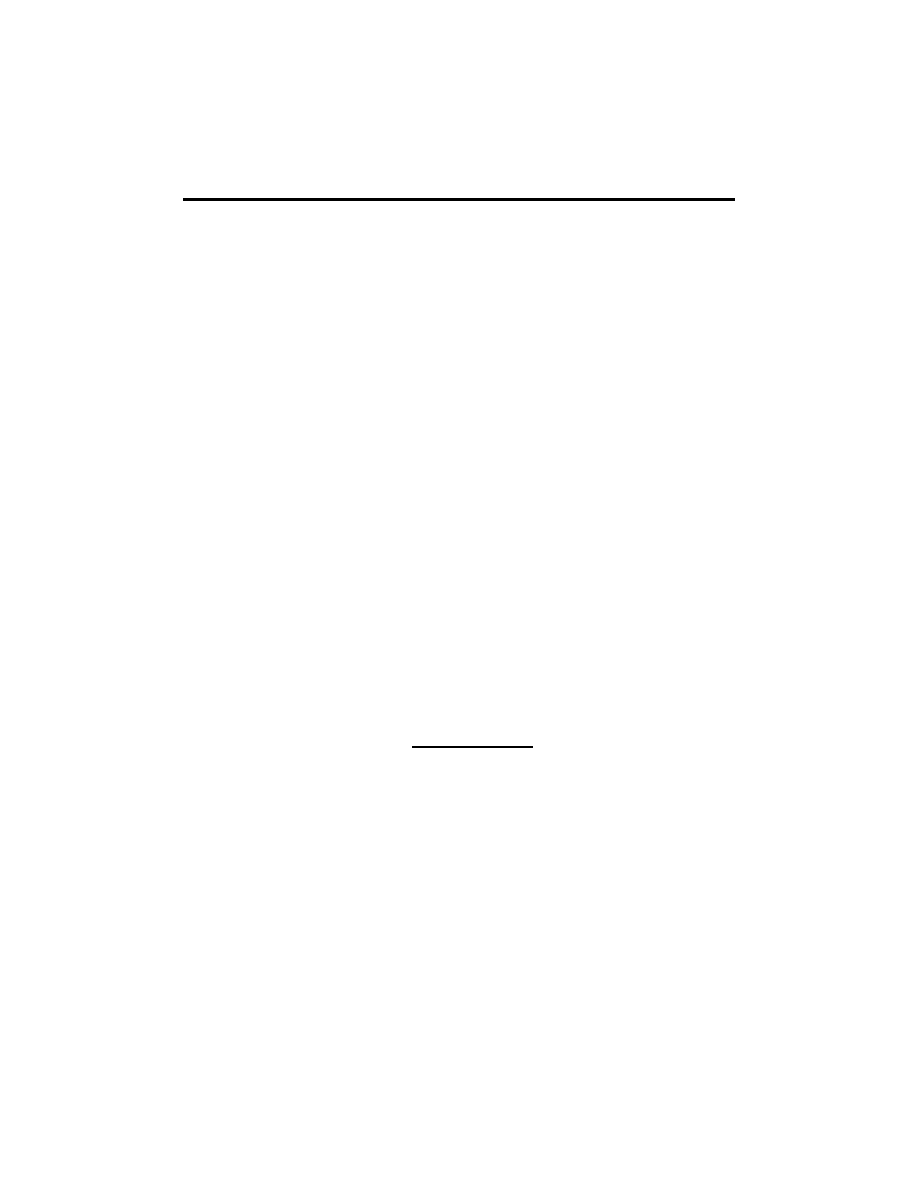

Ważne sygnały :

Hendszejki opisane w cz 2 artykulow

Są ważne 3 rejestry w trybie SPP

•Zdefiniowane są 3 adresy do dostępu rejestrów “LPT1:” odpowiada adresowi bazowemu 0x378

Bazowy używany do wysyłania danych(D0-D7)

Bazowy+1 rejestr statusu

Bazowy+2 rejestr controlny

Interfejs był ten popularny dla skanerów, też często do CD-ROMu zewnętrznego lub dysku zewnętrznego.

Był często używany do progrmowania innych rzeczy – jedyne realne okno na świat przez wiele lat

MODBUS

Interfejs MODBUS został opracowany w firmie Modicon i stał się w krótce standardem przyjętym przez większośd

znanych producentów sterowników przemysłowych dla asynchronicznej, znakowej wymiany informacji pomiędzy

urządzeniami systemów pomiarowo kontrolnych. O jego popularności i rozpowszechnieniu zdecydowały takie cechy jak :

Prosta reguła dostępu do łącza oparta na zasadzie master-slave

Zabezpieczanie przysłanych komunikatów przed błędami

Potwierdzanie wykonania rozkazów zdalnych i sygnalizacji błędów

Skuteczne mechanizmy zabezpieczające przed zawieszeniem systemu

Wykorzystanie asynchronicznej transmisji znakowej zgodnej z RS-232C

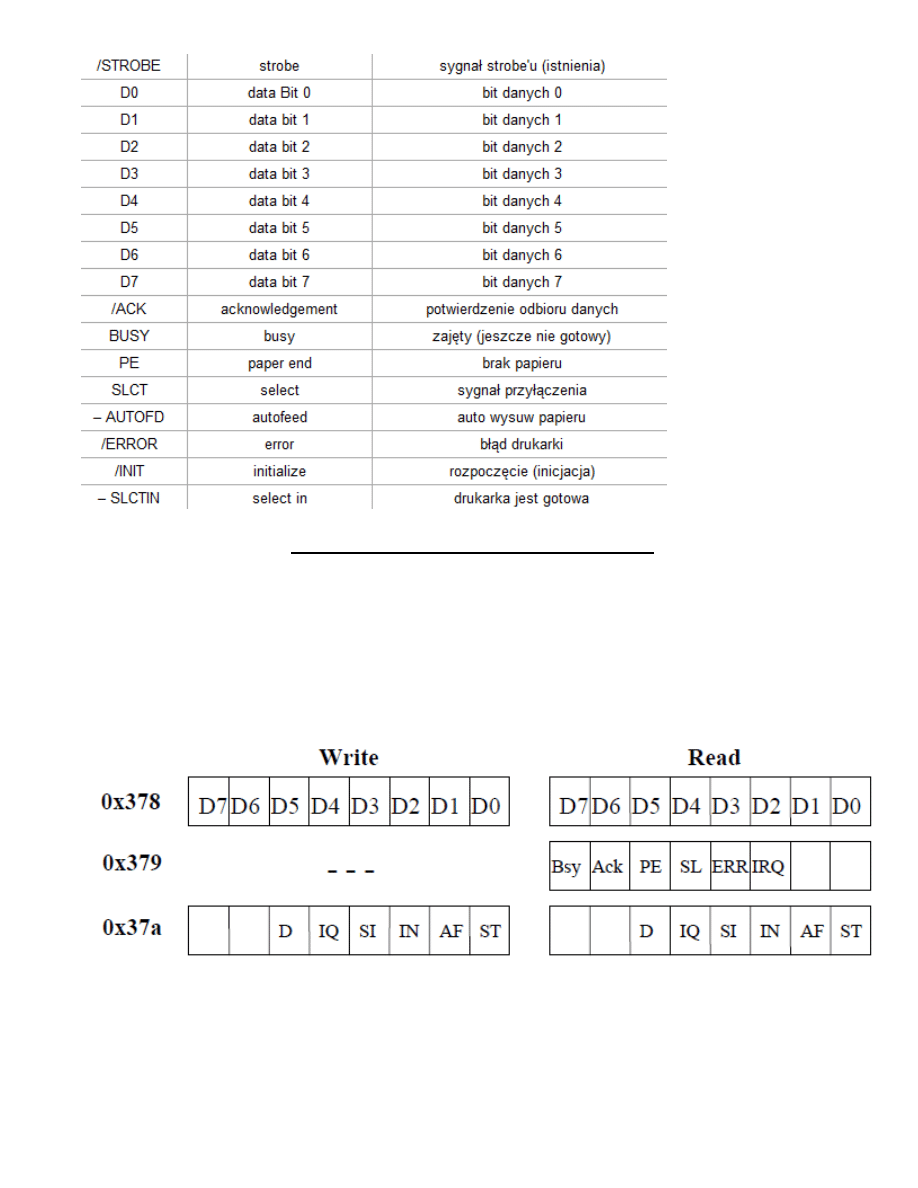

Transakcje w systemie MODBUS

Kontrolery urządzeo pracujących w systemie MODBUS komunikują sięze sobąprzy wykorzystaniu protokołu typu master-

slave, w którym tylko jedno urządzenie może inicjowad transakcje (jednostka nadrzędna – master), a pozostałe (

jednostki podrzędne – slave) odpowiadają jedynie na zapytania mastera. Transakcja składa się z polecnia (query)

wysyłanego z jednostki master do slave oraz z odpowiedzi (response) przesyłanej z jednostki slave do master.

Odpowiedź pomiędzy urządzeniem master i urządzeniem slave.

Master może adresowad indywidualnych odbiorców (jednostki slave) lub też przesyład wiadomości rozgłoszeniowe

(broadcast), przeznaczone dla wszystkich urządzeo podrzędnych w systemie. Na polecenia rozgłoszeniowe jednostki

slave nie przesyłają odpowiedzi. Protokół MODBUS określa format wiadomości przesyłanych z jednostki master do slave.

Zawiera on adres odbiorcy, kod funkcji reprezentujący żądane polenie, dane oraz słowo kontrolne zabezpieczające

przesyłaną wiadomośd. Odpowiedź urządzenia slave wysyłana jest również zgodnie z formatem zdefiniowanym w

protokole MODBUS. Zawiera ona pole potwierdzenia realizacji rozkazu, dane żądane przez master oraz słowo kontrolne

zabezpieczające odpowiedź przed błędami. Jeżeli urządzenie slave wykryje błąd przy odbiorze wiadomości, lub nie jest w

stanie wykonad polecenia , przygotowuje specjalny komunikat o wystąpieniu błędu i przesyła go jako odpowiedź do

mastera.

Ramka w systemie modbus

W systemie modbus wiadomości są zorganizowane w ramki o określonym początku i koocu. Pozwala to urządzeniu

odbierającemu na odrzucenie ramek niekompletnych i sygnalizacje związanych z tym błędów. Ze względu na możliwośd

pracy w jednym z dwóch trybów transmisji (ASCII lub RTU), definijue się 2 ramki

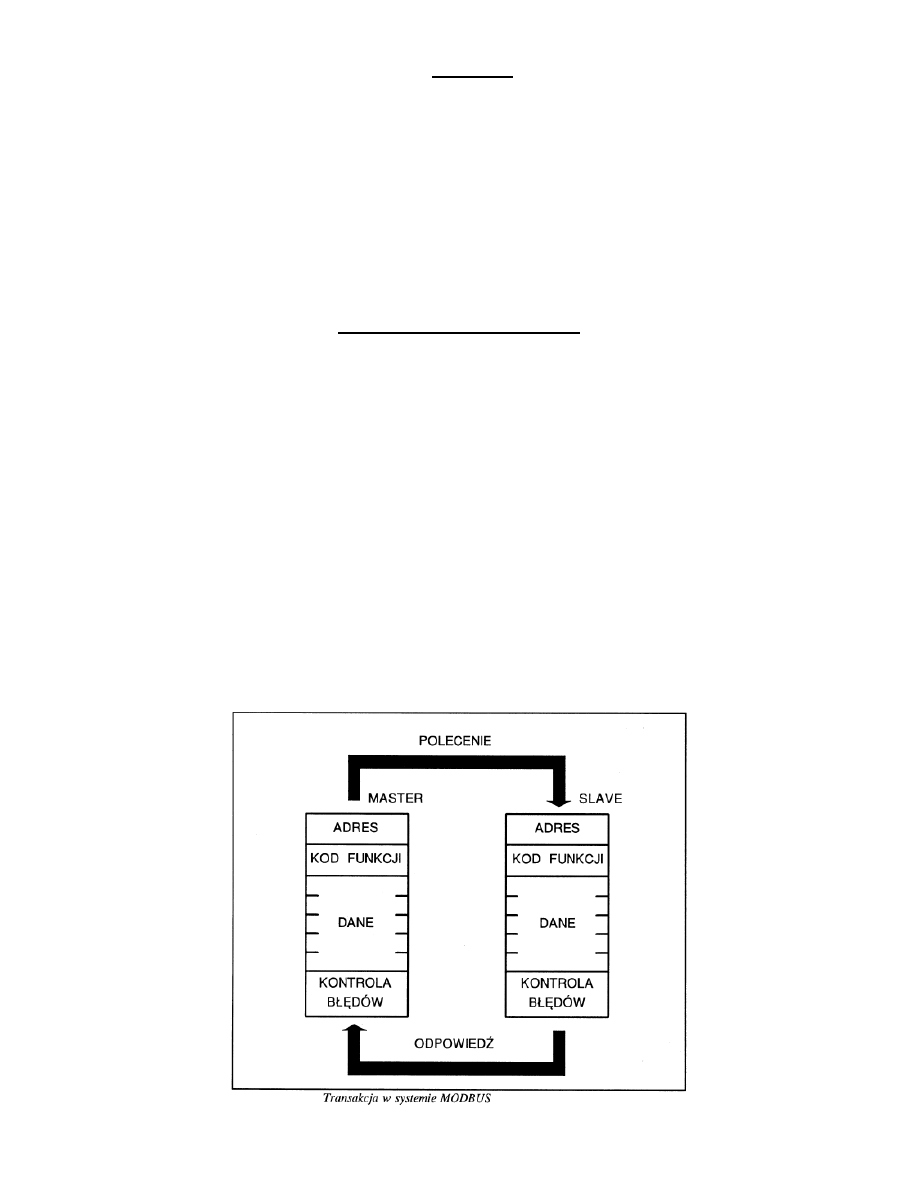

Ramka w trybie ASCII

W trybie ASCII, każdy bajt w wiadomości przesyłany jest w postaci dwóch znaków ASCII. Podstawową zaletą tego trybu

transmisji jest to, że pozwala on na długie odstępy między znakami (do 1s) bez powodowania błedów. Format znaku

przesyłanego w transmisji ASCII jest następujący:

System kodowania : heksadecymalny, znaki ASCII 0-9 A-F. Jeden znak heksadecymalny zawarty jest w każdym

znaku ASCII wiadomości.

Jednostka informacyjna: ograniczona znakami start (na początku) i stop na koocu, 10 bitową

Przy transmisji w trybie ASCII stosuje się zabezpieczenie części informacyjnej ramki kodem LRC (Longitudinal

Redudndancy Check)

Format ramki w trybie ASCII przedstawiono na rysunku. Znacznikiem początku ramki jest znak dwukropka ( „:” – ASCII

3Ah). Dopuszczalnymi znakami dla pozostałych pól (za wyjątkiem znacznika kooca ramki) są 0-9, Ah-Fh. Urządzenie po

wykryciu znacznika początku ramki sprawdza, czy pole adresowanie zawiera jego adres własny. Jeżeli tak, to odczytuje

zawartośd pola funkcji i związaną z nią zawartośd pola danych. Częśd informacyjną ramki (bez znaku „:”) zabezpiecza pole

kontrolne LRC. Ramka kooczy się przesłaniem dwóch znaków : CR i LF.

Odstęp pomiędzy znakami tworzącymi ramkę nie może przekraczad 1s. jeżeli odstęp ten będzie większy od podanej

wartości, rządzenie odbierające dane sygnalizuje błąd

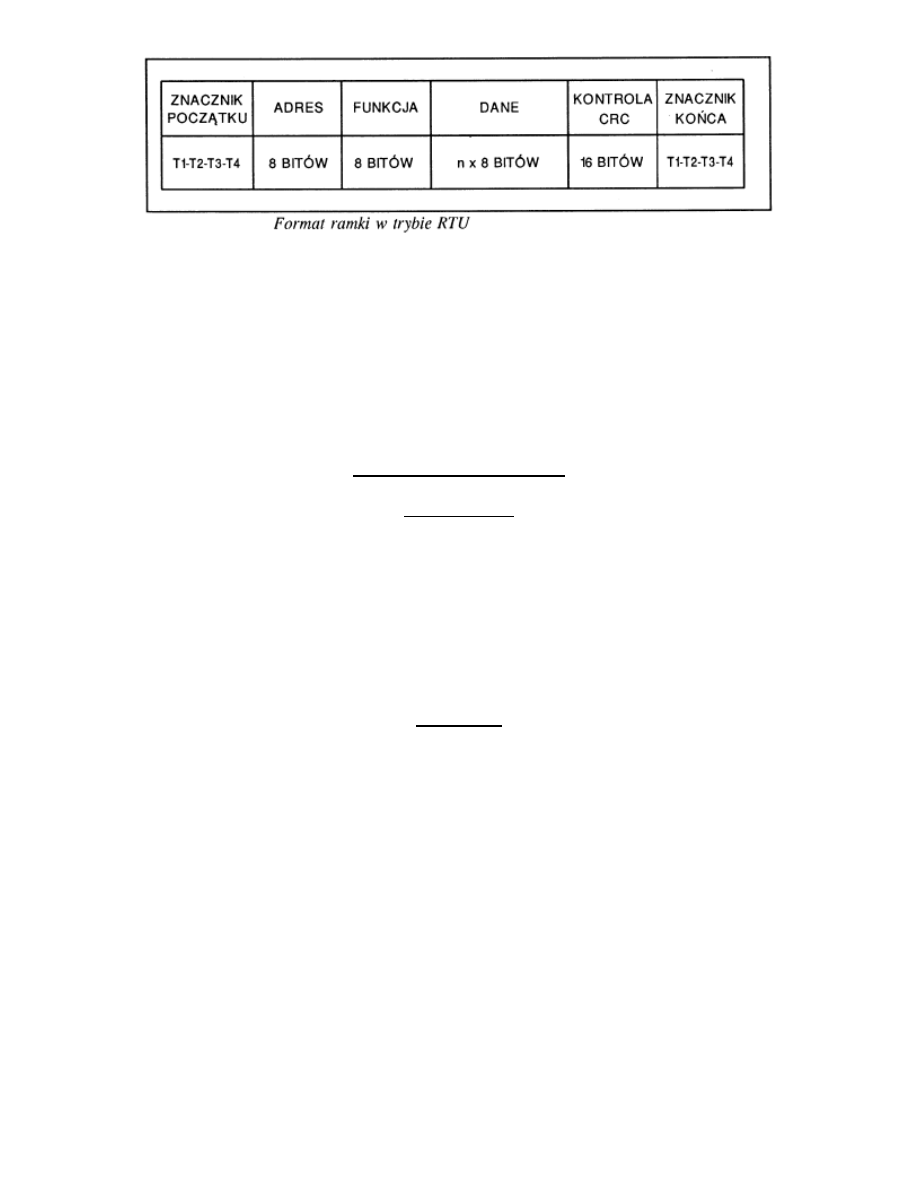

Ramka w trybie RTU

W trybie RTU wiadomości rozpoczynają się odstępem czasowym trwającym minimum 3.5 x (czas trwania pojedynczego

znaku), w którym panuje cisza na łączu. Najprostszą implementacją wymienionego interwału czasowego jest wielokrotne

odmierzanie czasu trwania znaku przy zadanej szybkości bodowej przyjętej w łączu. Na rysunku przedstawiającym ramkę

w trybie RTU, odstęp początkowy zaznaczono symbolicznie jako T1-t2-t3-t4, czyli równy czterem długościom znaku

(jednostki informacyjnej). Pierwszym polem informacyjnym ramki jest adres zarządzania.

Dopuszczalnymi znakami transmitowanymi w ramkach pól ramki są 0-9, A-F. Połączone w system urządzenia stale

(łącznie z przedziałami ciszy) monitorują magistralę. Po odebraniu zawartości pola adresu urządzenia sprawdzają czy

przesłany adres jest ich adresem własnym. Jeżeli tak to kontynuują interpretację pozostałych pól wchodzących w skład

ramki.

Ramkę kooczy przerwa czasowa trwająca co najmniej 3.5 x ( długości znaku). Po tym odstępie można wysład następną

ramkę, traktując go jako jej przerwę początkową. Całą ramka musi zostad przesłana w postaci ciągłej tzn. odstęp

pomiędzy kolejnymi znakami tworzącymi ramkę nie może byd większy od 1.5 x (długości znaku). Jeżeli odstęp ten

przekroczy podaną wartośd, to urządzenie odbierające uzna ramkę za niekompletną i następny znak przyjmie za bajt pola

adresowego kolejnej wiadomości. Podobnie, jeżeli nowa wiadomośd pojawi się na magistrali przed upływem koniecznej

przerwy (3.5 x długośd znaku)), to urządzenie odbierające potraktuję ją jako kontynuację poprzedniej wiadomości. To

doprowadzi do błędu sumy kontrolnej, ponieważ urządzenie odbierające będzie obliczad CRC dwóch wiadomości i

porównywad go z CRC drugiej.

Charakterystyka pól ramki

Pole adresowe

Pole adresowe w ramce zawiera dwa znaki ( w trybie ASCII) lub osiem bitów (w trybie RTU). Zakres adresów jednostek

slave wynosi 0-247. Master adresuje jednostkę slave umieszczając jej adres na polu adresowym ramki. Kiedy jednostka

slave wysyła odpowiedź, umieszcza swój własne adres na polu adresowym ramki, co pozwala masterowi sprawdzid z

która jednostką realizowana jest transakcja.

Adres 0 jest wykorzystywany jako adres rozgłoszeniowy, rozpoznawany przez wszystkie jednostki slave podłączone do

magistrali.

Pole funkcji

Pole funkcji w ramce zawiera dwa znaki w trybie ASCII lub osiem bitów w trybie RTU. Zakres kodów operacji 1-255.

Przy transmisji polecenia z jednostki master do slave, pole funkcji zawiera kod rozkazu, określający działanie, które ma

podjąd jednostka slave na żądanie mastera. Przykładowymi rozkazami mogą byd : rozkaz odczytu zespołu rejestrów,

odczyt status, zapis rejestrów w jednostce slave, ładowanie, odczytywanie lub weryfikacja programu jednostki slave.

Kiedy jednostka slave odpowiada masterowi, pole funkcji wykorzystuje do potwierdzenia wykonania polecenia lub

sygnalizacji błędu, jeżeli z jakiś przyczyn nie może wykonad rozkazu. Potwierdzenie pozytywne realizowane jest poprzez

umieszczenie na polu funkcji kodu wykonanego rozkazu. W przypadku stwierdzenia błędu, jednostka slave umieszcza na

polu funkcji „szczególną odpowiedź” (exception response), która stanowi kod funkcji z ustawionym na 1 najstaarszym

bitem. Na przykład polecenie (z mastera do jednostki slave) odczytu zespołu rejestrów posiada kod funkcji 0000 0011(

03h)

Jeżeli jednostka slave wykona rozkaz, w swojej odpowiedzi zwraca tą samą wartośd na polu funkcji. Jeżeli wykryje błąd,

zwróci 1000 0011 (83h).

Oprócz „szczególnej odpowiedzi” sygnalizującej błąd, jednostka slave umieszcza kod błędu na polu danych ramki

odpowiedzi. Pozwala to masterowi określid rodzaj lub powód błędu.

Program wykonywanny przez jednostkę master jest odpowiedzialny za obsługę błędów. Typową reakcjąna wystąpienie

błędu jest powtórzenie ramki polecenia, odczyt informacji statusowych umożliwiających diagnostykę błędów,

powiadomienie operatora.

Pole danych

Pole danych tworzy zestaw dwucyfrowych liczb heksadecymalnych o zakresie 00 – FF. Liczby te przy transmisji w trybie

ASCII reprezentowan są dwoma znakami, a przy transmisji w trybie RTU jednym.

Pole danych ramki poelcenia zawiera dodatkowe informacje potrzebne jednostce slave do wykonania rozkazu

określonego kodem funkcji. Mogą to byd adresy rejestrów, liczba bajtów w polu danych, dane itp. Na przykład, jeżeli

master żąda odczytu grupy rejestrów (kod funkcji 03), pole danych zawiera nazwę (adres) rejestru początkowego oraz

ilośd rejestrów do odczytu. Przy operacji zapisu grupy rejestrów (kod funkcji 10h), na polu danych znajdują się

następujące informacje: adres rejestru początkowego, ilośd rejestrów, ilośd pozostałych bajtów w polu danych, dane

przeznaczone do zapisu. Jeżeli nie wystąpi błąd, pole danych odpowiedzi zawiera żądane informacje. Wykrycie błędu

powoduje zapisanie przez jednostkę slave kodu błędu na polu danych ramki odpowiedzi, co umożliwia adekwatną

reakcję mastera.

W niektórych ramkach polecenia pole danych może posiadad zerową długośd. Tak jest zawsze w sytuacji, gdy operacja

określona kodem funkcji nie wymaga żadnych parametrów.

Pole kontrolne

W standardzie MODBUS słowo kontrolne zabezpieczające częśd informacyjną zależy od zastosowanego trybu transmisji.

W trybie ASCII pole kontrolne składa się z dwóch znaków ASCII, które są rezultatem obliczenia LRC na zawartośd części

informacyjnej ramki ( bez znaczników początku i kooca). Znaki LRC są dołączane do wiadomości jako ostatnie pole ramki,

bezpośrednio przed znacznikiem kooca (CR,LF).

W trybie RTU słowo kontrolne jest 16-bitowe i powstaje jako rezultat obliczenia CRC na zawartości ramki. Pole kontrolne

zajmuje dwa bajty dołączane na koocu ramki. Jako pierwszy przesyłany jest mniej znaczący bajt, jako ostatni starszy bajt,

który jest jednocześnie znakiem kooczącym ramkę.

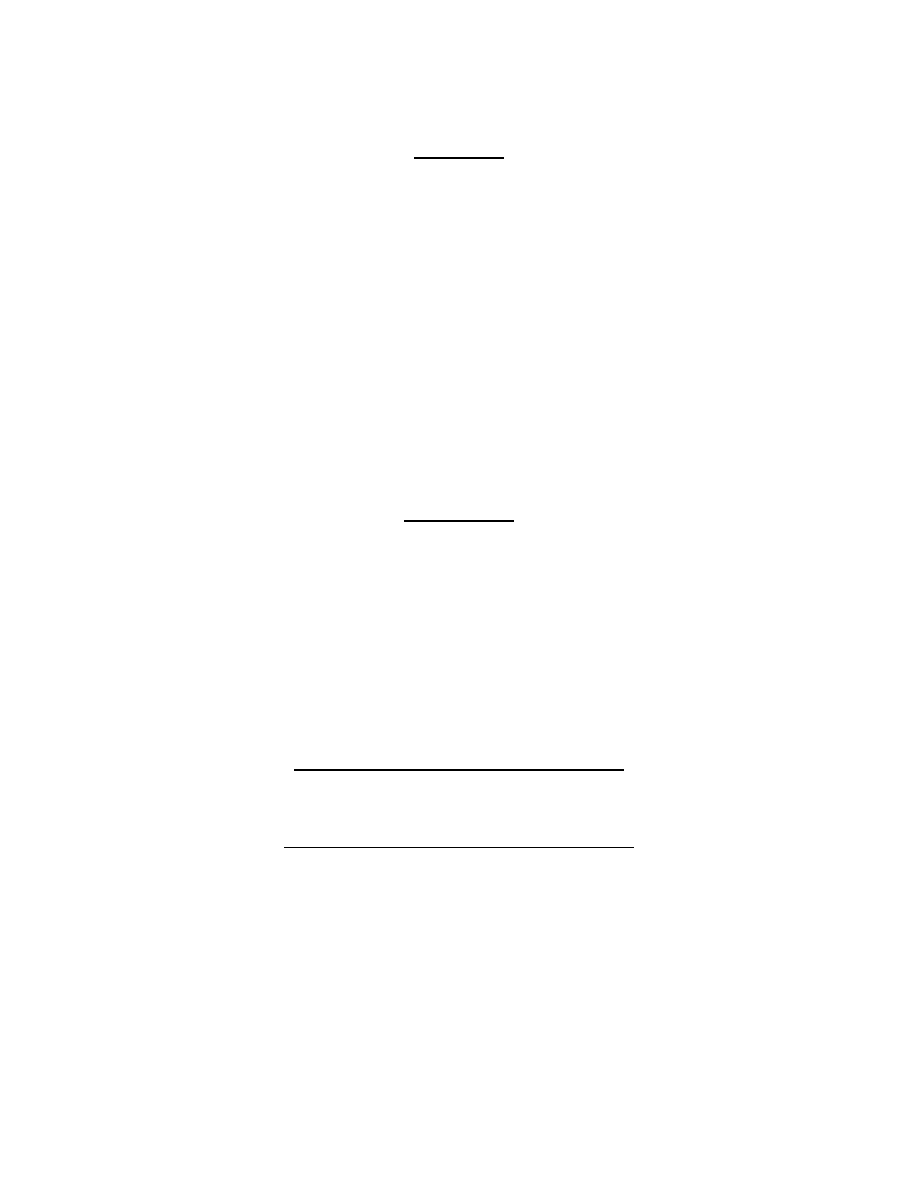

Format znaku przy transmisji szeregowej

W standardzie MODBUS znaki są przesyłane szeregowo od najmłodszego do najstarszego bitu.

Organizacja jednostki informacyjnej w trybie ASCII:

1 bit startu

7 bitów pola danych, jako pierwsze wysyłany jest najmniej znaczący bit

1 bit kontorli parzystości (nieparzystości) lub brak bitu kontroli parzystości

1 bit stopu przy kontroli parzystości lub 2 bity stopu przy braku kontroli parzystości

Zasada wypracowania bitu kontroli parzystości w jednostce informacyjnej jest następująca :

Kontrola parzystości (even parity) – bit posiada wartośd 1 , jeżeli ilośd jedynek na polu danych jest nieparzysta

oraz 0 ,jeżeli jest parzysta

Kontrola nieparzystości (odd parity) – bit posiada wartośd 1 , jeżeli ilośd jedynek na polu danych jest parzysta

oraz 0 , jeżeli ilośd jedynek jest nieparzysta

Organizacja jednostki informacyjnej w trybie RTU:

1 bit startu

8 bitów pola danch, jako pierwszy wysyłany jest najmniej znaczący bit

1 bit kontroli parzystości (nieparzystości) lub brak bitu kontroli parzystości

1 bit stopu przy kontroli parzystości, lub 2 bity stopu przy braku kontroli parzystości

Pole danych znaku może byd (opcjonalnie) zabezpieczone bitem konroli parzystości lub nieparzystości. Wspomnanie

wcześniej zabezpieczenie LRC lub CRC dotyczy całej treści ramki. Oba zabezpieczenia, tzn. zabezpieczenie znaku roaz

całej ramki, generowane są przez urządzenie nadające i dołączane do wiadomości przed transmisją. Urządzenie

odbierające sprawdza bit parzystości znaku (o ile występuje) oraz słowo kontrolne.

Funkcje w MODBUS:

Na początku ramki odpowiedzi urządzenie slave umieszcza swój adres, po którym następuje kod wykonywanej funkcji

oraz dane stanowiące zawartośd odczytywanych rejestrów

Podstawowymi funkcjami w interfejsie MODBUS są:

Odczyta stanu wybranego wejścia dwustanowego

Odczyt stanu wybranego wyjścia dwustanowego

Odczyt zawartości grupy rejestrów

Ustawienie (ON/OFF) wybranego wyjścia dwustanowego

Ustawienie (ON/OFF) grupy wyjści dwustanowych

Zapis wartości początkowej do rejestru

Zapis wartości początkowej do grupy rejestró1.

Odczyt rejestru status urządzenia slabe

Odczyt licznika komunikatów

Wyszukiwarka

Podobne podstrony:

Opracowanie Sciaga MC OMEN

Opracowanie pytań MC OMEN 2

Opracowanie wykladow MC OMEN

Opracowanie wykładów biofyzka 1 MC OMEN

Opracowanie pytań MC KULA MC OMEN 2

Opracowanie pytań RÓŻNE MC OMEN

Opracowanie wykładów biofyzka 2 MC OMEN

Opracowanie pytań MC OMEN 3

Opracowanie projektu MC OMEN

Opracowanie pytań MC OMEN

Opracowanie wykładów biofyzka 3 MC OMEN

Opracowanie pytań MC OMEN

Opracowanie do kolokwium part 2 MC OMEN

Opracowanie Sciaga MC OMEN

Opracowanie pytań MC OMEN 2

Opracowanie wykladow MC OMEN

więcej podobnych podstron