1

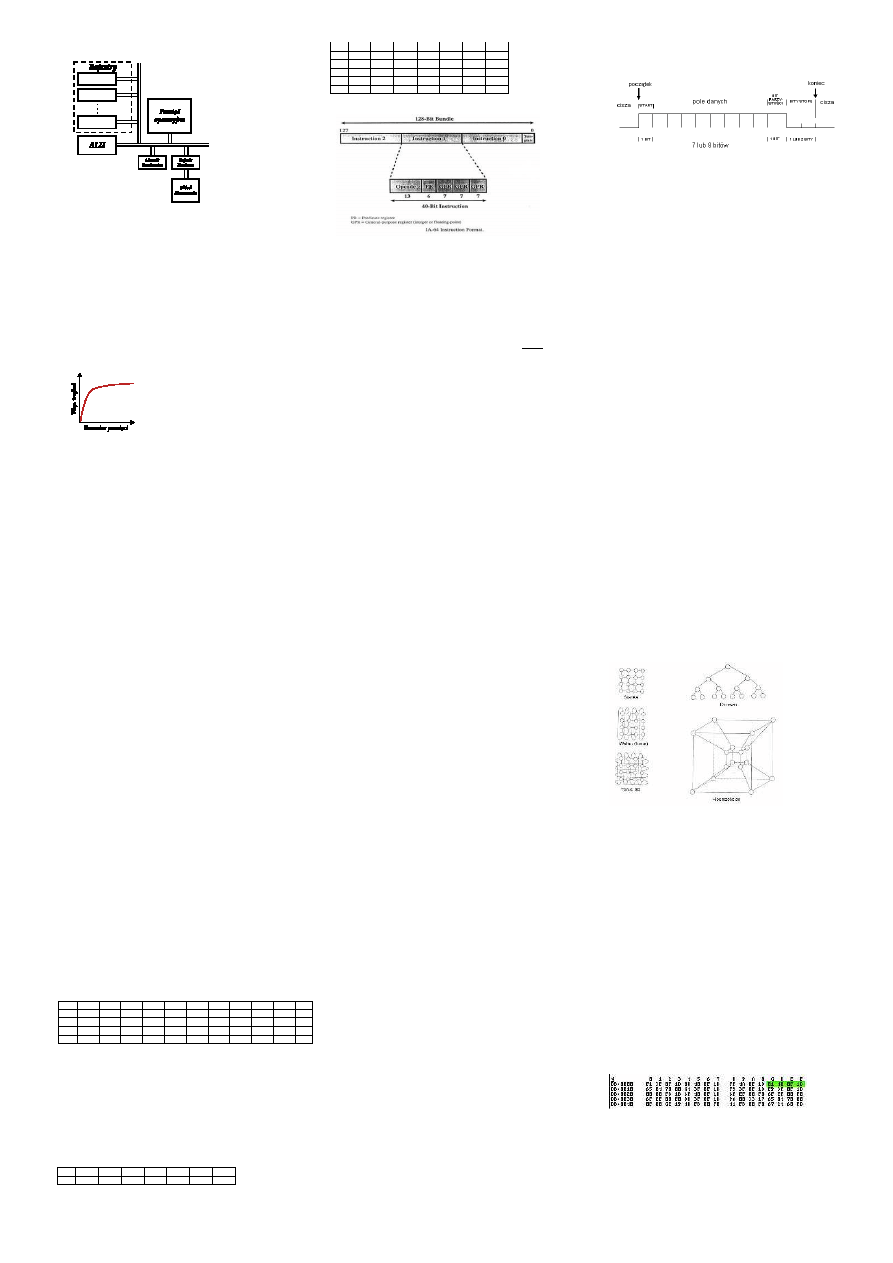

Przedstaw na rysunku ogólną budowę procesora.

Wymień i scharakteryzuj 2 podstawowe techniki zapewnienia

zgodności pamięci podręcznej z pamięcią główną.

WriteThrough – każda zmiana zawartości bloku cache'u zostaje

natychmiast zapisana w pamięci operacyjnej. Metoda ta jest

bezpieczniejsza (nie ma ryzyka wystąpienia rozbieżności pomiędzy

zawartością pamięci buforowej i operacyjnej), ale i nieco

wolniejsza.

WriteBack – W trybie tym dane przepisywane są z bufora z

opóźnieniem: trafiają tam dopiero wtedy, gdy "muszą", czyli gdy

bufor jest przepełniony lub gdy procesor lub inne urządzenie

próbuje bezpośrednio odwołać się do pamięci operacyjnej.

Przedstaw na rysunku jak zmienia się współczynnik trafień w

zależności od rozmiaru pamięci podręcznej.

Przedstaw metody ochrony pamięci operacyjnej.

Rejestry graniczne – jedna z dwóch metod ochrony pamięci op. –

zawierają rozmiar pamięci przydzielonej procesowi lub

maksymalny adres komórki dozwolony w procesie.

Metoda zamka i klucza – każdy proces uzyskuje unikalny podpis –

klucz, pasujący do przydzielonego mu obszaru pamięci

zawierającego zamek.

Ile rejestrów uniwersalnych zawierają typowo procesory: CISC,

RISC i EPIC?

CISC – 8+8

RISC - 32+32

EPIC – 128+128

Jaka jest długość rejestrów uniwersalnych w procesorach: 8086,

Pentium 4, Alpha 21264, Itanium?

8086 – 16 bit

Pentium 4 – 32 bit

AMD Athlon 64 – 64 bit

Itanium – 64 bit

Jaka jest długość licznika rozkazów w procesorach: 8086,

Pentium 4, Itanium?

8086 – 16 bit

Pentium 4 – 32 bit

Itanium – 64 bit

Jaka jest wielkość pamięci fizycznej adresowanej przez

procesory: 8086, 486, Pentium 4?

8086 – 64KB

486 – 4GB

Pentium 4 – 64GB

W jakich procesorach układ sterowania jest a w jakich nie jest

mikroprogramowany?

CISC – jest

RISC – nie jest (realizacja układowa)

Jaka jest zasadnicza różnica w budowie rozkazu między

procesorami CISC i RISC?

CISC – zmienna długość rozkazu

RISC – stała długość rozkazu

Jaki jest zakres liczb całkowitych ze znakiem zapisanych w

uzupełnieniu dwójkowym, jeżeli na każdą liczbę przypada n

bitów?

Od -(2

n-1

) do +(2

n-1

)

Jak wygląda:

największa 32-bitowa liczba dodatnia? Zapisz ją w Hex

najmniejsza 32-bitowa liczba ujemna? Zapisz ją w Hex

Największa liczba dodatnia: 7FFFFFFF

Najmniejsza liczba ujemna: 80000000

Przedstaw w postaci dwójkowej liczbę dziesiętną 0.25

0.01

(Każdy bit po przecinku odpowiada odpowiednio liczbom: ½, ¼, itd

[potęgi ujemne liczby 2], które się potem sumuje, by otrzymać

wynik)

Ile taktów potrzeba do wykonania programu złożonego z 8

rozkazów w procesorze potokowym. Wykonanie rozkazu

wymaga 5 taktów. Potok składa się z 5 faz.

12 taktów

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

Ile taktów zajmie wykonanie programu z poprzedniego zadania

w procesorze superskalarnym z dwoma układami

wykonawczymi. Każdy układ jest potokowy jak w zadaniu

poprzednim.

8 taktów

R

O

Z

K

R

O

Z

K

3

R

O

Z

K

4

R

O

Z

K

5

R

O

Z

K

6

R

O

Z

K

7

R

O

Z

K

8

R

O

Z

K

1 2 3 4 5 6 7 8

Przedstaw budowę rozkazu w procesorze Itanium.

Jakie rejestry występują w procesorze Itanium?

Rejestry predykatowe (64 sztuki, o długości 1 bitu)

Rejestry stało- i zmienno-przecinkowe (po 128, o długości 64

bitów)

W pewnym komputerze 70% czasu wykonania programu

przypada na przetwarzanie w procesorze. Ile razy będzie

szybszy ten komputer po wymianie procesora na dwukrotnie

szybszy?

1 wersja:

(1-0,7)+0,7=1 0,3+0,7/2=0,3+0,35=0,65 1/0,65=1,538

2 wersja:

70% (tyle czasu przetwarza) + 30% (czas bezczynności) = 1

czyli: 0,7 + 0,3 = 1

po wymianie na 2krotnie szybszy:

0,7/2 + 0,3 =0,35 + 0,3 = 0,65

dzielimy to co było 1 przez to co mamy 0,65 -1 / 0,65 = 1,538

Scharakteryzuj procesory VLIW i podaj przykłady takich

procesorów.

Procesory z długim słowem rozkazowym. Rozkaz podzielony jest

na grupy, z których każde pole zawiera instrukcje dla określonego

układu wykonawczego, np. Crusoe (Transmeta).

Scharakteryzuj procesory EPIC i podaj przykłady takich

procesorów.

64 bitowy procesor, rozkazy o długości 40 bitów, paczkowane po 3

+ obszar Template. Razem 128 bitów. Potrafi wykonywać rozkazy

x86 w trybie emulacji. Np. Itanium I i II.

Przedstaw, jakie rozwiązania architektoniczne pojawiały się w

kolejnych procesorach rodziny x86.

8086 -

16 linii adresowych, do 1MB pamięci;

286 -

16 linii adresowych, do 1MB pamięci;

386 -

32 linie adresowe, 4GB pamięci

Pentium -

32 linie adresowe, 4GB pamięci, 16kB L1 Cache

486 -

32 linie adresowe, 4GB pamięci, 8kB L1 Cache

Pentium Pro - 36 linii adresowych, 64GB pamięci, 16kB L1

Cache,

256 lub 512 L2 Cache, rejestr MMX 64 bitowy

Pentium II - 36 linii adresowych, 64GB pamięci, 32kB L1

Cache,

256 lub 512 L2 Cache, rejestr MMX 64 bitowy

Pentium III - 36 linii adresowych, 64GB pamięci, 32kB L1

Cache,

512 L2 Cache, SSE 128 bitów, rejestr MMX 64

bitowy

Pentium IV - 36 linii adresowych, 64GB pamięci, SSE, SSE2

Czas dostępu do pamięci RAM wynosi 50 ns a do pamięci cache

6 ns. Jaki jest średni czas dostępu do pamięci, jeżeli

współczynnik trafień wynosi 85%?

(T

CAM

=6ns , α = 85% , T

n

= 50ns)

EAT= α (T

CAM

+ T

n

) + ( 1- α ) * ( T

CAM

+ T

n

+ T

n

)

1 wersja: EAT= 0,85(6+50) + (1-0,85) * (6+50+50) = 55,25 +

0,15 * 106 = 55,25 + 15,9 = 71,15

Przedstaw własności różnych odmian magistrali PCI.

Zegar (MHz) Szerokość (b) Pasmo (MB/s)

PCI-33

33

32

133

PCI-66

66

32

266

PCI-64

33

64

266

PCI

66

64

528

PCI-X

133

64

>1GB

Krótko scharakteryzuj złącze USB.

Złącze szeregowe typu HotPlug, max 127 urządzeń, można

stworzyć 6 poziomów urządzeń, można rozgałęziać przy użyciu

koncentratorów (HUB), w 1 wersji prędkość 1,5 lub 12 Mbit/s

(wersja 1.1); w 2 wersji prędkość 1,5 lub 12 lub 480 Mbit/s; Można

łączyć pod napięciem.

Krótko scharakteryzuj złącze FireWire.

Złącze szeregowe typu HotPlug, max 64 urządzenia, 100, 200, 400

Mbit/s; znany również jako IEEE-1394 bądź iLink

Krótko scharakteryzuj złącze LPT.

Złącze równoległe, 8 bitowe, podstawowe sygnały sterujące –

STR, BUSY, ACK; 25 linii. Używane głownie do podłączenia

drukarek i skanerów. 8 linii danych. Możliwość kilku trybów pracy

(bez potwierdzenia jak i z jedno lub dwu stronnym

potwierdzeniem). Obecnie występuje w odmianach: SPP, EPP,

ECP, różniących się głownie miedzy sobą prędkością przesyłania

(EPP i ECP są prawie 10 razy szybsze.). Prędkość przesyłu do 12

Mbit/s.

Objaśnij, na czym polega przesyłanie z dwustronnym

potwierdzeniem

Przesyłanie z podwójnym potwierdzeniem – związane jest z

zastosowaniem dodatkowego sygnału sterującego, który informuje

o gotowości odbiorcy do odbioru danych lub o dostarczeniu

żą

danych danych przez źródło. Wykorzystuje się tu sygnał ACK.

Krótko scharakteryzuj złącze COM.

Złącze szeregowe. 9 pin. Możliwość pracy w różnych prędkościach

do 115Kbit/s. Wykorzystywane głownie do podłączenia myszy lub

modemu.

Przedstaw budowę ramki przy transmisji asynchronicznej.

Krótko scharakteryzuj złącze SATA (Serial ATA).

Złącze szeregowe dysków twardych, 2 pary przewodów

ekranowanych, max przepustowość 150 MB/s (dla pierwszej

wersji) lub 300MB/s (dla drugiej wersji). Kodowanie 8 na 10 (2

bity do każdego znaku), połączenie punkt-punkt. Następca złącza

PATA,

Objaśnij, na czym polega MMX.

Ang. MultiMedia eXtension. Rozszerzenie rozkazów procesora do

obsługi multimediów, operacja na wielu danych jednocześnie.

Znaczne przyśpieszenia działania aplikacji multimedialnych. 57

nowych rozkazów.

Objaśnij, na czym polega SSE.

Rozszerzenie MMX o 50 nowych instrukcji głownie do obliczeń

zmiennoprzecinkowych. Wprowadzone w Pantium III.

Przetwarzanie wektorowe, 4 32-bitowe rejestry

zmiennoprzecinkowe i 8 128 bitowych rejestrów.

W jakich warunkach ustawiane są znaczniki OF, CF, ZF w

procesorach x86?

OF – znacznik nadmiaru (overflow flag): Bit tego znacznika jest

ustawiany, gdy następuje przekroczenie zakresu w arytmetycznej

operacji na liczbach ze znakiem;

CF – znacznik przeniesienia: Wartość 1 tego znacznika oznacza,

ż

e w wyniku operacji arytmetycznej na liczbach ze znakiem

powstało przeniesienie. Oznacza to także ”pożyczkę” przy

operacjach odejmowania, w których stosuje się arytmetykę z

uzupełnieniem do dwóch;

ZF – znacznik zero: Ustawienie tego znacznika na wartość 1

oznacza, że wynik operacji jest zerowy;

Jakie pamięci podręczne zastosowano w Pentium 4?

Pamięć pierwszego poziomu L1, trace Execution Cache TEC ,

drugiego poziomu L2.

Na czym polega Hyper Threading?

Polega na równoległym przetwarzaniu 2-óch instrukcji (wątków)

przez jeden procesor fizyczny - (wielowątkowość).

Jak brzmi inna nazwa (niezastrzeżona) Hyper Threading?

SMT – Simultaneous MultiThreading.

Objaśnij pojęcia S(p), E(p).

S(p) = T(1) - czas rozwiązania zadania na 1 procesorze S(p) ≤ p

T(p) - czas rozwiązania zadania na p procesorach

E(p) = S(p) - przyśpieszenie (dla konkretnej l. proc.) E(p) ≤

1

P - liczba procesorów

E – efektywność

S – przyśpieszenie

p – liczba procesorów

Przedstaw rodzaje systemów wieloprocesorowych.

SMP – Simetrical Multi Procesor

NUMA – Non Uniform Memory Access

Przedstaw ważniejsze topologie systemów komputerowych

Jakie nowe własności posiada Athlon-64 w stosunku do wersji

32-bitowej?

Może pracować w trybie 64 bit, może zaadresować 264 bajtów

pamięci. Rejestry uniwersalne 64-bitowe – 16 sztuk (dołożono 8).

Przedstaw budowę płyty głównej.

Płyta główna zawsze zbudowana jest na laminacie zwykle co

najmniej 4-warstwowym, po którym prowadzone są ścieżki

łączące poszczególne elementy urządzenia. Zawiera m.in

chipset(mostki: południowy, północny) –„serce płyty”, szyny

transmisyjne, podstawkę procesora, pamięć ROM[BIOS - zasilany

przez układ CMOS(bateria)], sloty pamięci RAM, gniazda

rozszerzeń.

Jakie funkcje pełni mostek północny?

Jest odpowiedzialny za komunikację pomiędzy procesorem,

grafiką i pamięcią oraz pomiędzy mostkiem.

Jakie funkcje pełni mostek południowy?

Mostek południowy pełni więcej funkcji od północnego.

Zapewnia poprawne działanie portów np. USB, FireWire, kart

PCI, napędów podłączonych do kontrolera IDE oraz urządzeń

peryferyjnych typu mysz, klawiatura.

Przedstaw prawo Moore’a.

Wydajność komputera rośnie dwukrotnie co 18 miesięcy (funkcja

ma charakter wykładniczy).

Korzystając z przedstawionego niżej obrazu pamięci podaj

adres programu obsługi przerwania INT 3H. Rejestr DS

zawiera 0.

1D OF : 40 01

(czytamy od tyłu), każdy adres

programu obsługi

składa się z 4 bajtów.

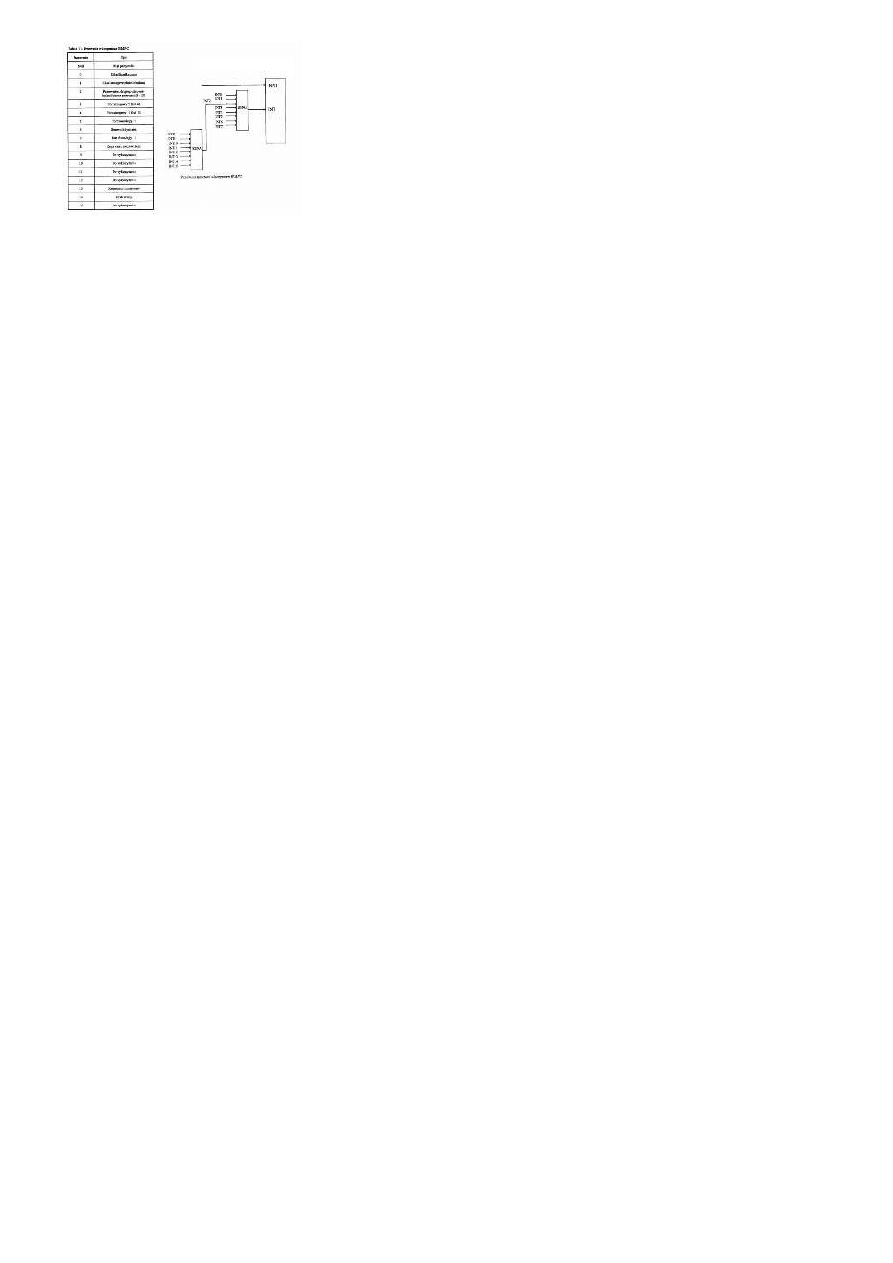

Przedstaw na rysunku jak rozwiązano obsługę przerwań w

komputerze IBM/PC.

2

Jak wygląda koniec programu obsługi przerwania jeżeli

początek to:

PUSH AX

PUSHF

PUSH DS

POP DS

POPF

POP AX

IRET

(należy pamiętać, że instrukcje na końcu trzeba wykonać w

odwrotnej kolejności, niż te na początku!)

Wyszukiwarka

Podobne podstrony:

ak poprawiona by mav

6 10 poprawione by Merlin 2

DR vs AK Walkthrough by kaizoebara (only Axis Campaign)

lek 2009 2termin rozw, Egzamin, I poprawkowy wrzesien 2009- by Kate M

Poradnik jak Poprawnie wgrac Ursus Addon 2013 Dodatek do Farming Simulator 2013 by Edzio021

Poradnik jak dodac Poprawnie MODY do ETS2 by Edzio021

Steel survey by AK

Moja gorsza strona the other side of me 1 20 by Aryaa Wersja poprawiona!

test poprawkowy grupa 1

WADY STÓP poprawki

ZPSBN T 24 ON poprawiony

Prezentacja poprawiona

Chemia organiczna czesc I poprawiona

Postępowanie poprawione

Wykład 5 Sektor finansów publicznych poprawiony

więcej podobnych podstron