Systemy sterowania

w elektronice przemysłowej

Wykład 2

dr inż. Bartosz Pękosławski

Łódź, dn. 8.03.2012

Katedra Mikroelektroniki i Technik Informatycznych

Politechnika Łódzka

Plan wykładu

2

1. Asembler – zapis stałych liczbowych

2. Asembler AVR – przegląd wybranych instrukcji

3. Stos

4. Przekazywanie parametrów do podprogramu

5. Obsługa przerwań

Asembler – stałe liczbowe

3

Przykłady:

1234

- wartość dziesiętna

'A'

- kod ASCII znaku „A”

$102A

- adres (zapis heksadecymalny)

0x2F

- wartość heksadecymalna (szestnastkowa)

0b01010111 - wartość binarna

1 << 6

- wartość 0b01000000 = 0x40

Równoważne instrukcje:

LDI R21, 0b01001000

LDI R21, 0x48

LDI R21, (1 << PB6) + (1 << PB3)

4

Asembler - rodzaje instrukcji

instrukcje przesyłu danych,

instrukcje arytmetyczne,

instrukcje operacji bitowych,

instrukcje porównań,

instrukcje skoków bezwarunkowych,

instrukcje skoków i powrotów z podprogramów,

instrukcje skoków warunkowych,

instrukcje dodatkowe.

5

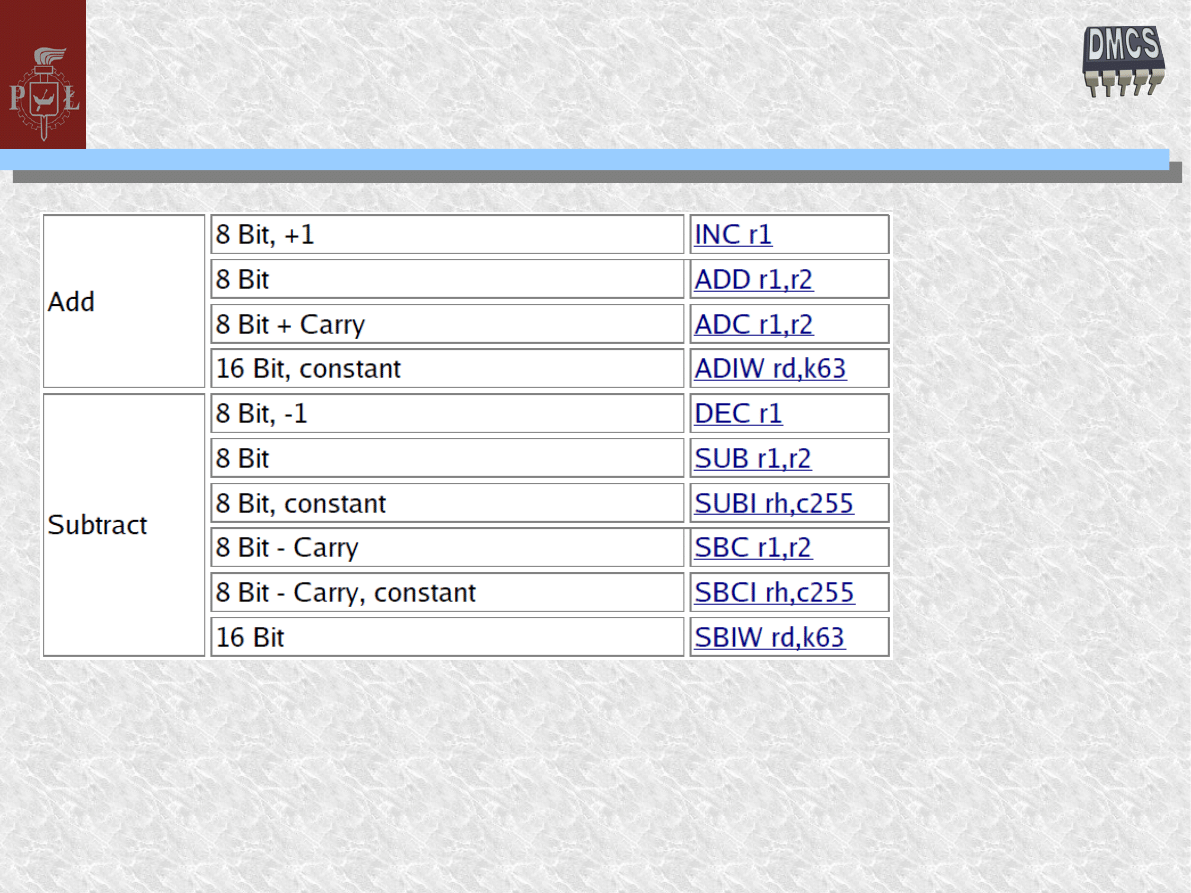

Asembler – instrukcje arytmetyczne

Również mnożenie (wynik R1:R0):

MUL r1, r2

MULS r1, r2

MULSU r1, r2

FMUL r1, r2

FMULS r1, r2

FMULSU r1, r2

r1, r2 = R0..R31

rh = R16..R31

rd =R24,R26,R28,R30

k63 = 0..63

c255 = 0..255

6

Asembler – instrukcje arytmetyczne

Reprezentacja liczb całkowitych w kodzie binarnym 8-bitowym:

Uzupełnienie do dwóch (Two's complement, U2) – zapis liczb całkowitych,

wartość ujemna –W zakodowana na N bitach odpowiada kodowi KOD = 2

N

– W

Operacje dodawania i odejmowania w U2 są wykonywane jednakowo dla

liczb ze znakiem jak i bez znaku

KOD

Liczba bez znaku

Liczba ze znakiem

0111 1111

127

127

0111 1110

126

126

....

...

...

0000 0001

1

1

0000 0000

0

0

1111 1111

255

255 – 256 = –1

1111 1110

254

254 – 256 = –2

...

...

...

1000 0001

129

129 – 256 = –127

1000 0000

128

128 – 256 = –128

7

Asembler – instrukcje arytmetyczne:

wybrane przykłady (dodawanie)

Instrukcja

Początkowa

zawartość

rejestrów

Wynik

SREG

ADD R21, R22

R21=0xFF

R22=0x22

R21=0x21

C=1

INC R21

R21=0xFF

R21=0x00

Z=1

(C bez zmian)

ADC R21, R22

R21=0x11

R22=0x22

C(SREG) = 1

R21=0x34

C=0

ADIW R24, 2

R24=0xFF

R25=0x00

R24=0x01

R25=0x01

8

Asembler – instrukcje arytmetyczne:

wybrane przykłady (odejmowanie)

Instrukcja

Początkowa

zawartość

rejestrów

Wynik

SREG

SUB R21, R22

R21=0x01

R22=0x02

R21=0xFF

C=1

N=1

DEC R21

R21=0x01

R21=0x00

Z=1

SUBI R21, 2

R21=0x02

R21=0x00

Z=1

(C bez zmian)

SBC R21, R22

R21=0x03

R22=0x03

C(SREG)=1

R21=0xFF

C=1

N=1

SBCI R21, 3

R21=0x04

C(SREG)=1

R21=0x00

C=0

Z=1

SBIW R24, 4

R24=0x03

R25=0x01

R24=0xFF

R25=0x00

9

Asembler – instrukcje arytmetyczne:

wybrane przykłady (mnożenie)

Instrukcja

Początkowa

zawartość

rejestrów

Wynik

SREG

MUL R21, R22

R21=0xFF (255)

R22=0xFE (254)

R0=0x02

R1=0xFD

(64770)

MULS R21, R22

R21=0xFF (-1)

R22=0xFE (-2)

R0=0x02

R1=0x00

(2)

MULSU R21, R22

R21=0xFF (-1)

R22=0xFE (254)

R0=0x02

R1=0xFF

(-254)

C=1

10

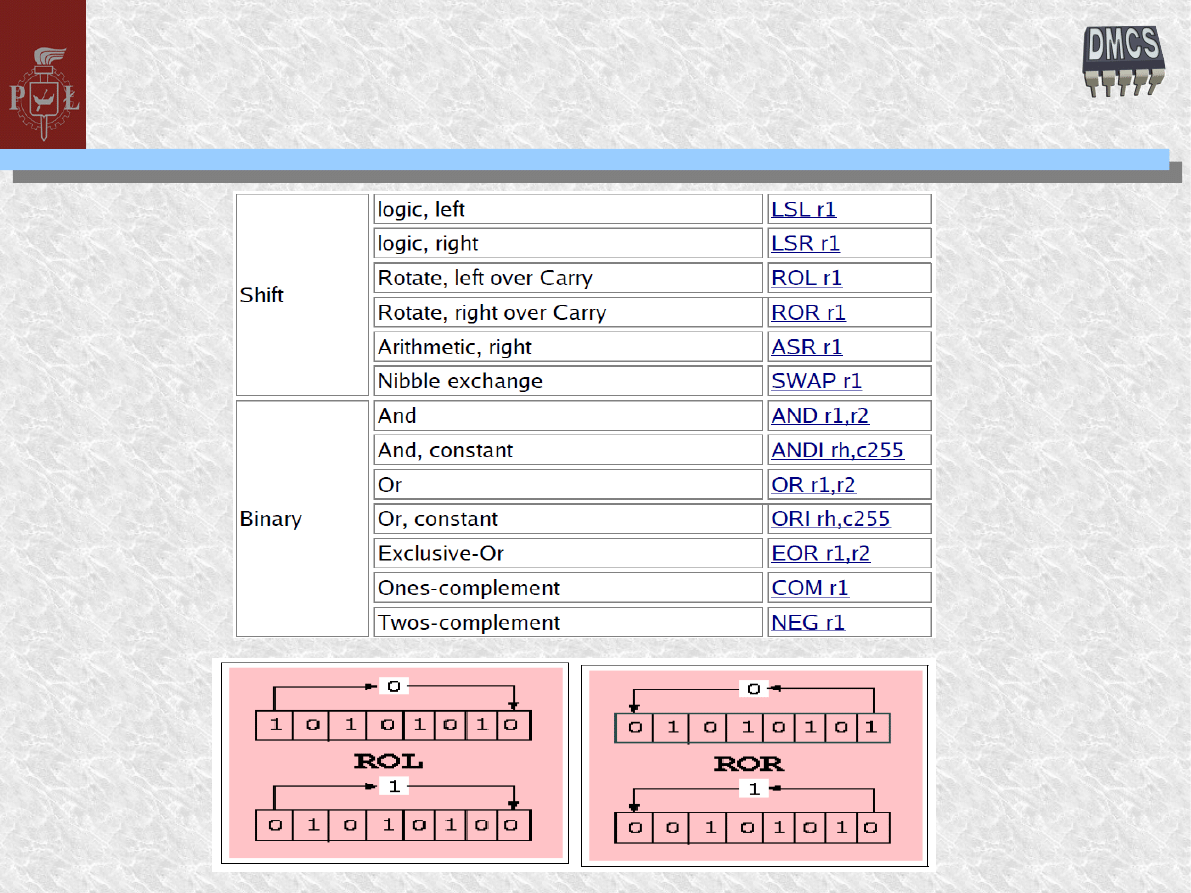

Asembler – instrukcje operacji bitowych

11

Asembler – instrukcje operacji bitowych:

wybrane przykłady (przesuwanie)

Instrukcja

Początkowa

zawartość

rejestrów

Wynik

SREG

LSL R21

R21=0x81

R21=0x02

C=1

LSR R21

R21=0x81

R21=0x40

C=1

ROL R21

R21=0x81

C(SREG)=1

R21=0x03

C=1

ROR R21

R21=0x81

C(SREG)=1

R21=0xC0

C=1

ASR R21

R21=0x81

R21=0xC0

C=1

SWAP R21

R21=0x23

R21=0x32

-

12

Asembler – instrukcje operacji bitowych:

wybrane przykłady (bitowe)

Instrukcja

Początkowa

zawartość

rejestrów

Wynik

SREG

AND R21, R22

R21=0x21

R22=0x20

R21=0x20

ANDI R21, 0x02

R21=0x21

R21=0x00

Z=1

OR R21, R21

R21=0x21

R22=0x20

R21=0x21

ORI R21, 0xFF

R21=0x21

R21=0xFF

EOR R21, R22

R21=0x21

R22=0x20

R21=0x01

COM R21

R21=0x01

R21=0xFE

NEG R21

R21=0x01

R21=0xFF

13

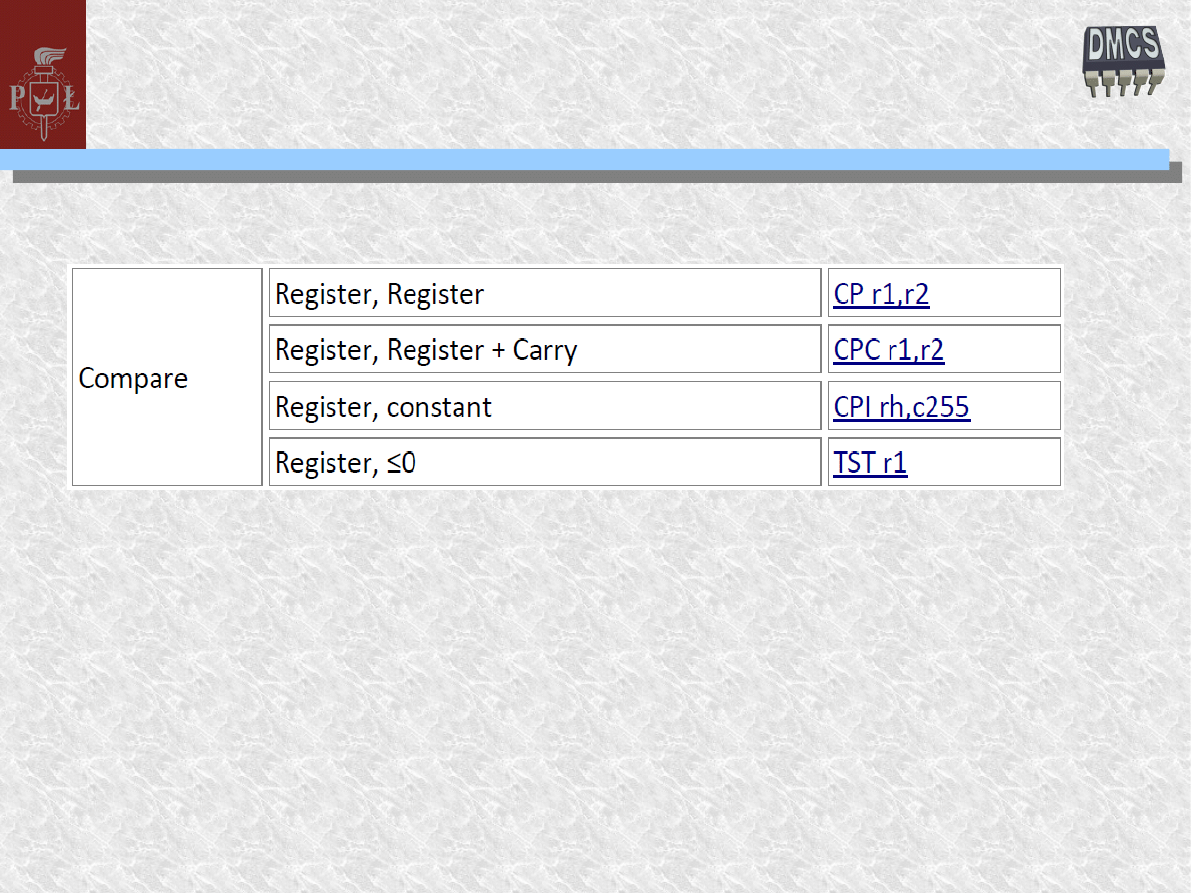

Asembler – instrukcje porównań

14

Asembler – instrukcje porównań:

wybrane przykłady

Instrukcja

Początkowa

zawartość

rejestrów

Wynik

SREG

CP R21, R22

R21=0x03

R22=0x02

CP R21, R22

R21=0x03

R22=0x03

Z=1

CP R21, R22

R21=0x03

R22=0x04

C=1

N=1

CPC R21, R22

R21=0x03

R22=0x03

C(SREG)=1

C=1

N=1

CPI R21, 3

R21=0x04

TST R21

R21=0x00

Z=1

15

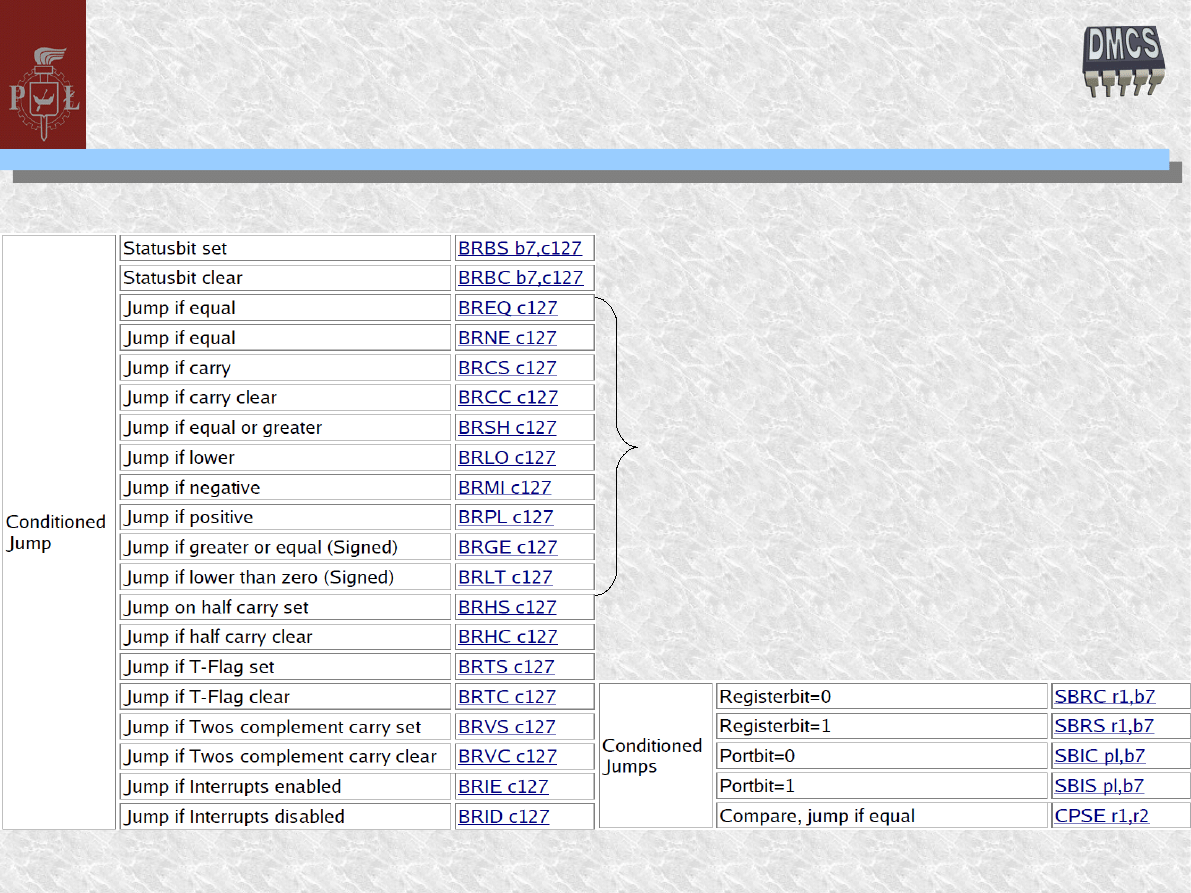

Asembler – skoków warunkowych

16

Asembler – instrukcje skoków

warunkowych: wybrane przykłady

Instrukcja

SREG

Skok

BREQ etykieta

Z=1

tak

BRNE etykieta

Z=0

tak

BRCS etykieta

C=1

tak

BRCC etykieta

C=0

tak

BRSH etykieta

C=0 lub Z=1

tak

BRLO etykieta

C=1 i Z=0

tak

BRMI etykieta

N=1

tak

BTPL etykieta

N=0

tak

BRGE etykieta

N=0 i V=0 lub

N=1 i V=1

tak

BRLT etykieta

N=1 i V=0 lub

N=0 i V=1

tak

17

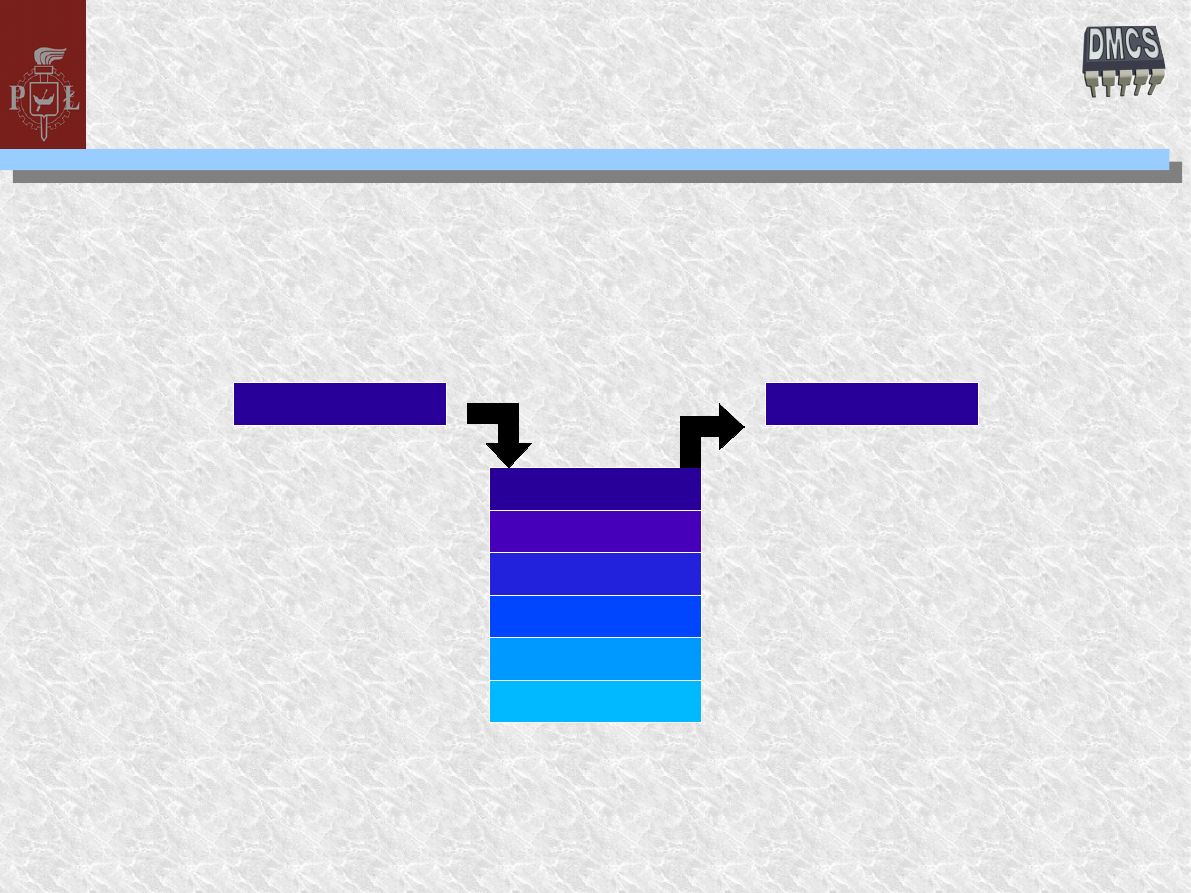

Stos

Stos – obszar pamięci danych, do którego dane są

odkładane na wierzch i pobierane z wierzchołka

Struktura LIFO (Last-In-First-Out)

18

Stos

1. Stos rosnący, wskaźnik stosu wskazuje na pierwszy wolny adres

2. Stos rosnący, wskaźnik stosu wskazuje na ostatni zajęty adres

3. Stos malejący, wskaźnik stosu wskazuje na pierwszy wolny

adres (AVR)

4. Stos malejący, wskaźnik stosu wskazuje na ostatni zajęty adres

Wskaźnik stosu – rejestry 8-bitowe SPH i SPL

19

Stos - instrukcje

PUSH r1

- odłożenie wartości rejestru r1 na stos

POP r1

- zdjęcie ze stosu wartości i zapisanie w rejestrze r1

Automatyczna aktualizacja wskaźnika stosu

Liczba użytych instrukcji PUSH i POP jednakowa

(inaczej - przepełnienie stosu)

Odwrócona kolejność odkładanych i zdejmowanych wartości

Przed użyciem należy ustawić jednorazowo wskaźnik stosu na adres

powyżej $5F

20

Stos - przykład

.include ”m32def.inc”

....

LDI R16, HIGH(RAMEND)

OUT SPH, R16

LDI R16, LOW(RAMEND)

OUT SPL, R16

....

PUSH R2

PUSH R3

POP R5

PUSH R1

POP R7

POP R8

....

ustawienie wskaźnika stosu (koniec pamięci SRAM)

.equ

RAMEND = $85F

21

Podprogram

– przekazywanie parametrów (rejestry)

....

LDI R16, 0x23

LDI R17, 0x45

RCALL podprogram

....

podprogram:

MUL R16, R16

MUL R17, R17

ADD R16, R17

RET

zapisanie wartości parametrów do rejestrów

22

Podprogram

– przekazywanie parametrów (stos)

....

LDI R16, 0x23

LDI R17, 0x45

PUSH R16

PUSH R17

RCALL podprogram

POP R17

POP R16

....

podprogram:

IN ZH, SPH

IN ZL, SPL

SBWI Z, 1

LD R17, -Z

LD R16, -Z

...

RET

zapisanie wartości parametrów na stos

Trudniejszy sposób, ale możliwość przekazania

dużej liczny parametrów i rekurencyjnego

wywoływania podprogramów

Adres powrotu

Parametr 2

Parametr 1

23

Podprogram

– kopia wartości rejestrów roboczych

....

LDI R20, 0x0A

next:

RCALL podprogram

DEC R20

BRNE next

....

podprogram:

PUSH R20

PUSH R21

LDI R20, 0x0B

....

POP R21

POP R20

RET

pętla indeksowana R20

Rejestr R20 zachowuje oryginalną wartość

24

Przerwania

Przerwanie (interrupt, IRQ) – sygnał powodujący wstrzymanie

wykonania aktualnego programu i wykonanie procedury obsługi

przerwania (interrupt handler)

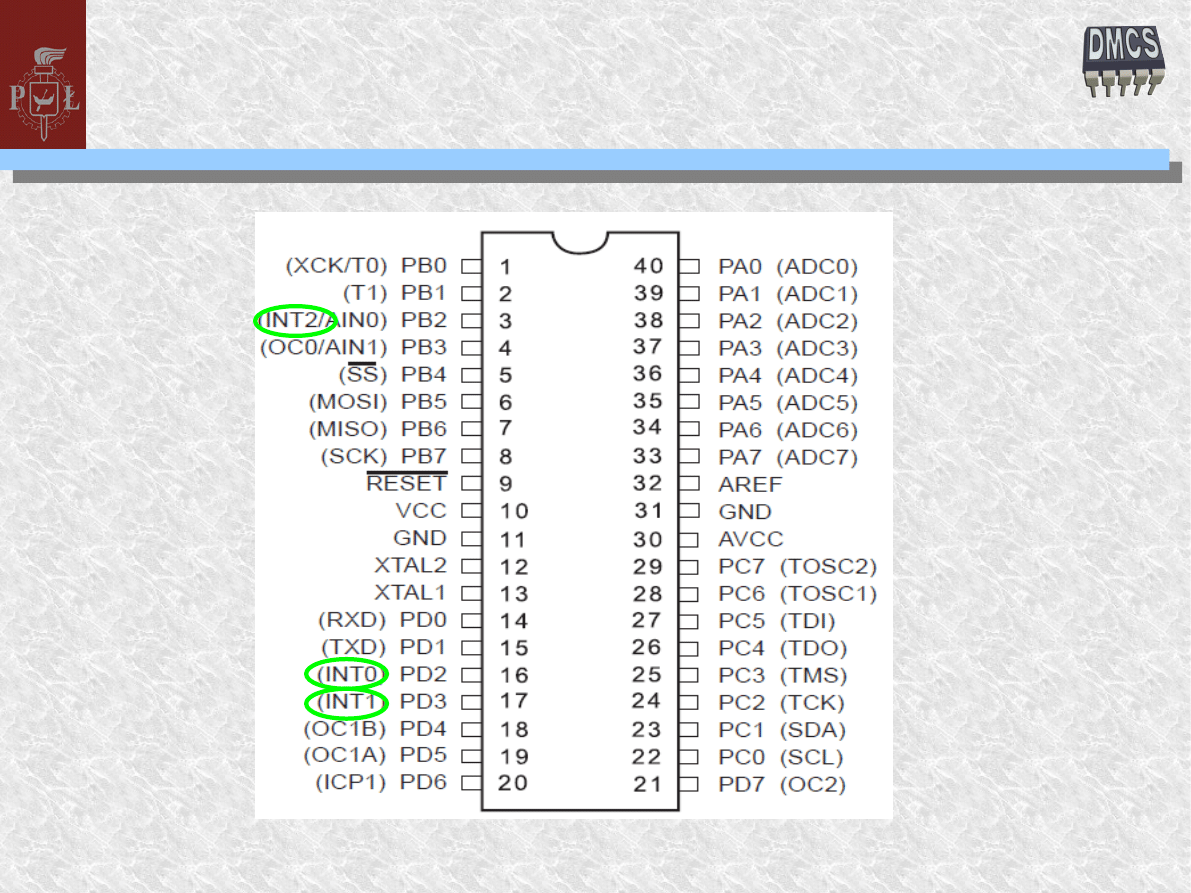

Źródła przerwań (ATmega):

przerwania zewnętrzne (zmiana stanu wejść),

timery,

interfejsy UART, SPI, 2-wire,

przetwornik A/C,

komparator analogowy,

pamięć EEPROM

Brak konieczności odpytywania urządzenia (odczytywania rejestru

w pętli) – program główny może realizować inne zadania

25

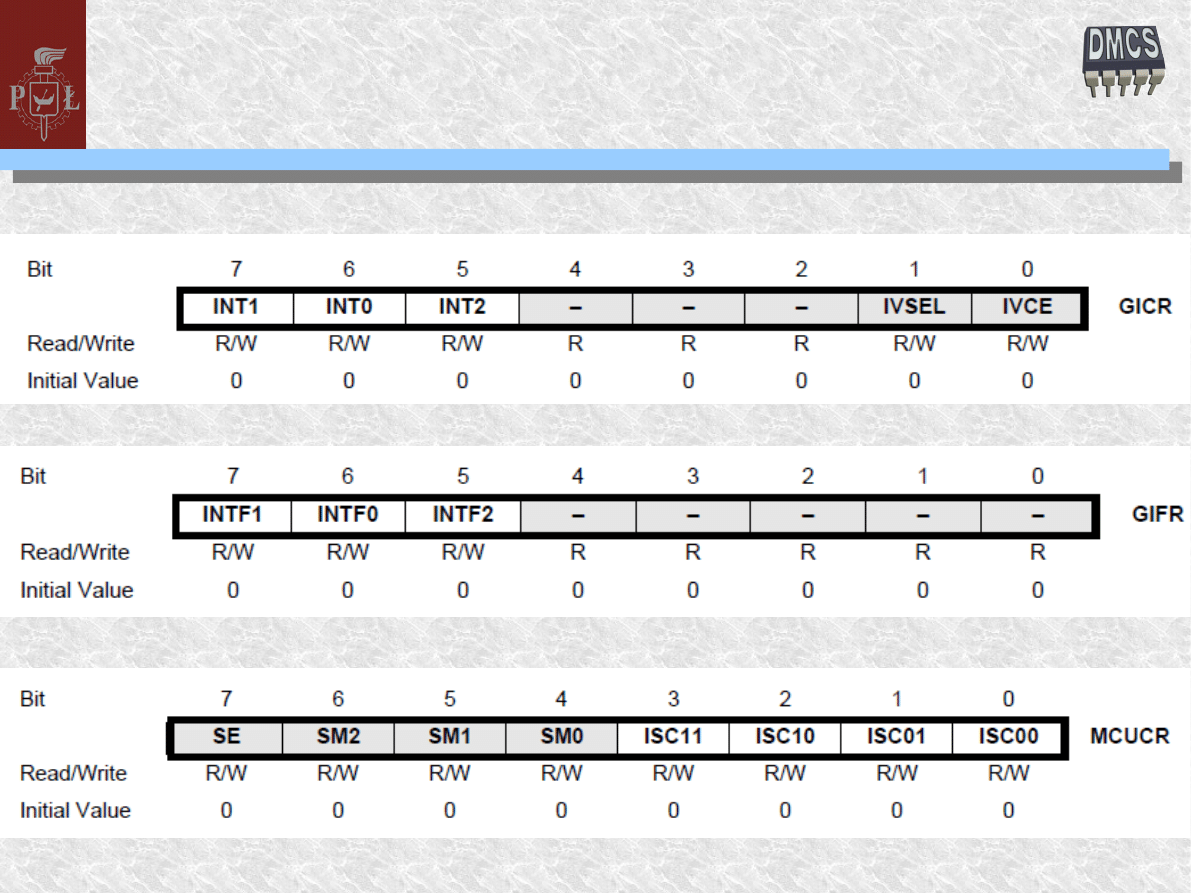

ATmega 32 – przerwania zewnętrzne

26

ATmega 32 – przerwania zewnętrzne

Rejestr flagowy:

Rejestr sterujący (maskujący):

Rejestr sterujący 2:

27

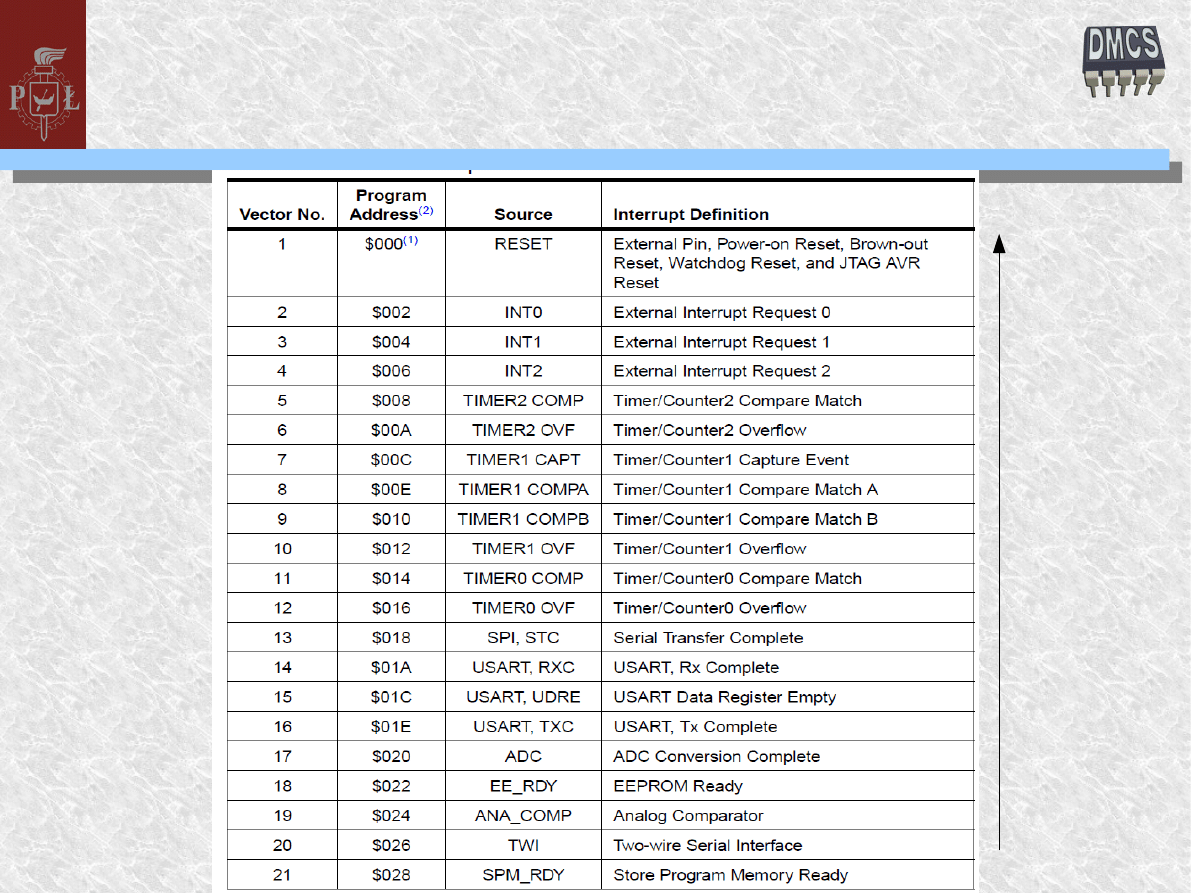

Wektory przerwań

Priorytet

28

Wektory przerwań

.equ

INT0addr=$002; External Interrupt0 Vector Address

.equ

INT1addr=$004; External Interrupt1 Vector Address

.equ

INT2addr=$006; External Interrupt2 Vector Address

.equ

OC2addr =$008; Output Compare2 Interrupt Vector Address

.equ

OVF2addr=$00a; Overflow2 Interrupt Vector Address

.equ

ICP1addr=$00c; Input Capture1 Interrupt Vector Address

.equ

OC1Aaddr=$00e; Output Compare1A Interrupt Vector Address

.equ

OC1Baddr=$010; Output Compare1B Interrupt Vector Address

.equ

OVF1addr=$012; Overflow1 Interrupt Vector Address

.equ

OC0addr =$014; Output Compare0 Interrupt Vector Address

.equ

OVF0addr=$016; Overflow0 Interrupt Vector Address

.equ

SPIaddr =$018; SPI Interrupt Vector Address

.equ

URXCaddr=$01a; USART Receive Complete Interrupt Vector Address

.equ

UDREaddr=$01c; USART Data Register Empty Interrupt Vector Address

.equ

UTXCaddr=$01e; USART Transmit Complete Interrupt Vector Address

.equ

ADCCaddr=$020; ADC Interrupt Vector Address

.equ

ERDYaddr=$022; EEPROM Interrupt Vector Address

.equ

ACIaddr =$024; Analog Comparator Interrupt Vector Address

.equ

TWSIaddr=$026; Irq. vector address for Two-Wire Interface

.equ

SPMRaddr=$028; Store Program Memory Ready Interrupt Vector Address

W pliku „m32def.inc” :

29

Przerwania – procedury obsługi

.include ”m32def.inc”

....

.cseg

.org $0000

RJMP start

.org $....

RJMP procedura

....

start:

LDI R16, HIGH(RAMEND)

OUT SPH, R16

LDI R16, LOW(RAMEND)

OUT SPL, R16

SEI

....

procedura:

....

RETI

wektor przerwania

30

Przerwania – przykład

.include ”m32def.inc”

.cseg

.org $0000

RJMP start

.org INT1addr

RJMP int_1

start:

LDI R16, HIGH(RAMEND)

OUT SPH, R16

LDI R16, LOW(RAMEND)

OUT SPL, R16

LDI R16, 1 << INT1

OUT GICR, R16

SEI

....

int_1:

INC R20

RETI

włączenie przerwania INT1

Dziękuję za uwagę.

Document Outline

- Slajd 1

- Slajd 2

- Slajd 3

- Slajd 4

- Slajd 5

- Slajd 6

- Slajd 7

- Slajd 8

- Slajd 9

- Slajd 10

- Slajd 11

- Slajd 12

- Slajd 13

- Slajd 14

- Slajd 15

- Slajd 16

- Slajd 17

- Slajd 18

- Slajd 19

- Slajd 20

- Slajd 21

- Slajd 22

- Slajd 23

- Slajd 24

- Slajd 25

- Slajd 26

- Slajd 27

- Slajd 28

- Slajd 29

- Slajd 30

- Slajd 31

Wyszukiwarka

Podobne podstrony:

BP SSEP wyklad6 id 92513 Nieznany (2)

BP SSEP wyklad4

BP SSEP wyklad1

BP SSEP wyklad11

BP SSEP wyklad5

BP SSEP wyklad7 id 92514 Nieznany

BP SSEP wyklad13

BP SSEP wyklad6 id 92513 Nieznany (2)

BP SSEP wyklad4

Zal-lab-BP-zaoczne, politechnika lubelska, budownictwo, 3 rok, semestr 5, fizyka budowli, wykład

Wykład 2 BP PLAN FINANSOWY, ZASADY SPORZĄDZANIA PROGNOZ FINANSOWYCH

Wykład 3 BP PLAN FINANSOWY – PROGNOZA PRZEPŁYWÓW PIENIĘŻNYCH

Wykład 5 BP PREZENTACJA PRZEDSIĘBIROSTWA I PLANOWANEGO PRZEDSIĘWZIĘCIA W BIZNESPLANIE

Wykład 1 BP PLANOWANIE W PRZEDSIĘBIORSTWIE, STRUKTURA I FUNKCJE BIZNESPLANU

tematyka wykładów bp czII regulacja, Studia, Budownictwo wodne I

Wykład 6 BP PLAN MARKETINGOWY

Wykład 8 BP OCENA OPŁACALNOŚCI PRZEDSIĘWZIĘCIA BIZNESOWEGO

Wykład 7 BP PLAN DZIAŁALNOŚCI OPERACYJNEJI PLAN ZASOBÓW LUDZKICH

Zal-lab-BP-zaoczne, politechnika lubelska, budownictwo, 3 rok, semestr 5, fizyka budowli, wykład

więcej podobnych podstron