Pami ci

W mikrokontrolerach mo na wyró ni nast puj ce typy pami ci:

•

pami programu (zawieraj ca kod programu, tablice sta!ych, wektor resetu i przerwa"),

•

pami danych (przechowuj ca zmienne),

•

stos sprz towy (obs!ugi przerwa" i wywo!a" funkcji odk!adaj na niego bie c warto%

licznika rozkazów i po zako"czeniu dzia!ania „zdejmuj ” j ),

•

pami EEPROM (przechowuje zmienne lub tablice sta!ych, które po wy! czeniu

zasilania nie mog ulec skasowaniu).

Pami programu jest wykonana w technologii ROM, EPROM, OTP lub FLASH. Natomiast

pami danych najcz %ciej jest typu SRAM. Przegl d podstawowych typów pami ci zestawiono

w tabeli 1.

W asno ci pami ci

Stosowane typy pami ci

Zawarto% pami ci nie zanika wraz z

wy! czeniem napi cia zasilania.

Z pami ci mo na czyta , lecz nie mo na do

niej wpisywa danych. Umieszczanie danych

w pami ci wymaga specjalnego procesu,

zwanego programowaniem.

ROM (Read Only Memory)

–

programowanie zawarto%ci pami ci

nast puje w procesie produkcyjnym i nie mo e

by przeprowadzone przez u ytkownika.

EPROM (Erasable Programmable ROM)

– pami ci z mo liwo%ci

kasowanie

dotychczasowej zawarto%ci promieniami

ultrafioletowymi i prowadzania nowej

zawarto%ci za pomoc

zewn trznego

programatora. Umieszczane s

w

obudowach z okienkiem kwarcowym w celu

umo liwienia kasowania.

OTP (One Time Programmable)

– pami ci typu EPROM umieszczane w

obudowach bez okienka kwarcowego.

Dlatego mo liwe jest tylko jednokrotne

zaprogramowanie pami ci bez mo liwo%ci

skasowanie jej zawarto%ci.

FLASH (Bulk Erasable Non-Volatile

Memory)

– pami ci z mo liwo%ci

kasowanie

zawarto%ci i programowania bezpo%rednio

w systemie mikroprocesorowym.

Zawarto% pami ci zanika wraz z wy! czeniem

napi cia zasilania.

Z pami ci mo na zarówno czyta , jak i

wpisywa do niej dane.

SRAM (Static Random Access Memory)

– pami ci RAM statyczne. S to pami ci o

krótkich czasach dost pu, prostsze w obs!udze

przez jednostk centraln , ale dro sze.

DRAM (Dynamic Random Access Memory)

– pami ci RAM dynamiczne. S to pami ci

ta"sze, ale ich obs!uga przez jednostk

centraln jest bardziej skomplikowana. Polega

to na konieczno%ci wykonywania w krótkich

odst pach czasu okre%lonych operacji na

pami ci (tzw. od%wie aniu). W przeciwnym

razie dane zawarte w pami ci dynamicznej

zanikaj .

Tabela 1. Przegl d podstawowych uk!adów pami ci

Uk'ady scalone pami ciowe

W sk!ad systemów mikroprocesorowych (mse)cz sto mog wchodzi uk!ady pami ciowe.

Szczególnie, gdy u yty mikrokontroler nie posiada wewn trznej pami ci danych i programu.

Generalnie pami ci mo na podzieli na dwie grupy:

•

pami ci ulotne, trzymaj dane tylko wtedy, gdy s zasilane. Zanik napi cia zasilania

powoduje utrat przechowywanych informacji,

•

pami ci nieulotne, zachowane dane nie ulegaj skasowaniu po wy! czeniu napi cia

zasilania.

Pierwsza grypa to pami ci RAM (Random Access Memory). S one pami ciami, w których dane

mog by zarówno zapisywane, jak z niej odczytywane. Istniej dwa g!ówne typy tych pami ci:

•

pami statyczna SRAM,

•

pami dynamiczna DRAM.

Pami SRAM przechowuje bity informacji w postaci stanów przerzutników bistabilnych. Ka da

komórka pami ci sk!ada si z oko!o od 4 do 6 tranzystorów. Uk!ady SRAM mog mie

wzgl dnie niski pobór mocy w trybie podtrzymywania zawarto%ci pami ci, natomiast w trybie

pracy pobieraj do% du y pr d. Zalet tych pami ci jest prostota sterowania oraz szybko%

(pami ci te wykonane z arsenku galu GaAs maj czas dost pu poni ej 1ns). Dzi ki prostemu

sterowaniu s one najcz %ciej stosowane w mse.

W pami ci DRAM informacja przechowywana jest w postaci !adunków zgromadzonych w

kondensatorach, jakie powstaj pomi dzy emiterami tranzystorów MOS i pod!o em uk!adu.

Dane w tych pami ciach maj tendencje do zanikania i wymagaj ci g!ego odnawiania. Proces

taki nazywa si „od)wie*aniem” i wymaga specjalnych uk!adów do wytwarzania sygna!ów

od%wie aj cych. Zalet uk!adów DRAM jest niski koszt produkcji, ze wzgl du na niewielk

powierzchni zajmowanej powierzchni krzemu. Ka da komórka pami ci DRAM ma tylko jeden

tranzystor MOS. Z zalety tej wynika równie inna cecha: pami ci DRAM posiadaj znacznie

wi ksz pojemno% od pami ci SRAM (obecnie dost pne s na rynku pami ci SRAM do 512kB).

Wad tych uk!adów jest skomplikowane sterowanie, wynikaj ce z multipleksowania adresów

rz dów i kolumn (pami ci te adresuje si jak macierz) oraz wynikaj cego z tego d!u szego czasu

dost pu, który jest dodatkowo zwi kszany o czas potrzebny na od%wie anie.

Istnieje ca!y szereg pami ci nieulotnych (cz % z nich zestawiono w tabeli 1). Poni ej

przedstawiono najcz %ciej spotykane typy tych pami ci:

•

Pami ROM (Read Only Memory) s!u y tylko do odczytywania. Informacja w pami ci

ROM jest zapisywana w czasie produkcji w formie maski, na podstawie dostarczonego

wzorca. Dla zamawiaj cego tak pami oznacza to wysoki koszt jednostkowy. Dlatego

pami ci ROM u ywa si jedynie w urz dzeniach, które s produkowane w d!ugich

seriach.

•

Pami EPROM jest pami ci programowan elektrycznie. U ytkownik sam programuje

swój wzór informacji, jak

chce zapisa . Gdy uk!ad posiada okienko ze szk!a

kwarcowego, mo na tak pami kasowa i programowa ponownie. Jest to du a zaleta

w fazie uruchamiania mse. Kasowanie odbywa si na ogó! przy pomocy %wiat!a

ultrafioletowego. Pami EPROM umieszczona w obudowie plastikowej, znacznie

ta"szej od obudowy ceramicznej z okienkiem szklanym, nosi nazw OTP (One Time

Programmable). Komórki pami ci EPROM s tranzystorami MOS z p!ywaj cymi

bramkami. S one programowane przez wstrzykiwanie elektronów o wysokiej energii.

Komórka taka zawiera „0”, podczas gdy nie zaprogramowane komórki zawieraj „1”.

Zaprogramowanego w ten sposób tranzystora nie mo na wprowadzi

w stan

przewodzenia i usun zgromadzonego w nim !adunku. Mo na tego dokona jedynie

przez kasowanie %wiat!em UV. Promienie UV dostarczaj

elektronom energii,

wystarczaj cej do ponownego przej%cia przez barier

energetyczn

w warstwie

izolacyjnej dwutlenku krzemu wokó! p!ywaj cej bramki. Uk!ady EPROM mog by

kasowane i ponownie programowane oko!o 100 razy.

•

Pami ci EEPROM s uk!adami, które nie tylko s elektrycznie programowalne, ale

równie elektrycznie kasowane. Maj ograniczon liczb cyklów programowania od

oko!o 10000 razy do 1000000 razy. Komórka pami ci EEPROM sk!ada si z tranzystora

NMOS (Metal Nitride Oxide Semiconductor). Do ka dej komórki mo na wprowadzi

!adunek elektryczny, który przechowywany jest w izolowanej warstwie azotku krzemu,

znajduj cej si mi dzy bramk tranzystora, a pod!o em z tlenku krzemu. Eadowanie

inicjuje si poprzez tzw. efekt tunelowy. Powstaje on po przy!o eniu wysokiego napi cia

(20-40V) do bramki tranzystora. Przez zmian polaryzacji tego napi cia, uk!ad mo na

programowa , b dG te kasowa .

•

Pami b'yskowa (FLASH) jest równie

pami ci

programowan

i kasowan

elektrycznie. Koszt jej produkcji jest ni szy ni uk!adu EEPROM. W porównaniu z

pami ci EEPROM cechuje si ona szybszymi czasami programowania i kasowania.

Najcz %ciej pami ta sk!ada si z sektorów, na których mog by wykonywane

odpowiednie operacje, posiada w!asn list komend automatyzuj cych programowanie i

kasowanie pami ci.

Poni ej zostan omówione trzy przyk!adowe uk!ady pami ciowe, które mo na spotka w mse:

pami SRAM 128kB i pami FLASH 128kB.

Pami

SRAM 128kB

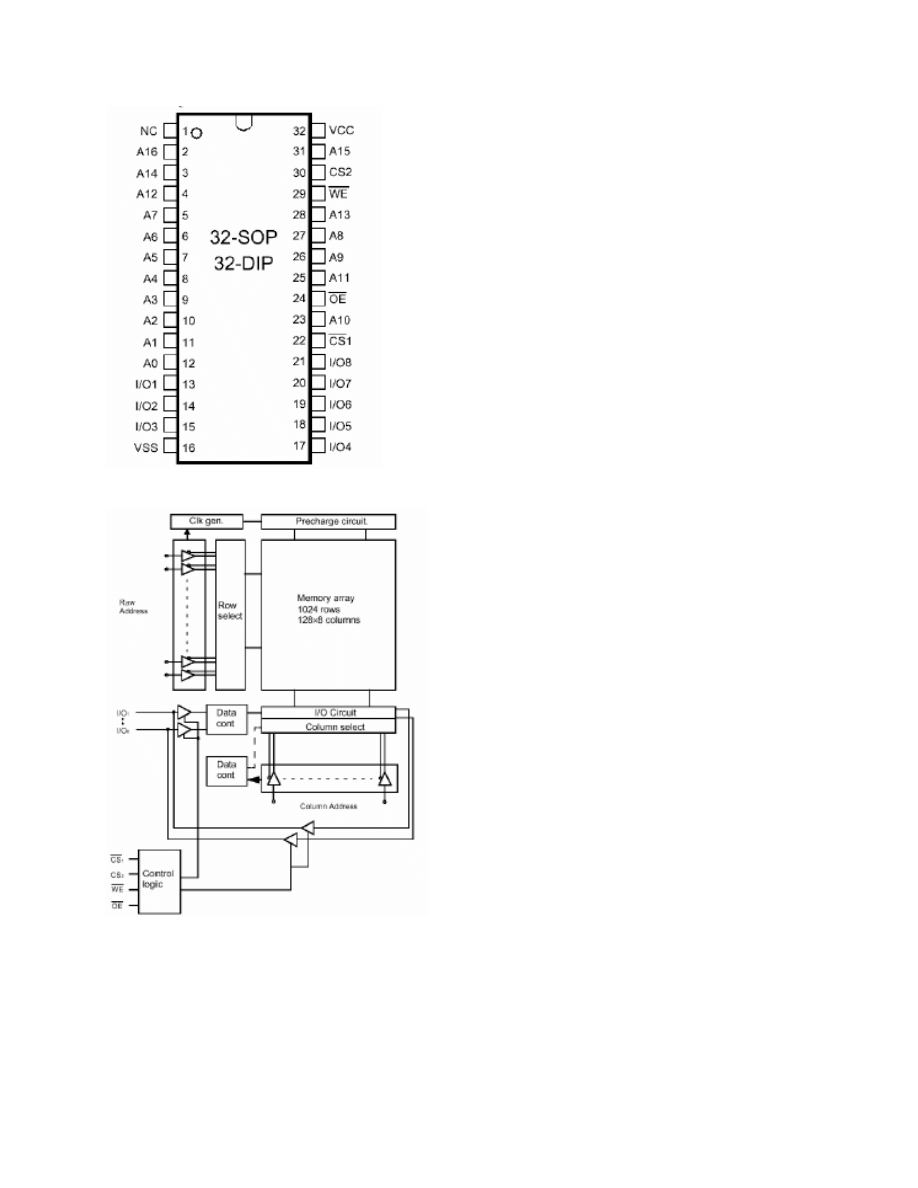

Pami SRAM zostanie przedstawiona na przyk!adzie uk!adu K6T1008C2E firmy Samsung

Electronics. Jest to pami SRAM o pojemno%ci 128Kx8 bitów wykonana w technologii CMOS

o ma!ym poborze mocy. Na rys. 1 pokazano wyprowadzenia uk!adu. S one zgodne ze

standardem dla pami ci o tej pojemno%ci. Równie identyczne wyprowadzenia maj pami ci

np. 512Kx8 bitów, przy czym pin 1 jest lini A17, a pin 30 lini A18.

Rys. 1 Wyprowadzenia uk!adu K6T1008C2E

Rys. 2 Schemat blokowy uk adu K6T1008C2E

Na rys. 2 pokazano schemat blokowy uk!adu pami ci SRAM. Sk!ada si on z uk!adu

kontrolnego, do którego pod! czone s sygna!y CS1, CS2, WE i OE za po%rednictwem których,

steruje si pami ci , uk!adu we/wy s!u cego do wymiany danych pomi dzy matryc pami ci

sk!adaj cej si z 1024 rz dów i 128x8 kolumn, a liniami danych I/O1 do I/O8. Wybór komórki

(bajtu) do zapisu lub odczytu odbywa si za pomoc uk!adów wyboru wierszy i rz dów do

których, pod! czone s linie adresowe A0 – A16.

Sygna y CS

1

i CS

2

s u do uaktywnienia uk adu. Najcz ciej steruje si pierwszym sygna em,

drugi jest na sta e pod czony do „1”. Sygna OE jest wykorzystywany w trakcie czytania danej,

a sygna WE w trakcie pisania danej do pami ci za po rednictwem dwukierunkowych linii

I/O

1

– I/O

8

pod adres wskazany przez linie A

0

– A

16

.

Aby móc zapisa bajt do pami ci musi by ona aktywna (CS

1

– stan niski (L), CS

2

– stan wysoki

(H)) oraz na linii OE ma by stan niski (aktywny), a na linii WE stan wysoki (nieaktywny).

Podobnie jest dla zapisu. W tym przypadku sygna! WE jest niski (warto aby OE by!o w stanie

wysokim).

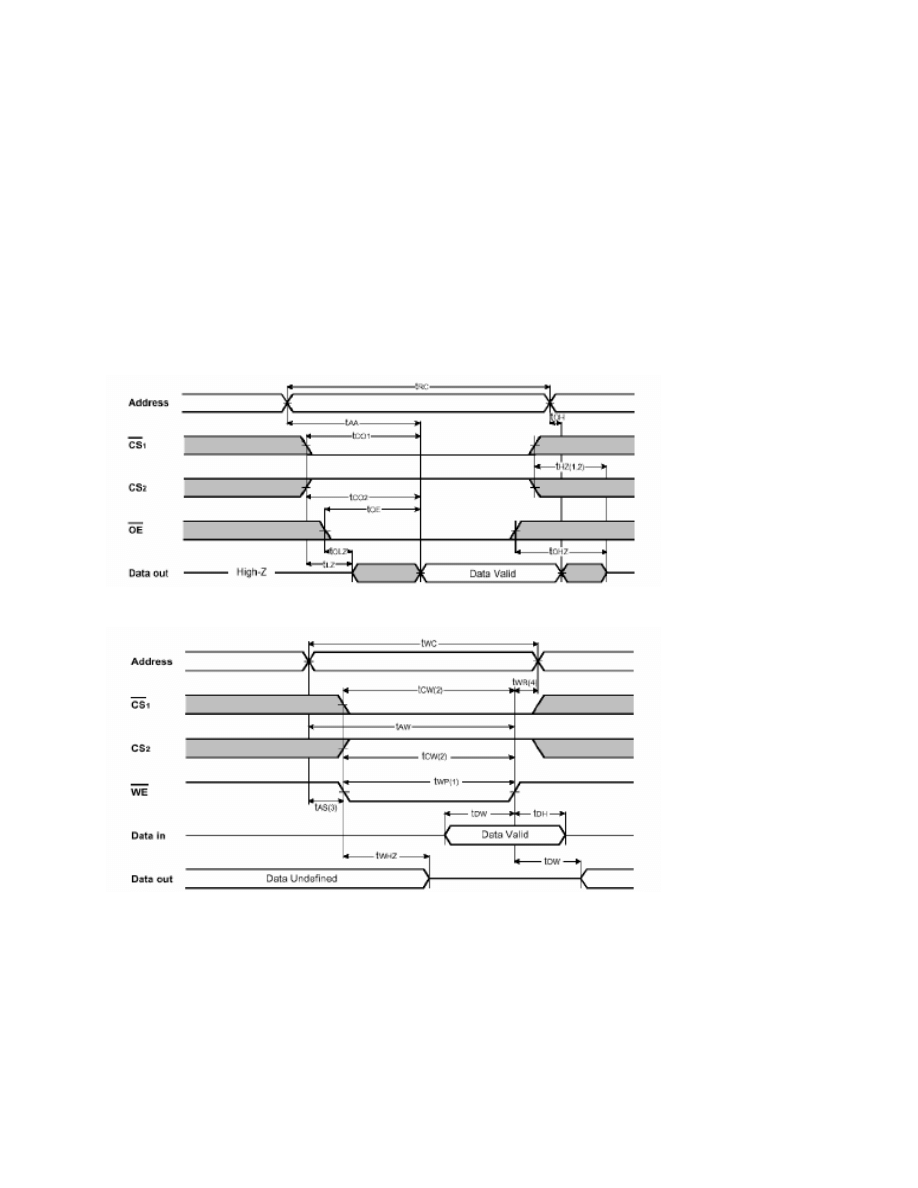

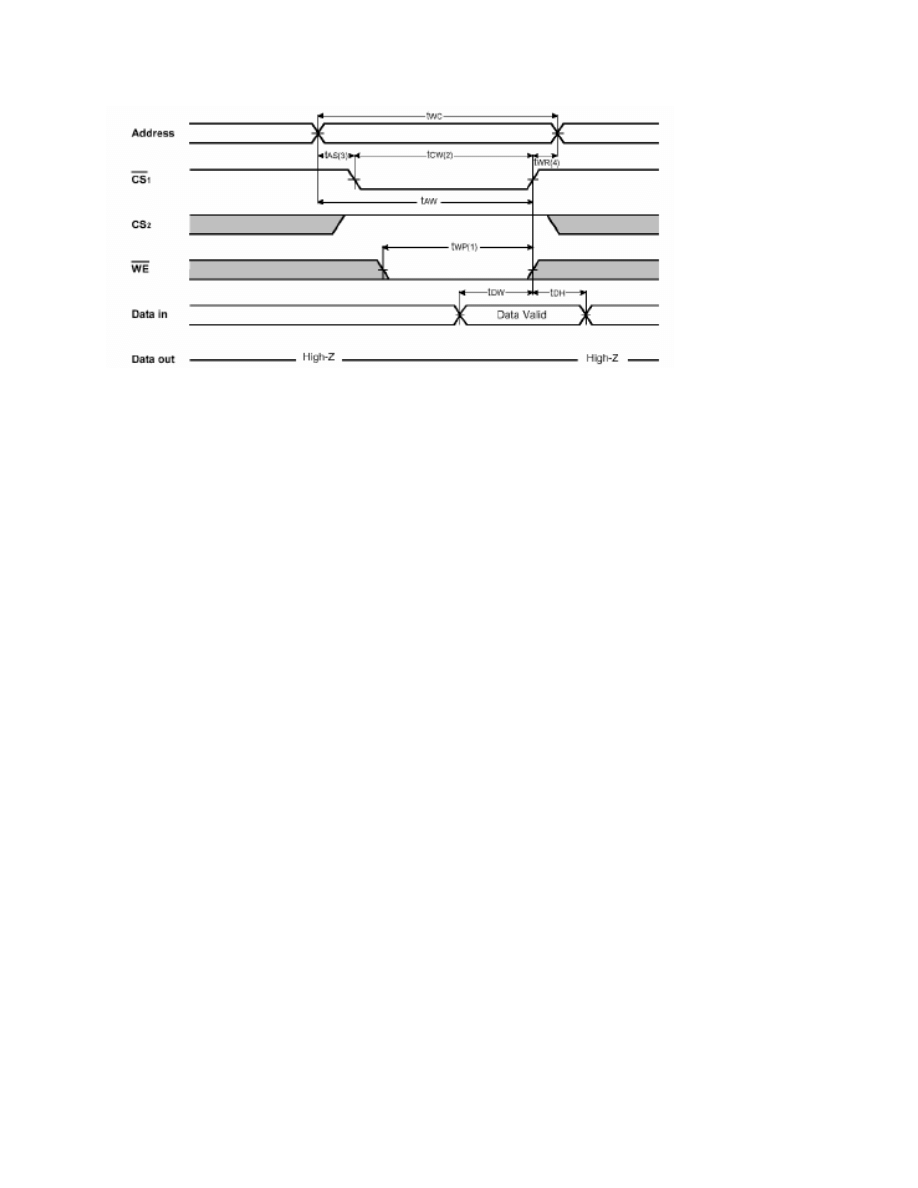

Na poni szych rysunkach pokazano przebiegi cyklu odczytu bajtu z pami ci SRAM (rys. 3) oraz

zapisu do niej bajtu dwoma sposobami, przy czym zak!ada si , e sygna! CS

2

jest nieaktywny (na

zacisku jest stan wysoki). Pierwszy sposób oparty jest na sterowaniu zapisem danej sygna!em

WE (rys. 4), natomiast drugi bazuje na sterowaniu zapisem za pomoc sygna!u CS

1

(rys. 5).

Rys. 3 Przebiegi czasowe cyklu odczytu danych z pami ci (sygna! WE w stanie „Hi”)

Rys. 4 Przebiegi czasowe cyklu zapisu danych do pami ci (sterowanie sygna!em WE)

Rys. 5 Przebiegi czasowe cyklu zapisu danych do pami ci (sterowanie sygna!em CS

1

)

Pami FLASH 128kB

Szczególn zalet pami ci b!yskowych (FLASH) w stosunku do pami ci EEPROM jest krótki

czas kasowania i zapisu. Do programowania i kasowania pami ci b!yskowych potrzebne jest

podwy*szone napi cie 11,5 - 13,5V, które w zale no%ci od typu uk!adu mo e by podawane z

zewn trz lub wytwarzane przez wbudowan1 przetwornic . Pami ci FLASH przyjmuj oprócz

danych polecenia, które umo liwiaj realizacj ró nych rodzajów operacji. Ten typ pami ci

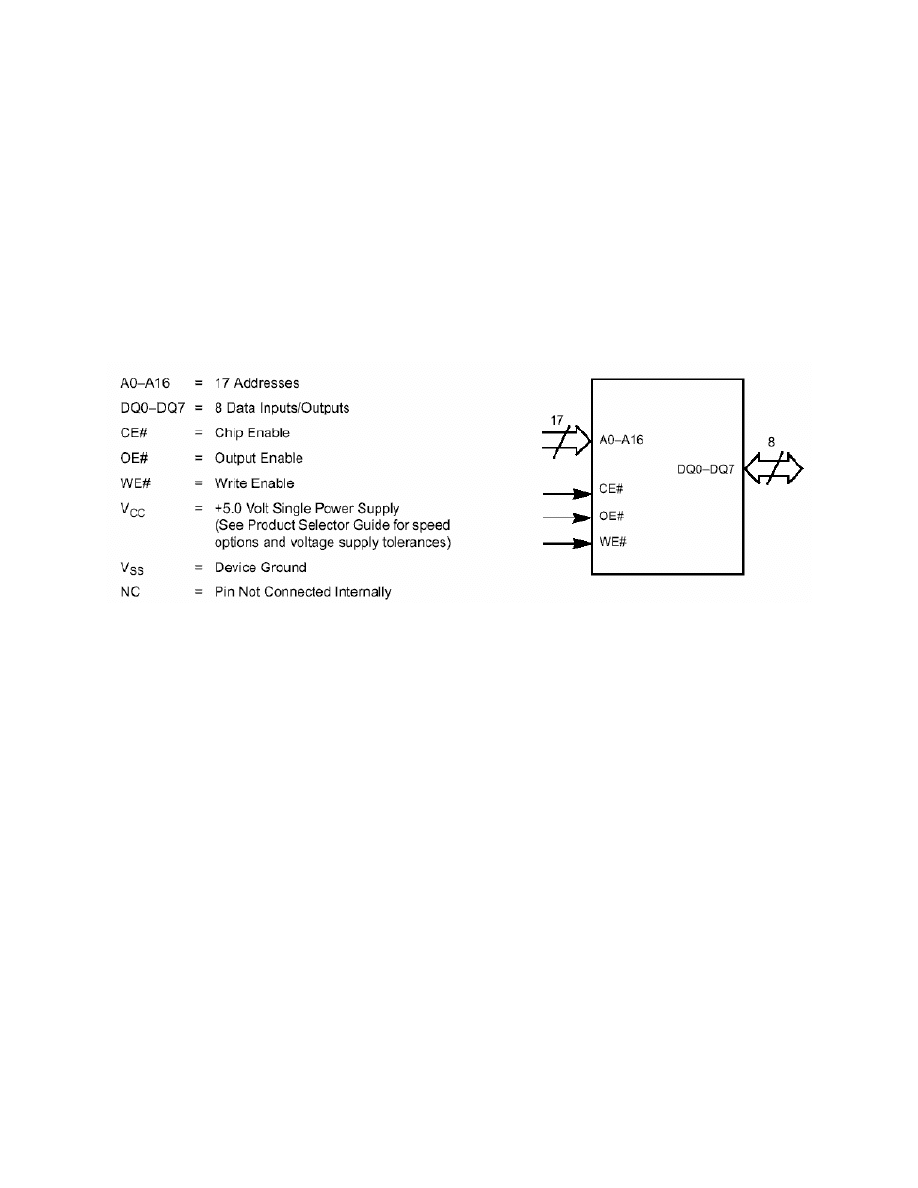

zostanie przedstawiony na przyk!adzie popularnej pami ci typu 29F010 firmy AMD (Advanced

Micro Devices) o organizacji 128k x 8 bitów. Na rys. 6 pokazano symbol logiczny pami ci wraz

z opisem linii.

Rys. 6. Symbol logiczny pami ci Am29F010

Pami ta posiada nast puj ce w!a%ciwo%ci:

•

pojedyncze zasilanie, 5V +-10% dla czytania, zapisu i operacji kasowania programu,

•

maksymalny czas dost pu 45ns,

•

niskie zu ycie energii, maksymalnie 30mA na odczyt i 50mA na programowanie oraz

czyszczenie, mniej ni 25QA podczas trybu standby,

•

elastyczna architektura oparta na sektorach, 8 zunifikowanych sektorów, wszystkie

kombinacje sektorów mog by czyszczone,

•

mo liwo% wymazania ca!ego chipu,

•

ochrona sektorów przed zapisem,

•

wsparcie sprz towe dla zablokowania i odblokowania programowania i czyszczenia dla

wszystkich kombinacji sektorów,

•

wbudowany algorytm czyszczenia automatycznie przeprogramuje i czy%ci chip lub

wszystkie kombinacje wybranych sektorów,

•

wbudowany algorytm programowania automatycznie programuj cy i sprawdzaj cy

dane z zadanego adresu,

•

minimum 100000 gwarantowanych cykli programowania i czyszczenia,

•

programowe metody detekcji ko"ca cyklu programowania i czyszczenia.

Pami Am29F010 jest 1Mbit, 5V pami ci FLASH zorganizowan jako 131072 bajtów.

Produkowana jest w 32-pinowych obudowach typu PLCC ,TSOP i PDIP. Zaprojektowano j z

mo liwo%ci programowania w systemie ze standardowym 5V zasilaniem. Ponadto mo e by

programowana za pomoc standardowego programatora do pami ci EPROM. Pami posiada

wbudowany algorytm programowania (wewn trzny algorytm, który automatycznie weryfikuje

szeroko% i czas trwania impulsów programowania). Zawiera ona tak e wbudowany algorytm

czyszczenia. Podczas czyszczenia urz dzenie automatycznie kontroluje czas i szeroko%

sygna!ów oraz weryfikuje w!a%ciwe komórki docelowe. System nadrz dny mo e wykrywa

zako"czenia operacji czyszczenia/programowania poprzez czytanie bitów statusu: DQ7

(DATA#Polling) i DQ6 (toggle).

Po zako"czeniu cyklu programowania/czyszczenia pami jest gotowa do czytania z niej danych

lub oczekuje na nast pn komend . Sektorowa architektura pami ci pozwala na czyszczenie, czy

ponowne programowanie wybranych sektorów pami ci bez wp!ywu na pozosta!e sektory.

Sprz towa ochrona danych wykrywa niski poziom napi cia zasilania i wstrzymuje proces

zapisywania podczas zmiany napi cia. Pami mo na prze! czy w tryb standby, w celu znacznej

redukcji pobieranej mocy.

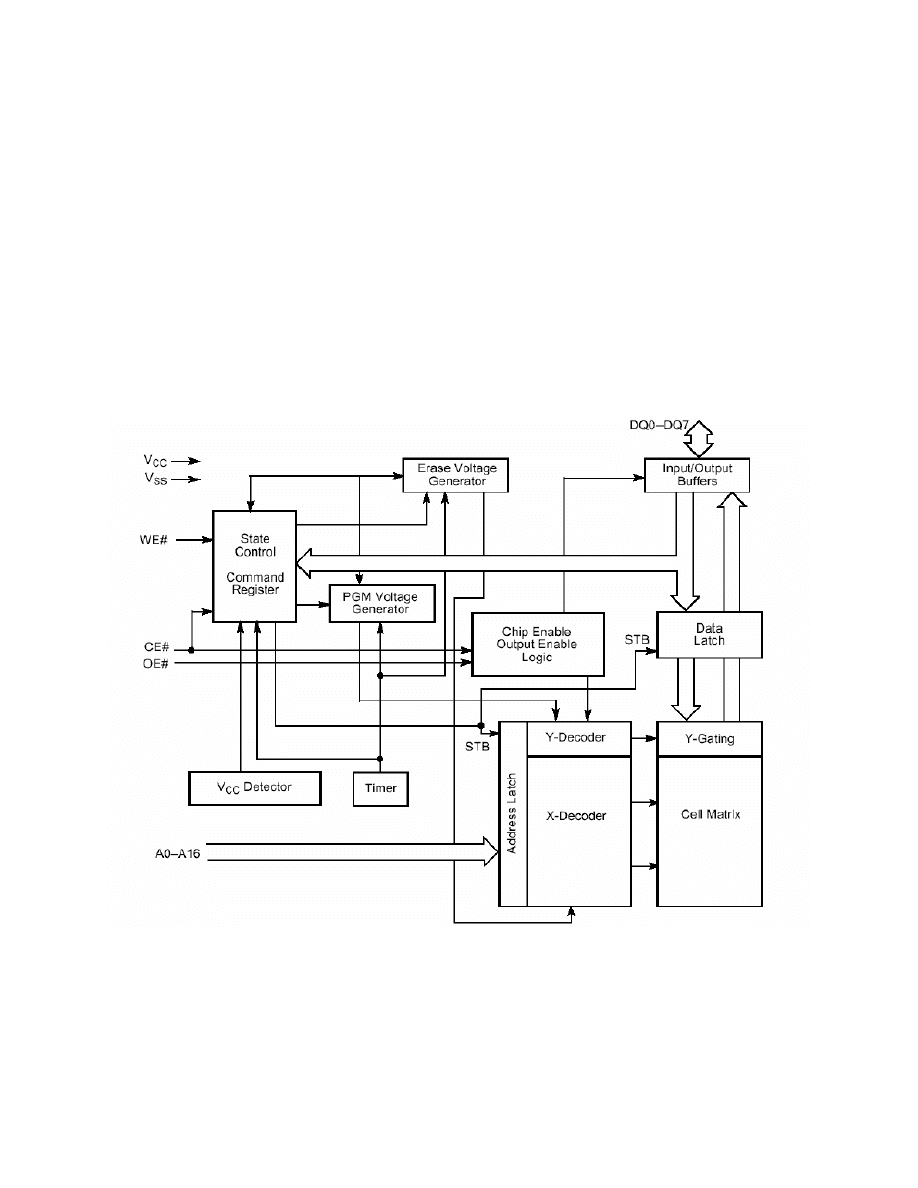

Rys. 7. Schemat blokowy pami ci Am29F010

Na rys. 7. przedstawiono schemat blokowy pami ci Am29F010. Jak wida , sk!ada si ona z

wielu bloków, z których cz % s!u y do obs!ugi procesu zapisu do pami ci (blok Cell Matrix), s

nimi generatory napi PGM Voltage Generator i Erase Voltage Generator. Prac ca!ego uk!adu

zarz dza blok State Control / Command Register. Komórki pami ci s wybierane za pomoc

uk!adu dekodera adresu. Sterowanie przep!ywem danych odbywa si

za po%rednictwem

dwukierunkowego bufora i rejestru zatrzaskuj cego oraz bloku Chip Enable / Output Enable

Logic. Rejestr komend (Command Register) sk!ada si z zatrzasków, które przechowuj komendy

z adresami i danymi potrzebnymi do wykonania komendy. Zawarto% rejestru s!u y jako wej%cia

dla „wewn trznej maszyny stanu”. Wyj%cia maszyny stanu dyktuj funkcje urz dzenia. Funkcje

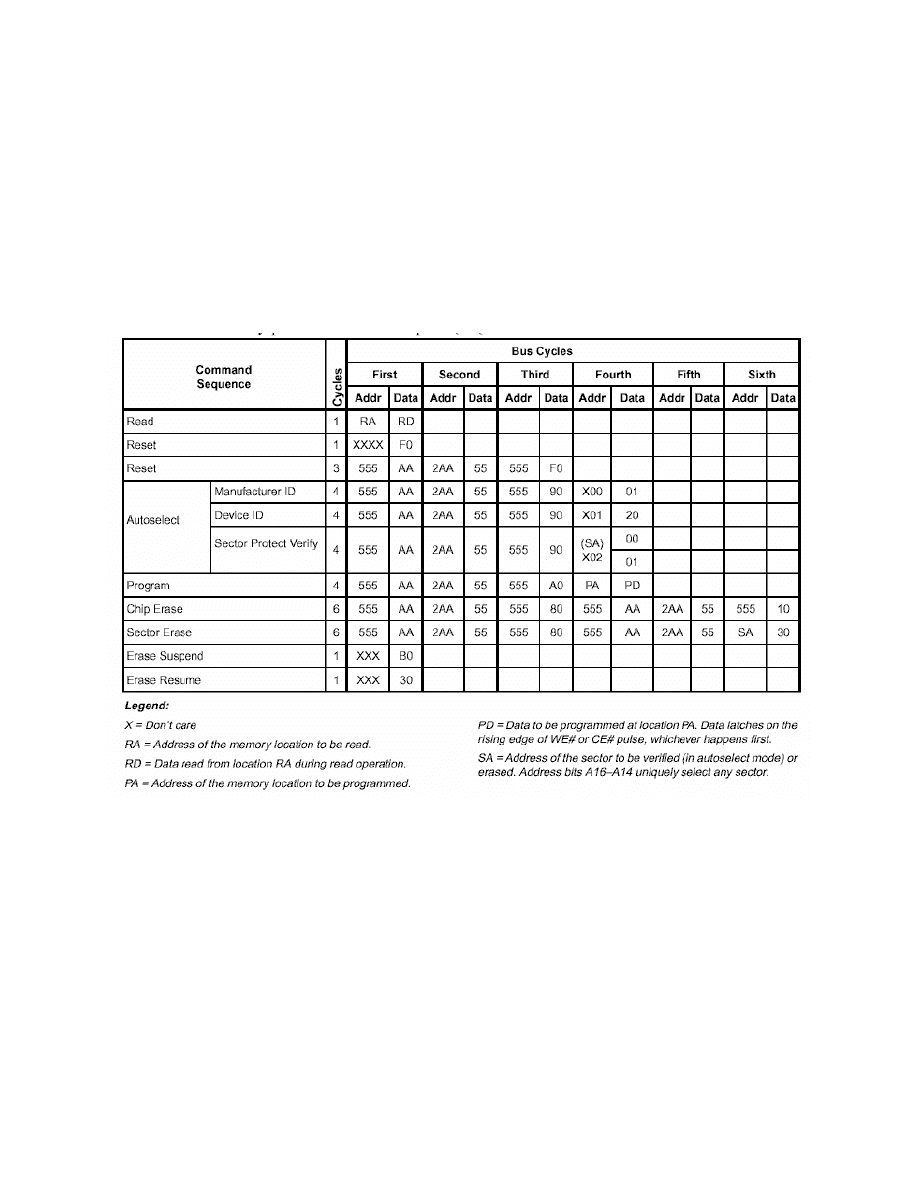

te (operacje na szynie danych) zestawiono w tabeli 2.

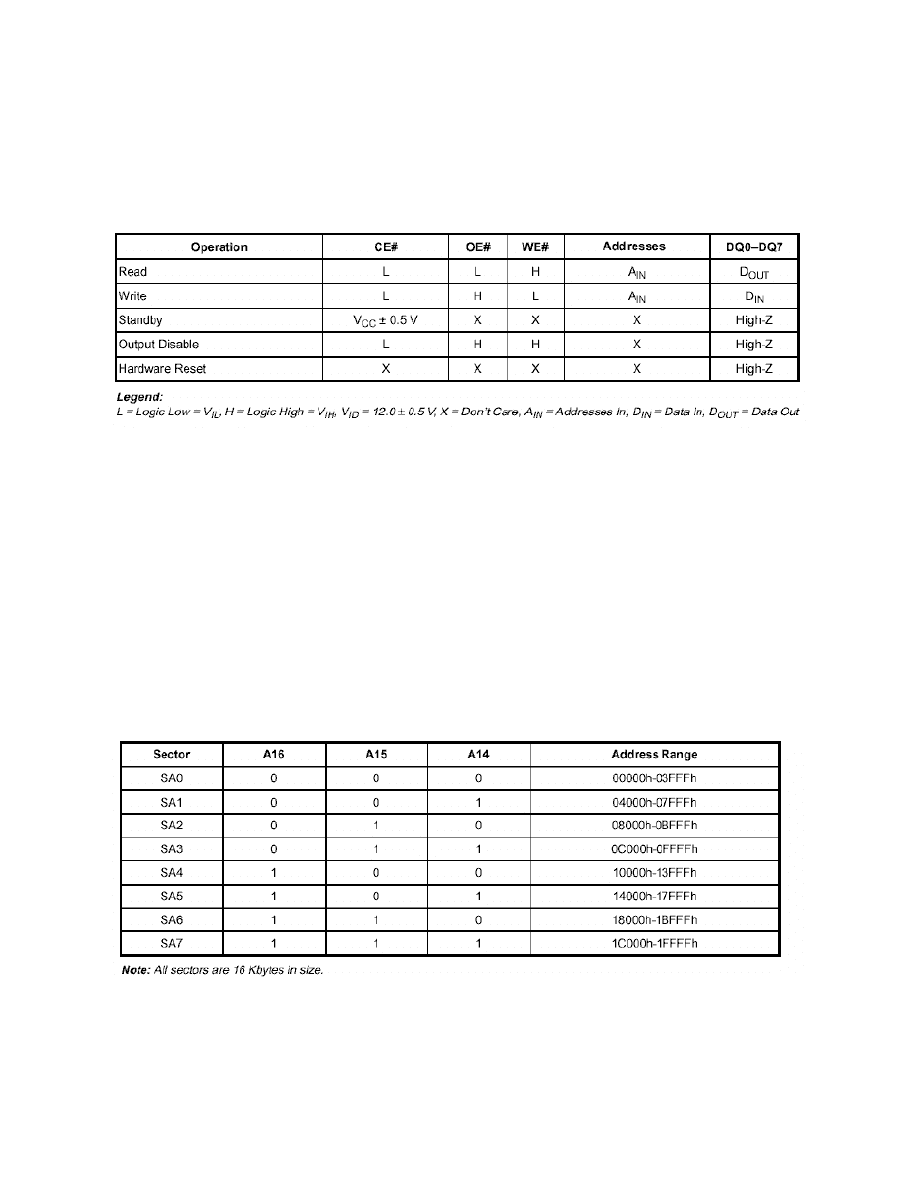

Tabela 2. Operacje na szynie danych

Aby odczyta dane z pami ci system musi zapewni niski stan linii CE# i OE#. Linia CE#

kontroluje odczyt. Linia OE# steruje buforem wyj%ciowym. Sygna! na linii WE# powinien by na

poziomie VIH. Uadna komenda nie jest wymagana w tym trybie. Jest on trybem domy%lnym po

w! czeniu napi cia zasilania. Zatem mk mo e podawa na linie adresowe A0 – A16 adresy

danych, które chce otrzyma na liniach danych DQ0 – DQ7. Urz dzenie pozostaje dost pne do

odczytu dopóki nie zmieni si zawarto% rejestru komend. Aby zapisa komend lub sekwencj

komend (które zawieraj dane programuj ce czy czyszcz ce wybrane sektory pami ci), system

musi zapewni nast puj ce stany: na liniach WE# i CE# stan niski VIL oraz na linii OE# stan

wysoki VIH . Operacja czyszczenia mo e skasowa jeden sektor, wiele sektorów lub ca!e

urz dzenie. Tablica adresów sektorów wskazuje na adres w przestrzeni jak ka dy sektor

zajmuje. „Adres sektora” to bity adresu potrzebne aby jednoznacznie zidentyfikowa sektor

(patrz tabela 3).

Tabela 3. Tablica adresów sektorów pami ci Am29F010

Podczas operacji czyszczenia lub programowania system mo e sprawdzi status operacji przez

czytanie bitów statusu DQ7-DQ0.

Pami posiada tryb autoselect, który umo liwia identyfikacj urz dzenia oraz producenta, a

tak e weryfikacj chronionych sektorów przez kody identyfikacyjne podane na DQ7-DQ0. Ten

tryb jest niezb dny dla urz dze" programuj cych, aby mog!y wykorzysta odpowiedni algorytm

programuj cy. Ten tryb mo e by tak e wykorzystany w systemie przez rejestr komend. Pami

mo na wprowadzi w tryb autoselect wydaj c odpowiedni komend (tabela 4). Zapis adresu i

danej rozkazu lub ca!ej sekwencji rozkazowej do rejestru rozkazów inicjuje wykonanie operacji.

Poprawne sekwencje rozkazowe przedstawia tabela rozkazów (tabela 4). Zapis niepoprawnych

warto%ci adresu i danych lub zapis sekwencji w nieodpowiedniej kolejno%ci przestawia pami w

tryb odczytu danych. Adres jest "zatrzaskiwany" w momencie pojawienia si opadaj cego zbocza

na linii WE# lub CE#, w zale no%ci od tego, które z tych zdarze" wyst pi jako ostatnie.

Tabela 4. Formaty polece" sterowania pami ci Am29F010

Po w! czeniu zasilania domy%lnie ustawiany jest tryb odczytu danych. Tryb ten jest ustawiany

domy%lnie tak e po wykonaniu wbudowanego algorytmu programowania (Embedded Program

Algorithm) lub wbudowanego algorytmu kasowania (Embedded Erase Algorithm). Odczyt jest

mo liwy bez u ycia jakichkolwiek rozkazów.

Rozkaz AUTOSELECT umo liwia uzyskanie dost pu do kodów producenta i pami ci, a

tak e pozwala na ustalenie, czy dany sektor jest chroniony. Na sekwencj rozkazow sk!ada si

rozkaz AUTOSELECT poprzedzony zapisem 2 cykli odblokowuj cych. Nast pnie pami

wchodzi w tryb autoselect i mo liwy jest odczyt spod ka dego adresu dowoln ilo% razy bez

inicjowania kolejnej sekwencji rozkazowej. Cykl odczytu spod adresu XX00h zwraca kod

producenta, a spod adresu XX01h kod urz dzenia. Cykl odczytu zawieraj cy adres sektora (SA) i

adres 02h zwraca 01h je%li ten sektor jest chroniony, a 00h w przeciwnym wypadku. W celu

wyj%cia z trybu autoselect do pami ci trzeba przes!a rozkaz RESET.

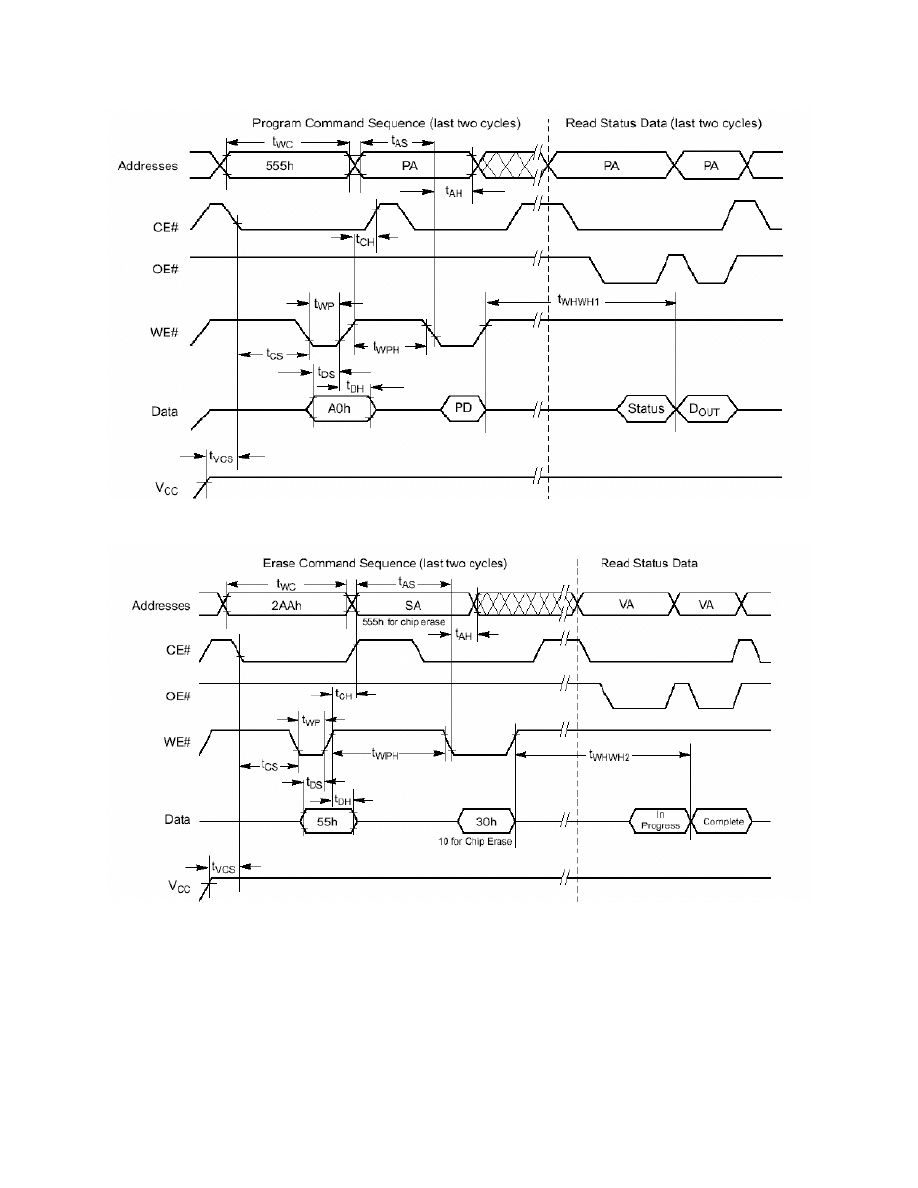

Programowanie pami ci sk!ada si z 4 cykli szyny (rozkaz PROGARM). Na sekwencj

rozkazow sk!ada si rozkaz ustawiaj cy tryb programowania poprzedzony zapisem 2 cykli

odblokowuj cych. Dane i adres s wysy!ane w nast pnej kolejno%ci. Operacja ta inicjuje

wykonanie wbudowanego algorytmu programowania. System programuj cy nie musi dostarcza

dodatkowych sygna!ów steruj cych czy taktuj cych. Urz dzenie samo generuje wewn trzne

impulsy programuj ce i weryfikuje poprawno% zaprogramowania komórki. Kiedy wbudowany

algorytm programowania zako"czy dzia!anie urz dzenie wraca do trybu odczytu danych i

zwalniany jest przerzutnik "zatrzaskuj cy" adresy. System nadrz dny mo e ustali status operacji

programowania na podstawie stanu linii DQ6 i DQ7. Wszystkie rozkazy wysy!ane do urz dzenia

podczas wykonywania wbudowanego algorytmu programowania s ignorowane. Programowanie

mo e odbywa si w dowolnej kolejno%ci i mo e przekracza granice sektorów.

Sekwencja kasowania pami ci sk!ada si 6 cykli szyny. W jej sk!ad wchodzi rozkaz

ustawienia (set-up) poprzedzony zapisem 2 cykli odblokowuj cych. Po nich nast puj kolejne 2

cykle odblokowuj ce zapis i rozkaz kasowania, który uruchamia wbudowany algorytm

kasowania. Wszystkie rozkazy wysy!ane do urz dzenia podczas wykonywania wbudowany

algorytm kasowania s ignorowane. Kiedy ten algorytm zako"czy dzia!anie urz dzenie wraca do

trybu odczytu danych i zwalniany jest przerzutnik "zatrzaskuj cy" adresy.

Na rozkaz kasowanie sektora równie sk!ada si 6 cykli szyny. Pierwszym jest rozkaz

ustawienia (set-up) poprzedzony zapisem 2 cykli odblokowuj cych. W nast pnej kolejno%ci

wysy!ane s 2 dodatkowe cykle odblokowuj ce. Potem zapisywane s : adres sektora do

kasowania oraz rozkaz kasowania. Po zapisie sekwencji rozkazowej rozpoczyna si 50Qs

przerwy. W trakcie tej przerwy mog zosta przes!ane dodatkowe adresy i rozkazy kasowania

sektorów. Za!adowanie bufora kasowania sektorów mo e si odby w dowolnej kolejno%ci.

Dowolna mo e by tak e liczba sektorów przeznaczonych do skasowania. Odst p czasu mi dzy

tymi dodatkowymi cyklami, w których przesy!ane s informacje o dodatkowych sektorach do

skasowania musi by mniejszy ni 50Qs. Jakikolwiek rozkaz wys!any podczas 50Qs przerwy

przestawia urz dzenie w tryb odczytu. System musi ponownie wys!a sekwencje rozkazow oraz

adresy dodatkowych sektorów i rozkazy. System mo e nadzorowa stan linii DQ3 w celu

sprawdzenia, czy min ! czas przerwy. Przerwa zaczyna si od narastaj cego zbocza ostatniego

impulsu w sekwencji rozkazowej na linii WE#. Wszystkie rozkazy wysy!ane do urz dzenia

podczas kasowania sektora s ignorowane. Kiedy wbudowany algorytm kasowania zako"czy

dzia!anie urz dzenie wraca do trybu odczytu danych i zwalniany jest przerzutnik "zatrzaskuj cy"

adresy. System nadrz dny mo e ustali status operacji programowania przy wykorzystaniu linii

DQ6 i DQ7.

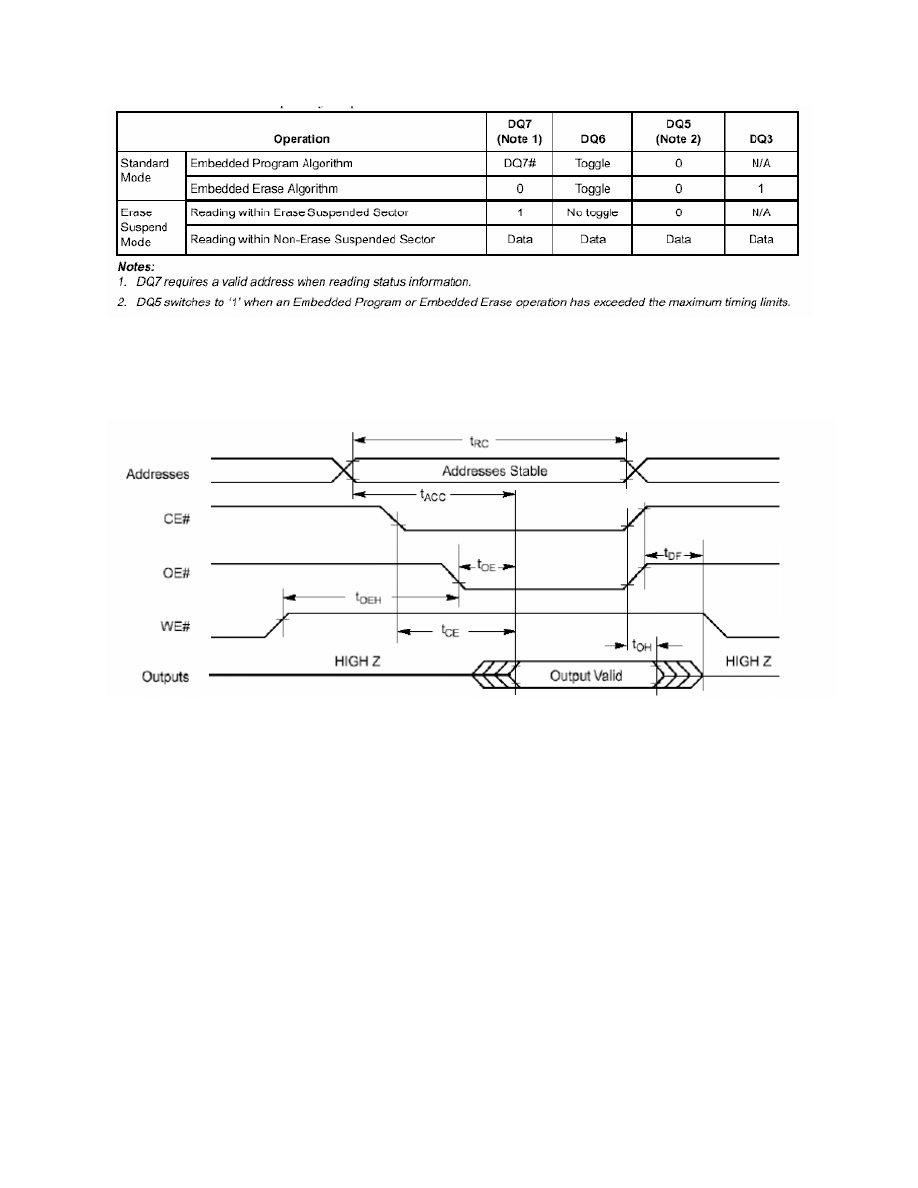

Stan operacji zapisu mo na sprawdzi wykorzystuj c linie: DQ3, DQ5, DQ6 i DQ7. Za pomoc

pinów DQ7 i DQ6 mo na sprawdzi , czy operacja programowania lub kasowania zosta!a

zako"czona (tabela 5).

Tabela 5. Status operacji zapisu

Na poni szych rysunkach pokazano przebiegi czasowe operacji odczytu (rys. 8), operacji

zapisu danej do pami ci (rys. 9) oraz operacji kasowania pami ci (rys. 10).

Rys. 8. Przebieg czasowy operacji odczytu z pami ci Am29F010

Rys. 9. Przebieg czasowy operacji programowania pami ci Am29F010

Rys. 10. Przebieg czasowy operacji kasowania pami ci Am29F010

Szeregowe pami ci EEPROM

Pami ci nieulotne EEPROM i FLASH z szeregowym wej%ciem i wyj%ciem danych s

coraz cz %ciej stosowane w mse ze wzgl du na mo liwo% programowania ich zawarto%ci w

uk!adzie, w którym pracuj (in-circuit programming). Przechowuj one dane, które po zaniku

napi cia zasilania nie mog ulec skasowaniu. Dane te najcz %ciej s wykorzystywane do

indywidualnej linearyzacji charakterystyk czujników, zbierania danych pomiarowych,

parametryzacji wbudowanych algorytmów itd. Ich zalet , oprócz niskiej ceny i ma!ych

rozmiarów obudowy, jest standardowe napi cie zasilania równe zwykle +5V lub +3V. Uk!ady te

maj

zwykle wbudowan1 przetwornic

napi cia i nie wymagaj

do programowania i

kasowania zewn trznego napi cia programuj cego. Ponadto posiadaj w!asn automatyk , tzn.

odczyt, zapis, kasowanie oraz funkcje zwi zane z ochron danych s obs!ugiwane za pomoc

odpowiednich rozkazów wprowadzanych do uk!adu i przez niego interpretowanych.

Spotykane pami ci szeregowe EEPROM maj pojemno% : 1Kbit, 2Kbit, 4Kbit, 8Kbit,

16Kbit, 32Kbit i 64Kbit. Pami jest zorganizowana bajtowo (x8), dwubajtowo (x16) i bajtowo

lub dwubajtowo (x8 lub x16 – wybór przez u ytkownika). W praktyce spotyka si trzy

podstawowe odmiany pami ci EEPROM z szeregowym wej%ciem i wyj%ciem danych:

•

uk!ady z interfejsem SPI,

•

uk!ady pracuj ce z niestandardowym protoko'em wymiany danych (przewa nie

standard przemys!owy Microwire),

•

uk!ady z interfejsem I2C.

Do sterowania pami ci EEPROM z szeregowym dost pem stosuje si powszechnie dwie metody:

•

sterowanie przy u*yciu linii portów we/wy mk (dla pami ci z niestandardowym

protoko!em wymiany danych),

•

sterowanie przez interfejs komunikacji szeregowej (dla pami ci z interfejsem SPI i

I2C).

Zasadnicz wad pami ci EEPROM jest d'ugi czas zapisu informacji, jak i kasowania uk!adu

wynosz cy typowo od 2ms do 5ms, a nawet 10ms.

Szeregowe pami ci EEPROM z interfejsem SPI

Zalet

pami ci szeregowych EEPROM z interfejsem SPI jest mo liwo% ich

bezpo%redniego pod! czenia do interfejsu SPI mk. Zatem obs!uga tych pami ci przez mk mo e

odbywa si w trybie przerwaniowym. W tym trybie mk mo e realizowa inne zadania, podczas

gdy trwa transmisja. Jc jest anga owana tylko przy odczycie lub zapisie danych do rejestru

szeregowego interfejsu SPI. Powiadomienie jc o zako"czeniu transmisji bajtu odbywa si za

pomoc przerwania od interfejsu SPI, który wpierw musi by w!a%ciwie skonfigurowany.

Kolejn zalet jest fakt, i konwersja równoleg!o-szeregowa (wpis danej przez jc do bufora

szeregowego i wys!anie jej szeregowo przez wyj%cie danych interfejsu) i szeregowo-równoleg!a

(szeregowy odczyt danej z wej%cia interfejsu do bufora i odczyt jej przez jc z tego bufora) danych

odbywa si sprz towo, a nie programowo jak ma to miejsce przy zastosowaniu popularnych

pami ci EEPROM, umówionych w kolejnym podrozdziale, z niestandardowym interfejsem

Microwire.

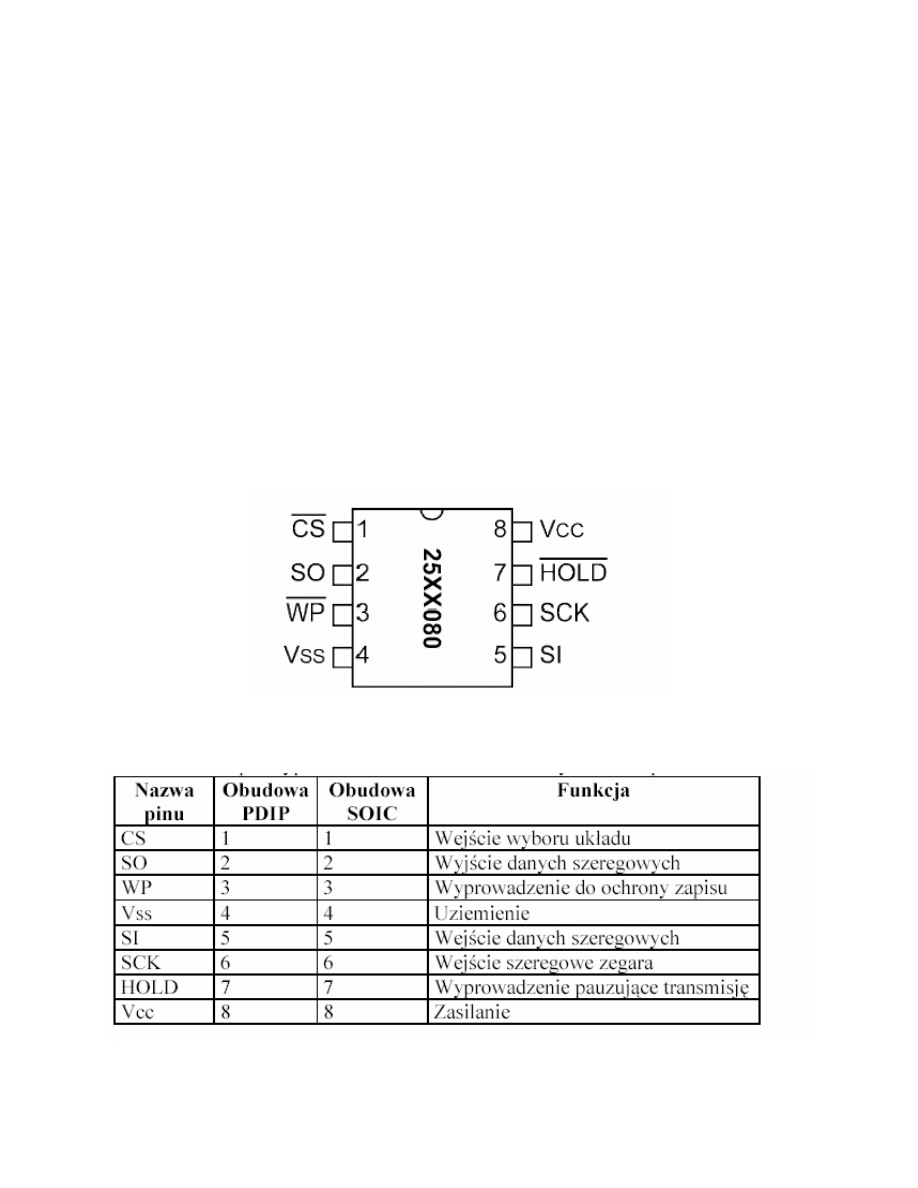

Pami ci szeregowe EEPROM i interfejsem SPI zostan przedstawione na przyk!adzie

uk!adu 25C080 firmy Microchip. Jest to 8Kbitowa pami o architekturze bajtowej (1024x8

bitów). Dost p do pami ci, jak i jej sterowanie odbywa si za pomoc interfejsu SPI, który sk!ada

si z linii: sygna! zegara SCK, sygna! danych wej%ciowych SI oraz sygna! danych wyj%ciowych

SO. Dost p do urz dzenia jest kontrolowany poprzez sygna! wyboru uk!adu CS (Chip Select).

Istnieje mo liwo% wstrzymania komunikacji z pami ci poprzez sygna! HOLD.

Uk!ad ten ma nast puj ce w!a%ciwo%ci:

•

Niski pobór mocy: pr d podczas zapisu maksymalnie 3mA, pr d podczas odczytu typowo

500QA, pr d spoczynkowy typowo 500nA.

•

Organizacja pami ci: 1024x8 bity.

•

16 bajtowa strona.

•

Czas cyklu zapisu maksymalnie 5ms.

•

Wewn trzne automatyczne cykle kasowania i zapisu.

•

Ochrona zapisu bloku: ochrona adnej,1/4,1/2 lub ca!ej tablicy.

•

Wbudowana ochrona zapisu: ochrona danych podczas w! czania/wy! czania uk!adu,

zatrzask umo liwiaj cy zapis, pin ochrony przed zapisem.

•

Sekwencyjny odczyt danych.

•

Wysoka niezawodno% : wytrzyma!o% 1M cykli kasowania/zapisu, czas przechowywania

danych > 200 lat, ochrona wej% cyfrowych przed przepi ciami typu ESD.

•

Obudowa 8-pinowa PDIP oraz SOIC (rys. 11).

Rys. 11. Wyprowadzenia uk!adu 25C080 firmy Microchip

Na rys. 11 pokazano wyprowadzenia pami ci EEPROM. Opis tych wyprowadze zebrano w

tabeli 6.

Tabela. 6. Opis wyprowadze uk adu 25C080 firmy Microchip

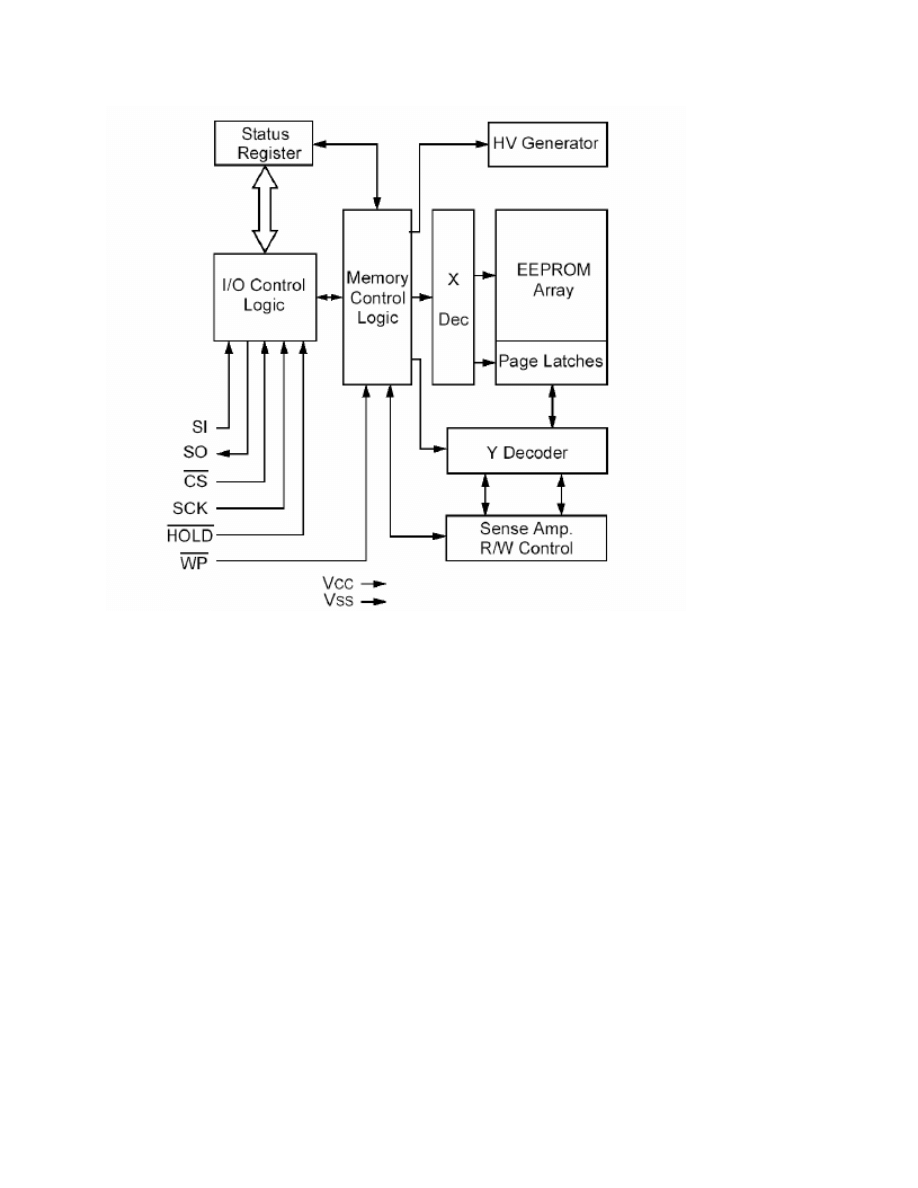

Rys. 12. Schemat blokowy uk adu 25C080 firmy Microchip

Na rys 12 pokazano schemat blokowy uk!adu 25C080. Jak wida sk!ada si on z dwóch cz %ci:

pierwsz cz % stanowi zespó! bloków zwi zanych z interfejsem SPI i sterowaniem pami ci . S

to bloki: we/wy uk!ad steruj cy (I/O Control Logic), rejestr statusu, uk!ad steruj cy pami ci

(Memory Control Logic), generator wysokiego napi cia (HV Generator), uk!ad kontroli

amplitudy przy odczycie/zapisie (Sense Amp. R/W Control). Druga cz % to pami "w!a%ciwa".

Sk!ada si ona z dekodera wierszy (X Dec) i dekodera kolumn (Y Dec), rejestru zatrzaskowego

stron (Page Latches) i matrycy komórek EEPROM (EEPROM Array).

Zastosowania i funkcje pinów uk!adu s nast puj ce:

•

Linia CS s!u y do uaktywnienia pami ci przez uk!ad nadrz dny z ni wspó!pracuj cy

(np. mk). Uaktywnienie pami ci dokonuje si poprzez wystawienie na wej%cie CS

niskiego poziomu sygna!u. Wysoki poziom na tej linii dezaktywuje uk!ad. Podczas

inicjacji b dG trwania cyklu programowania wysoki stan sygna!u CS nie powoduje

przerwania procesu zapisu/odczytu. Zostaje on doko"czony, po czym nast puje

dezaktywacja uk!adu pami ci i przej%cie w stan czuwania. W tym trybie pracy wyj%cie SO

przechodzi w stan wysokiej impedancji umo liwiaj c innym uk!adom korzystanie z

magistrali SPI. Zmiana stanu na wej%ciu CS z niskiego na wysoki po zako"czonej

sekwencji wprowadzania rozkazów do pami ci inicjuje wewn trzny cykl zapisu.

•

Wyj)cie SO jest u ywane w celu wysy!ania danych z uk!adu pami ci 25C080. Podczas

cyklu odczytu dane s

wystawiane na to wyj%cie na opadaj ce zbocze sygna!u

zegarowego.

•

Wej)cie WP wraz z bitem WPEN rejestru statusu s!u do blokady zapisu rejestru statusu

pami ci. Ochron t uzyskuje si , gdy na linii WP wystawiony jest niski poziom, za%

bitowi WPEN przypisana jest jedynka. W przypadku gdy bit WPEN jest ustawiony, to

pojawienie si niskiego poziomu na linii WP podczas sekwencji zapisu rejestru statusu

spowoduje przerwanie tej operacji. Je eli za% wewn trzny cykl zapisu zosta! rozpocz ty

wszelkie zmiany na linii WP nie wp!ywaj na kontynuacj wykonywania operacji zapisu.

Gdy bit WPEN jest wyzerowany funkcja linii WP jest nieaktywna. Ustawienie bitu

WPEN odblokowuje funkcj wyprowadzenia WP.

•

Wej)cie SI jest u ywane do szeregowego wprowadzania instrukcji, adresów oraz danych

z urz dzenia nadrz dnego do pami ci. Dane na SI zatrzaskiwane s na narastaj ce zbocze

sygna!u zegarowego.

•

Sygna' wej)ciowy SCK s!u y do synchronizacji komunikacji pomi dzy urz dzeniem

nadrz dnym, a pami ci . Narastaj ce zbocze zegara zatrzaskuje (próbkuje) dane

wprowadzane na wej%ciu SI, za% opadaj ce wystawia dane na wyj%ciu SO.

•

Wej)cie HOLD s!u y do wstrzymania transmisji do pami ci, bez konieczno%ci

powtarzania ca!ego cyklu transmisyjnego od nowa. W celu wstrzymania transmisji na

pinie HOLD powinien by stan niski w momencie, gdy sygna! zegara SCK jest równie w

stanie niskim. W innym przypadku zawieszenie transmisji zostanie wykonane przy

kolejnym przej%ciu sygna!u SCK z poziomu wysokiego do niskiego. Istotne jest, aby

uk!ad pami ci pozostawa! aktywny podczas wstrzymywania transmisji. Gdy transmisja

zostaje zawieszona linie SI, SCK oraz SO przechodz w stan wysokiej impedancji.

Wymuszenie na linii HOLD wysokiego poziomu podczas niskiego poziomu sygna!u

zegara powoduje wznowienie transmisji.

Uk!ad 25C080 zawiera 8 bitowy rejestr instrukcji. Aby uk!ad by! aktywny i przyjmowa!

rozkazy/dane na linii CS musi panowa stan niski, za% na linii HOLD stan wysoki. Aby mo na

by!o dokonywa operacji zapisu do tablicy pami ci na linii WP powinien by stan wysoki.

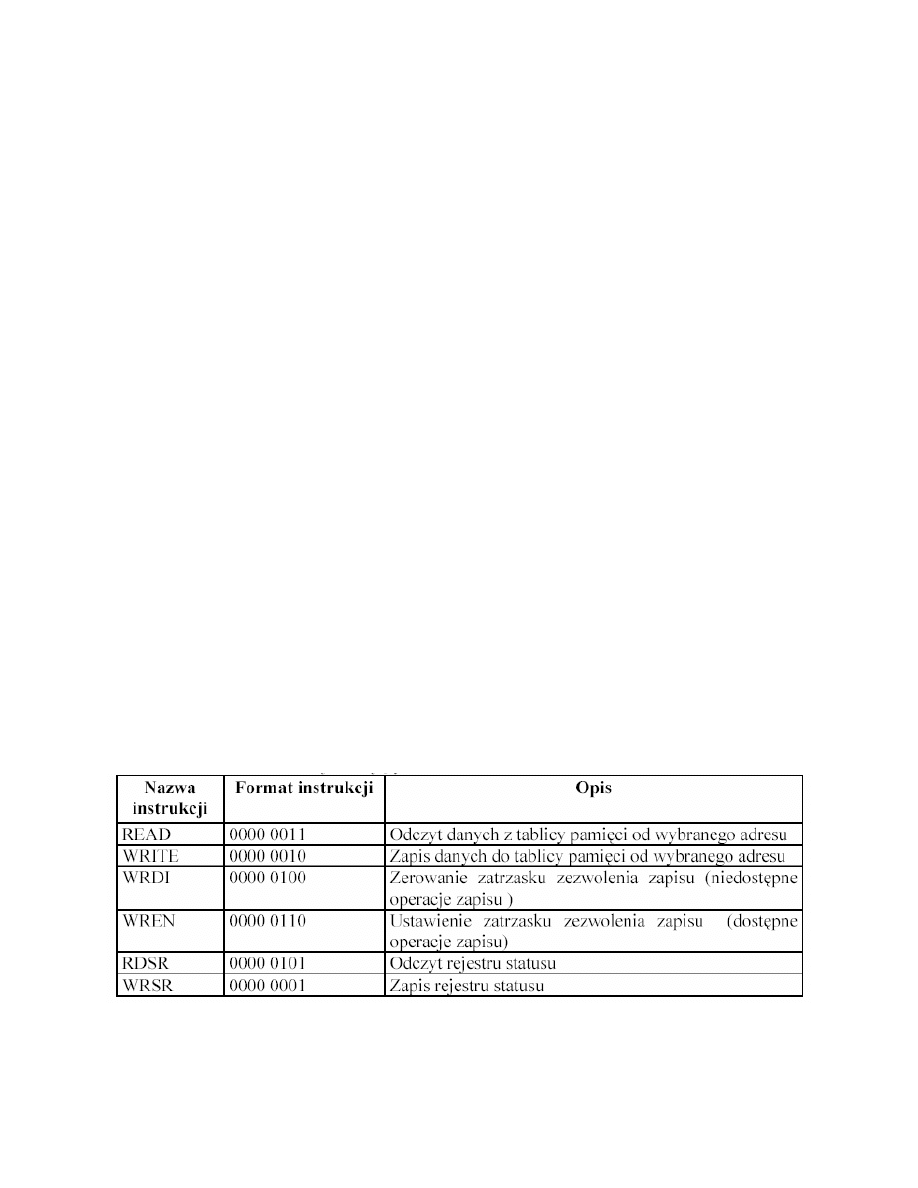

Tabela 12 zawiera list i formaty instrukcji dost pnych dla uk!adu 25C080. We wszystkich

instrukcjach, adresach czy danych pierwszy jest przesy!any najbardziej znacz cy bit MSB, a jako

ostatni bit LSB. Wszelkie instrukcje, adresy, czy dane przesy!ane s do pami ci paczkami 8-

bitowymi, co pozwala na bezpo%rednie stosowanie w tym celu interfejsu SPI mk.

Tablela 12. Zestaw instrukcji steruj cych uk adem 25C080

Dane s próbkowane na pierwsze narastaj ce zbocze sygna!u zegara SCK po wymuszeniu na linii

CS niskiego poziomu. W przypadku, gdy sygna! zegara na magistrali SPI jest wspó!dzielony

przez inne urz dzenia peryferyjne, u ytkownik mo e wprowadzi pami 25C080 w stan

wstrzymania ‘HOLD’ poprzez wymuszenie niskiego stanu na linii HOLD. Po zmianie poziomu

sygna!u na tej linii z niskiego na wysoki nast puje kontynuacja wstrzymanej transmisji.

Poni ej zestawiono opis rozkazów zawartych w tabeli 12:

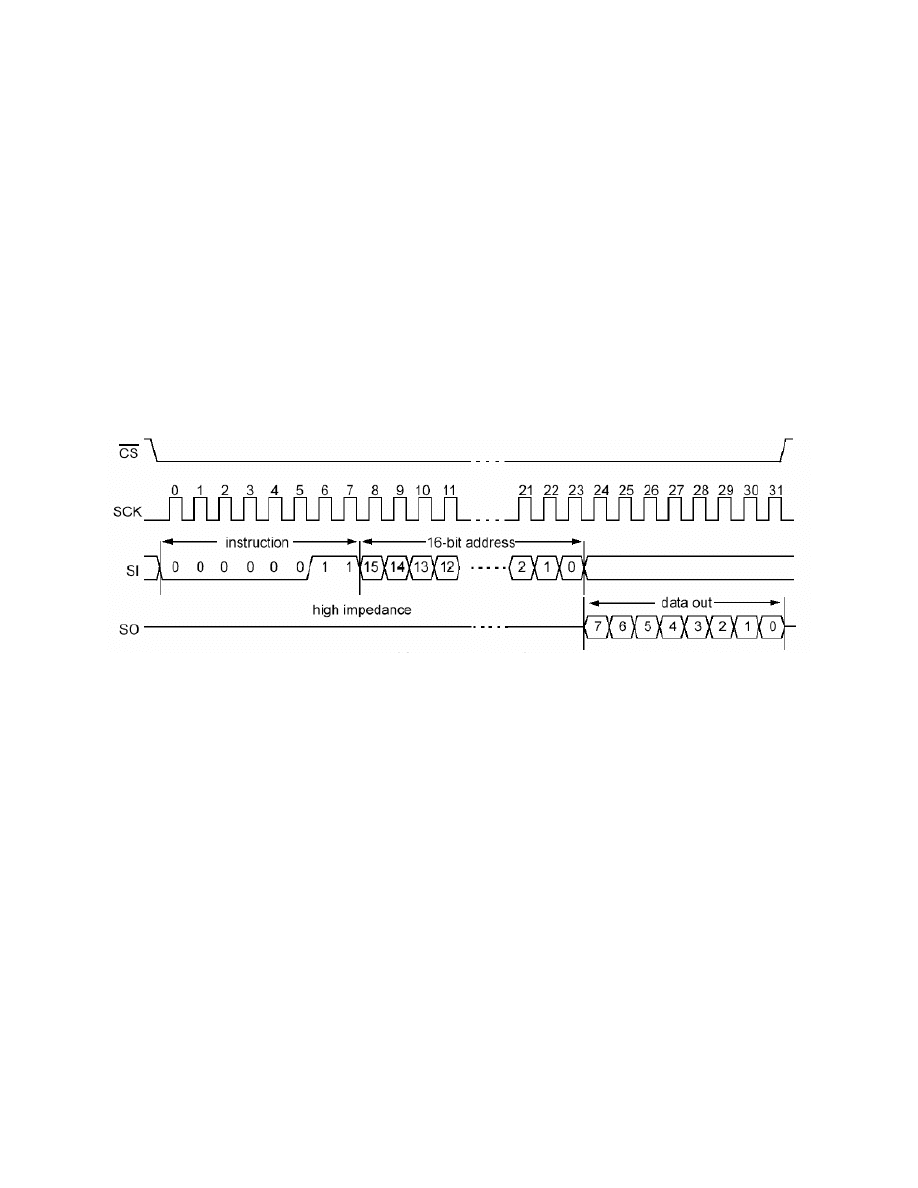

•

Sekwencja odczytu READ rozpoczyna si od wyboru pami ci poprzez wymuszenie na

linii CS stanu niskiego. Nast pnie wysy!ana jest 8-bitowa instrukcja odczytu oraz 16-

bitowy adres, gdzie sze% najbardziej znacz cych bitów adresu nie jest brane pod uwag .

Po prawid!owej transmisji instrukcji i adresu, dane umieszczone pod wybranym adresem

s wystawiane szeregowo na wyj%ciu SO. Po ka dorazowym wys!aniu bajta danych

wewn trzny wskaGnik adresu jest automatycznie inkrementowany, aby wskazywa na

kolejn dan w pami ci. Kiedy osi gnie adres 03FFH nast puje zmiana jego wskazania na

adres 0000H. Operacja transmisji sekwencji odczytu jest ko"czona na narastaj cym

zboczem sygna!u CS.

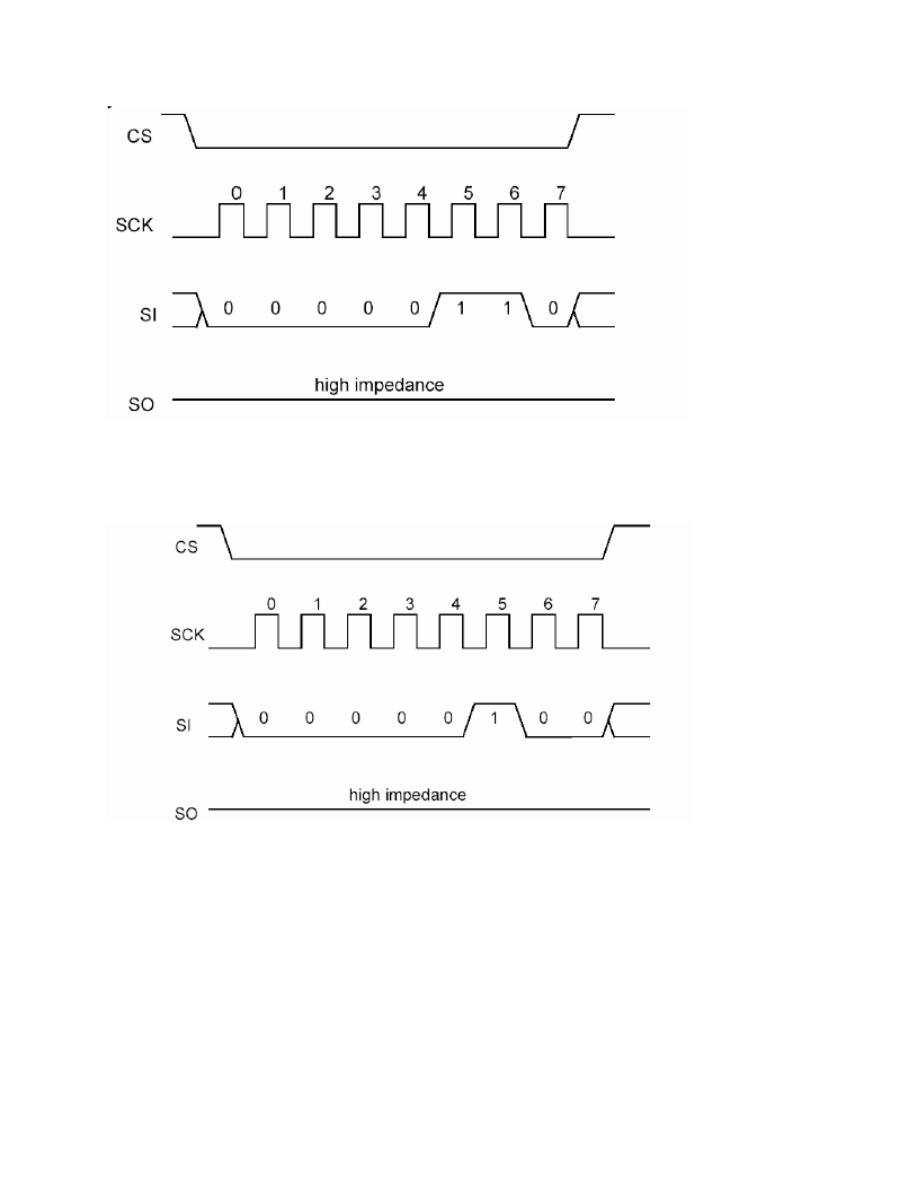

Rys. 13. Przebieg czasowy rozkazu READ

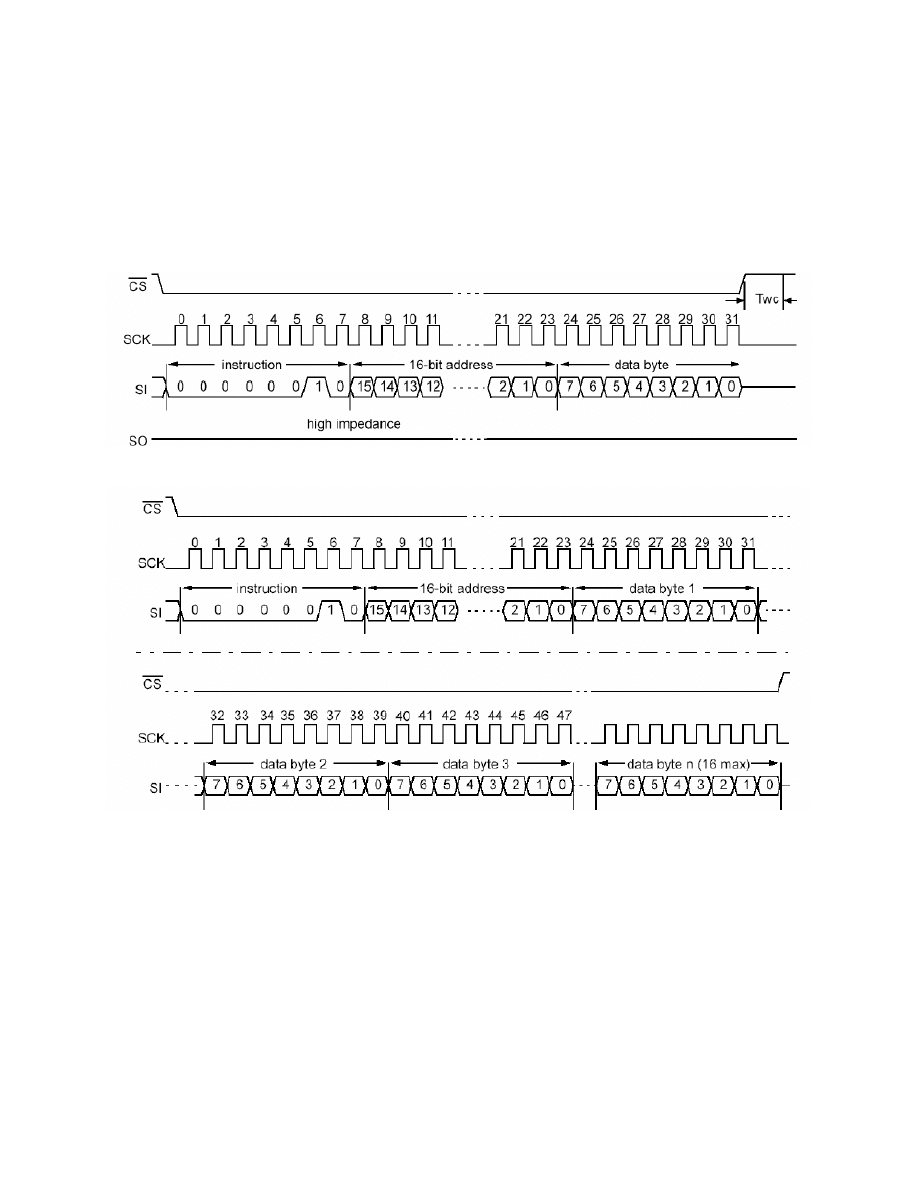

•

Przed jak kolwiek prób zapisu danych do uk!adu rozkazem WRITE, zatrzask zezwolenia

zapisu musi by ustawiony poprzez wykonanie instrukcji WREN. Sekwencja zapisu tej

instrukcji sprowadza si do wybrania uk!adu niskim poziomem sygna!u CS oraz wys!ania

kodu WREN do uk!adu. Po transmisji 8 bitów tej instrukcji, poziom sygna!u na linii CS

musi zosta ustawiony z powrotem w stan wysoki, co w rezultacie powoduje ustawienie

zatrzasku zezwolenia zapisu. Próba rozpocz cia transmisji zaraz po wys!aniu instrukcji

WREN, bez zmiany stanu sygna!u na linii CS pomi dzy tymi operacjami, nie powiedzie

si ze wzgl du na niew!a%ciwe ustawienia zatrzasku zezwolenia zapisu. W momencie

prawid!owego ustawienia tego zatrzasku, u ytkownik mo e rozpocz operacj zapisu

danych do uk!adu wcze%niej wymusiwszy na pinie CS stan niski. Sekwencja zapisu

sprowadza si do wys!ania instrukcji zapisu WRITE, 16-bitowego adresu z sze%cioma

najbardziej znacz cymi bitami nie branymi pod uwag oraz danej przeznaczonej do

zapisu pod przes!any adres. Przed wymaganym cyklem zapisu do pami ci mo e by

wys!anych 16 bajtów danych. Jedynym ograniczeniem w tym przypadku jest to, i

wszystkie bajty musz mie%ci si w obszarze jednej strony pami ci. Adres strony

zaczyna si od XXXX XXXX XXXX 0000 i ko"czy na XXXX XXXX XXXX 1111. W

przypadku kiedy wewn trzny licznik adresu osi gnie warto% graniczn , wskazuje on z

powrotem na pierwszy adres strony i nast puje nadpisywanie danych na ju wcze%niej

zachowane. Aby zako"czy sekwencj zapisu danych do tablicy pami ci sygna! na

wyprowadzeniu CS powinien zosta ustawiony w stan wysoki tu po otrzymaniu

ostatniego najmniej znacz cego bitu n-bajtowej danej. W przypadku gdy sygna! CS

zostanie wcze%niej ustawiony w stan wysoki operacja zapisu nie zostanie skompletowana.

Podczas trwania sekwencji zapisu rejestr statusu mo e by odczytywany w celu

sprawdzenia bitów WPEN, WIP, WEL, BP1 oraz BP0. Podczas trwania cyklu zapisu nie

jest mo liwy odczyt tablicy lokacji pami ci. Po zako"czeniu tego cyklu zatrzask

zezwolenia zapisu jest zerowany.

Rys14. Przebieg czasowy rozkazu WRITE dla zapisu pojedynczego bajta

Rys. 15. Przebieg czasowy rozkazu WRITE dla zapisu wielu bajtów

•

Instrukcja WREN (Write Enable) zezwala na zapis do pami ci. Jej przebieg czasowy

pokazano na rys. 16.

Rys. 5.6. Przebieg czasowy rozkazu WREN

•

Instrukcja WRDI (Write Disable) blokuje zapis do pami ci. Przebiegi czasowe tej

instrukcji przedstawiono na rys. 17.

Rys. 17. Przebieg czasowy rozkazu WRDI

•

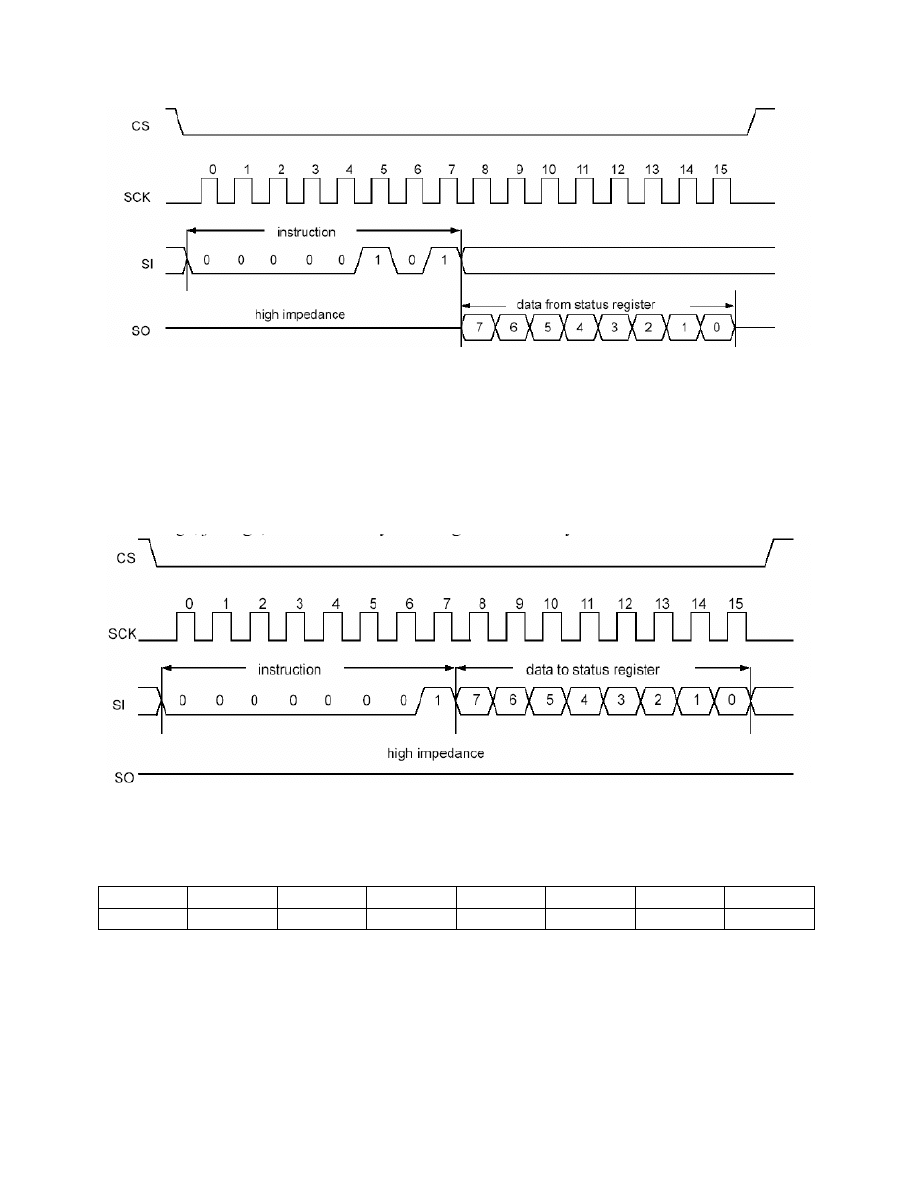

Instrukcja RDSR odczytu rejestru statusu (Read Status Register) zapewnia dost p do

rejestru statusu. Rejestr ten mo na odczyta w ka dej chwili, nawet podczas cyklu zapisu.

Rys. 18. Przebieg czasowy rozkazu RDSR

•

Instrukcja WRSR zapisu rejestru statusu (Write Status Register) pozwala

u ytkownikowi na wybór jednego z czterech poziomów ochrony tablicy pami ci

EEPROM. Odbywa si to poprzez zapis bitów BP0 i BP1 w rejestrze statusu. Tablica

pami ci podzielona jest na cztery segmenty. U ytkownik ma mo liwo% ochrony zapisu

adnego, jednego, dwóch lub wszystkich segmentów tablicy.

Rys. 19. Przebieg czasowy rozkazu WRSR

Format rejestru statusu jest nast puj cy:

7

6

5

4

3

2

1

0

WPEN

X X X BP1

BP0

WEL

WIP

gdzie:

•

Bit WIP (Write-in-Process – zapis w trakcie) wskazuje czy uk!ad pami ci jest w trakcie

operacji zapisu, czy nie. WIP =1 – pami w trakcie operacji zapisu, za% WIP =0 – adna

operacja zapisu nie jest przeprowadzana. Bit WIP jest bitem przeznaczonym tylko do

odczytu.

•

Bit WEL (Write Enable Latch – zatrzask zezwolenia zapisu) wskazuje na status zatrzasku

zezwolenia zapisu. WEL =1 – zezwolenie zapisu do tablicy, WEL =0 – zakaz zapisu do

tablicy. Stan tego bitu mo e by zawsze zmieniony poprzez polecenia WREN lub WRDI.

Bit WEL jest bitem przeznaczonym tylko do odczytu.

•

Bity BP0 i BP1 (Block Protection – ochrona bloku) informuj , który blok obecnie jest

chroniony przed zapisem (patrz tabela 5.3). Stan tych bitów jest nieulotny i mo e by

zmieniany przez u ytkownika poprzez wykonanie instrukcji WRSR.

•

Bit WPEN (Write Protect Enable – zezwolenie ochrony zapisu) jest nieulotnym bitem

dost pnym jako bit zezwalaj cy dla wej%cia WP.

BP1

BP0

Adresy Tablicy Chronione przed Zapisem

0

0

BRAK

0

1

wy sza wiartka

(0300H-03FFH)

1

0

wy sza po!ówka

(0200H-03FFH)

1

1

wszystkie

(0000H-03FFH)

Tabela 13. Znaczenie bitów BP0 i BP1

Wej%cie WP (Write Protect – ochrona zapisu) i bit rejestru statusu WPEN s!u do

sprz towej ochrony pami ci przed zapisem. Ochrona ta jest aktywna je%li wyprowadzenie WP

jest w stanie niskim za% bit WPEN =1. Dotyczy ona ochrony nieulotnych bitów rejestru statusu.

Uk!ady pami ci 25C080 zawieraj zatrzask zezwolenia zapisu. Zatrzask musi by

ustawiony przed tym, jak dowolna operacja zapisu zostanie „wewn trznie” zako"czona.

Instrukcja WREN ustawia ten zatrzask, natomiast instrukcja WRDI go zeruje. Poni ej zosta!a

przedstawiona lista warunków, pod którymi nast pi wyzerowanie zatrzasku:

•

w! czenie zasilania,

•

wykonanie instrukcji WRDI zako"czone sukcesem,

•

wykonanie instrukcji WRSR zako"czone sukcesem,

•

wykonanie instrukcji WRITE zako"czone sukcesem.

Czyli przed ka dym zapisem danych do pami ci nale y ustawi ten zatrzask instrukcj WREN.

Zastosowano nast puj ce %rodki ochrony tablicy pami ci EEPROM przed

przypadkowymi wpisami:

•

zatrzask zezwolenia zapisu jest zerowany natychmiast po w! czeniu zasilania,

•

w celu ustawienia zatrzasku zezwolenia zapisu wymagana jest odpowiednia instrukcja,

•

zatrzask zezwolenia zapisu jest zerowany zaraz po zako"czonym cyklu zapisu bajtu,

strony lub statusu rejestru,

•

sygna! na linii CS musi by ustawiony w stan wysoki po odpowiedniej liczbie cykli

zegara w celu rozpocz cia wewn trznego cyklu zapisu,

•

próba dost pu do tablicy podczas wewn trznego cyklu zapisu jest odrzucana, za%

programowanie jest nadal kontynuowane.

W tabeli 14 zestawiono stan ochrony bloków pami ci i rejestru statusu w zale no%ci od bitów

WPEN i WEL oraz stanu na linii WP.

WPEN WP WEL BLOKI

CHRONIONE BLOKI

NIECHRONIONE

REJESTR STATUSU

X

X

0

chroniony

chroniony chroniony

0

X

1

Chroniony zapisywalne

zapisywalne

1

low 1

Chroniony

zapisywalne

chroniony

X

high 1

chroniony

zapisywalne

zapisywalne

Tablica 14. Macierz Funkcjonalno%ci Ochrony Zapisu

Uk!ad pami ci 25C080 po w! czeniu zasilania przyjmuje nast puj cy stan:

•

uk!ad jest w trybie czuwania, ma!y pobór mocy CS=1,

•

zatrzask zezwolenia zapisu jest wyzerowany,

•

wyj%cie SO jest w stanie wysokiej impedancji,

•

przej%cie ze stanu wysokiego do niskiego na linii CS powoduje wej%cie uk!adu w stan

aktywny.

Wyszukiwarka

Podobne podstrony:

pamiec id 348519 Nieznany

pamiec 4 id 348531 Nieznany

alokacja pamieci id 58435 Nieznany (2)

pamieci 12 id 348557 Nieznany

pamiec komputera id 348541 Nieznany

6 Pamieci ROM RAM id 43808 Nieznany

Pamiec wewnetrzna id 348371 Nieznany

Pamieci RAM id 348388 Nieznany

pamieci 12 id 348557 Nieznany

pamiec komputera id 348541 Nieznany

Abolicja podatkowa id 50334 Nieznany (2)

4 LIDER MENEDZER id 37733 Nieznany (2)

katechezy MB id 233498 Nieznany

metro sciaga id 296943 Nieznany

perf id 354744 Nieznany

interbase id 92028 Nieznany

Mbaku id 289860 Nieznany

Probiotyki antybiotyki id 66316 Nieznany

miedziowanie cz 2 id 113259 Nieznany

więcej podobnych podstron