TECHNIKA MIKROPROCESOROWA, SEMESTR IV

CZĉĝû OGÓLNA

1.1 Podaj hierarchiĊ pamiĊci w typowym komputerze.

klasyfikacja z punktu widzenia dostĊpnoĞci - odlegáoĞci od procesora

x

rejestry

x

pamiĊü podrĊczna (notatnikowa) - cache -

czĊsto wielopoziomowa; kolejka rozkazów i najczĊĞciej

uĪywane dane i fragmenty programu; nie zawsze wystĊpuje

x

pamiĊü operacyjna -

wykonywana w róĪnych technologiach mogących wystĊpowaü razem

x

bufory pamiĊci zewnĊtrznych

x

pamiĊci dyskowe i optyczne, macierze dyskowe

x

pamiĊci taĞmowe

1.2 Jakie podstawowe rejestry wystĊpują w kaĪdym komputerze?

LR - licznik rozkazów - w momencie wykonywania rozkazu zawiera adres z którego pobrany bĊdzie kod

nastĊpnego rozkazu do wykonania, za wyjątkiem:

- polecenia skoku

- polecenia wykonania procedury

- wyjĞcia z procedury

- obsáugi przerwania

Po kaĪdym pobraniu kodu rozkazu zawartoĞü LR jest zwiĊkszana o 1.

DáugoĞü licznika rozkazów wyznacza zwykle maksymalną pojemnoĞü pamiĊci jaką moĪna bezpoĞrednio

doáączyü do mikroprocesora. Adresy pamiĊci o maksymalnej pojemnoĞci tworzą przestrzeĔ adresową uP.

SP - wskaĨnik stosu - zawiera adres pamiĊci zewnĊtrznej przeznaczonej na stos (dowolne miejsce w

pamiĊci wskazywane przez SP); pokazuje zawsze na "wierzchoáek" stosu. Przed zapisem zawartoĞü

wskaĨnika stosu jest zmniejszana o 1, natomiast po dokonaniu odczytu ze stosu, zawartoĞü SP jest

zwiĊkszana o wartoĞü odczytu.

A - akumulator - zawiera zwykle jeden z argumentów oraz jest miejscem wpisu wyniku operacji arytmetyczno

logicznych

F - rejestr wskaĨników (znaczników, warunków, flag) - zawiera informacje o przebiegu i wyniku operacji

arytmetyczno-logicznych.

2.1 Omów ogólny cykl rozkazowy

cykl rozkazowy - czas realizacji jednego rozkazu - skáada siĊ z dwóch zasadniczych faz: cyklu pobrania

rozkazu z pamiĊci oraz cyklu wykonania rozkazu. JeĪeli w trakcie wykonywania tych operacji wystąpi

przerwanie i speánione są warunki by to przerwanie obsáuĪyü, to trzecią fazą cyklu rozkazowego (po

zakoĔczeniu cyklu wykonywania rozkazu) jest obsáuga przerwania.

2.2 Co to jest i w którym miejscu wystĊpuje przerwanie oraz na czym polega jego obsáuga?

Przerwanie jest to sygnaá o niespodziewanym zdarzeniu, pojawiający siĊ w dowolnej chwili i zapamiĊtywany

w rejestrze przyjĊü przerwaĔ.

Przerwanie zostanie obsáuĪone jeĪeli speánione są warunki:

- odblokowana obsáuga przerwaĔ

- aktualnie nie jest wykonywana obsáuga przerwania o wyĪszym priorytecie

Obsáuga przerwania jest procedurą skáadającą siĊ z trzech zasadniczych kroków:

Z nóĪki wejĞciowej pobierane jest napiĊcie i porównywane z napiĊciem odniesienia w obrĊbie macierzy

kondensatorów. KaĪda konwersja A/D skáada siĊ z 8 operacji porównania, począwszy od najbardziej

znaczącego bitu. Wyniki kolejnych konwersji zapisywane są w odpowiednich rejestrach wynikowych. àącznie

moĪna dokonaü przetworzenia 16 sygnaáów analogowych: 8 wejĞciowych, 4 wewnĊtrznych punktów

odniesienia i 4 rezerwy.

Cztery tryby pracy:

x

4 kolejne konwersje w kanale pojedynczym

x ciągáa konwersja w kanale pojedynczym

x

po jednym przetwarzaniu w czterech kanaáach

x ciągáa konwersja w 4 kanaáach

PROCESORY SIECIOWE

38. Porównaj ukáady typu ASIC z procesorami typu NP.

Procesory sieciowe to wyspecjalizowane ukáady scalone, które pracują duĪo szybciej niĪ ukáady CPU

ogólnego przeznaczenia, a jednoczeĞnie moĪna je elastycznie programowaü, co nie jest moĪliwe w

przypadku ukáadów typu ASIC (Application Specific Integrated Circuits). Ukáady ASIC pracują co prawda

bardzo szybko, ale potrafią wykonywaü tylko jedno okreĞlone zadanie lub pewien ograniczony zestaw

zadaĔ, zgodnie z zaprojektowanymi poáączeniami i architekturą.

Do tej pory urządzenie sieciowe oparte na ukáadzie (lub ukáadach) ASIC byáo przygotowane do

realizowania konkretnego zadania (np. odbieranie pakietów i przekazywanie ich do odpowiedniego portu).

Konstrukcja takiego urządzenia i jego wewnĊtrzne poáączenia nie pozwalają mu realizowaü innych zadaĔ.

Procesory sieciowe dziĊki swojej konstrukcji pracują nieporównywalnie elastyczniej niĪ klasyczne ukáady

scalone typu ASIC - moĪna je w dowolny sposób zaprogramowaü, a co za tym idzie szybko modyfikowaü i

przystosowywaü do nowego Ğrodowiska pracy. Zaprojektowanie (i wdroĪenie do produkcji) tradycyjnego

ukáadu ASIC trwa ok. 18 miesiĊcy, a wiĊc bardzo dáugo. W przypadku procesorów sieciowych nie trzeba

czekaü póátora roku na pojawienie siĊ nowego modelu np. przeáącznika, wystarczy zmodyfikowaü ten

uĪywany, instalując w jego pamiĊci kolejną wersjĊ oprogramowania. Samo programowanie NP nie jest

trudnym zadaniem - moĪna uĪyü znanego jĊzyka C.

Dáugi cykl projektowy ukáadów ASIC nie pozwala speániü aktualnych oczekiwaĔ rynku i powoduje

szybkie "starzenie moralne" produktu. Poza tym ukáady specyfikowane produkowane są w maáej iloĞci, a do

ich zaprojektowania i konfiguracji potrzeba wielu wyspecjalizowanych inĪynierów, co znacznie podnosi ich

cenĊ. WiĊksze jest równieĪ ryzyko wystąpienia báĊdów, poniewaĪ ukáady ASIC moĪna przetestowaü dopiero

po ich wykonaniu, a wprowadzenie poprawki wymaga projektowania ukáadu od podstaw. ElastycznoĞü,

uniwersalnoĞü i programowalnoĞü procesorów sieciowych pozwala na eliminacjĊ wszystkich z tych wad. Ich

wysoka wydajnoĞü zapewnia ponadto wykonanie záoĪonych operacji, takich jak przetwarzanie gáosu.

Jedyną niedogodnoĞcią w stosunku do ukáadów ASIC jest brak standardów okreĞlających podstawowe

cechy architektury procesora sieciowego. Pierwsze programowalne procesory sieciowe weszáy na rynek

zaledwie kilkanaĞcie miesiĊcy temu, dlatego podaĪ tego rodzaju ukáadów scalonych jest jeszcze bardzo

maáa.

39. Podaj sposoby konfiguracji procesorów NP. w systemach telekomunikacyjnych.

Procesory sieciowe to wyspecjalizowane ukáady scalone, które moĪna elastycznie programowaü.

Charakteryzują siĊ tym, Īe potrafią wykonywaü szereg skomplikowanych funkcji, które obsáugują róĪnego

rodzaju procesy sieciowe: klasyfikowanie, modyfikowanie i transmitowanie danych, buforowanie i

kolejkowanie danych, profilowanie pakietów, planowanie zadaĔ sieciowych, bezpieczeĔstwo i szyfrowanie

danych, zarządzanie sprzĊtem sieciowym, kartami sieciowymi itp.

x

scentralizowane - wielu uĪytkowników i terminali w jednej maszynie - superkomputerze typu mainframe

x

rozproszone - komputery PC lub stacje robocze i serwery

x

sieciowe - sieü lokalna lub globalna z klientami lub serwerami

architektura systemu = sposób implementacji modelu przetwarzania - konfiguracja sprzĊtu i oprogramowania

7. Co to jest proces i na czym polega przetwarzanie wspóábieĪne?

przetwarzanie wspóábieĪne - biorą w nim udziaá co najmniej 2 procesy, które mogą ze sobą

wspóápracowaü lub rywalizowaü; programy procesów wykonują siĊ "równolegle", wspóádzieląc zasoby

(procesor, pamiĊü, komunikacja). Jądro szereguje kolejnoĞü dostĊpu do procesora, a funkcje jądra

umoĪliwiają interakcjĊ. Dwa rodzaje podziaáu czasu procesora: ze staáym podziaáem czasu lub sterowanie

priorytetami procesów i zdarzeniami.

8. Do czego sáuĪy i jak dziaáa mechanizm stronicowania?

Stronicowanie sáuĪy do zarządzania i ochrony pamiĊci operacyjnej, eliminując jej fragmentacjĊ.

Mechanizm segmentacji polega na wydzieleniu w pamiĊci operacyjnej (fizycznej) jednakowej wielkoĞci

ramek, a w pamiĊci logicznej stron, tej samej wielkoĞci co ramki. Translacja adresu logicznego o postaci

[strona:offset] na adres fizyczny odbywa siĊ za pomocą tablicy stron, zawierającej numery ramek. Numer

strony wskazuje miejsce pozycji w tablicy stron, a pozycja w tej tablicy wskazuje numer ramki. W ten sposób

programy mają adresy logiczne uáoĪone w sposób ciągáy, natomiast fizycznie mogą byü rozrzucone w

pamiĊci operacyjnej. DziĊki temu ramki zwolnione po zakoĔczeniu dziaáania jednego z programów mogą byü

zapeánione nowymi programami.

9. Do czego sáuĪy i jak dziaáa mechanizm segmentacji?

Segmentacja sáuĪy do zarządzania i ochrony pamiĊci operacyjnej (jest jednym ze sposobów eliminacji

jej fragmentacji). Mechanizm segmentacji polega na wydzieleniu w programie kolejnych bloków,

umieszczonych w odpowiadających im jednostkach logicznych (segmentach), na które podzielona jest

pamiĊü operacyjna. Posáugujemy siĊ segmentem stosu, segmentem danych, segmentem kodu (programu) i

segmentem dodatkowym. Adresy początkowe segmentów zapisane są w odpowiednich rejestrach w

mikroprocesorze. W mikroprocesorze 16-bitowym dostĊp do informacji zawartych w segmencie polega na

zsumowaniu 16-bitowego adresu efektywnego z przesuniĊtą o 4 bity zawartoĞcią odpowiedniego rejestru

segmentu, tworząc 20-bitowy adres fizyczny, wysyáany na magistralĊ adresową. Odbywa siĊ to za pomocą

deskryptorów adresów. Deskryptory aktualnie uĪywanych segmentów zawarte są w pamiĊci podrĊcznej, aby

translacja adresu wirtualnego na adres fizyczny nie wymagaáa kaĪdorazowo dodatkowego odwoáania do

pamiĊci operacyjnej.

Zalety segmentacji:

x umoĪliwia oddzielenie programu od stosu i danych, są one umieszczone niezaleĪnie w pamiĊci

x umoĪliwia przesuwanie programu i danych w pamiĊci fizycznej, poniewaĪ adres logiczny jest to adres

wzglĊdny, liczony wzglĊdem początku segmentu

x

uáatwia ochronĊ i zarządzanie pamiĊcią przy pracy wieloprogramowej

10. Porównaj szeregową transmisjĊ synchroniczną i asynchroniczną w ogólnym przypadku

W transmisji asynchronicznej:

x

przy braku informacji linia jest w stanie 1

x znaki n-bitowe przesyáane są w tzw. ramkach. W zaleĪnoĞci od sposobu kontroli przesyáany znak moĪe

mieü dáugoĞü od 5 do 8 bitów

x

bit startu sáuĪy do uruchomienia procedury synchronizacji bitowej

W mikrokontrolerze M68HC11 mamy 21 Ĩródeá przerwaĔ: 6 niemaskowalnych i 15 maskowalnych.

Przerwania niemaskowalne mają wyĪszy priorytet, przy czym najwaĪniejsze są te związane z wystąpieniem

sygnaáu RESET. Priorytety przerwaĔ maskowalnych mogą byü zmieniane, lub moĪna zablokowaü przyjĊcie

niektórych. Zazwyczaj wyĪszy priorytet mają przerwania wymagające dáuĪszego czasu obsáugi. Obsáuga

przerwania maskowalnego nie moĪe byü wstrzymana przez przerwanie o wyĪszym priorytecie.

33. Opisz zachowanie siĊ buforów nadajnika i odbiornika oraz rejestrów sterujących podczas

realizacji transmisji asynchronicznej w M68HC11

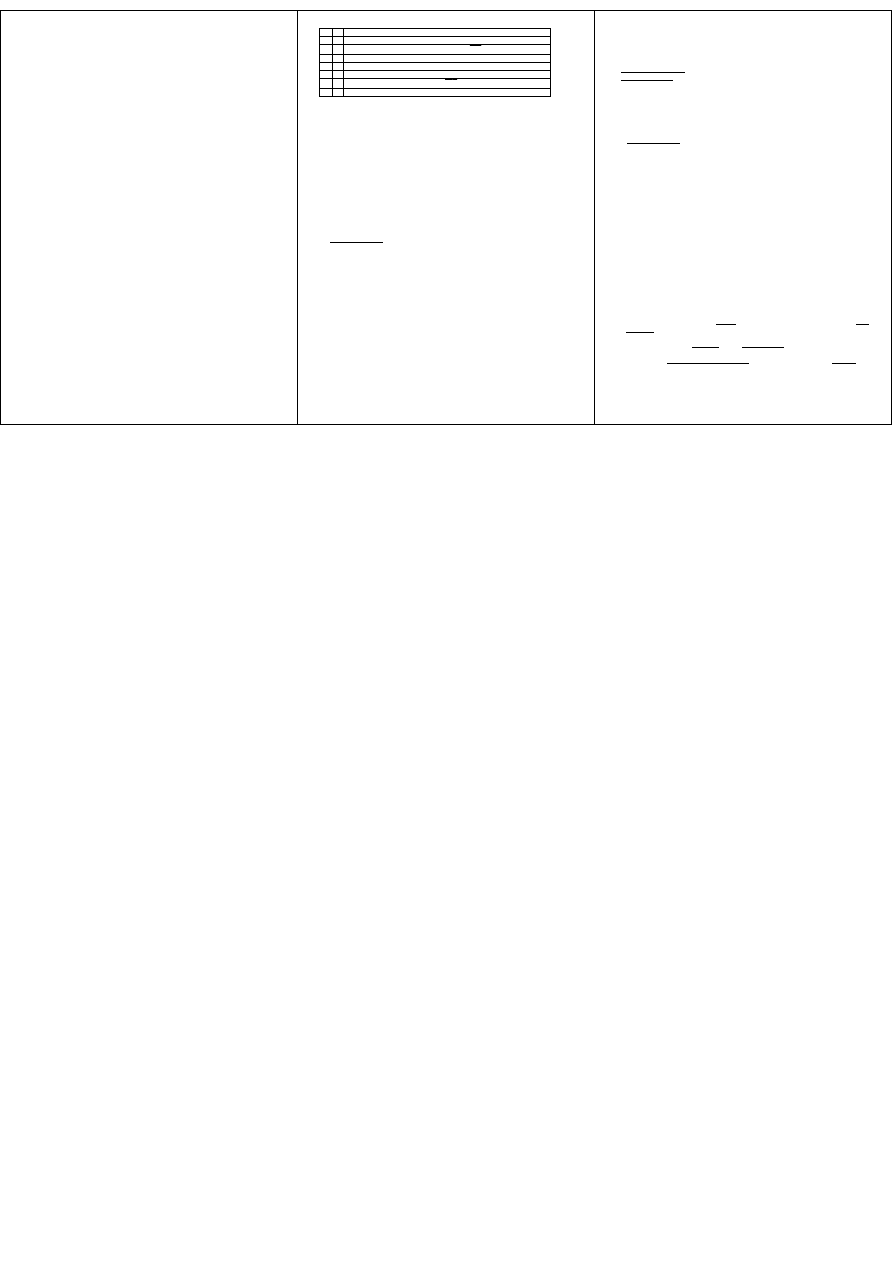

W ukáadzie transmisji asynchronicznej SCI uĪywane są nastĊpujące rejestry:

x

SCDR - rejestr równolegáy (bufor) danych - do niego wprowadzamy dane do nadania lub pobieramy z

niego dane odebrane

x Szeregowo-równolegáy rejestr przesuwający - z niego są wyprowadzane znaki do linii, lub gromadzi

bity odbieranego znaku (jest dáuĪszy od buforu danych

o bity startu, stopu i bit 9-ty)

x

SCCR1 - pierwszy rejestr sterujący - sáuĪy do wyboru trybu Wakeup, dáugoĞci sáowa (8 lub 9 bitów)

oraz przechowuje 9-ty bit danych

x

SCCR2 - drugi rejestr sterujący - wysyáa przerwĊ (break - 10 lub 11 zer), odblokowuje nadawanie,

odbieranie, funkcjĊ Wakeup i przerwania

x

SCSR - rejestr stanu - statusowy

x

BAUD - rejestr do ustawiania dzielnika prĊdkoĞci transmisji (szybkoĞci bodowej)

Nadawanie:

Po wpisaniu danej do rejestru SCDR sterowanie czeka aĪ ostatni bit poprzedniego nadawanego znaku

opuĞci rejestr przesuwny. Wówczas nastąpi przepisanie danej z rejestru SCDR do rejestru przesuwnego,

ewentualnie przepisanie dziewiątego bitu (T8) danej z rejestru SCCR1 oraz uzupeánieniem bitu startu i

stopu. Tak sformatowany znak jest wysyáany w liniĊ bit po bicie, zgodnie z taktem zegara wyznaczającego

prĊdkoĞü transmisji. Przerwania bĊdą sygnalizowane, gdy odblokowane jest przyjmowanie przerwaĔ

nadajnika (TIE = 1) w rejestrze SCCR2 oraz gdy ustawią siĊ bity w rejestrze statusowym:

- bit TDRE - rejestr danych zostaá opróĪniony i jest gotowy na przyjĊcie nastĊpnego znaku (Transmit Data

Register Empty) lub

- bit TC - ostatni bit znaku opuĞciá rejestr przesuwny i nadajnik staje siĊ bezczynny (Transmit Complete)

Odbieranie:

Podczas odbioru rejestr przesuwny gromadzi bity odbieranego znaku (próbkowanie zegarem o 16-krotnie

wiĊkszej prĊdkoĞci) i po skompletowaniu znaku usuwa bity startu i stopu a bity danych przepisuje do rejestru

SCDR i ewentualnie wykorzystuje 9-ty bit danych do realizacji funkcji "budzenia" odbiornika. Sygnalizuje

ewentualne báĊdy, ustawiając bity w rejestrze statusowym:

- OR - nadpisanie danej nie przeczytanej w SCDR

- NF - zakáócenia (Noise Flag)

- FE - wykrycie wartoĞci 0 na pozycji bitu stopu (Framing Error)

- IDLE - stan bezczynnoĞci linii

- RDRF - znak gotowy do odczytu w rejestrze SCDR (Receive Data Register Full)

Przerwania są generowane gdy odblokowane są przerwania odbiornika (RIE = 1) w rejestrze SCCR2 oraz

zostaną ustawione bity statusowe RDRF lub OR lub IDLE.

34. Do jakich celów moĪna wykorzystaü dziewiąty bit danych w transmisji asynchronicznej w

M68HC11?

9-ty bit danych ustawiany w pierwszym sáowie statusowym SCCR1 moĪe sáuĪyü do:

READY = 1. W ten sposób adres i sygnaáy zapisu/odczytu mogą byü podawane na magistrale na dowolnie

dáugi odstĊp czasu.

14. WyjaĞnij jakie funkcje peánią sygnaáy HOLD oraz HLDA doprowadzone do mikroprocesora I8080

HOLD (we) - sygnaá Īądania wstrzymania realizacji cyklu rozkazowego i zwolnienia magistral

HLDA (wy) - sygnaá potwierdzenia wstrzymania realizacji cyklu rozkazowego

W celu zrealizowania bezpoĞredniego przesáania danych miĊdzy pamiĊcią a urządzeniami zewnĊtrznymi, z

pominiĊciem mikroprocesora, sterownik DMA musi zaĪądaü od uP zwolnienia magistral systemu. SáuĪy do

tego celu wejĞcie HOLD - podanie stanu 1 na to wejĞcie powoduje wstrzymanie cyklu rozkazowego i

wprowadzenie magistral w stan wysokiej impedancji. Wstrzymanie cyklu rozkazowego jest potwierdzane

sygnaáem HLDA. ZnikniĊcie sygnaáu HOLD powoduje wznowienie cyklu rozkazowego mikroprocesora.

15. Jaką rolĊ peáni ukáad 8228 w systemie mikroprocesorowym 8080?

8228 - sterownik magistrali systemowej - w pierwszej fazie cyklu rozkazowego pobiera od procesora

sáowo statusowe i na jego podstawie generuje sygnaáy, które sterują wszystkimi ukáadami doáączonymi do

magistrali systemowej (szyny sterującej):

x -MEMR

-

sygnaá odczytu z pamiĊci

x -MEMW

-

sygnaá zapisu do pamiĊci

x -IOR

-

sygnaá odczytu z buforów wejĞcia/wyjĞcia

x -IOW

-

sygnaá zapisu do buforów wejĞcia/wyjĞcia

x

-INTA - potwierdzenie przyjĊcia przerwania przez uP

sáowo statusowe - zawiera informacjĊ o operacji, która bĊdzie wykonywana w aktualnym cyklu rozkazowym

16. ObjaĞnij znaczenie bitów rejestru wskaĨników procesora

WskaĨniki w rejestrze F są ustawiane w wyniku operacji arytmetycznych, logicznych lub w sposób jawny. W

procesorze 8086 rejestr wskaĨników (znaczników, flag) jest 16-bitowy, ale znaczenie mają tylko podane niĪej

bity. W przypadku procesora 8080 rejestr znaczników jest 8-bitowy i ustawianych jest 5 piĊü flag.

D

11

O

Overflow - przekroczenie zakresu - sygnalizuje nadmiar przy operacjach na liczbach ze znakiem

D

10

D

Direction - kierunek transmisji - okreĞla czy rozkazy operujące na ciągach sáów powodują

zwiĊkszenie czy zmniejszenie zawartoĞci wskaĨników

D

09

I

Interrupt Enable - zblokowanie/odblokowanie przerwania

D

08

T

Trap - puáapka - umoĪliwia krokowe wykonywanie programu, tj. po wykonaniu kaĪdego rozkazu jest

zgáaszane przerwanie

D

07

S

Sign - znak - ustawiany gdy wynik jest ujemny

D

06

Z

Zero - ustawiany gdy wszystkie bity wyniku są zerami

D

04

A

Auxiliary Carry - przeniesienie pomocnicze - ustawiany przy operacjach na 4-bitowych liczbach w

kodzie BCD

D

02

P

Parity - parzystoĞü - ustawiany gdy waga mniej znaczącego wyniku jest parzysta

D

0

C

Carry - przeniesienie przy dodawaniu i jego negacja (poĪyczka) przy odejmowaniu

Rejestr wskaĨników w mikrokontrolerze M68HC11 - CCR (Condition Code Register):

D

11

S

Stop Disable - blokada moĪliwoĞci zatrzymania procesora

D

10

X

blokada przerwaĔ niemaskowalnych

D

09

H

Half Carry from bit 3 to 4

1. zapamiĊtanie na stosie Ğladu programu (co najmniej licznika rozkazów, ewentualnie pozostaáych rejestrów

za wyjątkiem wskaĨnika stosu) i przejĞcie do programu obsáugi przerwania wskazanego przez wektor

przerwania (wskazujący miejsce w pamiĊci operacyjnej zawierające adres podprogramu obsáugi przerwania)

2. wykonanie podprogramu obsáugi przerwania i (najczĊĞciej) odblokowanie moĪliwoĞci przyjmowania

przerwaĔ

3. powrót z obsáugi przerwania do miejsca przerwania programu gáównego - automatyczne odtworzenie

zapamiĊtanego Ğladu programu

3. Co to jest adres efektywny? Co oznaczają tryby adresowania: rejestrowy, poĞredni, indeksowy?

x

adres efektywny argumentu rozkazu to ostateczna lokalizacja tego argumentu w pamiĊci komputera

x

tryby adresowania (modyfikacje w kodzie rozkazu) okreĞlają miejsce gdzie jest umieszczony adres

argumentu lub wskazują sposób obliczania adresu efektywnego:

- tryb rejestrowy - za kodem operacji wskazywany jest rejestr (wskaĨnik danych), zawierający adres

miejsca pamiĊci, gdzie znajduje siĊ argument (jedna z odmian trybu poĞredniego)

- tryb poĞredni (pamiĊciowy) - adres w kodzie rozkazu wskazuje miejsce pamiĊci zawierające adres

argumentu

- tryb indeksowy - adres argumentu to suma zawartoĞci rejestru indeksowego i przesuniĊcia w kodzie

rozkazu

4. Opisz tryb adresowania poĞredniego indeksowego i indeksowego poĞredniego

x poĞrednie indeksowe: adres argumentu to suma adresu bazowego wskazanego przez adres poĞredni w

kodzie rozkazu i zawartoĞci rejestru indeksowego I

Adres = (adres poĞredni) + (I)

x indeksowe

poĞrednie: adres argumentu jest wskazany przez sumĊ zawartoĞci rejestru indeksowego i

adresu poĞredniego w kodzie rozkazu; tzn. najpierw odbywa siĊ sumowanie adresu poĞredniego z

zawartoĞcią rejestru indeksowego, a potem wyciąganie danej z pamiĊci

Adres = (adres poĞredni + I)

5. Co to jest przetwarzanie i jakie znasz typy przetwarzania?

przetwarzanie = wykonywanie programu uĪytkownika na komputerze

przetwarzanie = uĪytkownik + komputer + program

Typy przetwarzania:

x

sekwencyjne - instrukcja po instrukcji zgodnie z ich kolejnoĞcią w programie

x

wspóábieĪne - biorą w nim udziaá co najmniej 2 procesy wspóádziaáające lub rywalizujące ze sobą;

programy procesów wykonują siĊ "równolegle", wspóádzieląc zasoby (procesor, pamiĊü, komunikacja)

x

równolegáe - równolegáoĞü danych lub funkcji

x

wątkowe - proces nadrzĊdny generuje wątki wykonywane wspóábieĪnie w przestrzeni zasobów procesu

x

wieloprogramowe - kilka programów wykonywanych sekwencyjnie naprzemiennie

x

wieloprocesorowe - ze wspólną lub rozproszoną pamiĊcią

x

wielokomputerowe - rozproszone (sieü lokalna ze stacjami roboczymi lub PC i serwerami) i zespoáowe

(sieü lokalna lub globalna z klientami lub serwerami)

6. Co to jest model przetwarzania i architektura systemu?

model przetwarzania = sposób wykonywania zadaĔ i usáug w systemie informatycznym

model przetwarzania = przetwarzanie + zarządzanie + komunikacja

Modele przetwarzania:

Typowe zastosowania w Ğrodowisku sieciowym:

x przeáączniki sieciowe i routery, przeáączniki wielozadaniowe, przeáączniki wielopoziomowe

x rozwiązania QoS (Quality Of Service parameters) - jakoĞü obsáugi definiowana dla sieci ATM

x

mosty i bramki do transmisji VoIP (Voice Over Internet Protocol)

x

zabezpieczenia - zapory ogniowe, kontrola dostĊpu, szyfrowanie

x rozwiązania pojemnoĞciowe

TYPY OPROGRAMOWANIA

1) platformy programistyczne - do budowy oprogramowania

x aplikacje

uĪytkowe - kompilatory

x narzĊdzia wspomagające projektowanie - CAD'y, Buildery

x wytwarzanie

záoĪonych systemów informatycznych

2) wspomaganie zarządzania

x

systemy operacyjne i maszyna wirtualna

x

pakiety wspomagania administrowania

x narzĊdzia konfigurowania i inicjalizowania

3) zapewnianie jakoĞci i kontrola

x

testowanie i uruchamianie - debuggery

x pakiety

pomiarowe

x

zintegrowane systemy oceny

x ramkĊ rozpoczyna bit startu (0), nastĊpnie przesyáane jest n-bitów sáowa w kolejnoĞci od najmniej do

najbardziej znaczącego, kontrolny bit parzystoĞci lub nieparzystoĞci i jeden, 1.5 lub dwa bity stopu (1)

x po bitach tych moĪe pojawiü siĊ od razu nastĊpna ramka lub linia moĪe pozostaü w stanie 1. OdstĊp

miĊdzy kolejnymi ramkami jest dowolny (tylko w 8251, nie w M68HC11!!!)

x

dáugoĞü przesyáanego sáowa, prĊdkoĞü bodowa transmisji oraz dzielnik czĊstotliwoĞci muszą byü

jednakowo zdefiniowane w nadajniku i odbiorniku przed rozpoczĊciem transmisji. Oznacza to, Īe

nadajnik i odbiornik pracują z tą samą czĊstotliwoĞcią chociaĪ takty zegara nie są dokáadnie

zsynchronizowane

W transmisji synchronicznej:

x

poszczególne bity są wprowadzane zgodnie z taktem nadawania i odbioru

x oprócz linii danych, po której przesyáane są kolejne bity danych, istnieje linia synchronizacji, w której

strona nadająca podaje zegar wyznaczający moment wysáania kolejnych bitów

x

nie ma bitów startu i stopu - wysyáane są znaki synchroniazacji

x

nie ma odstĊpu miĊdzy bajtami (tylko w 8251, nie w M68HC11!!!)

x przed

rozpoczĊciem transmisji wysyáany jest znak synchronizacji. Znaki synchronizacji wyáawiane są

automatycznie i wychwytywany jest moment kolejnego bajtu - wystĊpuje synchronizacja bajtowa

x nie

moĪna przerwaü transmisji gdy nadajnik jest aktywny

x

sytuacja gdy nadawane są tylko znaki synchronizacji jest niepoprawna

INTEL

11. Podaj ogólną organizacjĊ procesora I8080

Mikroprocesor 8080 jest przykáadem mikroprocesora 8-bitowego typu CISC (powyĪej 100 rozkazów)

Szyny:

x adresowa

16-bitowa

x danych

8-bitowa

x sterująca - wiele indywidualnych linii, którymi są przesyáane sygnaáy sterujące urządzenia zewnĊtrzne

Rejestry:

x

16-bitowe: licznik rozkazów PC i wskaĨnik stosu SP

x 8-bitowe

tworzące pary 16-bitowe: BC, DE, HL, WZ

x

8-bitowe: akumulator A, rejestr znaczników stanu F, rejestr rozkazów IR (Instruction Register)

Para HL sáuĪy do adresowania pamiĊci w trybie rejestrowym poĞrednim, natomiast WZ tworzą parĊ rejestrów

tymczasowych.

Ponadto w skáad mikroprocesora wchodzi jednostka obliczeĔ arytmetyczno-logicznych ALU, ukáad

sterowania i róĪne rejestry pomocnicze niewidoczne dla programisty.

12. Jak jest realizowane adresowanie poĞrednie w procesorze I8080

Adresowanie pamiĊci w trybie poĞrednim realizowane jest przez parĊ rejestrów oĞmiobitowych H i L.

16-bitowa zawartoĞü tych rejestrów wskazuje adres miejsca pamiĊci zawierającej argument.

13. WyjaĞnij jakie funkcje peánią sygnaáy READY oraz WAIT doprowadzone do mikroprocesora I8080

READY (we) - sygnaá gotowoĞci moduáów zewnĊtrznych

WAIT (wy) - sygnaá przejĞcia mikroprocesora w stan oczekiwania

Przy wspóápracy z wolnymi pamiĊciami lub ukáadami zewnĊtrznymi moĪe siĊ okazaü, Īe czas trwania cyklu

rozkazowego mikroprocesora jest zbyt krótki. Czas ten moĪna wydáuĪyü za pomocą sygnaáu READY. JeĪeli

podczas odwoáywania siĊ uP do pamiĊci lub ukáadu wejĞcia/wyjĞcia pojawi siĊ sygnaá niegotowoĞci READY

= 0 to uP odpowiada sygnaáem WAIT i cykl procesora jest przedáuĪany aĪ do chwili pojawienia siĊ sygnaáu

x kontroli

parzystoĞci lub nieparzystoĞci

x procedury budzenia grupy urządzeĔ: w trybie WAKEUP odbiorniki ustawiane są w stan uĞpienia i

wówczas ich wszystkie bity statusowe są zablokowane i nie mogą byü ustawiane. Przed rozpoczĊciem

transmisji nowej wiadomoĞci nadajnik wysyáa znak "pobudki": dziewiąty bit ustawiony jest na 1, a na

oĞmiu bitach zapisany jest adres odbiornika, który ma siĊ obudziü. Poprzez dziewiąty bit sterowanie

"budzi" uĞpione odbiorniki, które wówczas mogą sprawdziü czy wiadomoĞü jest adresowana do nich.

(inny rodzaj funkcji WAKEUP to budzenie wszystkich Ğpiących odbiorników gdy zostanie wykryty stan

bezczynnoĞci linii IDLE - 10 lub 11 jedynek)

35. Do czego sáuĪy i jaka jest podstawowa budowa podzespoáu transmisji synchronicznej w

M68HC11?

Ukáad ten sáuĪy do dwukierunkowej, szeregowej synchronicznej transmisji danych wraz z sygnaáem

zegarowym, który wymusza w odbiorniku moment próbkowania linii (dane są jednoczeĞnie nadawane i

odbierane)

Do transmisji danych nadajnik/odbiornik wykorzystuje trzy rejestry:

x

SPDR - 8-bitowy rejestr danych

x

SPCR - rejestr sterujący - ustawia tryb pracy, blokadĊ przerwaĔ, a takĪe oprogramowanie moĪe ustaliü

jeden z czterech formatów fazy i polaryzacji zegara (2 bity)

x

SPSR - rejestr statusowy - sygnalizuje zakoĔczenie transmisji kaĪdego bajtu i ewentualne báĊdy

36. Opisz zachowanie siĊ buforów nadajnika i odbiornika oraz rejestrów sterujących podczas

realizacji transmisji asynchronicznej w M68HC11

Podczas odbioru rejestr danych SPDR jest podwójnie buforowany (najpierw bity danej są gromadzone

w rejestrze przesuwnym, a po skompletowaniu bajtu są one przepisywane do wáaĞciwego rejestru SDPR) i

jest pojedynczym rejestrem z wejĞciem równolegáym i wyjĞciem szeregowym dla operacji nadawania.

Dane są nadawane w postaci transferu niezaleĪnych bajtów. KaĪdy z bajtów jest nadawany

synchronicznie, tzn. w rytm sygnaáów zegarowych generowanych przez ukáad MASTER. RozpoczĊcie

transmisji bajtu poprzedza ustawienie linii ^SS (Slave Select) w stan niski. Istnieje moĪliwoĞü

zaprogramowania czterech róĪnych formatów kombinacji polaryzacji i fazy zegara SCK przy uĪyciu dwóch

bitów CPOL i CPHA rejestru sterującego SPCR.

Przerwania są generowane wtedy, kiedy w rejestrze SPCR jest ustawiony bit SPE i SPIE, i gdy

zakoĔczy siĊ transmisja bajtu (bit SPIF = 1 w rejestrze statusowym) oraz gdy wystąpi báąd związany z

usiáowaniem przejĊcia kontroli nad magistralą przez wiĊcej niĪ jeden ukáad MASTER. Inna typowa sytuacja

báĊdna to próba zapisu bajtu do rejestru danych SPDR wówczas, gdy nie zakoĔczyáa siĊ transmisja

poprzedniego bajtu.

37. Opisz dziaáanie przetwornika A/C w mikrokontrolerze M68HC11

System A/D jest 8-kanaáowym, 8-bitowym przetwornikiem z multipleksowanym wejĞciem, dziaáającym z

dokáadnoĞcią do najmniej znaczącego bitu. Przetwarzanie realizowane jest metodą kompensacji wagowej.

Cztery podstawowe bloki funkcjonalne przetwornika to:

- multiplekser

- przetwornik analogowy - kondensatory áadowane napiĊciem odniesienia

- blok sterowania - ukáad porównania

- 4 rejestry przechowujące wynik

Dziaáanie:

D

08

I

Interrupt - blokada przerwaĔ

D

07

N

Negative - ustawiany gdy wynik jest ujemny

D

02

Z

Zero - ustawiany gdy wszystkie bity wyniku są zerami

D

01

O

Overflow - przekroczenie zakresu - sygnalizuje nadmiar przy operacjach na liczbach ze znakiem

D

0

C

Carry - przeniesienie przy dodawaniu i jego negacja (poĪyczka) przy odejmowaniu

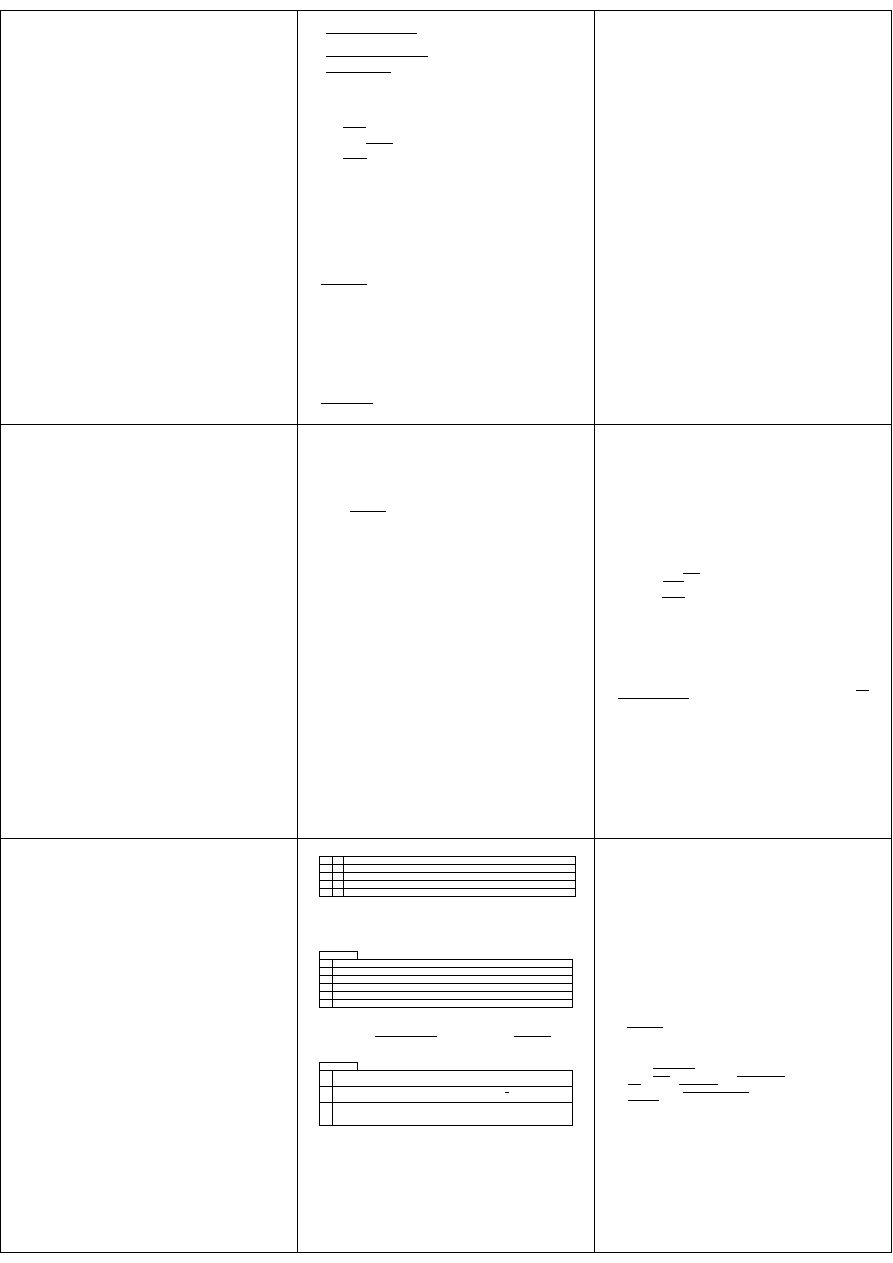

17. Podaj podstawowe rejestry i opisz tryby pracy w ukáadzie 8253

8253 - programowalny moduá czasowy. Zawiera 3 rejestry 16-bitowe (liczniki w kodzie dwójkowym lub

BCD) sáuĪące do realizacji róĪnych przebiegów czasowych w szeĞciu trybach. Rejestry mogą pracowaü

niezaleĪnie poniewaĪ kaĪdy z nich ma osobne wejĞcie bramkujące, taktujące i wyjĞcie.

Tryby pracy:

0

generator pojedynczego narastającego zbocza (skoku)

1

generator pojedynczego impulsu o zadanej dáugoĞci i poziomie aktywnym 0

2

ukáad dzielnika czĊstotliwoĞci - licznik modulo n (tryb cykliczny)

3

ukáad dzielnika czĊstotliwoĞci - generator fali prostokątnej o zadanej czĊstotliwoĞci (tryb cykliczny)

4

generator pojedynczego impulsu opóĨnionego o zadaną liczbĊ bitów - wyzwalany programowo

5

generator pojedynczego impulsu opóĨnionego o zadaną liczbĊ bitów - wyzwalany sprzĊtowo

18. Podaj podstawowe rejestry i opisz tryby pracy w ukáadzie 8255

8255 - programowalny ukáad we/wy do równolegáej, 8-bitowej transmisji dwukierunkowej, w trzech

trybach pracy. Zawiera 3 rejestry 8-bitowe: A, B, C peániące rolĊ portów we/wy oraz rejestr sterujący.

Rejestry A i B mogą pracowaü jako rejestry 8-bitowe we/wy o funkcjach zaleĪnych od trybu pracy; rejestr C

moĪe byü uĪywany jako 2 niezaleĪnie sterowane rejestry 4-bitowe.

Tryby pracy:

0

kaĪdy z rejestrów A i B oraz oddzielnie obie poáówki rejestru C mogą pracowaü niezaleĪnie jako ukáad

wejĞciowy lub wyjĞciowy (ustawia siĊ w ten tryb po sygnale RESET)

1

do transmisji wykorzystywane są tylko rejestry A i B. Obie poáówki rejestru C sáuĪą do ich

wysterowania

2

rejestr A moĪe peániü rolĊ dwukierunkowego kanaáu transmisyjnego z potwierdzeniem; tzn. bufora i

sterownika magistrali komunikacyjnej. Sterowanie odbywa siĊ z wykorzystaniem bitów rejestru C, a

rejestr B moĪe pracowaü w trybie 0 lub 1

19. Jak dziaáa ukáad 8214 w systemie mikroprocesorowym 8080?

8214 - ukáad kontroli przerwaĔ priorytetowych. 8-bitowy rejestr zgáoszeĔ przerwaĔ ma moĪliwoĞü

przyjĊcia do 8 sygnaáów zgáoszenia Īądania przerwania. Fakt wystąpienia przerwania jest zapisywany z

zachowaniem jego priorytetu. Z rejestru jest wybierane przerwanie o najwyĪszym priorytecie i porównywane

w komparatorze z priorytetem przerwania aktualnie obsáugiwanego. JeĪeli przyjĊte zgáoszenie ma priorytet

wyĪszy od obsáugiwanego przerwania to 8214 wystawia do procesora sygnaá Īądania przerwania INT.

Procesor odpowiada sygnaáem potwierdzenia odbioru INTA. NastĊpnie ukáad wystawia na magistrali danych

rozkaz RST n, gdzie n jest zaleĪne od priorytetu i wskazuje od którego bajtu ma siĊ rozpocząü program

obsáugi przerwania.

x RSTn zapisuje Licznik Rozkazów adresem 8xn, gdzie n = 0...7 jest zapisywane na tzrech bitach w

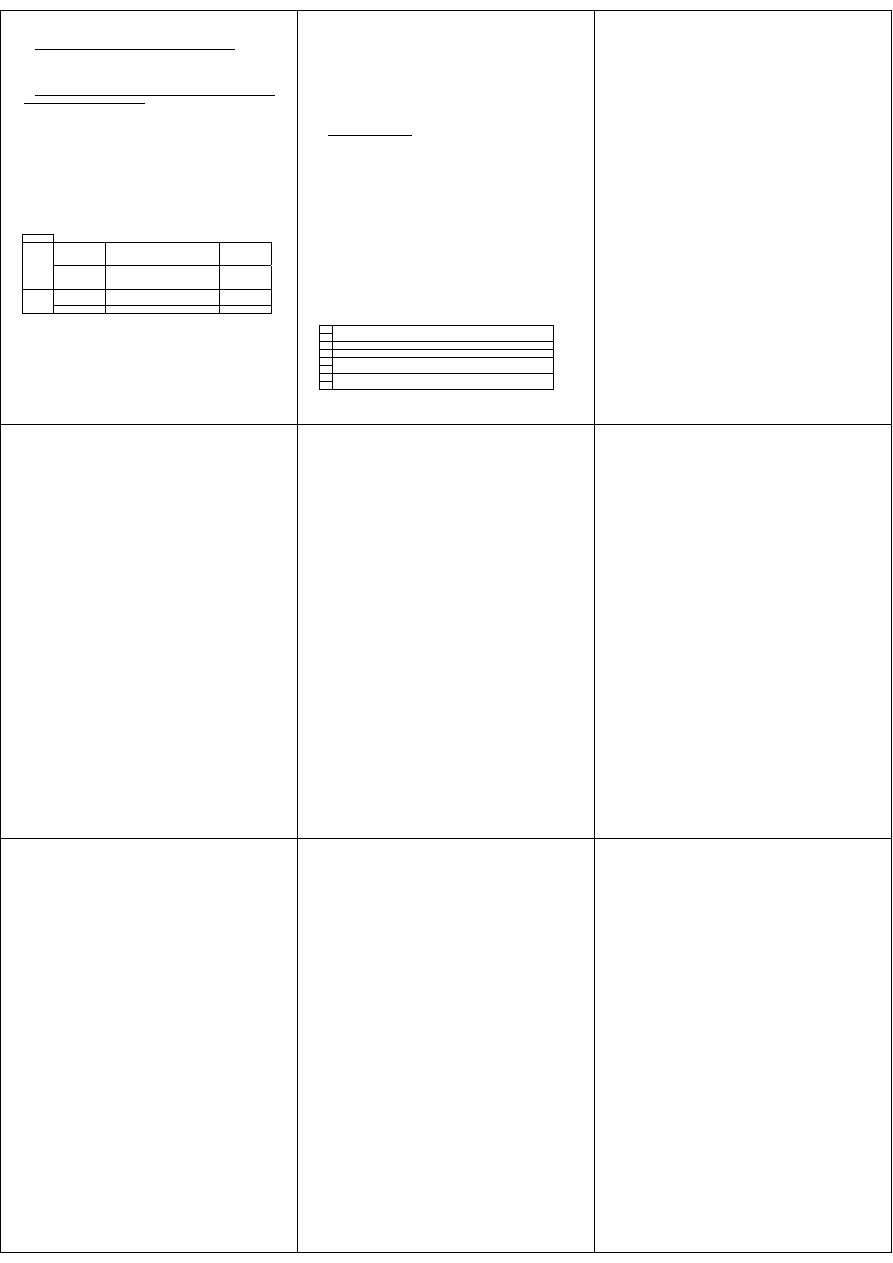

adresie tablicy wektorów przerwaĔ: 1111___1

Jest to obszar przeznaczony na tablicĊ wektorów przerwaĔ programowych (Normal Interrupt Vectors).

Zawiera adresy programów obsáugi wszystkich przerwaĔ niemaskowalnych, dwóch maskowalnych oraz -

XIRQ (np. adresy, którymi jest zapisywany licznik rozkazów po wystąpieniu sygnaáu RESET)

31. Co to jest RESET - opisz cztery typy ponownej inicjalizacji i zachowanie siĊ mikrokontrolera

M68HC11 po ich wystąpieniu

RESET jest to sygnaá, w wyniku którego nastĊpuje ponowna inicjalizacja systemu - ustawienie podzespoáów,

rejestrów i portów mikrokontrolera w stan początkowy; przy czym nie jest zachowywany Ğlad na stosie.

ħródáa sygnaáu RESET:

x POWER ON RESET - zimny spowodowany wáączeniem zasilania i ciepáy wywoáany przez chwilowy

spadek i powrót do wymaganego poziomu napiĊcia

x

EXTERNAL HARDWARE RESET - zewnĊtrzny przycisk RESET

x COMPUTER OPERATING PROPERLY - spowodowany wyzerowaniem rejestru licznika WATCHDOG -

zapobiega zapĊtleniu programu. Licznik ten zlicza wstecz impulsy zegarowe i musi byü co pewien czas

ponownie ustawiany, bo inaczej nastąpi ponowna inicjalizacja ukáadu mikrokontrolera

x CLOCK MONITOR - spowodowany spadkiem czĊstotliwoĞci taktowania zegara systemowego poniĪej

pewnego poziomu (zazwyczaj 10kHz)

W wyniku pojawienia siĊ sygnaáu RESET podzespoáy, rejestry i porty mikrokontrolera zostają ustawione w

stan początkowy:

x Licznik

rozkazu przyjmuje nastĊpujące wartoĞci, w zaleĪnoĞci od Ĩródáa RESETu:

- Power On FFFE FFFF (najpierw opóĨnienie 4096 cykli zegarowych)

- External FFFE FFFF (najpierw opóĨnienie 4096 cykli zegarowych)

- COP FFFA FFFB

- Clock Monitor FFFC FFFD

x NastĊpuje blokada przerwaĔ oraz blokada moĪliwoĞci zatrzymania procesora

x Pozostaáe rejestry procesora (oprócz LR) mają nieustalone wartoĞci

x Porty są ustawiane w stan inicjalny (najczĊĞciej jako porty wejĞciowe lub I/O), a wszystkie bity

statusowe wskazują na brak jakichkolwiek transmisji, generacji, lub przechwyceĔ impulsów

x Zablokowana jest moĪliwoĞü programowania pamiĊci EEPROM

x JeĞli ukáad COP Watchdog nie jest zablokowany w rejestrze CONFIG, to rejestr ten jest zapeániany

najmniejszą dopuszczalną wartoĞcią

32. Opisz dziaáanie mikrokontrolera M68HC11 związane z obsáugą przerwania

1) Przerwanie

bĊdzie obsáuĪone, jeĞli aktualnie nie jest obsáugiwane przerwanie o wyĪszym priorytecie lub

mikrokontroler M68CH11 nie znajduje siĊ w stanie RESET, a ponadto bity I i X nie są ustawione w stan

blokowania przerwaĔ (1)

2) W momencie rozpoczĊcia obsáugi przerwania nastĊpuje ustawienie bitu I (i bitu X jeĞli jest to przerwanie

niemaskowalne) na 1, co oznacza blokadĊ tej grupy przerwaĔ oraz zapamiĊtanie na stosie wszystkich

rejestrów procesora (z wyjątkiem SP): PC, A, B, IX, IY, CCR.

3) NastĊpnie na podstawie priorytetu przerwaĔ (moĪna go zmieniü programowo dla przerwaĔ

maskowalnych) zostaje wyznaczony wektor przerwaĔ i do licznika rozkazów PC wpisywana jest nowa

wartoĞü z górnego obszaru pamiĊci (adres programu obsáugi przerwania)

4) Program obsáugi przerwania powinien byü zakoĔczony rozkazem RTI, który odtwarza Ğlad (rejestry

procesora) ze stosu.

27. Czym róĪni siĊ proces obsáugi przerwaĔ wewnĊtrznych (wyjątki) od zewnĊtrznych w mikroproce-

sorze 16-bitowym I8086?

W przypadku przerwania programowego procesor nie komunikuje siĊ z otoczeniem. Po wystąpieniu

przerwania i zapisaniu Ğladu na stosie, mikroprocesor pobiera z pamiĊci adres dáugiego skoku: 2 sáowa 16-

bitowe tworzące adres w postaci [segment:przesuniĊcie]. Adres ten wskazuje początek tablicy wektorów

programów obsáugi przerwaĔ i jest wpisywany do licznika rozkazów. Program obsáugi przerwania powinien

byü zakoĔczony rozkazem RET powrotu z obsáugi przerwania i odtworzenia Ğladu (rejestrów procesora) ze

stosu.

Dla obsáugi przerwania sprzĊtowego potrzebna jest komunikacja na magistralach miĊdzy

mikroprocesorem a ukáadem sterownika przerwaĔ. W tym przypadku początek tablicy wektora obsáugi

przerwaĔ sprzĊtowych wpisywany jest do sterownika 8259. Gdy pojawi siĊ Īądanie obsáugi przerwania ukáad

powiadamia o tym procesor sygnaáem INT. Gdy procesor potwierdzi moĪliwoĞü przyjĊcia przerwania,

poprzez sygnaá INTA, 8259 wystawia na szynĊ danych 2 bajty bĊdące adresem początku programu obsáugi

dla tego przerwania. Po zakoĔczeniu obsáugi przerwania wysyáany jest rozkaz EOI

(End Of Interrupt)

a

nastĊpnie rozkaz powrotu z obsáugi przerwania RET.

MOTOROLA

28. Podaj ogólną organizacjĊ mikrokontrolera M68HC11 oraz podstawowe tryby pracy

Mikrokontroler M68HC11 skáada siĊ z nastĊpujących podzespoáów:

x procesor

8-bitowy

x pamiĊü operacyjna: RAM, ROM, EEPROM - róĪne wartoĞci w zaleĪnoĞci od typu ukáadu

x

5 portów do komunikacji z otoczeniem: Port A .... Port E

x ukáad przerwaĔ (3 poziomy - maskowalne i niemaskowalne)

x

generator taktów sterujących i ukáad selekcji trybu pracy

Tryby pracy

JEDNOUKàADOWY

praca tylko z wbudowanymi zasobami -

dostĊpna jest tylko pamiĊü zawarta wewnątrz

ukáadu a nóĪki A i B są dostĊpne jako we/wy

Normal Single Chip

normalne

ROZSZERZONY

moĪliwy jest dostĊp do zewnĊtrznej pamiĊci za

pomocą portów B i C. Dwa dodatkowe porty

sterują zapisem/odczytem pamiĊci

Normal Expanded

àADUJĄCY

umoĪliwia zaáadowanie programu, który

zostanie uruchomiony po resecie

Special Bootstrap

specjalne

TESTOWY

Special Test

29. Opisz funkcje podstawowych rejestrów mikrokontrolera M68HC11

x

A, B - 2 akumulatory 8-bitowe tworzące 16-bitowy akumulator D

x

IX - 16-bitowy rejestr indeksowy X

x

IY - 16-bitowy rejestr indeksowy Y

x

SP - 16 bitowy wskaĨnik stosu

x

PC - 16 bitowy licznik rozkazów

x

CCR - 8-bitowy rejestr wskaĨników (Condition Code Register)

30. Jakie funkcje peáni górny obszar pamiĊci (FFF0-FFFF)?

20. Jak dziaáa ukáad 8259 w systemie mikroprocesorowym 8080?

8259 - ukáad sterownika przerwaĔ. 8-bitowy rejestr zgáoszeĔ przerwaĔ ma moĪliwoĞü przyjĊcia do 8

sygnaáów zgáoszenia Īądania przerwania. Fakt wystąpienia przerwania jest zapisywany z zachowaniem jego

priorytetu. Z rejestru jest wybierane przerwanie o najwyĪszym priorytecie i porównywane w komparatorze z

priorytetem przerwania aktualnie obsáugiwanego. JeĪeli przyjĊte zgáoszenie ma priorytet wyĪszy od

obsáugiwanego przerwania to 8259 wystawia do procesora sygnaá Īądania przerwania INT. Procesor

odpowiada sygnaáem potwierdzenia odbioru INTA. NastĊpuje wpisanie 1 na odpowiednią pozycjĊ w rejestrze

obsáugi, co blokuje moĪliwoĞü przyjmowania przerwaĔ o tym samym lub niĪszym priorytecie. NastĊpnie

ukáad wysyáa na magistralĊ danych kolejno 2 bajty rozkazu CALL zawierającego nazwĊ kodu programu

obsáugującego przerwanie - adres początku programu obsáugi przerwania (wektor przerwania).

Odblokowanie obsáugi przerwaĔ nastĊpuje po zakoĔczeniu obsáugi przerwania rozkazem EOI, co powinno

nastąpiü przed pojawieniem siĊ rozkazu RET w podprogramie obsáugi przerwania.

Wielopoziomowa obsáuga przerwaĔ: JeĪeli wejĞcie przerwania jest odblokowane to istnieje moĪliwoĞü

przerwania podprogramu obsáugi przerwania aktualnego przez zgáoszenie o wyĪszym priorytecie i przejĞcie

do obsáugi tego przerwania. W rejestrze obsáugi bit odpowiadający temu przerwaniu jest ustawiany na 1 i w

tym przypadku bĊdą ustawione juĪ dwie jedynki (w ogólnym przypadku wiĊcej). Po zakoĔczeniu obsáugi

przerwania o najwyĪszym priorytecie nastĊpuje zerowanie odpowiadającego mu bitu w rejestrze obsáugi i

powrót do zawieszonego podprogramu obsáugi przerwania o niĪszym priorytecie.

x

cechy i dodatkowe moĪliwoĞci ukáadu 8259:

- programowe umiejscowienie wektora przerwaĔ w dowolnym miejscu w pamiĊci

- programowane maskowanie przerwaĔ: okreĞlenie, które przerwania nie bĊdą przyjmowane

- maskowanie specjalne: dopuszcza przyjĊcie przerwania o równym lub niĪszym priorytecie od aktualnie

obsáugiwanego

- programowy wybór protokoáu priorytowego: np. rotacja priorytetów - obsáuĪone przerwanie uzyskuje

najniĪszy priorytet (lub inny zdefiniowany przez projektanta), a pozostaáe są cyklicznie przesuwane w

obrĊbie numerów wejĞü zgáoszeĔ IR0...IR7

- moĪliwoĞü pracy w trybie ankietowania (kto pierwszy ten lepszy)

- rozbudowa do 64 poziomów przerwaĔ przez poziom slave - doáączenie do kaĪdej lub kilku z nóĪek

ukáadu 8259 (8214)

- moĪliwoĞü pobrania zawartoĞci rejestru zgáoszeĔ bez generacji przerwania

21. W jaki sposób przygotowujemy ukáad 8251 do transmisji asynchronicznej?

Przygotowanie ukáadu 8251 do transmisji asynchronicznej polega na wpisaniu sáów MODE (tryb pracy) i

CONTROL (sterowanie) w odpowiedniej postaci.

format instrukcji MODE:

m

7

m

6

okreĞla iloĞü bitów stopu: 01 - 1 bit; 10 - 1.5 bitu; 11 - 2 bity

m

5

czy bit kontrolny ma byü bitem parzystoĞci (1) czy nieparzystoĞci (0)

m

4

blokada (0) lub zezwolenie (1) parzystoĞci

m

3

m

2

dáugoĞü znaku: 00 - 5 bitów; 01 - 6 bitów; 10 - 7 bitów; 11 - 8 bitów

m

1

m

0

stosunek czĊstotliwoĞci zegara do czĊstotliwoĞci transmisji: 01 - 1x; 10 - 16x; 11 - 64x

format instrukcji CONTROL:

c

7

1

nie ma znaczenia w transmisji asynchronicznej

c

6

1 reset

wewnĊtrzny - oczekiwanie na sáowo MODE przed rozpoczĊciem transmisji

c

5

1

wysterowanie pracy modemowej - wymuszenie stanu

0

S

T

R

Request To Send

c

4

1 kasowanie

wskaĨników báĊdów w sáowie statusowym

c

3

1 wysáanie znaku przerwy - wymuszenie stanu TxD = 0

c

2

1

uruchomienie odbiornika 0 - zablokowanie

c

1

1

realizacja komunikacji - wymuszenie stanu

0

R

T

D

Data Terminal Ready

c

0

1

uruchomienie nadajnika 0 - zablokowanie

22. Jak dziaáa ukáad 8251 w trybie pracy synchronicznej

Na początku do rejestru sterującego wpisywane jest sáowo MODE okreĞlające tryb pracy synchronicznej

oraz sáowo CONTROL. Sáowo MODE okreĞla liczbĊ znaków synchronizacji (1 lub 2), kierunek sygnaáu

(wejĞcie lub wyjĞcie), sposób kontroli parzystoĞci oraz dáugoĞü znaku. Do przyjmowania informacji sáuĪy

rejestr odbiorczy RB taktowany sygnaáem zewnĊtrznego zegara. Ukáad odbiornika zamienia informacjĊ

szeregową na postaü równolegáą, usuwa bity synchronizacji i przepisuje odebrany znak do wejĞciowego

bufora danych RA. W momencie przepisania znaku do bufora pojawia siĊ sygnaá gotowoĞci odbiornika.

Odczytanie przez mikroprocesor informacji z wejĞciowego rejestru danych kasuje sygnaá gotowoĞci.

Mikroprocesor chcąc wysáaü znak do urządzenia zewnĊtrznego wpisuje go do wyjĞciowego bufora

danych TA. Autonomiczny blok sterowania ukáadu transmisji przepisuje ten znak do rejestru nadawczego TB

(jeĞli poprzedni znak juĪ zostaá wysáany), uzupeániając go o bit(y) synchronizacji, po czym rozpoczyna

szeregowe przesyáanie informacji do wyjĞcia TxD. Przesyáanie to odbywa siĊ w takt sygnaáu synchronizacji

TxC. Przepisanie wysyáanego znaku do rejestru nadawczego (a wiĊc zwolnienie wyjĞciowego bufora

danych) jest sygnalizowane pojawieniem siĊ stanu 1 na wyjĞciu gotowoĞci nadajnika oraz ustawieniem

odpowiedniej pozycji rejestru stanu. Wpisanie przez mikroprocesor nowego znaku do rejestru wyjĞciowego

kasuje sygnaá gotowoĞci.

x podwójne

buforowanie - dodatkowy rejestr danych - umoĪliwia zapisanie do nadawania lub odebranie

kolejnej danej, nawet jeĪeli poprzednia transmisja/odbiór nie zostaáa zakoĔczona.

23. Podaj ogólną budowĊ procesora I8086

Mikroprocesor I8086 jest jednym z najbardziej popularnych mikroprocesorów 16-bitowych

Szyny:

x Adresowa

20-bitowa

x Danych

16-bitowa

Rejestry ogólnego przeznaczenia lub funkcjonalne, 16-bitowe:

x

AX - akumulator

x

BX - rejestr bazowy

x

CX - rejestr zliczający

x

DX - rejestr danych

x

SP - wskaĨnik stosu

x

BP - wskaĨnik bazy

x

SI - rejestr indeksowy Ĩródáa

x

DI - rejestr indeksowy przeznaczenia

x

PC - licznik programu (Program Counter)

x

F - rejestr znaczników (wskaĨników, flag)

x

IP - licznik rozkazów (Instruction Pointer)

Rejestry segmentów:

x

CS - rejestr segmentu programu (kodu)

x

DS - rejestr segmentu danych

x

SS - rejestr segmentu stosu

x

ES - dodatkowy rejestr segmentowy

Mikroprocesor 8086 skáada siĊ z dwu czĊĞci:

- ukáadu sterowania magistral - BIU (bus interface unit)

- ukáadu wykonawczego - EU (execution unit)

Obie czĊĞci mają wáasne ukáady sterowania i pracują czĊĞciowo niezaleĪnie. Zadaniem ukáadu sterowania

magistral BIU jest adresowanie pamiĊci, pobieranie kolejnych rozkazów z pamiĊci i umieszczanie ich w

kolejce rozkazów oraz, na Īądanie EU, pobieranie lub przesyáanie argumentów do pamiĊci. Zadaniem

ukáadu wykonawczego EU jest pobieranie kolejnych rozkazów z kolejki i ich wykonanie, a wiĊc m.in.

obliczanie adresów efektywnych argumentów i realizacja odpowiadających rozkazom operacji przetwarzania

informacji.

x kolejkowanie

rozkazów - pobieranie z pamiĊci operacyjnej rozkazów z pewnym wyprzedzeniem. Kolejka

moĪe przechowywaü 3 rozkazy

24. Podaj sposób obliczania adresu efektywnego w mikroprocesorze 8086

W mikroprocesorze 8086 dostĊp do informacji zawartych w segmencie polega na zsumowaniu 16-

bitowego adresu z przesuniĊtą o 4 bity zawartoĞcią odpowiedniego rejestru segmentu, tworząc 20-bitowy

adres fizyczny, wysyáany na magistralĊ adresową. Adres efektywny jest zapisywany jako [S:P]

adres efektywny = adres segmentu * 16 + przesuniĊcie

25. Podaj nazwy i opisz rolĊ rejestrów wewnĊtrznych sterownika przerwaĔ 8259

x rejestr zgáoszeĔ ĪądaĔ (przerwaĔ) IRR - przyjmuje i zachowuje zewnĊtrzne przerwania wraz z priorytetem

x rejestr maskujący IMR - umoĪliwia programowane maskowanie sygnaáów zgáoszeĔ przerwaĔ (okreĞlenie,

które przerwania nie bĊdą przyjmowane - te na których miejscu bĊdzie wpisane 0) oraz maskowanie

specjalne (przyjmowanie przerwaĔ o równym lub niĪszym priorytecie od aktualnego)

x rejestr obsáugi przerwaĔ ISR - przechowuje informacje o przerwaniu aktualnie obsáugiwanym - 1 na

pozycji aktualnie obsáugiwanego przerwania (w zaleĪnoĞci od priorytetu)

x ukáad wyboru priorytetu (porównania)

26. Jaką rolĊ peánią sáowa rozkazowe ICW1, ICW2 oraz kiedy uĪywamy sáowa ICW3 w programowaniu

dziaáania sterownika przerwaĔ?

Sáowa ICW1 i ICW2 pozwalają okreĞliü adres wektora przerwania (adres początku programu obsáugi

przerwania) i jego organizacjĊ.

x

ICW1 (podawany na adres bazowy parzysty - adres ukáadu) - okreĞla wartoĞci 2 - 3 bitów mniej

znaczącego bajtu adresu wektora przerwania, odstĊp pomiĊdzy początkami programów w tablicy

wektorów przerwaĔ oraz rozbudowĊ ukáadu sterowania przerwaniami

x

ICW2 (podawany na adres nieparzysty) zawiera bardziej znaczący bajt adresu początku podprogramu

obsáugi przerwania

x

ICW3 - okreĞla strukturĊ ukáadu kontroli przerwaĔ i uĪywamy go gdy pracujemy w kaskadzie kilku

ukáadów 8259. Pozwala to nam na rozbudowĊ do 64 poziomów przerwaĔ w konfiguracji MASTER -

SLAVE. Dla ukáadu MASTER jedynka na danej pozycji D

i

sáowa ICW3 wskazuje, Īe na wejĞcie S

i

doáączony jest ukáad SLAVE. Dla ukáadu SLAVE trzy ostatnie bity wskazują numer wejĞcia ukáadu

MASTER do którego przyáączony jest ten moduá.

Wyszukiwarka

Podobne podstrony:

Ksiazek id 252570 Nieznany

BP Mikroprzedsiebiorstwa id 925 Nieznany (2)

Abolicja podatkowa id 50334 Nieznany (2)

4 LIDER MENEDZER id 37733 Nieznany (2)

katechezy MB id 233498 Nieznany

metro sciaga id 296943 Nieznany

perf id 354744 Nieznany

interbase id 92028 Nieznany

Mbaku id 289860 Nieznany

Probiotyki antybiotyki id 66316 Nieznany

miedziowanie cz 2 id 113259 Nieznany

LTC1729 id 273494 Nieznany

D11B7AOver0400 id 130434 Nieznany

analiza ryzyka bio id 61320 Nieznany

pedagogika ogolna id 353595 Nieznany

Misc3 id 302777 Nieznany

cw med 5 id 122239 Nieznany

więcej podobnych podstron