8.10. Pamięci

Pamięcią

nazywa się układ, umożliwiający

przechowywanie wartości pewnej (zwykle dużej) liczby

bitów, zorganizowanych w

N słów m bitowych

. Wybór

pojedynczego słowa pamięci realizuje się przez podanie

numeru słowa, zwanego adresem, na specjalnych liniach

adresowych. Numer słowa (

adres

) wyraża się w

naturalnym kodzie dwójkowym.

1

ETR 8.10

Opracował dr inż. Grzegorz Stępień

1. Wprowadzenie

Podstawowym parametrem pamięci jest

pojemność

,

określająca liczbę zapamiętywanych bitów lub słów. Jeśli

długość słowa wynosi 8 bitów (bajt), pojemność pamięci

podaje się w bajtach. Pojemność małych pamięci,

stosowanych w prostych układach cyfrowych, jest rzędu

kilkunastu do kilkudziesięciu bitów lub bajtów. Pojemność

dużych pamięci, stosowanych np. w komputerach, podaje

się w kilobitach (Kb), megabitach (Mb), kilobajtach (KB),

megabajtach (MB) lub gigabajtach (GB). Przedrostek K

oznacza 2

10

=1024, czyli ok. 1000. Przedrostek M oznacza

2

20

=1048576, a więc ok. miliona. Przedrostek G oznacza

2

30

=1073741824, a więc ok. miliarda ( 10

9

).

2

ETR 8.10

Budowa pamięci o dużej pojemności wymaga umieszczenia w

jednej strukturze ogromnej, sięgającej wielu milionów, liczby

elementarnych komórek pamięci, przechowujących wartość

jednego bitu informacji. Komórki pamięci muszą mieć zatem

możliwie prostą budowę, bardzo małe wymiary (powierzchnię) i

bardzo mały pobór mocy. W pamięciach o dużej pojemności

powierzchnia komórki jest rzędu kilku do kilkudziesięciu µm

2

a

pobór mocy rzędu ułamka do kilkudziesięciu W na bit.

Układy pamięciowe wykonywane są jako

bipolarne

lub

unipolarne

. Układy bipolarne, wymagające relatywnie dużej

powierzchni jednego tranzystora, mają mniejszą pojemność lecz

generalnie większą szybkość działania. Układy unipolarne

(MOS, CMOS) umożliwiają uzyskanie większych pojemności.

Produkowane są także układy Bi-CMOS, w których stosuje się

zarówno tranzystory bipolarne i unipolarne, uzyskując dużą

szybkość działania przy większych pojemnościach.

3

ETR 8.10

Rozróżnia się

dwa zasadnicze rodzaje pamięci

:

• pamięci do zapisu i odczytu

, w których w łatwy sposób można

w dowolnej chwili wpisać nową wartość wybranego słowa;

pamięci takie nazywane są pamięciami

RAM

(Random

Access Memory -

pamięci o dostępie swobodnym

); pamięci

RAM tracą wpisaną wcześniej zawartość po wyłączeniu

napięcia zasilającego; po ponownym włączeniu zasilania

słowa pamięci przyjmują przypadkowe wartości.

• pamięci tylko do odczytu

, o stałej zawartości, której nie można

wcale bądź łatwo zmienić; pamięci takie nazywane są

pamięciami

ROM

(Read Only Memory) lub

pamięciami

stałymi

; pamięci ROM nie tracą zawartości po wyłączeniu

napięcia zasilającego i służą do przechowywania

niezmiennych wartości.

4

ETR 8.10

Pamięci

RAM

stosowane są w przypadku konieczności częstej

zmiany wartości niektórych słów, do przechowywania

cząstkowych wyników obliczeń, pomiarów itp. Pamięci takie

stosowane są powszechnie jako pamięć operacyjna

komputera. W pamięciach

ROM

zapisane są podstawowe

procedury systemu operacyjnego komputera, umożliwiające

inicjalizację pracy komputera po włączeniu zasilania.

5

ETR 8.10

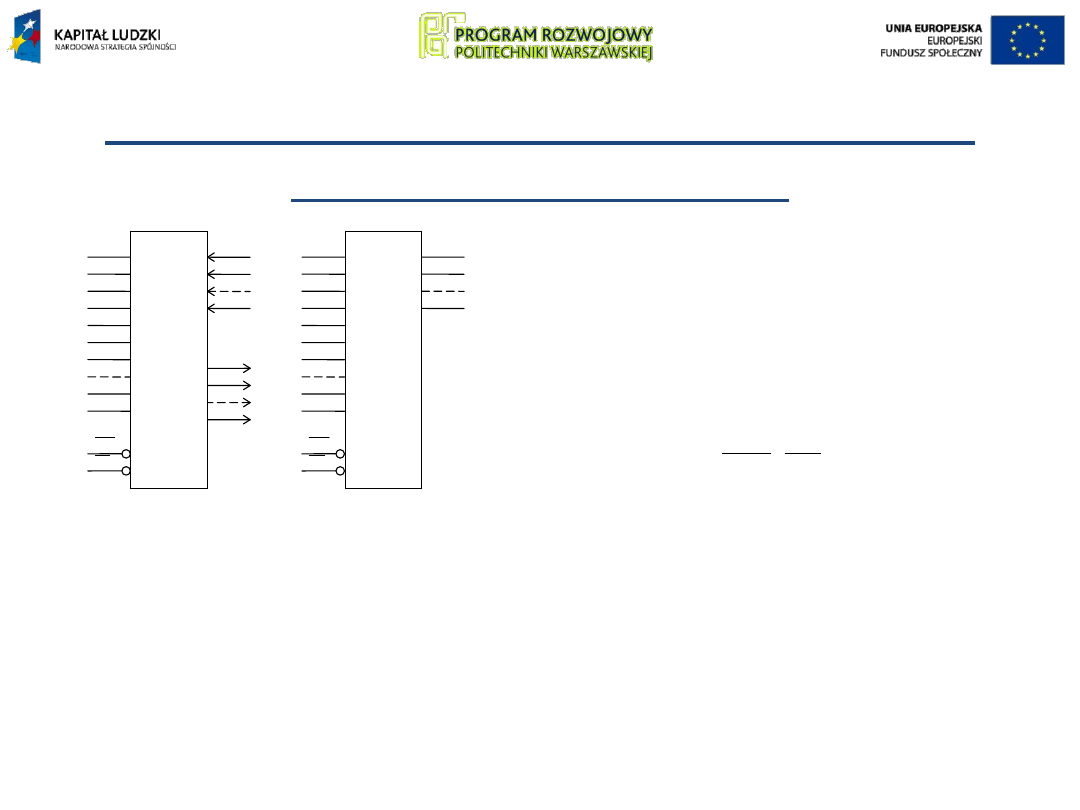

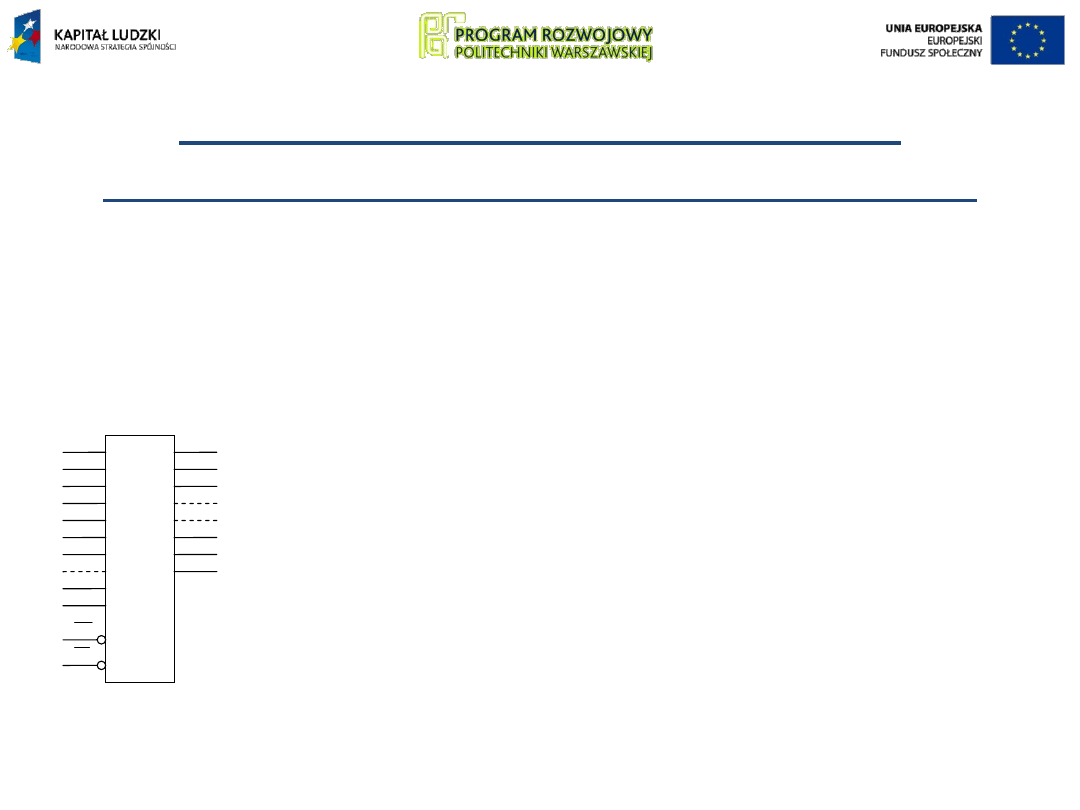

2. Zwykłe (statyczne) pamięci do zapisu i

odczytu (RAM, S-RAM)

Pamięć ma:

• m linii wejścia/wyjścia danych

(I

0

...I

m-1

, O

0

...O

m-1

, D

0

...D

m-1

);

• n linii adresowych (A

0

... A

n-1

);

• kilka dodatkowych linii

sterujących ( ).

Linie wejścia i wyjścia mogą być:

• osobne, (I

0

…I

m-1

) i (O

0

…O

m-1

) jak (a);

• wspólne, (D

0

...D

m-1

), przez które następuje zarówno

wyprowadzanie danych jak i zapis danych do pamięci jak (b).

6

O

0

O

1

O

m-1

I

0

I

1

I

m-1

D

0

D

1

D

m-1

CS

WE

A

0

A

1

A

2

A

3

A

4

A

5

A

6

A

n-2

A

n-1

a)

b)

CS

WE

A

0

A

1

A

2

A

3

A

4

A

5

A

6

A

n-2

A

n-1

CS

,

WE

ETR 8.10

• Długość słowa

wynosi m bitów;

• Linie adresowe wybierają jedno z

N = 2

n

słów

. Numer (

adres

)

słowa jest równy liczbie dwójkowej, ustawionej na tych liniach.

• Pojemność pamięci

to N słów m - bitowych lub N∙m bitów.

• Wejścia (Chip Select - selekcja struktury) i (Write

Enable -

dozwolony zapis) sterują pracą pamięci.

7

CS WE

1

0

pamięć nieaktywna;

zapis i odczyt niemożliwy;

wyjścia danych w stanie wysokiej impedancji

1

1

0

0

zapis danych

0

1

odczyt danych

CS

WE

ETR 8.10

• przy zapisie słowa

o numerze (adresie) ustawionym na liniach

adresowych bity słowa przyjmują wartości, występujące na

liniach danych I

0

…I

m-1

lub D

0

...D

m-1

na końcu stanu, przy

przejściu linii ze stanu 0 z powrotem do stanu 1;

• przy odczycie danych

pamięć wyprowadza na linie O

0

...O

m-1

lub D

0

...D

m-1

wartość słowa o numerze (adresie) ustawionym

na liniach adresowych.

• Niektóre typy pamięci wyposażone są w dodatkowe wejście

sterujące (Output Enable - dozwolone wyjście), włączające lub

blokujące wyprowadzanie danych. Odczyt pamięci następuje przy

, i . Przy linie wyjścia danych są w stanie

wysokiej impedancji, niezależnie od stanu pozostałych linii

sterujących. Stan wejścia nie ma znaczenia w cyklu zapisu

pamięci (przy ).

• W niektórych typach pamięci wejście sterujące zapisem nazywane

jest nie lecz (Read/Write

– zapis/odczyt).

8

WE

OE

0

CS

1

WE

0

OE

1

OE

OE

0

WE

WE

W

/

R

ETR 8.10

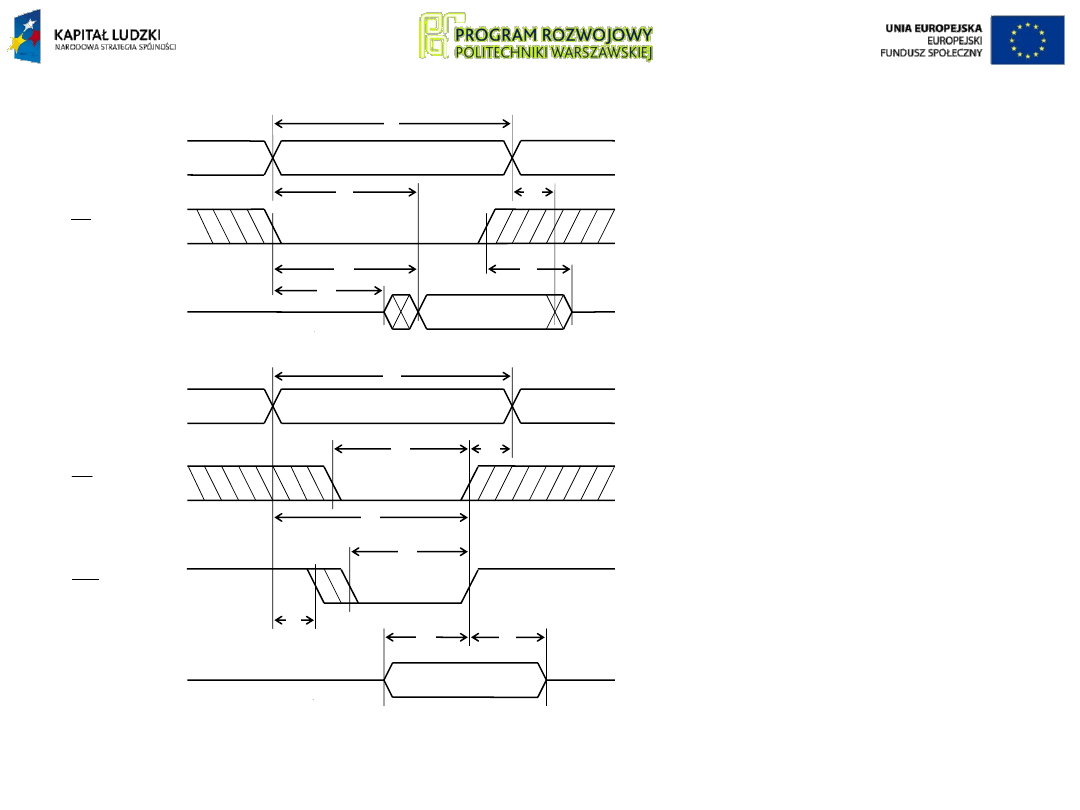

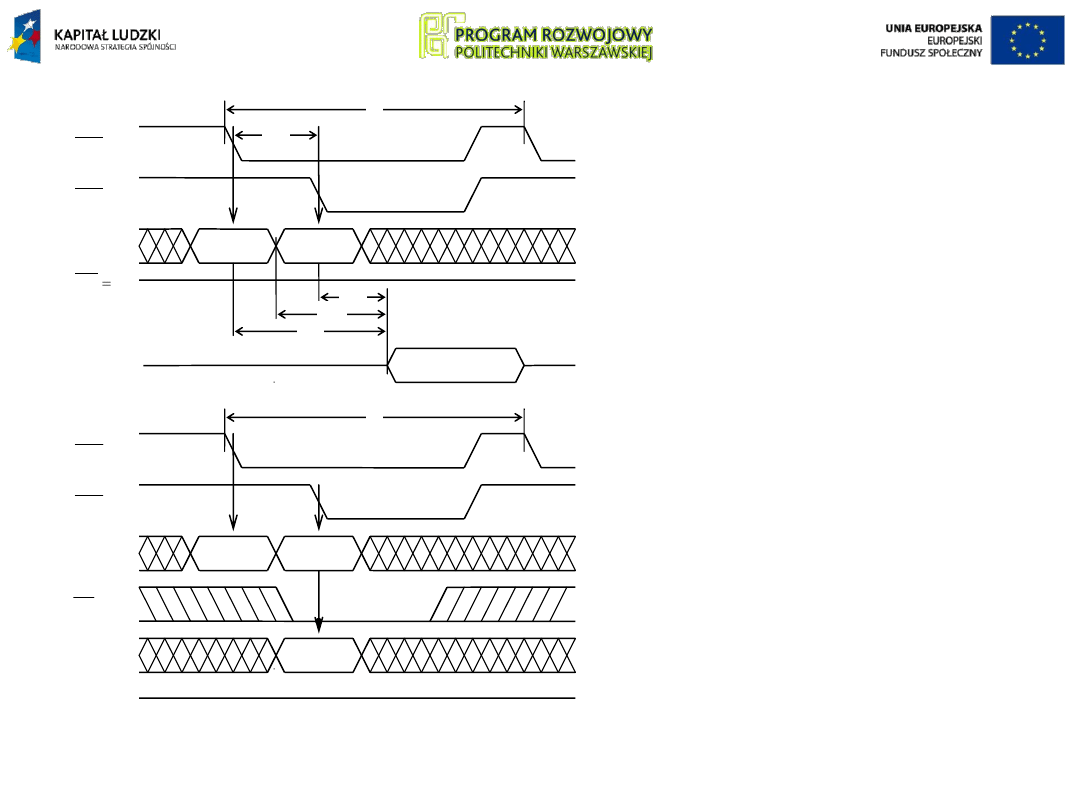

9

Przebiegi czasowe

sygnałów przy

odczycie (a) i zapisie

(b) pamięci:

Podstawowe czasy

charakteryzujące

pamięć to:

• t

RC

–

czas cyklu

odczytu

;

• t

WC

–

czas cyklu

zapisu

.

stan wysokiej impedancji

Adres

Dane (wyjście)

CS

t

AA

t

RC

t

ACS

t

CH

t

OH

Dane stabilne

a)

Adres

Dane (wejście)

t

WC

Dane stabilne

CS

WE

t

CW

t

WR

t

AW

t

WP

t

AS

t

DW

t

DH

b)

t

CLZ

ETR 8.10

Przy odczycie

wartość bitów słowa o numerze (adresie) ustawionym na

liniach adresowych pojawia się na liniach wyjścia danych po pewnym

czasie opóźnienia od chwili ustawienia CS

i ustalenia adresu. Po

czasie t

CLZ

od zmiany

CS z 1 na 0 linie wyjścia danych przestają być w

stanie nieaktywnym (wysokiej impedancji) i przyjmują przypadkowe

wartości. Dopiero po czasie t

AC

, zwanym

czasem dostępu od sygnału

selekcyjnego

(chip select access time) i czasie t

AA

, zwanym czasem

dostępu od chwili ustawienia adresu (address access time), na liniach

danych pojawiają się stabilne wartości, odpowiadające wartościom

bitów wybranego słowa. Wartości te utrzymują się jeszcze przez czas

t

OH

po zmianie adresu (output hold

time). Linie wyjścia danych wracają

do stanu wysokiej impedancji po czasie t

CH

od zmiany sygnału CS z 0

na 1. Sekwencyjny odczyt danych z kolejnej komórki pamięci o innym

adresie może nastąpić dopiero po czasie t

RC

, zwanym

czasem cyklu

odczytu

(read cycle time).

W układach, wyposażonych w wejście OE, wejście to ma krótszy czas

dostępu od wejścia CS.

10

ETR 8.10

Zapis danych

do pamięci realizuje się przy

WE

=0. Sygnał

CS

powinien

być przy tym równy 0 wcześniej i dłużej niż

WE

lub co najmniej w tym

samym czasie. Adres słowa powinien być ustawiony wcześniej o t

AS

i

utrzymywać się dłużej o t

WR

lub zmieniać się jednocześnie z sygnałem

WE

(t

AS

0, t

WR

0 ). Stan

WE

=0 i

CE

=0 musi występować przez

określony czas, odpowiednio t

CW

i t

WP

. Dane wejściowe należy ustawić

wcześniej o t

DW

i utrzymywać jeszcze przez t

DH

od zmiany

WE

z

powrotem z 0 na 1. Sekwencyjny wpis danych do kolejnej komórki

pamięci o innym adresie może nastąpić dopiero po czasie t

WC

, zwanym

czasem cyklu zapisu

(write cycle time).

Omówione czasy dostępu i cyklów określają maksymalną szybkość, z

jaką można odczytywać i zapisywać dane. Z reguły czas dostępu od

sygnału selekcyjnego t

AC

jest mniejszy lub taki sam jak czas dostępu od

adresu t

AA

a minimalne czasy trwania cyklu odczytu i zapisu są także

równe t

AA

. Szybkość działania pamięci można zatem w większości

przypadków opisać przez podanie jednego

czasu dostępu do pamięci

,

wynikającego z wartości t

AA

. Czas ten ma wartość od kilku do kilkuset

nanosekund, zależną od typu i technologii wykonania pamięci.

11

ETR 8.10

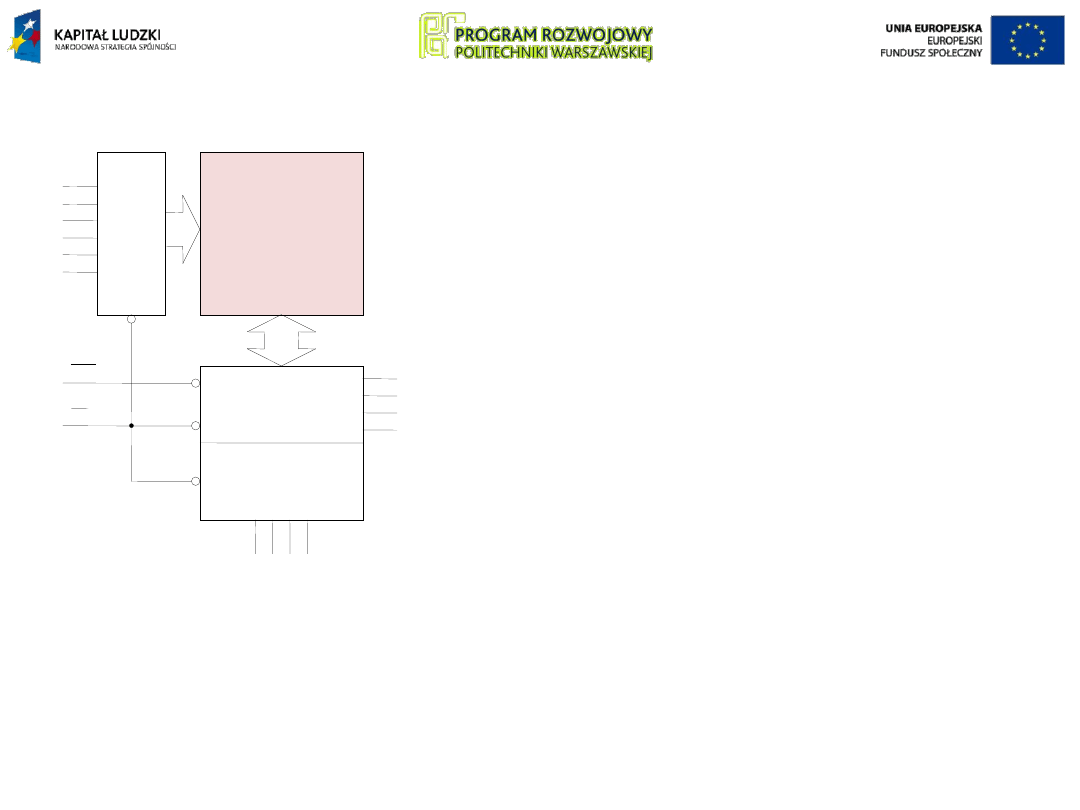

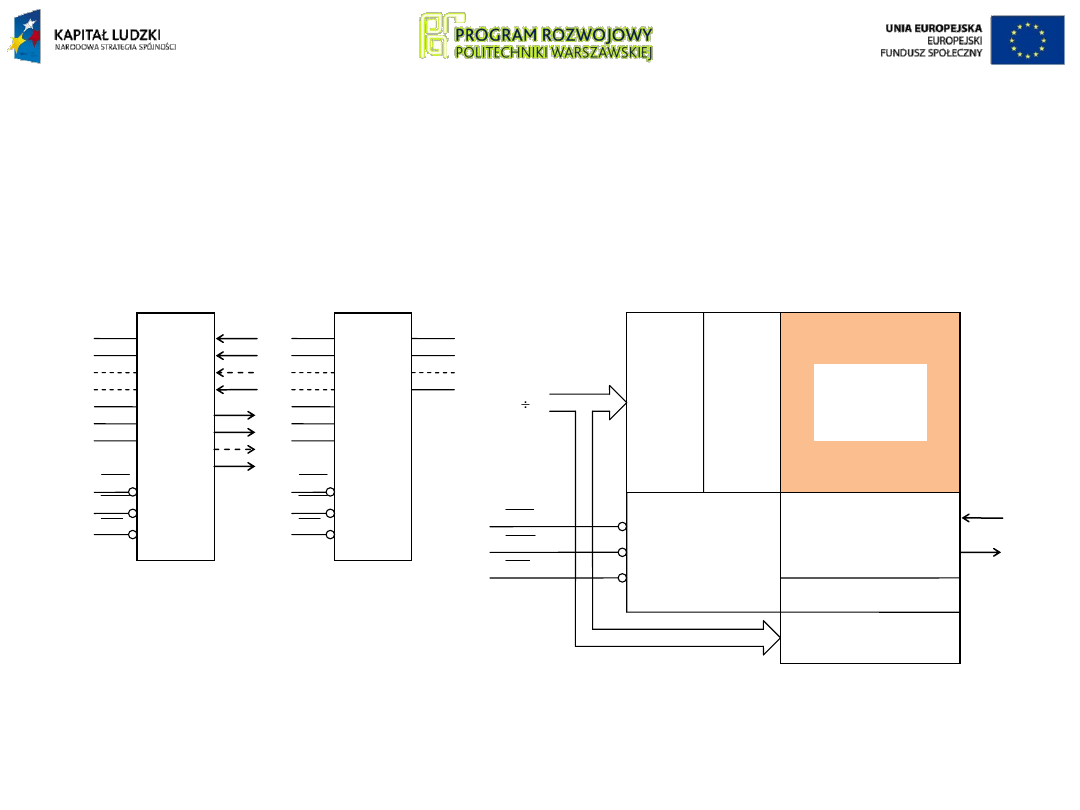

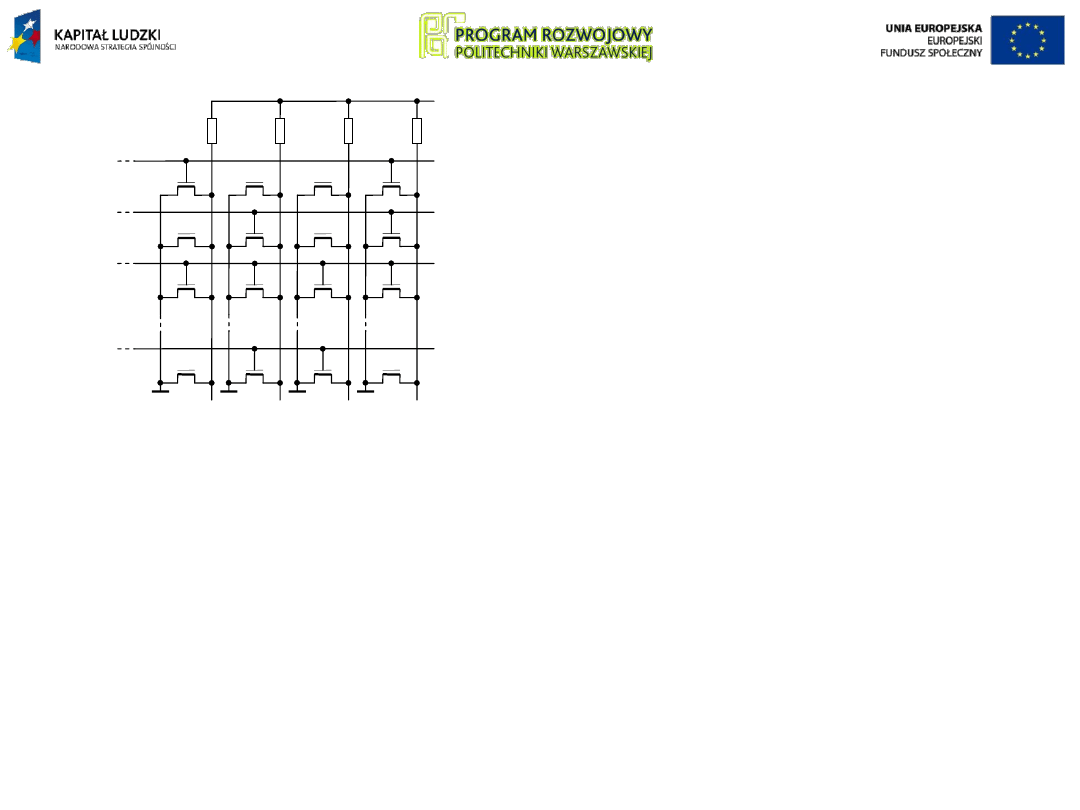

Wewnętrzna struktura pamięci RAM:

W każdym przecięciu wiersza z kolumną znajduje się jedna

elementarna komórka pamięci

. Liczba wierszy i kolumn matrycy

jest z reguły jednakowa.

12

W celu uzyskania zwartej konstrukcji,

zmniejszenia długości połączeń między

elementami oraz ułatwienia i

przyspieszenia adresowania,

elementarne komórki pamięci,

przechowujące 1 bit informacji,

zgrupowane w

matrycę pamięciową

,

czyli prostokątną strukturę o

charakterze siatki. Linie poziome tej

siatki nazywa się

wierszami

lub

liniami

słowa

, a linie poziome

kolumnami

lub

liniami bitu

.

A

4

A

5

A

6

A

7

A

8

A

9

Dekoder

wiersza

Obwody

wejścia / wyjścia

Dekoder kolumn

D

0

D

1

D

3

D

4

WE

CS

A

0

A

1

A

2

A

3

Matryca

komórek pamięci

64x16x4

ETR 8.10

Przy pojemności pamięci N słów m bitowych (N∙m bitów) liczba

wierszy i kolumn matrycy jest równa . Odpowiednia

liczba (log

2

w) linii adresowych (na ogół starszych) wybiera

poprzez dekoder wiersza komórki pamięci, umieszczone w

jednym wierszu matrycy. Pozostałe (log

2

N

– log

2

w) linie

adresowe, dołączone do dekodera kolumn, wybierają z tego

wiersza m komórek pamięci adresowanego słowa i dołączają te

komórki poprzez obwody wejścia / wyjścia do linii danych.

Kierunek przepływu danych (zapis - odczyt) określa stan linii

WE

. Przy

CS

=1 obwody wejścia / wyjścia danych i dekodery

wierszy i kolumn zostają zablokowane.

Podstawowym układem, umożliwiającym przechowanie wartości

jednego bitu informacji jest

statyczny przerzutnik RS

. Dla

uzyskania małych wymiarów, w układzie pamięci nie jest to

przerzutnik, zbudowany z bramek NAND lub NOR, lecz znacznie

prostszy,

złożony z kilku tranzystorów

.

13

m

N

w

ETR 8.10

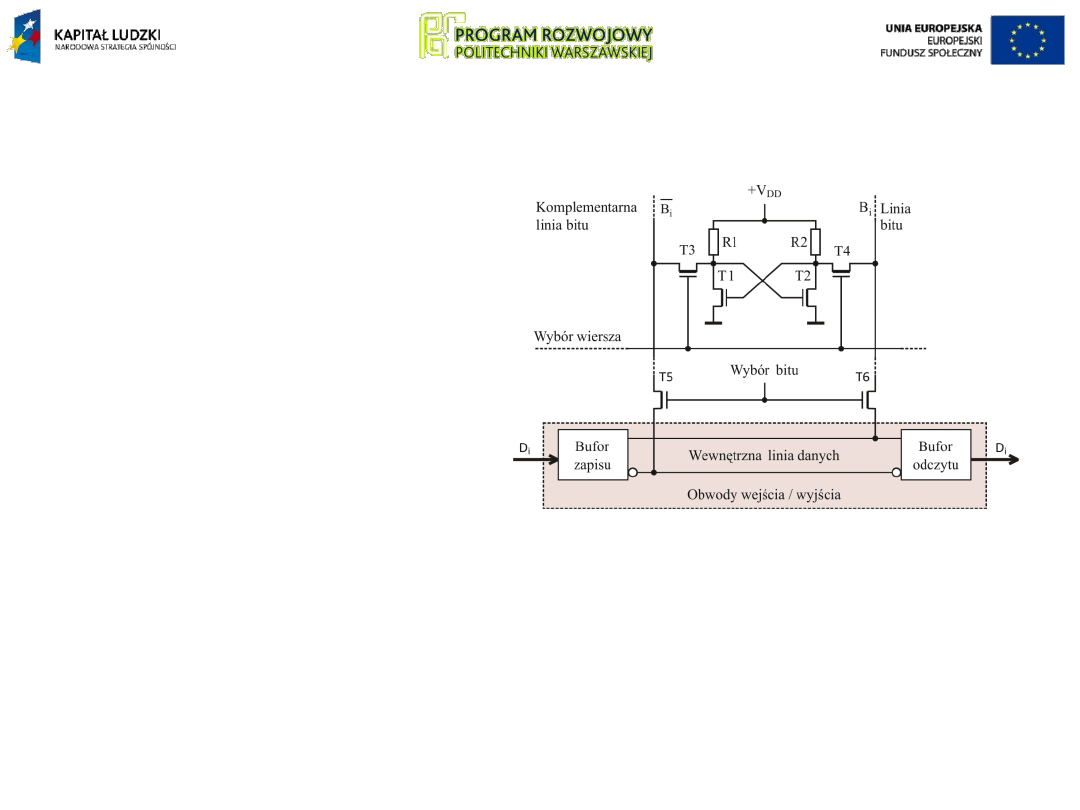

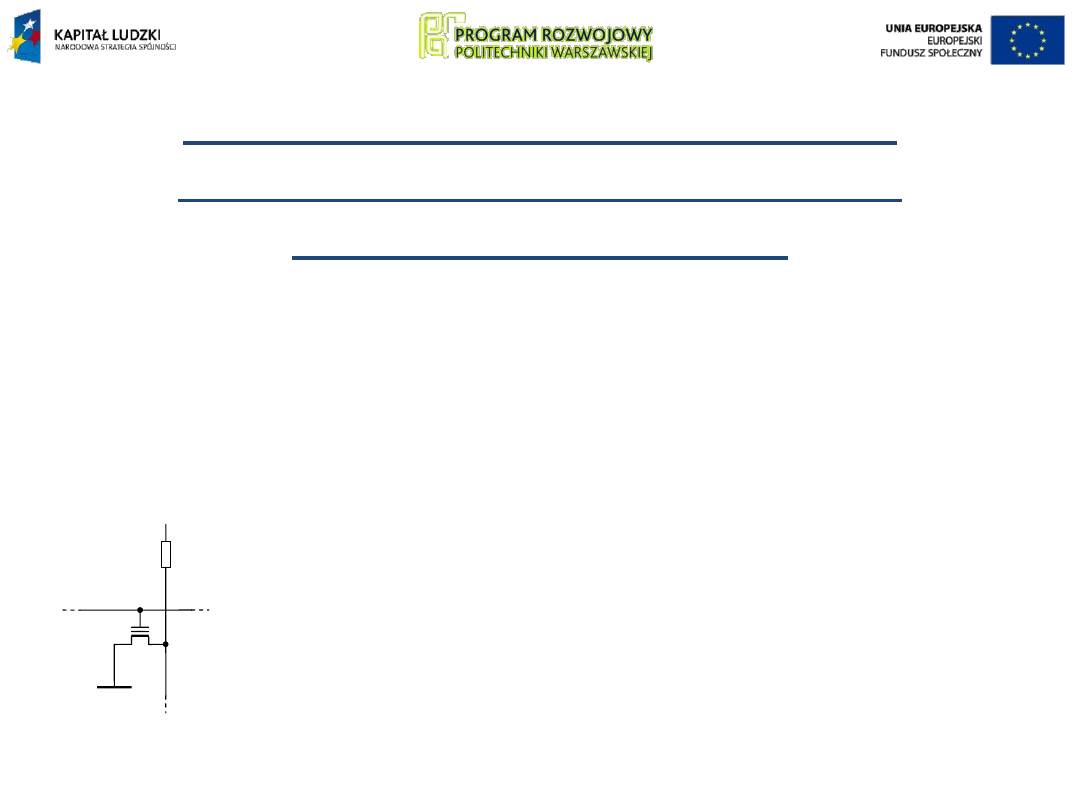

Schemat elementarnej komórki statycznej pamięci RAM z

tranzystorami NMOS:

Przerzutnik RS

tworzą

tranzystory T1 i T2 z

rezystorami R1 i R2. Wybór

i dołączenie tego

przerzutnika do obwodów

wejścia / wyjścia pamięci

realizuje się przez

ustawienie przez

dekoder

wiersza

stanu 1 na linii wyboru wiersza i ustawienie przez

dekoder kolumn

stanu 1 na wejściu wyboru bitu (kolumny).

Wprowadza to tranzystory T3, T4, T5 i T6 w stan przewodzenia i

dołącza dreny tranzystorów T1 i T2 do biegnących wzdłuż

kolumn matrycy pamięci linii bitów i oraz z kolei te linie do

odpowiedniej linii danych obwodów wejścia / wyjścia.

14

ETR 8.10

W nie wybranych komórkach pamięci, należących do innych

kolumn, tranzystory T5 i T6 są wyłączone. W komórkach

pamięci, należących do innych wierszy, wyłączone są także

tranzystory T3 i T4. Izoluje to nie wybrane komórki pamięci od

obwodów wejścia / wyjścia.

Zapis bitu

do wybranej komórki pamięci uzyskuje się po ustawieniu

przez bufor zapisu odpowiednich stanów na liniach bitów B

i

i

B

i

.

Ustawienie B

i

=0 i

B

i

=1 wymusza stan niski (0) na drenie T2 i stan

wysoki (1) na drenie T1. Stan wysoki na drenie T1 i połączonej z nim

bramce T2 wprowadza T2 w stan przewodzenia, co podtrzymuje stan

niski na drenie T2. Stan ten, doprowadzony do bramki T1, powoduje

zablokowanie T1, co podtrzymuje stan wysoki (1) na drenie T1.

Przerzutnik zostaje ustawiony w stan 0. Podobnie, przy B

i

=1 i

B

i

=0

przerzutnik zostaje ustawiony w stan 1. Wymuszone w ten sposób

stany napięć na drenach T1 i T2 zostają zachowane po zablokowaniu

bufora zapisu. Stan przerzutnika poprzez bufor odczytu wyprowadzany

jest na linię wyjścia danych.

15

ETR 8.10

Podobne układy komórek pamięci wykonywane są także z

tranzystorami bipolarnymi.

Pamięci RAM, w których elementarną komórką pamięci jest

przerzutnik statyczny RS, nazywane są

pamięciami

statycznymi RAM

(w skrócie S-RAM, Static RAM).

Większość współczesnych pamięci statycznych RAM ma

właściwość znacznej redukcji poboru prądu przy

zablokowaniu pamięci sygnałem CS=1. Ponadto możliwe

jest wówczas użycie niskiego napięcia zasilającego (1,5...3

V). Umożliwia to przechowywanie zawartości pamięci po

wyłączeniu głównego napięcia zasilającego i przejściu na

zasilanie bateryjne.

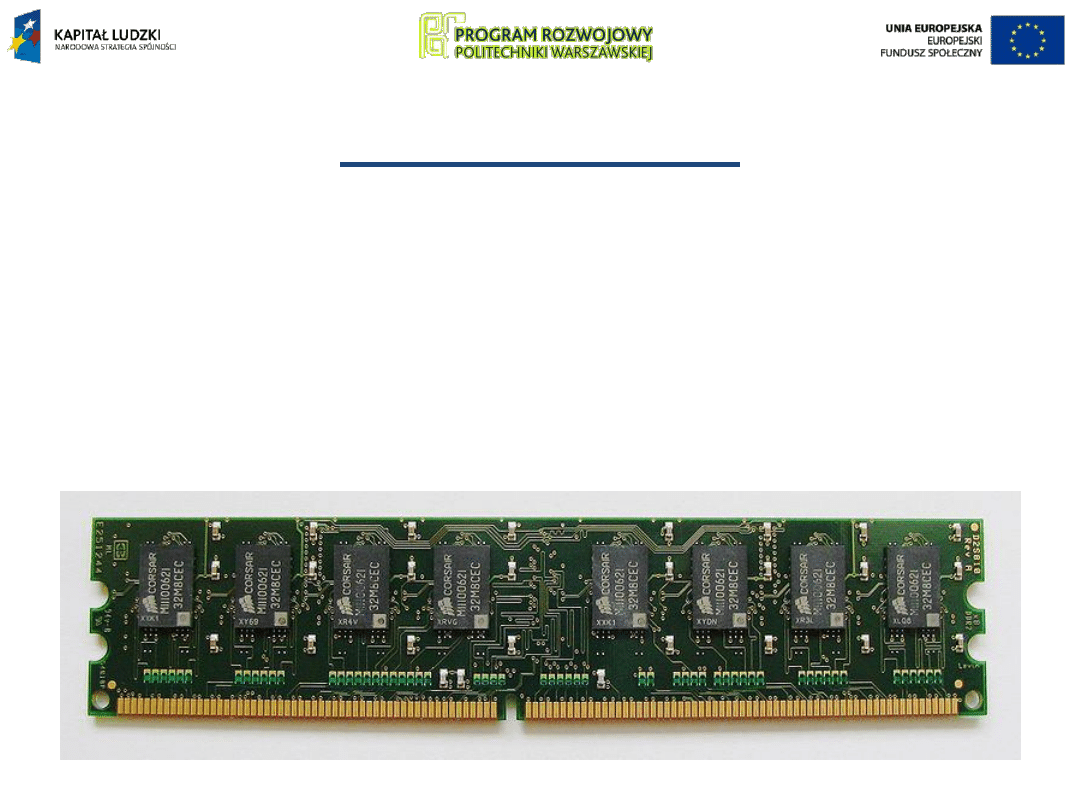

W celu zwiększenia pojemności i (lub) długości słowa,

produkowane są moduły pamięci statycznych RAM,

zawierające na małej prostokątnej płytce drukowanej kilka

odpowiednio połączonych układów S-RAM

.

16

ETR 8.10

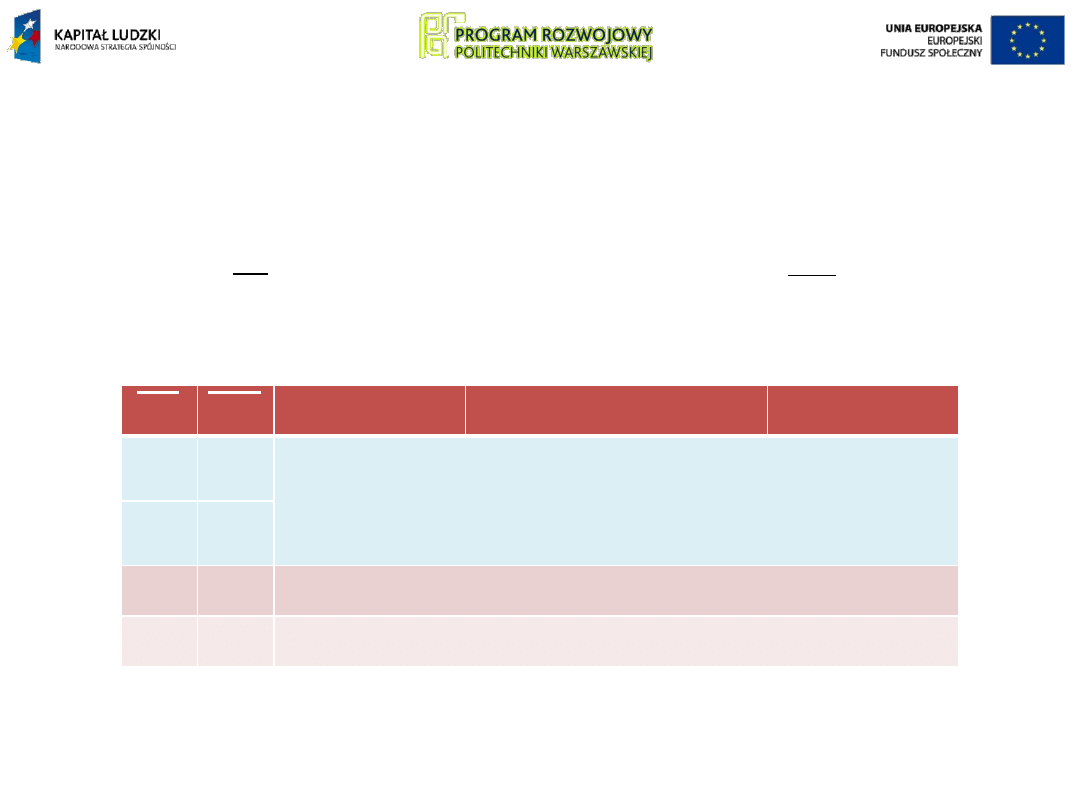

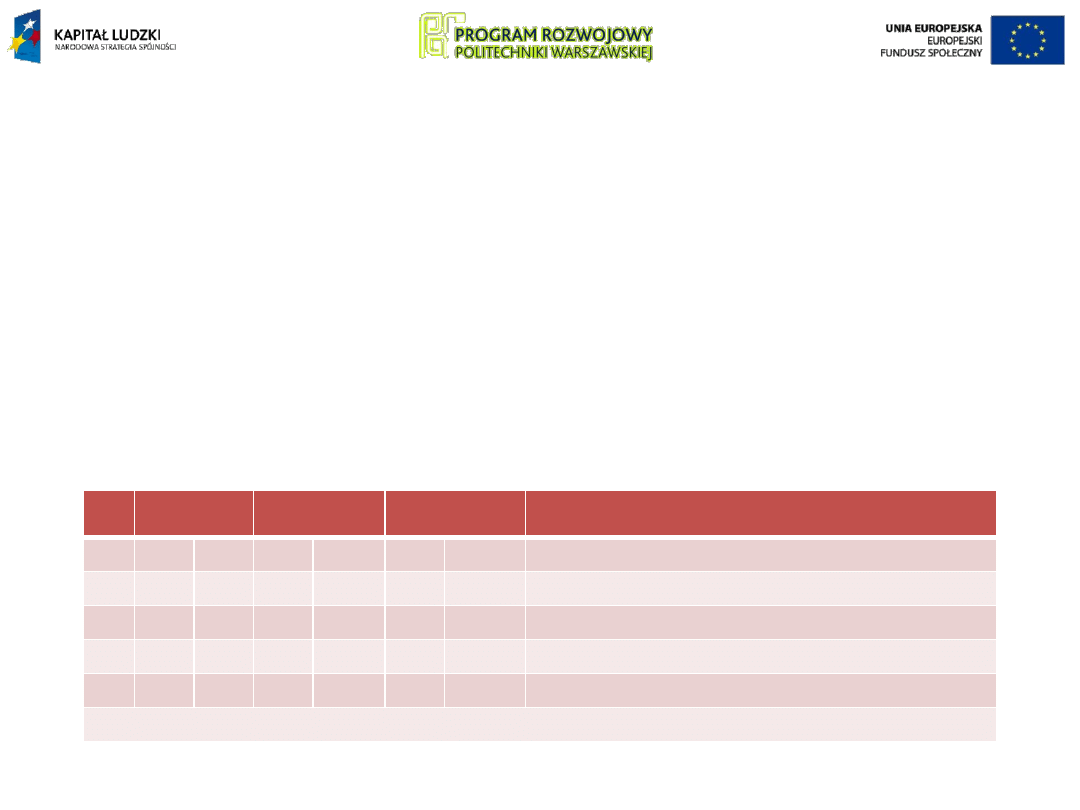

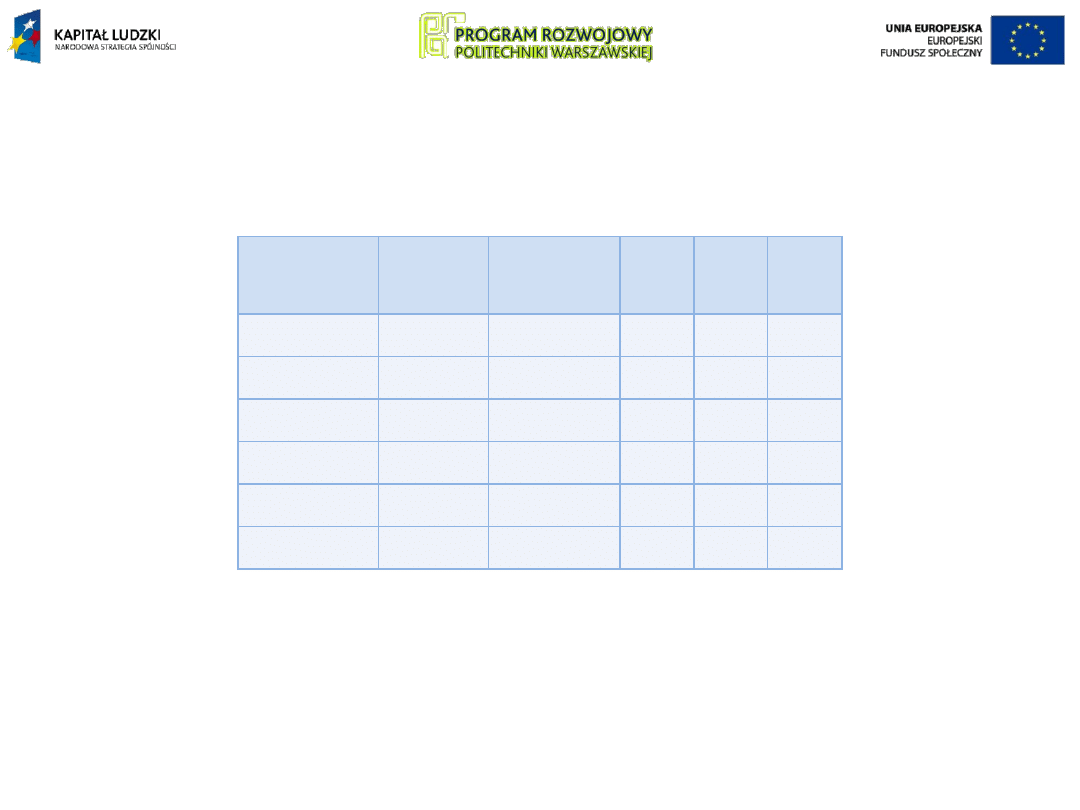

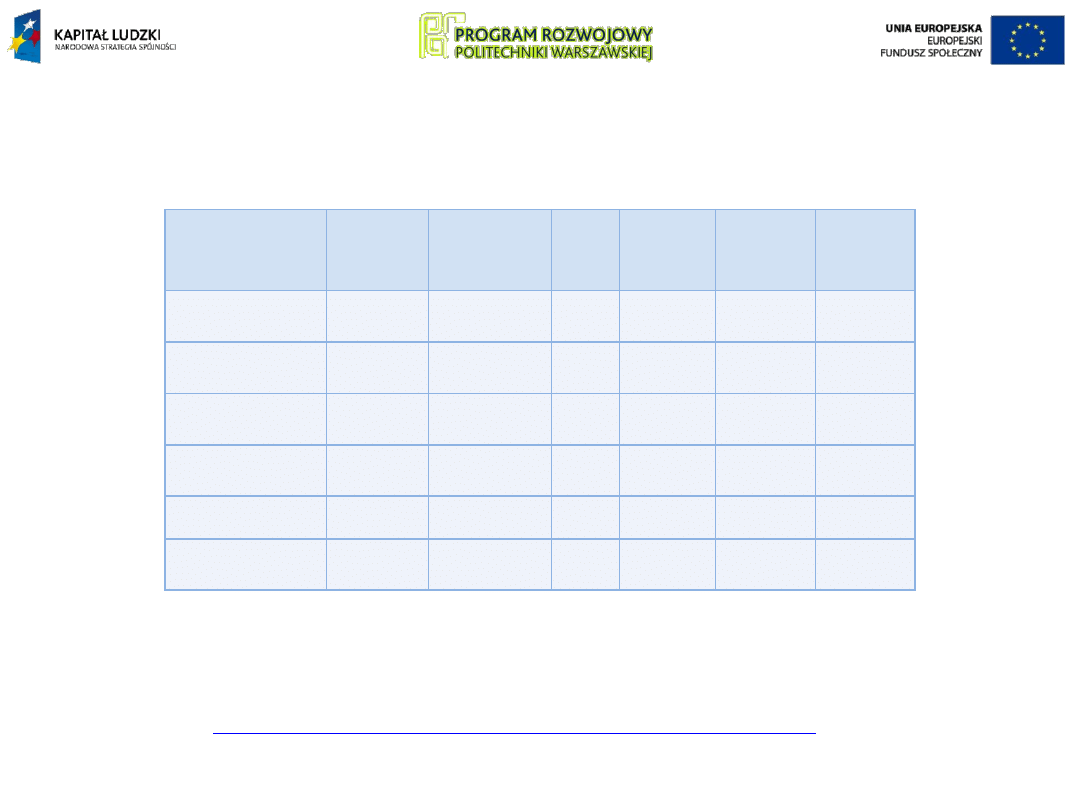

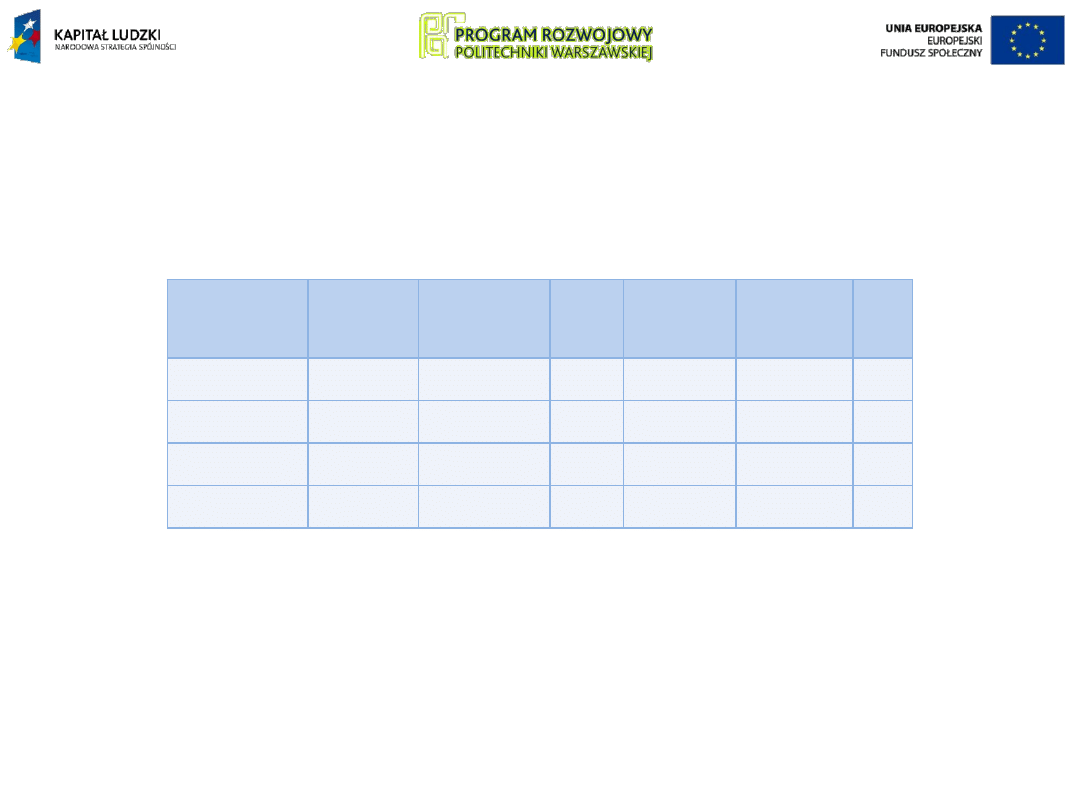

Dane kilku typów pamięci statycznych RAM firmy Hitachi

17

Typ

Pojemność

Organizacja

Proces

Czas dostępu

[ns]

Liczba nóżek

HM6716-25

16 Kb

2048 x 8

Bi-CMOS

25

24

HM6289-25

64 Kb

16384 x 4

CMOS

25

24

HM628128-7

1 Mb

131072 x 8

CMOS

70

32

HM621100A-20

1 Mb

1048576 x 1

CMOS

20

28

HM628512-5

4 Mb

524288 x 8

CMOS

55

32

ETR 8.10

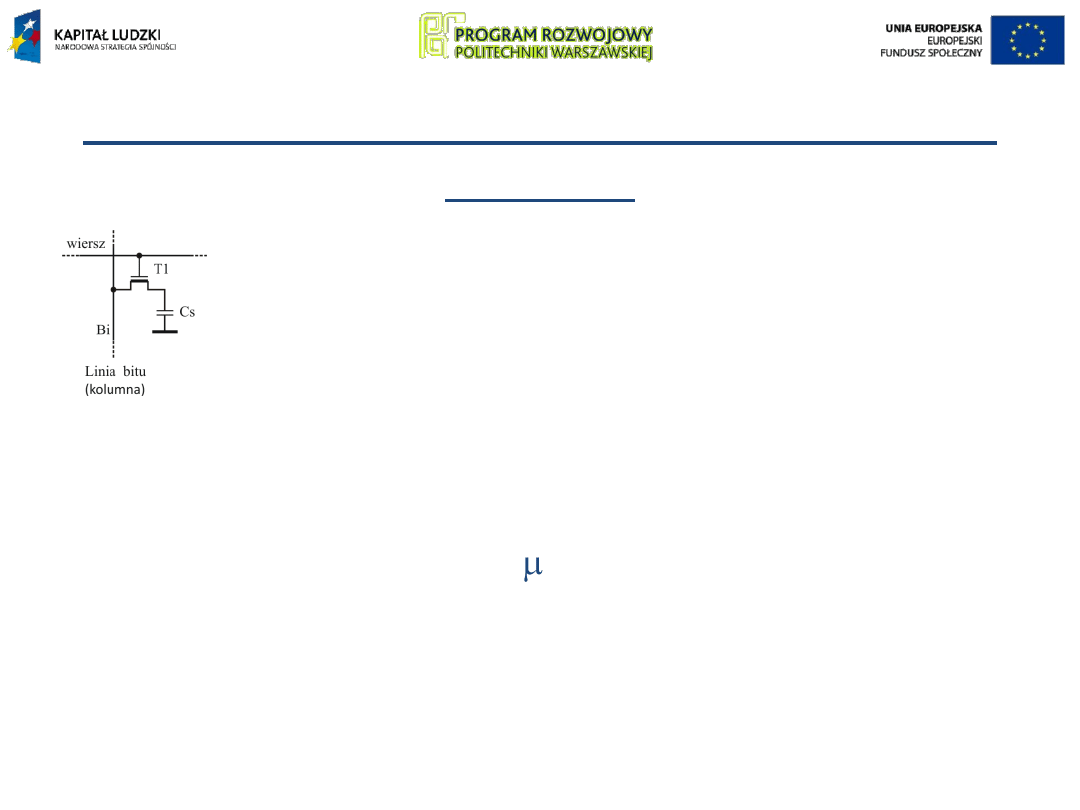

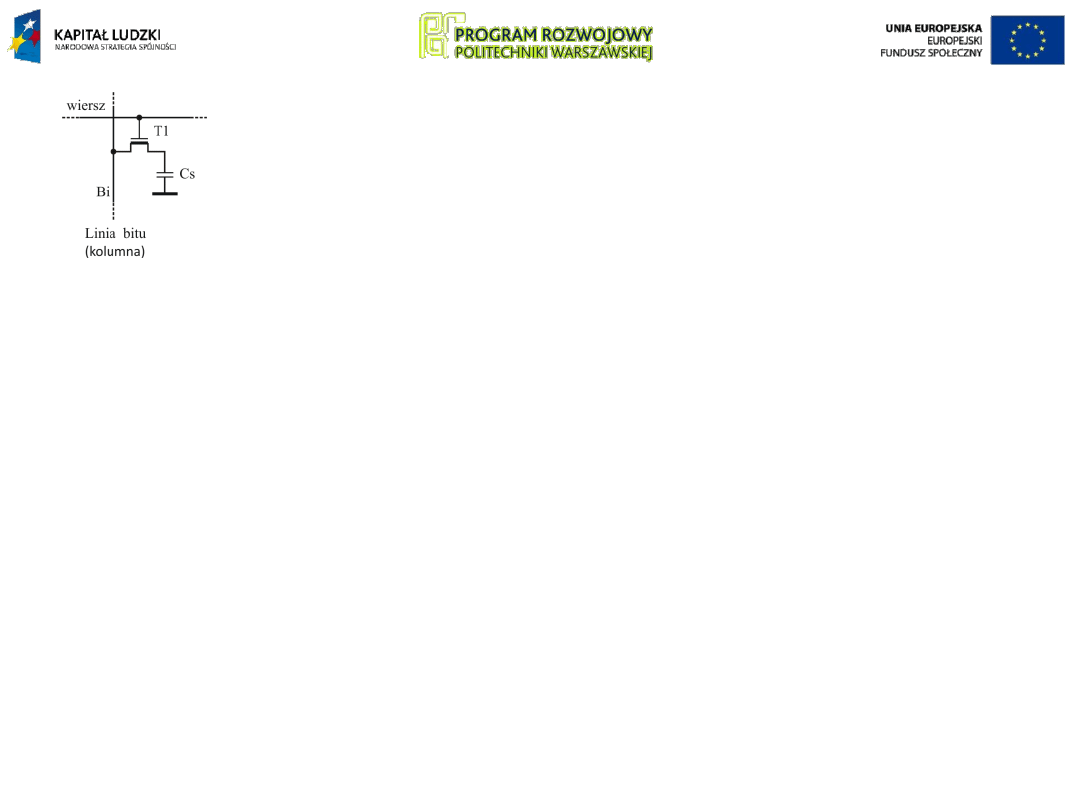

3. Pamięci dynamiczne do zapisu i odczytu

(D-RAM)

Pamięciami dynamicznymi RAM (D-RAM)

nazywa się pamięci, w których

stan bitu

przechowuje się w odpowiednio naładowanym

lub rozładowanym kondensatorze

.

Elementarna komórka pamięci dynamicznej zawiera tylko

dwa elementy: tranzystor MOS i kondensator

o bardzo

małej pojemności i powierzchni. Cała komórka jest bardzo

mała (rzędu kilku, np. 20 m

2

), co umożliwia budowę

pamięci o wielkich pojemnościach. Uzyskuje się przy tym

bardzo małą powierzchnię, koszt i moc strat na jeden bit

przechowywanej informacji.

18

ETR 8.10

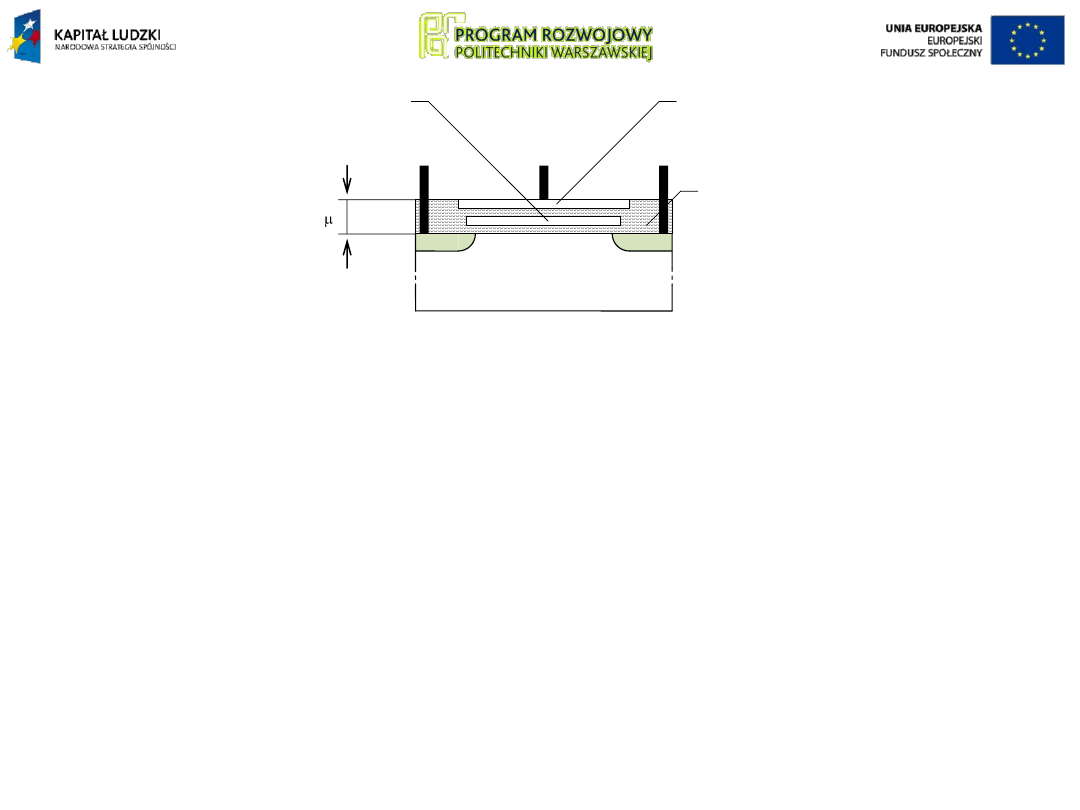

Podstawowym elementem pamięciowym jest

kondensator

C

s

o pojemności rzędu 50 fF (50 x

10

-15

F).

Tranzystor T1 stanowi

klucz

, dołączający kondensator do

linii bitu (kolumny) B

i

po ustawieniu stanu 1 na połączonej z

bramką T1 linii wyboru wiersza.

W procesie

zapisu

pamięci do komórki wpisuje się stan 1

przez ustawienie B

i

=1 i naładowanie kondensatora C

s

. Stan

0 wpisuje się przez ustawienie B

i

=0 i rozładowanie

kondensatora. W procesie odczytu, kondensator dołączony

do B

i

zmienia na tej linii wartość napięcia, a połączony z B

i

wzmacniacz odczytu ustawia na linii wyjścia danych

pamięci odpowiednio stan 1 lub 0.

19

ETR 8.10

Po odłączeniu komórki pamięci od linii bitu kondensator

zachowuje trwale

odpowiadający logicznemu zeru

stan

rozładowania

. Kondensator zachowuje również

przez pewien

czas

odpowiadający logicznej jedynce

stan naładowania

.

Jednakże ze względu na nieuniknione upływności kondensator

rozładowuje się i nie zachowuje ładunku, odpowiadającemu

stanowi 1 w sposób trwały. Aby nie dopuścić do rozładowania

kondensatora i zmiany stanu z 1 na 0, ładunek zgromadzony w

kondensatorze w stanie 1 musi być co pewien czas odtwarzany

w procesie, zwanym

odświeżanie pamięci

(ang.

refresh

).

Odświeżanie polega na odczytaniu stanu komórki pamięci i po

stwierdzeniu stanu 1 doładowaniu kondensatora pełnym

ładunkiem, takim jak w procesie zapisu. Odświeżanie jest

realizowane podczas każdego odczytu komórki. Ponadto, aby

uniknąć utraty zawartości w przypadku długich przerw w

odczycie pamięci, realizowane musi być okresowo przez

specjalne

dodatkowe układy odświeżania

.

20

ETR 8.10

Układy do odczytu i doładowywania komórki znajdują się w

każdej kolumnie matrycy pamięciowej i realizują odtwarzanie

stanu 1 jednocześnie we wszystkich kolumnach aktualnie

wybranego wiersza matrycy, nie tylko w m kolumnach,

odczytywanych w procesie odczytu pamięci, których stan

wyprowadzany jest na linie wyjścia danych. Ponadto

odświeżanie może być realizowane także bez wyprowadzania

danych na linie wyjściowe. Okresowe odświeżanie całej pamięci

polega

zatem

na aktywacji kolejnych wierszy matrycy na czas,

niezbędny do wykonania operacji rozpoznania i odtworzenia

stanów 1

. Dla uniknięcia straty zawartości pamięci cykle

aktywacji kolejnych wierszy muszą być powtarzane w czasie, nie

przekraczającym ustalonego progu bezpieczeństwa,

wynoszącego kilka do kilkunastu ms. Przykładowo, w pamięci o

pojemności 4Mb okres powtarzania aktywacji

1024

wierszy

matrycy wynosi 16 ms.

21

ETR 8.10

Odpowiednie układy odświeżania buduje się z elementów

TTL / LS lub specjalizowanych układów scalonych, np.

Intel 8203. W komputerach typu IBM/PC XT do odświeżania

dynamicznej pamięci operacyjnej wykorzystany był jeden z

kanałów odpowiednio zaprogramowanego kontrolera

bezpośredniego dostępu do pamięci (DMA). W nowszych

komputerach IBM/PC odświeżanie pamięci realizuje układ

sterownika płyty głównej.

22

ETR 8.10

Aby zmniejszyć rozmiary i liczbę końcówek obudowy oraz

uprościć układy odświeżania, w pamięciach dynamicznych

stosuje się

mechanizm multipleksowania adresu

.

Adres wprowadzany jest na dwukrotnie mniejszą liczbę

końcówek adresowych w dwóch porcjach.

Najpierw podaje się na linie adresowe

starszą część

adresu

i za pomocą specjalnego sygnału

RAS

(ang. Row

Address

Strobe) zatrzaskuje się tą część adresu w

umieszczonym wewnątrz pamięci rejestrze adresu wiersza.

Następnie podaje się na linie adresowe

młodszą część

adresu

i za pomocą specjalnego sygnału

CAS

(ang.

Column Address

Strobe) wpisuje te wartości do rejestru

adresu kolumn. Sygnał CAS odblokowuje ponadto bufory

wejścia / wyjścia danych, pełniąc jednocześnie funkcję

sygnału CS (Chip Select).

23

ETR 8.10

Symbol pamięci dynamicznej RAM z rozdzielonymi (a) i

wspólnymi (b) liniami wejścia / wyjścia danych oraz

schemat blokowy wewnętrznej struktury pamięci:

24

I

0

I

1

I

m-1

O

0

O

1

O

m-1

A

0

A

1

A

n/2-2

A

n/2-1

RAS

CAS

WE

a)

A

0

A

1

A

n/2-2

A

n/2-1

RAS

CAS

WE

b)

D

0

D

1

D

m-1

Matryca

komórek pamięci

256Kb

512x512x1

Wzmacniacze

zapisu / odczytu

Obwody

wejścia /wyjścia

Dekoder kolumn

Rejestr adresu

kolumn

I

D

O

D

Rejestr

adresu

wiersza

Dekoder

wiersza

Obwody

sterowania

A

0

A

8

RAS

CAS

WE

ETR 8.10

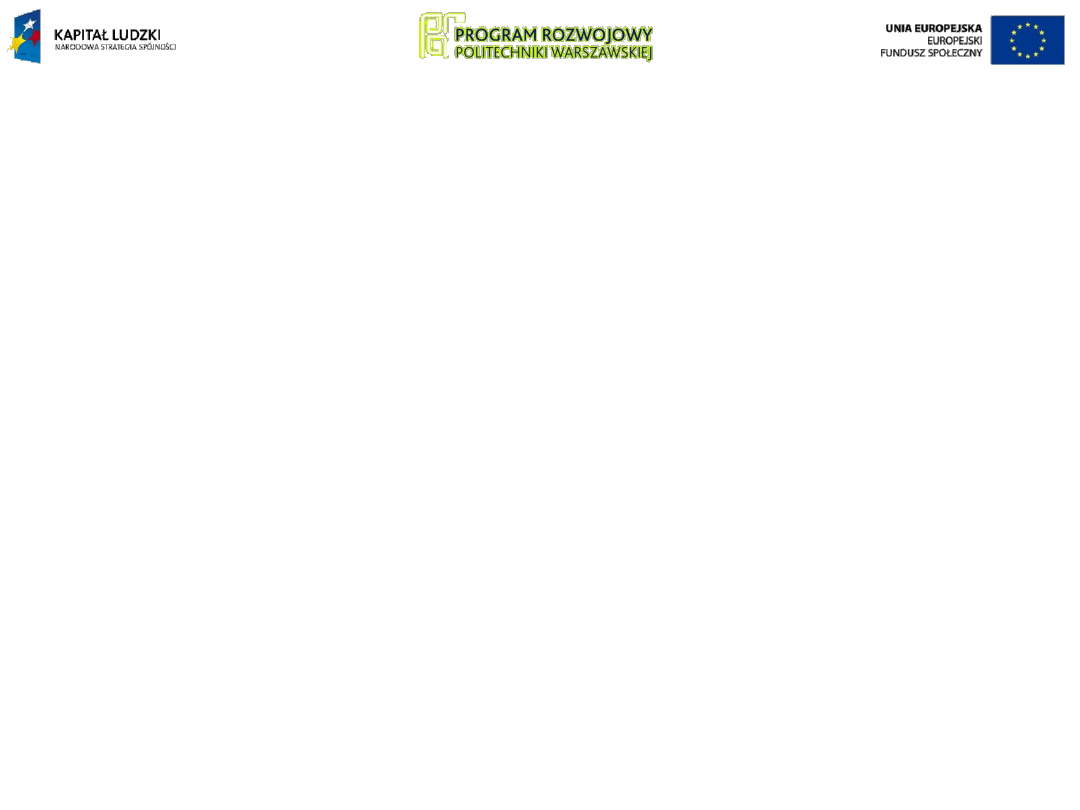

Przebiegi czasowe

sygnałów przy odczycie

(a) i zapisie (b) pamięci

D-RAM:

• t

RC

–

czas cyklu odczytu

lub zapisu

.

25

WE 1

Adres

RAS

stan wysokiej impedancji

Dane

(wyjście)

Adres

Dane stabilne

a)

CAS

t

RCD

t

AA

t

CAC

t

RAC

dane

ważne

stan wysokiej impedancji

Dane

(wyjście)

Dane

(wejście)

b)

RAS

CAS

adres

kolumny

adres

kolumny

adres

wiersza

t

RC

t

RC

adres

wiersza

WE

ETR 8.10

Adres wiersza jest zatrzaskiwany przy zmianie sygnału RAS z 1

na 0. Następnie, przy zmianie sygnału CAS z 1 na 0

zatrzaskiwany jest adres kolumny.

Przy

WE=1, po czasie t

RAC

od zmiany

RAS i czasie t

CAC

po

zmianie

CAS na liniach wyjścia danych pojawiają się dane,

zapisane w zaadresowanym słowie pamięci.

Jeśli natomiast przy opadającym zboczu CAS sygnał WE=0,

zamiast odczytu realizowany jest zapis danych, występujących w

tym momencie na liniach wejścia. Odpowiednie dane muszą być

przygotowane wcześniej, przed zmianą CAS.

Zapis może być także opóźniony względem CAS (

delayed write

),

jeśli przy opadającym zboczu CAS sygnał WE jest równy 1 a

później zmieni się na 0 przy CAS utrzymanym w stanie 0. Jeżeli

od zmiany

CAS do zmiany WE upływa czas większy od t

CAC

,

następuje także odczyt danych. Realizowany jest wówczas w

jednym cyklu odczyt i zapis tej samej komórki pamięci (

read -

modify - write cycle

).

26

ETR 8.10

Szybkość działania pamięci D-RAM charakteryzuje się

przez podanie czasu dostępu do danych od zmiany

sygnału RAS (t

RAC

-

access time from

RAS). Czas ten jest

rzędu 50 do 100 ns. Całkowity czas normalnego cyklu

zapisu lub odczytu t

RC

(random read or write cycle) jest ok.

dwa razy dłuższy. Czasy te są znacząco dłuższe od takich

samych czasów pamięci statycznych.

We współczesnych pamięciach D-RAM można jednak

wydatnie skrócić czas cyklu odczytu i zapisu, jeżeli

korzysta się z komórek, należących do jednego wiersza

matrycy pamięci. Nie ma wówczas potrzeby zmiany adresu

(numeru) wiersza, wystarczy zmieniać adresy (numery)

kolumn. Praca przy stałym adresie wiersza określana jest

jako

praca w trybie szybkiego dostępu

(high speed access

mode).

27

ETR 8.10

praca w trybie szybkiego dostępu:

• tryb szybkiego stronicowania (Fast Page Mode - FPM),

polega na ustaleniu adresu wiersza ujemnym skokiem

RAS i

następnie przy utrzymaniu RAS=0 zmianie tylko adresu

kolumny i sygnału CAS;

• tryb statyczny kolumn (static column mode), polega na

utrzymywaniu

RAS=0 i CAS=0 a zmianie tylko adresu kolumn,

bez synchronizacji skokiem ujemnym

CAS;

• tryb wyprowadzania czwórek (nibble mode) w specjalnych

rodzajach pamięci, w których po ustaleniu adresu wiersza i

adresu początkowego kolumny cztery kolejne ujemne skoki

sygnału CAS powodują wyprowadzenie zawartości czterech

kolejnych komórek pamięci bez zmiany adresu kolumny.

Wymienione wyżej tryby szybkiego dostępu skracają zarówno

czas cyklu odczytu jak i zapisu

28

ETR 8.10

Dalsze skrócenie cyklu odczytu (ale nie zapisu) uzyskuje się przy pracy

w trybie szybkiego stronicowania (FPM) i dodatkowo przedłużeniu

czasu odczytu danych tak, że odczytane informacje pozostają na

liniach wyjścia danych także wtedy, gdy sygnał CAS przestaje być

aktywny i przyjmuje wartość 1 (Extended Data Out - EDO). Pozwala to

na skrócenie impulsu CAS i generowanie kolejnego adresu kolumny

jeszcze w trakcie odczytu danych, nie czekając na zakończenie

operacji odczytu. Cykl odczytu jest przy tym krótszy o ok. 10...15% od

cyklu odczytu w trybie szybkiego stronicowania.

W pamięci o czasie dostępu 60 ns i czasie cyklu 110 ns poszczególne

tryby skróconego dostępu pozwalają na uzyskanie następujących

czasów cyklu:

29

tryb szybkiego stronicowania

40 ns

tryb statyczny kolumn

35 ns

tryb szybkiego stronicowania z przedłużonym odczytem (EDO)

25 ns

tryb wyprowadzania czwórek

15 ns

ETR 8.10

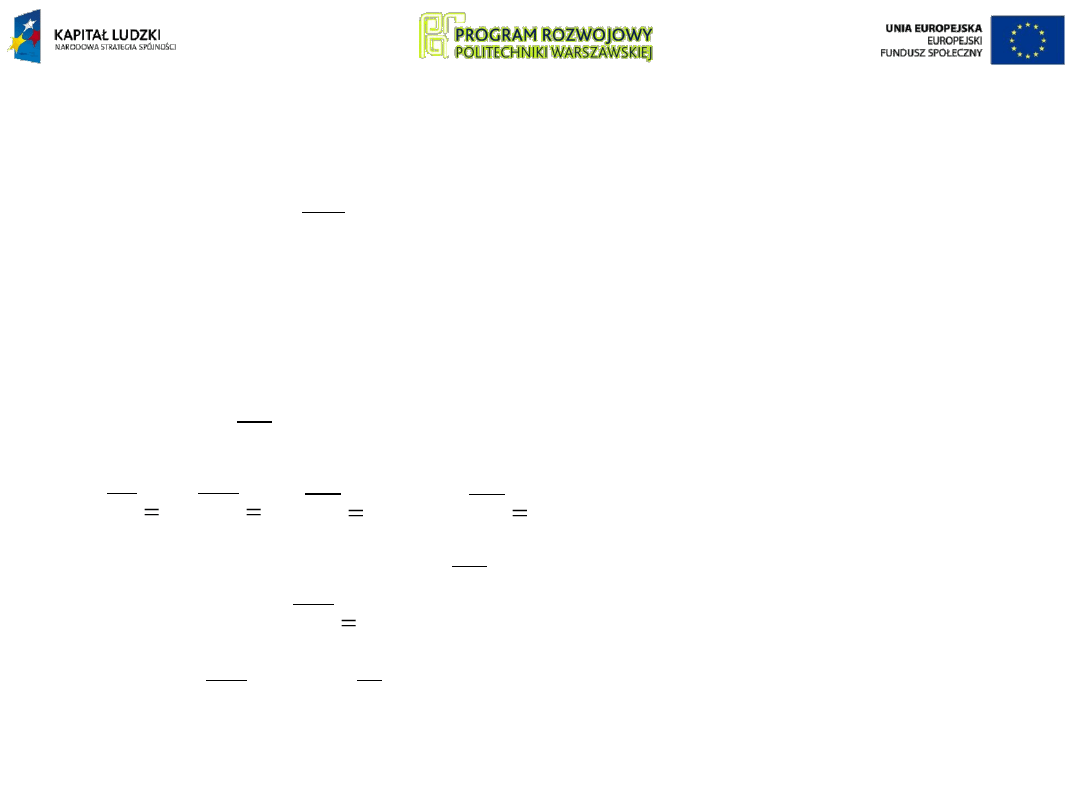

Inną szybką odmianą pamięci dynamicznych są

pamięci

synchroniczne

(Synchronous DRAM -

SDRAM

). Pamięci

takie zawierają programowane struktury, obsługujące

potokowo, w dużych paczkach danych, kilka (co najmniej

dwa) banki komórek pamięci w sposób, taktowany zegarem

zsynchronizowanym z zegarem systemu

mikrokomputerowego. Pamięci SDRAM umożliwiają płynny

transfer danych z częstotliwością do kilkuset MHz (z

okresem rzędu kilkunastu ns).

30

PC-3200

(DDR-400)

PC2-6400

(DDR2-800)

PC3-12800

(DDR3-1600)

cykle

czas

cykle

czas

cykle

czas

t

CL

3

15 ns

5

12,5 ns

9

11,25 ns

CAS

low to valid data out (equivalent to t

CAC

)

t

RCD

4

20 ns

5

12,5 ns

9

11,25 ns

RAS

low to

CAS

low time

t

RP

4

20 ns

5

12,5 ns

9

11,25 ns

RAS

precharge time (minimum precharge to active time)

t

RAS

8

40 ns

16

40 ns

27

33,75 ns

Row active time (minimum active to precharge time)

z en.wikipedia.org/wiki/Dynamic_random_access_memory

ETR 8.10

Współczesne pamięci dynamiczne mają wbudowane w strukturę

układy, ułatwiające odświeżanie. Układy takie generują

wymaganą przy odświeżaniu sekwencję adresów wierszy, co

usuwa potrzebę podawania tych adresów przez układ

zewnętrzny. Operację odświeżania kolejnego wiersza inicjuje się

po prostu przez podanie sygnału, którym jest najczęściej nie

stosowana w innych cyklach pracy sekwencja „

CAS przed RAS

"

(

CAS - before – RAS refresh). Operację odświeżania można w

ten sposób zainicjować także pod koniec cyklu zapisu lub

odczytu, jeżeli przy CAS utrzymywanym w stanie 0 wprowadzi

się dodatkowy cykl zmiany RAS. Odświeżany jest wiersz o

numerze ustalonym przez wewnętrzny licznik odświeżania, a nie

wiersz zaadresowany w operacji zapisu czy odczytu. Takie

odświeżanie nosi nazwę "

ukrytego

" (hidden refresh

), gdyż cykl

odświeżania jest ukryty w końcu normalnego cyklu pracy.

31

ETR 8.10

Współczesne pamięci dynamiczne mają wbudowane układy

przyspieszające testowanie każdej z milionów komórek pamięci,

przeprowadzane np. przy włączaniu komputera typu IBM/PC. W

pamięci 16 Mb firmy Hitachi testowanie jest uruchamiane przez

sekwencję sygnałów „WE i CAS przed RAS", po czym dane są

wpisywane jednocześnie w 16 komórek pamięci i następnie

odczytywane. Jeżeli wszystkie 16 komórek zawierają prawidłowe

dane, linie wyjścia danych pozostają w stanie wysokiej

impedancji. Jeżeli zawartość choć jednej komórki jest

nieprawidłowa, linie wyjścia danych wprowadzane są w stan 0.

Pamięci o bardzo dużej pojemności pracują przy obniżonym

napięciu zasilania w celu zmniejszenia wydzielanej w układzie

mocy.

Produkowane są także moduły pamięci dynamicznych,

zawierające kilka połączonych w większe bloki układów D-RAM.

Współczesne pamięci dynamiczne są bardzo złożonymi

strukturami a projektowanie i wytwarzanie tych pamięci stanowi

obok rozwoju mikroprocesorów wiodącą gałąź mikroelektroniki.

32

ETR 8.10

4. Pamięci stałe, tylko do odczytu,

programowane przez producenta (ROM).

Pamięci stałe, tylko do odczytu, programowane przez

producenta (ROM), stosowane są

w produkowanych

seryjnie urządzeniach

elektronicznych, wymagających

użycia pamięci o stałej zawartości

Układ ma:

• n linii adresowych (A

0

... A

n-1

);

• m linii wyjścia danych (D

0

... D

m-1

);

• jedno lub dwa wejścia selekcyjne: (CS Chip

Select - selekcja struktury) i (

OE Output

Enable -

dozwolone wyjście).

33

A

0

A

1

A

2

A

3

A

4

A

5

A

6

A

n-2

A

n-1

OE

CS

D

0

D

1

D

2

D

m-3

D

m-2

D

m-1

ETR 8.10

Przy

CS=0 i OE=0 pamięć wyprowadza na linie wyjścia

danych wartość jednego z 2

n

słów o numerze (adresie)

ustawionym na liniach adresowych. Dane wyprowadzane

są z opóźnieniem względem zmiany adresu i sygnałów

sterujących, podobnie jak w pamięci RAM. Przy OE=1 lub

CS=1 linie wyjścia danych znajdują się w stanie wysokiej

impedancji i nie wpływają na dołączone do nich linie

przesyłania danych. Przy CS=1 cała pamięć jest

nieaktywna i przechodzi zwykle w stan zmniejszonego

poboru prądu (mocy).

Pamięć ROM zawiera matrycę komórek, kodujących

wartości poszczególnych bitów, sterowane liniami

adresowymi dekodery kolumny i wierszy matrycy,

wybierające komórki, odpowiadające określonemu słowu

pamięci oraz sterowany wejściami selekcyjnymi zespół

trójstanowych buforów wyjściowych. Zespoły te są ze sobą

powiązane podobnie, jak w pamięci RAM.

34

ETR 8.10

W każdej komórce matrycy ROM,

na przecięciu wiersza i kolumny

,

umieszczony jest tranzystor MOS,

włączony między masę a biegnącą

wzdłuż kolumny linię bitu,

dołączoną poprzez obciążenie

rezystancyjne R do napięcia

zasilającego

+V

DD

.

Bramki tranzystorów dołączone są do linii wiersza lub nigdzie nie

dołączone. Jeden wybrany wiersz matrycy ma linię wiersza

ustawioną w stan 1, co odpowiada dołączeniu linii do napięcia

bliskiego +V

DD

.

Tranzystory z bramkami

, dołączonymi do tej linii

zostają wprowadzone w stan silnego przewodzenia i zwierają

linię bitu do masy, ustawiając na niej

stan 0

. Linie bitu z

tranzystorami

o bramkach nie połączonych

z linią wiersza są

utrzymywane przez R

w stanie 1

. Tranzystory należące do

innych, nie wybranych wierszy, o liniach wiersza w stanie niskim

(0) nie przewodzą i nie wpływają na stan linii bitów.

35

R

R

R

R

wiersz 0

+V

DD

wiersz 1

wiersz 2

wiersz w

B

0

B

1

B

2

B

3

linie bitów:

ETR 8.10

Kodowanie

stanu poszczególnych bitów pamięci

polega na

wykonaniu połączenia bramki tranzystora

matrycy z linią wiersza

lub nie wykonaniu takiego połączenia

. W prezentowanym

przykładzie struktury ROM w poszczególnych wierszach

zakodowane są następujące słowa: wiersz 0: 0110; wiersz 1:

1010; wiersz 2: 0000; wiersz w: 1001

.

Połączenia wykonywane są w trakcie jednego z cykli

wytwarzania układu pamięci przy użyciu odpowiedniej maski

fotograficznej linii połączeń, przygotowanej według danych

dostarczonych przez zamawiającego układ pamięci. Pamięci

nazywa się wobec tego "

programowanymi przez producenta

" lub

"

programowane maską

„. Programowanie maską jest procesem

jednorazowym i nieodwracalnym. W wykonanej pamięci nie

można wprowadzić żadnych zmian. Pamięci ROM stosuje się

tylko w finalnych wyrobach, po starannym przygotowaniu i

zbadaniu modeli i prototypów, przy odpowiednio dużej serii

produkcyjnej.

36

ETR 8.10

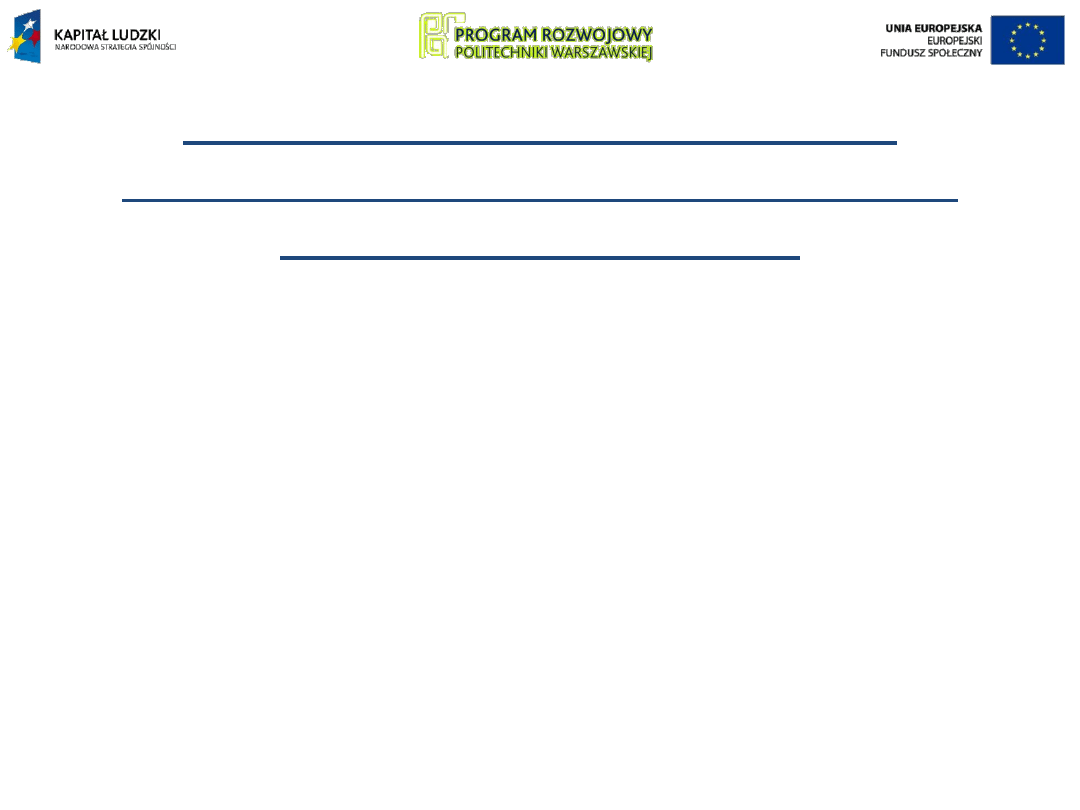

Dane kilku typów pamięci ROM firmy Hitachi

:

Typ

Pojemność

Organizacja

Proces

Czas

dostępu

[ns]

Liczba

nóżek

HN623557

256 Kb

32768 x 8

CMOS

120

28

HN62331

1 Mb

131072 x 8

CMOS

120

28

HN62422

2 Mb

262144 x 8

CMOS

170

32

HN62314B-15

4 Mb

524288 x 8

CMOS

150

32

HN62308B-15

8 Mb

1048576 x 8

CMOS

150

32

HN62442B

16 Mb

1048576 x 16

CMOS

100

40

37

ETR 8.10

5. Pamięci stałe do wielokrotnego

programowania i kasowania przez

użytkownika (EPROM).

Matryca pamięci EPROM o strukturze jak w

zwykłej pamięci MOS ROM zawiera w komórce

pamięci tranzystor MOS o specjalnej konstrukcji.

Najczęściej stosowane są tranzystory o opracowanej w

1971 r. przez firmę Intel strukturze FAMOS (Floating gate

Avalanche - injected MOS).

Przy niewielkich potrzebach ilościowych, zwłaszcza w fazie

projektowania i konstruowania systemu, używane są

pamięci stałe, które mogą być wielokrotnie programowane i

kasowane przez użytkownika. Pamięci takie nazywane są

EPROM

(Erasable and Programmable ROM).

38

R

T

i

B

i

+V

DD

linia bitu

(kolumna)

wiersz

ETR 8.10

Tranzystor FAMOS zawiera dwie bramki: normalną,

sterująca (control gate), dołączoną do linii wiersza oraz

dodatkową, umieszczoną między bramką sterującą a

kanałem.

Bramka ta, zwana swobodną

(floating gate)

jest

całkowicie zatopiona

w izolującym dwutlenku krzemu SiO

2

i

nie ma żadnego doprowadzenia.

Bezpośrednio po

wykonaniu

, po doprowadzeniu do linii wiersza napięcia

rzędu +5V, odpowiadającego stanowi 1,

tranzystor taki

przewodzi i wymusza na linii bitu stan 0

.

39

n

+

n

+

bramka swobodna

bramka sterująca

Źródło S

Bramka G

Dren D

SiO

2

podłoże p

1 m

ETR 8.10

Właściwości tranzystora FAMOS można zmienić

w procesie

programowania pamięci

, podczas której do linii wiersza i

połączonej z nią bramki sterującej tranzystora oraz linii bitu i

połączonego z nią drenu tranzystora doprowadza się

napięcie

rzędu 10 ... 25 V

, znacznie większe od występującego w

normalnej pracy napięcia V

DD

= +5V. Pod wpływem tego napięcia

miedzy źródłem i drenem indukuje się przewodzący kanał, przez

który przepływają elektrony z obszaru n źródła. Podwyższone

napięcie wytwarza w kanale silne pole elektryczne o natężeniu,

przekraczającym 10

5

V/cm

. Przepływające elektrony są silnie

przyspieszane przez to pole i osiągają dużą energię. Część z

nich, przyciągana przez wysoki dodatni potencjał bramki

sterującej pokonuje cienką (poniżej 100 nm) warstwę SiO

2

między kanałem i bramką swobodną i osadza się na tej bramce.

Po usunięciu podwyższonego napięcia, używanego przy

programowaniu, elektrony nie mogą opuścić bramki swobodnej,

gdyż nie dysponują energią, umożliwiającą pokonanie SiO

2

.

40

ETR 8.10

Przy normalnym napięciu zasilającym V

DD

= +5V, po

doprowadzeniu do linii wiersza napięcia rzędu +5V,

odpowiadającego stanowi 1,

tranzystor z naładowaną ujemnymi

elektronami bramką swobodną nie przewodzi

, gdyż ujemny

ładunek bramki swobodnej osłabia działanie dodatniego napięcia

bramki sterującej.

Linie bitów

, dołączone do tranzystorów z

osadzonymi na bramce swobodnej elektronami nie są zwierane

do masy przez nie przewodzące tranzystory i

pozostają w stanie

jeden

.

W procesie odczytu linie bitów wybranego przez adres słowa

dołączone są do linii wyprowadzania danych pamięci poprzez

bufory, realizujące funkcję negacji

.

Tranzystory z nie naładowaną

bramką swobodną wyprowadzają na wyjście jedynkę, a

tranzystory z naładowaną bramką - zero

. W procesie

programowania można w wybranych komórkach pamięci zmienić

naturalny stan pamiętania jedynki na stan pamiętania zera.

41

ETR 8.10

Programowanie

przeprowadza się w sterowanych komputerem

specjalnych programatorach, wykonywanych zwykle jako

przystawka lub karta komputera. Programowanie polega na

doprowadzeniu do pamięci adresu i wymaganej wartości słowa

oraz odpowiednich impulsów podwyższonego napięcia. Pamięci

EPROM wyposażone są w tym celu w dodatkową końcówkę V

pp

,

do której doprowadza się podwyższone napięcie programujące

oraz niekiedy w końcówkę PGM (program), której stan PGM=0

wyznacza czas programowania. W układach, w których nie ma

końcówki PGM czas trwania impulsu programującego wyznacza

impuls

CS=0 przy podwyższonym napięciu V

pp

.

Trwałość zaprogramowanych zer uzależniona jest od czasu

utrzymywania się elektronów w bramce swobodnej i zależy od

jakości izolatora SiO

2

. Trwałość ta jest szacowana na 5 ... 10 lat

(wg danych firmy Intel może wystąpić 2 x 10

-4

% uszkodzeń z

powodu ulotności przez 10 lat).

42

ETR 8.10

Kasowanie

zawartości pamięci EPROM uzyskuje się

przez

naświetlanie

układu pamięci

promieniowaniem

nadfioletowym

o długości fali 2537 Å. Obudowa

pamięci jest w tym celu wyposażona w okienko ze

szkła kwarcowego, umieszczone nad płytką układu

scalonego pamięci.

Promieniowane fotony są absorbowane przez elektrony w

swobodnej bramce, co zwiększa ich energię. Przy odpowiednio

dużej energii elektrony opuszczają bramkę swobodną i

przechodzą przez warstwę tlenku SiO

2

do bramki sterującej lub

podłoża. Do całkowitego skasowania zer w pamięci wymagana

jest dawka promieniowania rzędu 15 W/cm

2

. W typowych

kasownikach EPROM z lampami UV pamięć należy naświetlać

przez 15 do 30 minut. Po naświetlaniu wszystkie komórki

pamięci znajdują się w stanie 1. Kasowaniu podlegają

jednocześnie wszystkie komórki pamięci.

43

ETR 8.10

Pamięć EPROM może być także skasowana przez światło słoneczne

lub sztuczne, jeżeli wystawiona jest na działanie takiego światła przez

kilka lat. Dla uniknięcia tego procesu

okienka pamięci zakleja się

paskiem nieprzezroczystego materiału. Wielokrotne kasowanie i

programowanie zużywa pamięć. Maksymalna liczba cykli

programowania i kasowania jest rzędu 100 do 1000.

Pamięci EPROM mają pojemność od 256 Kb (32768 x 8) do 4 Mb

(524288 x 8 lub 262144 x 16). Czas dostępu jest stosunkowo długi i

wynosi od 70 do 100 ns.

Produkowana jest także

odmiana pamięci EPROM do jednorazowego

programowania

, bez możliwości kasowania, nazywana

OTPROM

(One

Time Programmed

ROM). Są to po prostu

pamięci EPROM w

obudowie bez kwarcowego okienka

. Pamięci takie są tańsze i mogą

być używane w dobrze opracowanych i sprawdzonych produktach.

Pamięci OTPROM są również używane

do zapisywania danych,

których nie wolno kasować

(np. w kasach fiskalnych).

44

ETR 8.10

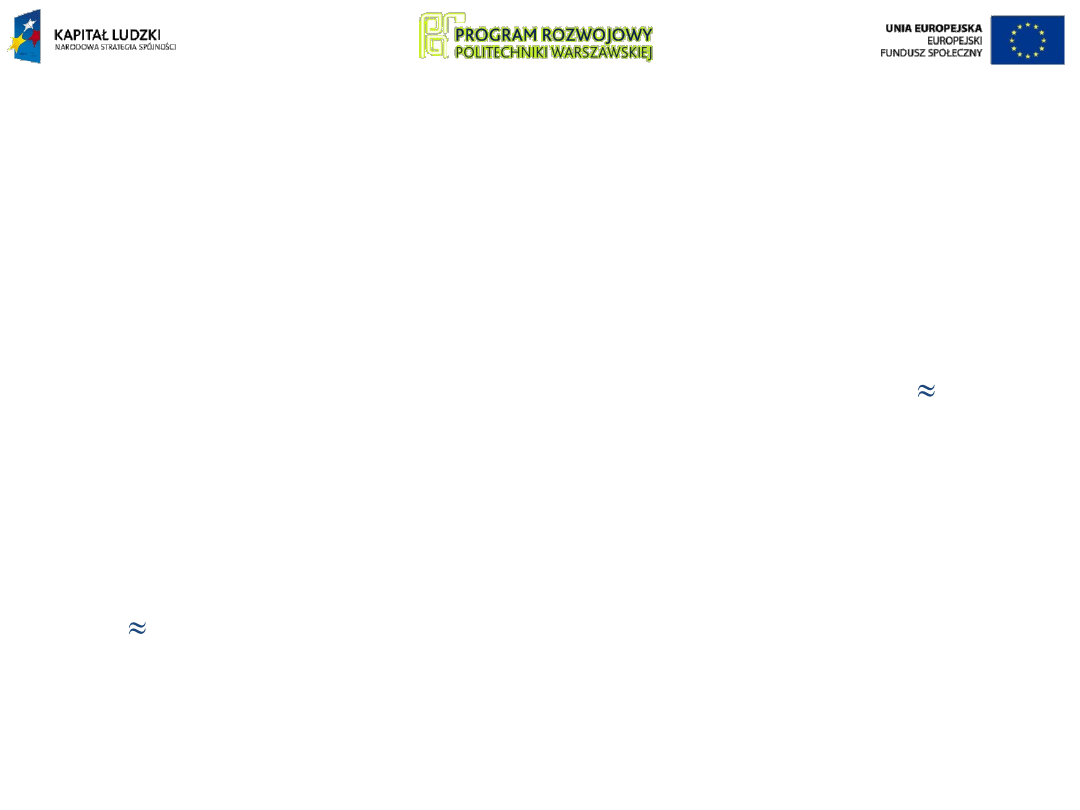

Dane kilku typów pamięci EPROM firmy Hitachi i STMicroelectronics

:

45

Typ

Pojemność

Organizacja

Proces

Czas

dostępu

[ns]

Liczba

nóżek

Cena

[zł.]

(04.2010)

HN27C256H-70

M27C256B-70XF1

256 Kb

32 768 x 8 CMOS

70

28

22,00

HN27C512-17

M27C512-70XF1

512 Kb

65 536 x 8 CMOS

70

28

28,00

HN27C101A-10

M27C1001-70F1

1 Mb

131 072 x 8 CMOS

70

32

23,70

HN27C4001-15

M27C4001-10F1

4 Mb

524 288 x 8 CMOS

100

32

30,90

M27C801-100F1

8 Mb 1 048 576 x 8

100

32

34,00

M27C160-100F1

16 Mb

2Mb x 8

1Mb x 16

100

48

49,20

ETR 8.10

https://www1.elfa.se/elfa3~pl_pl/b2b/init.do?shop=ELFA_PL-PL#toc=19972;

6. Pamięci stałe do wielokrotnego

programowania i kasowania, kasowane

elektrycznie (EEPROM).

Kasowanie i programowanie pamięci EPROM wymaga

wyjęcia pamięci z podstawki w urządzeniu, w którym

pracuje i umieszczenia jej w specjalnym kasowniku i

programatorze. Kasowanie trwa długo, 15 do 30 minut.

Ponadto kasowana jest cała zawartość pamięci nawet

wtedy, gdy w pamięci trzeba zmienić tylko kilka bitów.

Niedogodności tych nie mają pamięci

EEPROM

(Electrically Erasable and Programmable

ROM), których

zawartość może być zmieniana w urządzeniu, w którym

pracują

.

Zmieniać można tylko wybrane słowa pamięci

a

operacja zmiany zawartości trwa krótko.

46

ETR 8.10

Komórki matrycy pamięci EEPROM zawierają zmodyfikowany

tranzystor FAMOS, zwany FLOTOX (Floating Gate Tunnel

Oxide

), w którym wykonano dodatkową bardzo cienką (około 20

nm

) warstwę tlenkową między drenem a bramką swobodną.

Warstwa ta umożliwia przepływ elektronów o dużej energii w obu

kierunkach, z drenu do bramki swobodnej lub odwrotnie,

zależnie od ich wzajemnej polaryzacji. Przy doprowadzeniu do

bramki sterującej podwyższonego napięcia dodatniego U

G

+20V

i napięciu drenu U

D

=0 bramka swobodna jest pojemnościowo

sprzężona z dodatnim potencjałem bramki sterującej i elektrony

są przyciągane do bramki swobodnej z drenu. Bramka

swobodna ładuje się elektronami i komórka pamięci zostaje

zaprogramowana

. Przy normalnym napięciu bramki sterującej

U

G

+5V tranzystor taki nie przewodzi, co odpowiada wpisaniu

zera.

47

ETR 8.10

Z kolei przy U

G

=0 i U

D

+20V bramka swobodna jest opróżniana

z elektronów, które przechodzą do drenu. Komórka pamięci

zostaje

skasowana

. Przy normalnym napięciu bramki sterującej

U

G

+5V tranzystor taki przewodzi, co odpowiada wpisaniu

jedynki. Przy normalnych napięciach na elektrodach, nie

większych od +5V, elektrony przez warstwę tlenku nie

przechodzą i pamięć może być czytana bez zmiany zawartości.

Czas utrzymywania podwyższonego napięcia przy

programowaniu i kasowaniu jest rzędu 10 ms. Ponieważ dren

tranzystora FLOTOX połączony jest z linią bitu i stan zera na linii

bitu jest wymuszany przez ten tranzystor, operacja wpisania

zera, wymagająca U

D

=0, musi być poprzedzona operacją

kasowania komórki. Całkowity czas wpisywania zera trwa zatem

dwa razy dłużej (ok. 20 ms).

48

ETR 8.10

W celu przyspieszenia zapisu w dużych pamięciach EEPROM

skraca się czas programowania i stosuje równoległy zapis wielu

bajtów, wpisanych wcześniej szybko do zespołu rejestrów

zatrzaskowych. Uzyskuje się w ten sposób np. zapis 32 bajtów w

10 ms.

Pamięci EEPROM są znacznie droższe od porównywalnych

pamięci EPROM (ok. 10 razy).

Specyficzną odmianą pamięci, zwaną

Flash EEPROM

, jest

pamięć kasowana w dużych blokach lub w całości w jednej

szybkiej operacji kasowania. Pamięci Flash mają nieco

zmienioną strukturę tranzystora komórki pamięci i są relatywnie

tanie (1,5 ... 2 razy droższe od EPROM).

Pamięci Flash są intensywnie rozwijane i ich możliwości szybko

rosną a cena spada.

49

ETR 8.10

Produkowane są również pamięci, zwane nieulotnymi

pamięciami RAM (NVRAM, Non-Volatile RAM), które zawierają

komórki pamięci statycznej RAM z przerzutnikiem RS, połączone

równolegle z komórkami pamięci EEPROM. Przy wejściu NE

(Non-

Volatile Enable) w stanie 1 zachowują się jak pamięci RAM

o czasach cyklu rzędu 200 300 ns. Przy NE=0 i odczycie

następuje szybkie (10 s) przepisanie stanu komórki EEPROM

do komórki RAM. Przy NE=0 i zapisie następuje zapisanie stanu

komórki RAM do komórki EEPROM w czasie ok. 10 ms. Przy

włączeniu napięcia zasilającego cała treść matrycy EEPROM

jest samoczynnie przepisywana do matrycy RAM.

Czas utrzymywania danych i dopuszczalna liczba cykli

kasowania i programowania pamięci EEPROM jest tego samego

rzędu co pamięci EPROM.

50

ETR 8.10

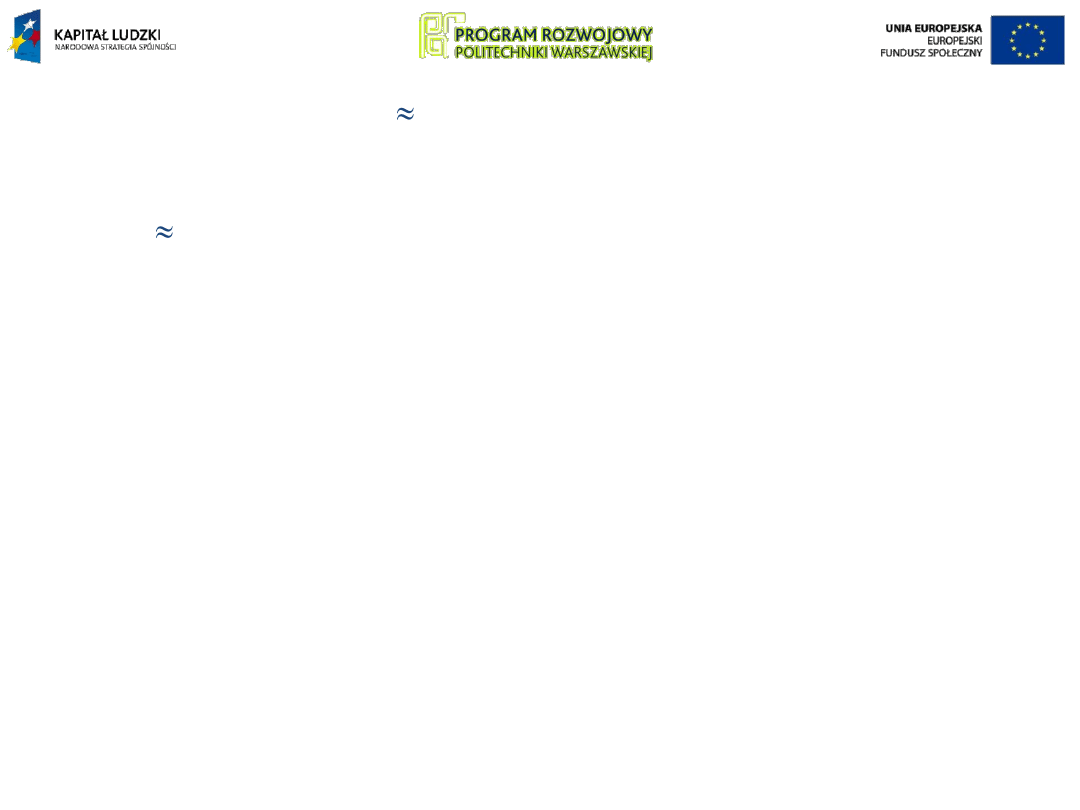

Dane kilku typów pamięci EEPROM firmy Hitachi

:

51

Typ

Pojemność

Organizacja

Proces

Czas

dostępu

[ns]

Liczba nóżek

Typ

HN58C65-25

64 Kb

8193 x 8 CMOS

250

28

HN58C256-20

256 Kb

32768 x 8 CMOS

200

28

HN58C1000-12

1 Mb

131072 x 8 CMOS

120

32

HN29C101-12

1 Mb

131072 x 8 CMOS

120

32

Flash

ETR 8.10

Wyszukiwarka

Podobne podstrony:

10 pamięć utajonaid 10594 ppt

10 pamiec zewnetrzna

10 Dynamiczne przydzielanie pamieci

Ćwiczenia 10 4 XII 2008percepcja sluchowa, Psychologia, poznawcza (percepcja, myślenie, pamięć), ćwi

10 Dynamiczna alokacja pamiecii Nieznany (2)

2009 10 Akwizycja i analiza pamięci

10 rodzajów pamięci, Różne pliki

w 10 procesy pamieciowe

Programy usprawniania pamięci i uwagi 10

pamięci dynamiczne (10 str)

1999 10 Odtwarzacz efektów akustycznych z pamięcią EPROM

10 Metody otrzymywania zwierzat transgenicznychid 10950 ppt

10 dźwigniaid 10541 ppt

więcej podobnych podstron