PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

1

KATEDRA ELEKTRONIKI

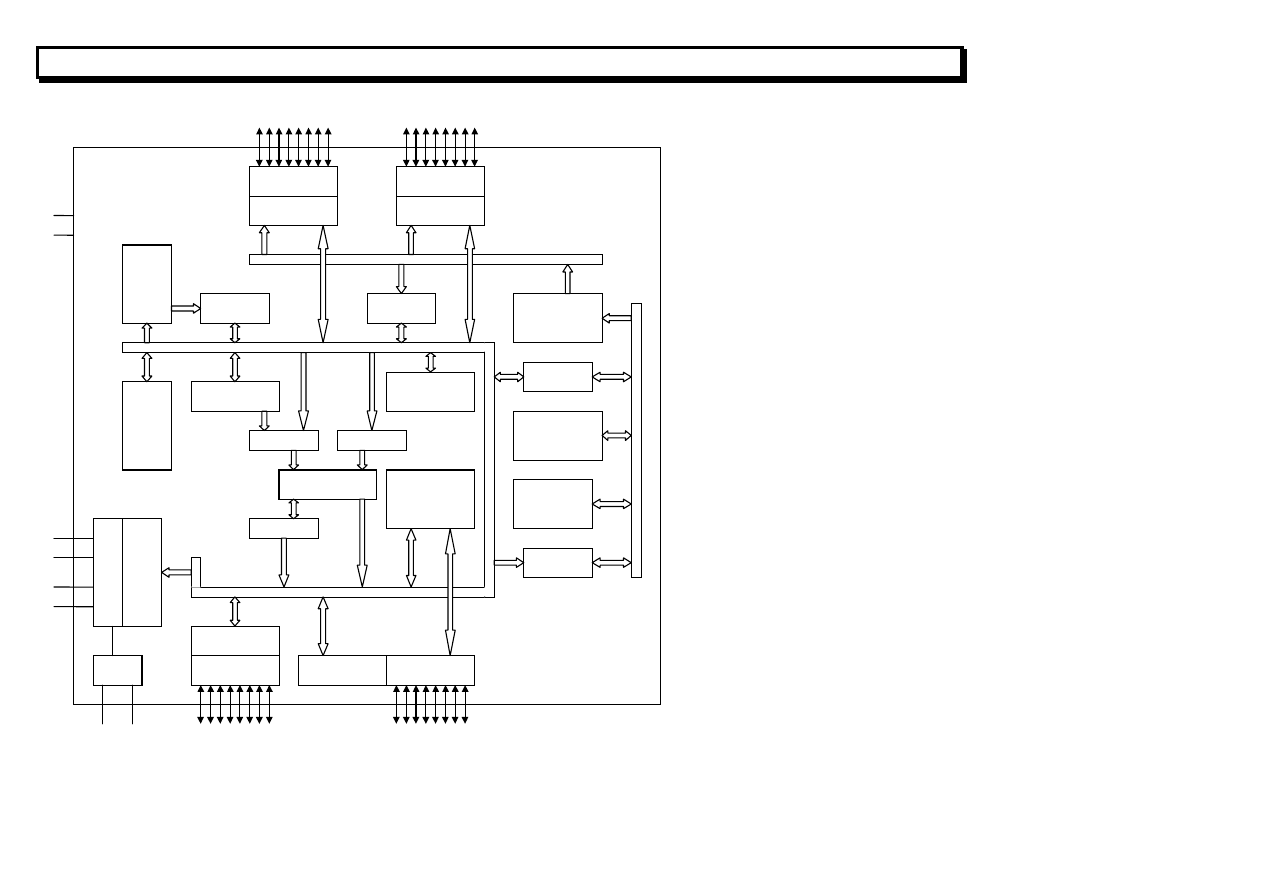

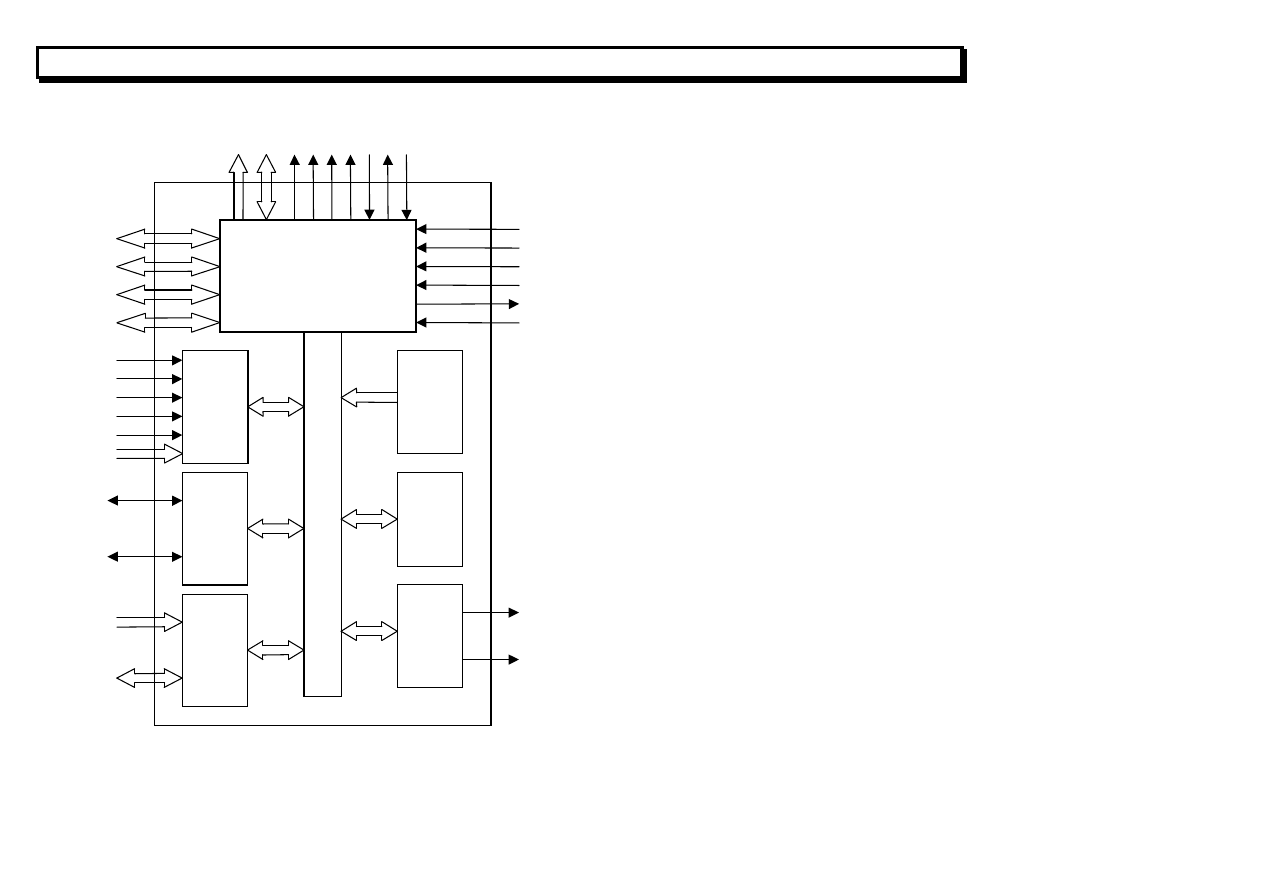

PORT 0

PORT LATCH

PORT 0

PORT LATCH

RAM

A

DD

R

E

S

S

R

EG

IS

T

ER

RAM

B

R

EG

IS

TE

R

ACCUMULATOR

TMP 2

TMP 1

ALU

PSW

ROM

PROGRAM

ADDRESS

REGISTER

BUFFER

PC

INCREMENTER

PROGRAM

COUNTUNER

DPTR

STACK

POINTER

INTRRUPT,

SERIAL

PORT,

TIMER

PORT 1

PORT LATCH

PORT 3

PORT LATCH

OSC

T

IM

IN

G

A

N

D

CO

NT

RO

L

IN

S

T

R

U

C

T

IO

N

R

EG

IS

T

ER

P1.0 – P1.7

P3.0 – P3.7

P0.0 – P0.7

P2.0 – P2.7

Vcc

GND

/PSEN

ALE

/EA

RST

XTAL1

XTAL2

Schemat blokowy mikrokontrolera 8051

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

2

KATEDRA ELEKTRONIKI

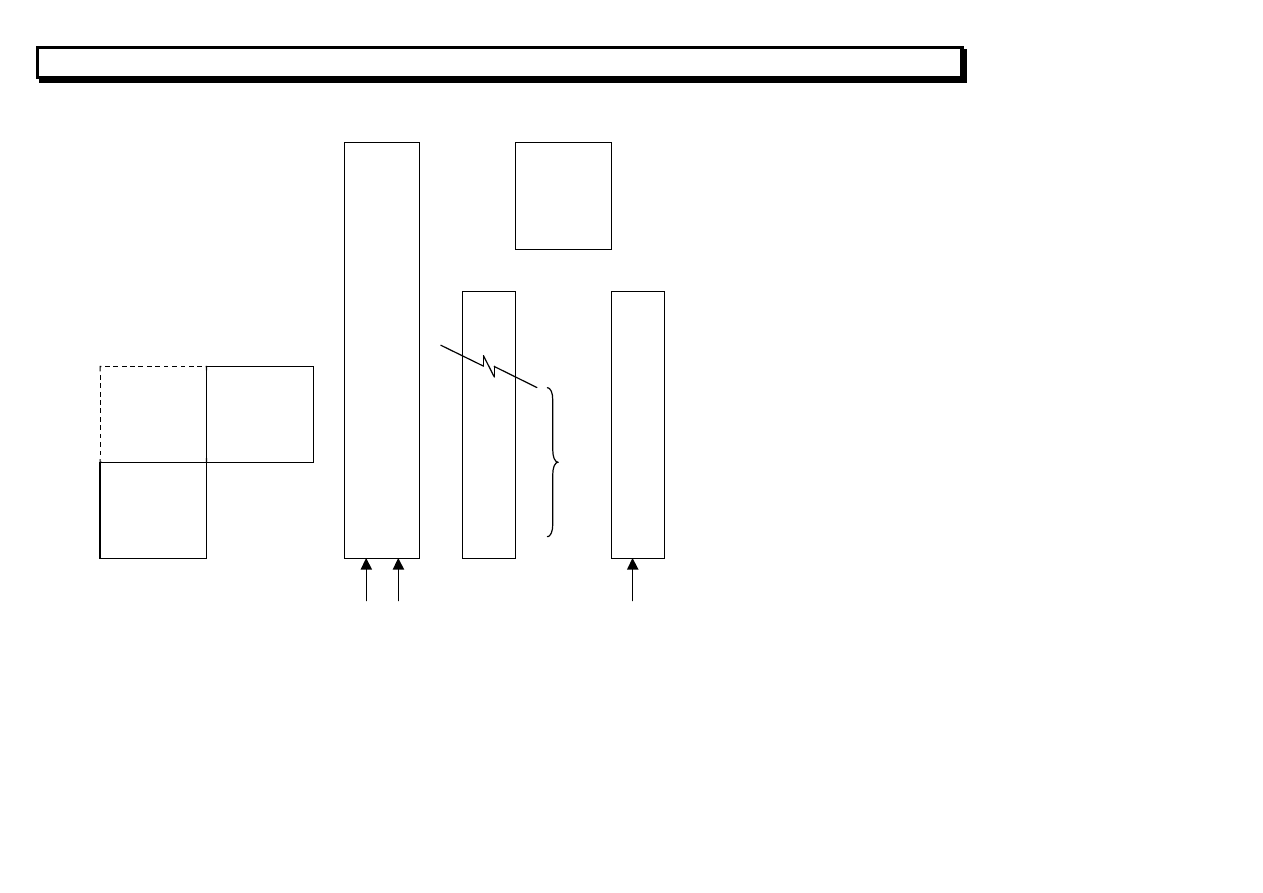

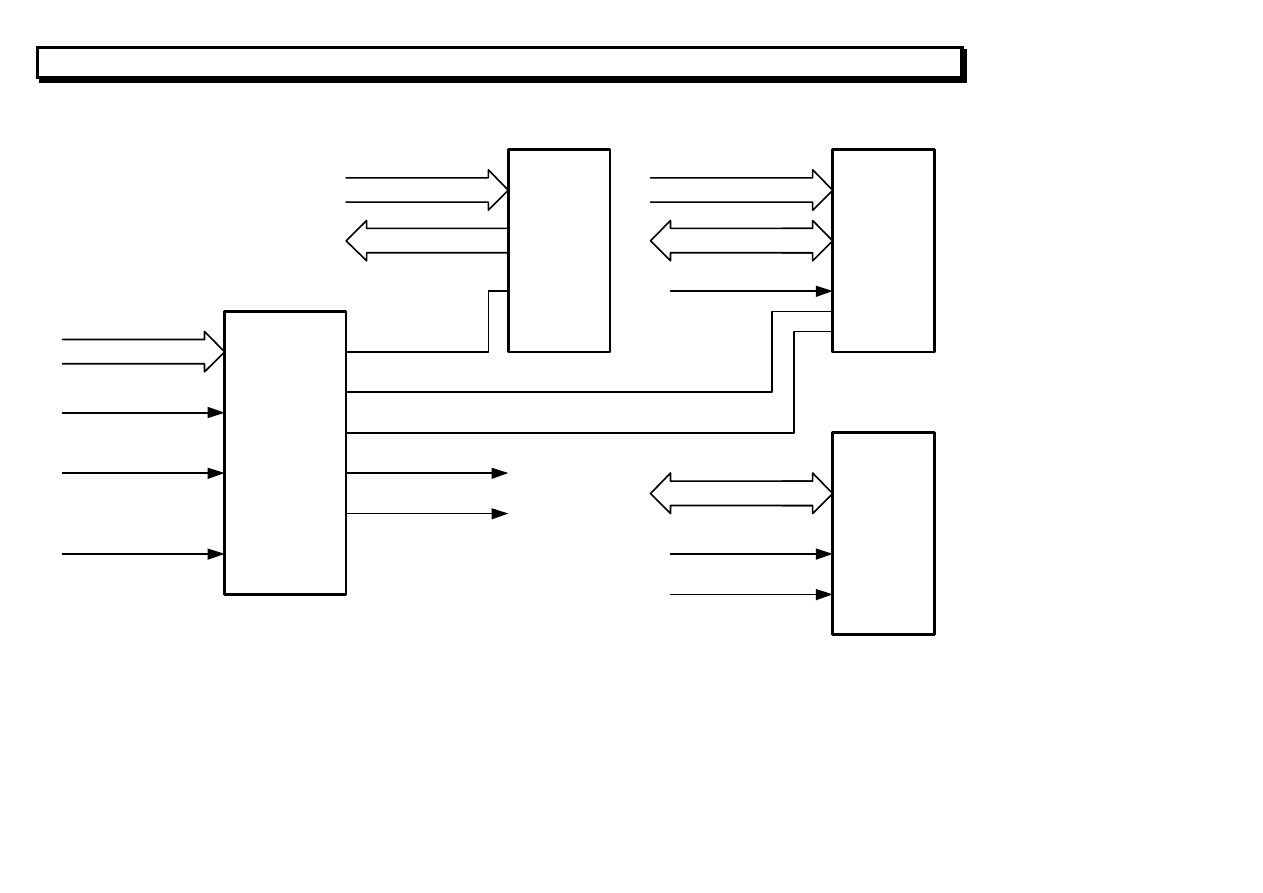

a)

b)

Dost3pne

przez

adresowanie

po7rednie i

bezpo7rednie

Dost3pne

przez

adresowanie

bezpo7rednie

(SFR)

Dost3pne

tylko przez

adresowanie

po7rednie

00h

7Fh

80h

FFh

Ze

w

n3

trzn

a

Pa

m

i3:

Da

ny

ch

FFFFh

/RD /WR

00h

03h

0Bh

13h

1Bh

23h

L

ok

ali

za

cj

a p

rz

erw

a<

0FFFh

Wew

n3

tr

zn

a

Pa

m

i3:

P

ro

gr

am

u

Ze

w

n3

tr

zn

a

Pa

m

i3:

P

ro

gr

am

u

/PSEN

Zewn3trzna

Pami3:

Programu

1000h

FFFFh

Mapy pami3ci mikrokontrolera 8051

a) pami3ci danych, b) pami3ci programu

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

3

KATEDRA ELEKTRONIKI

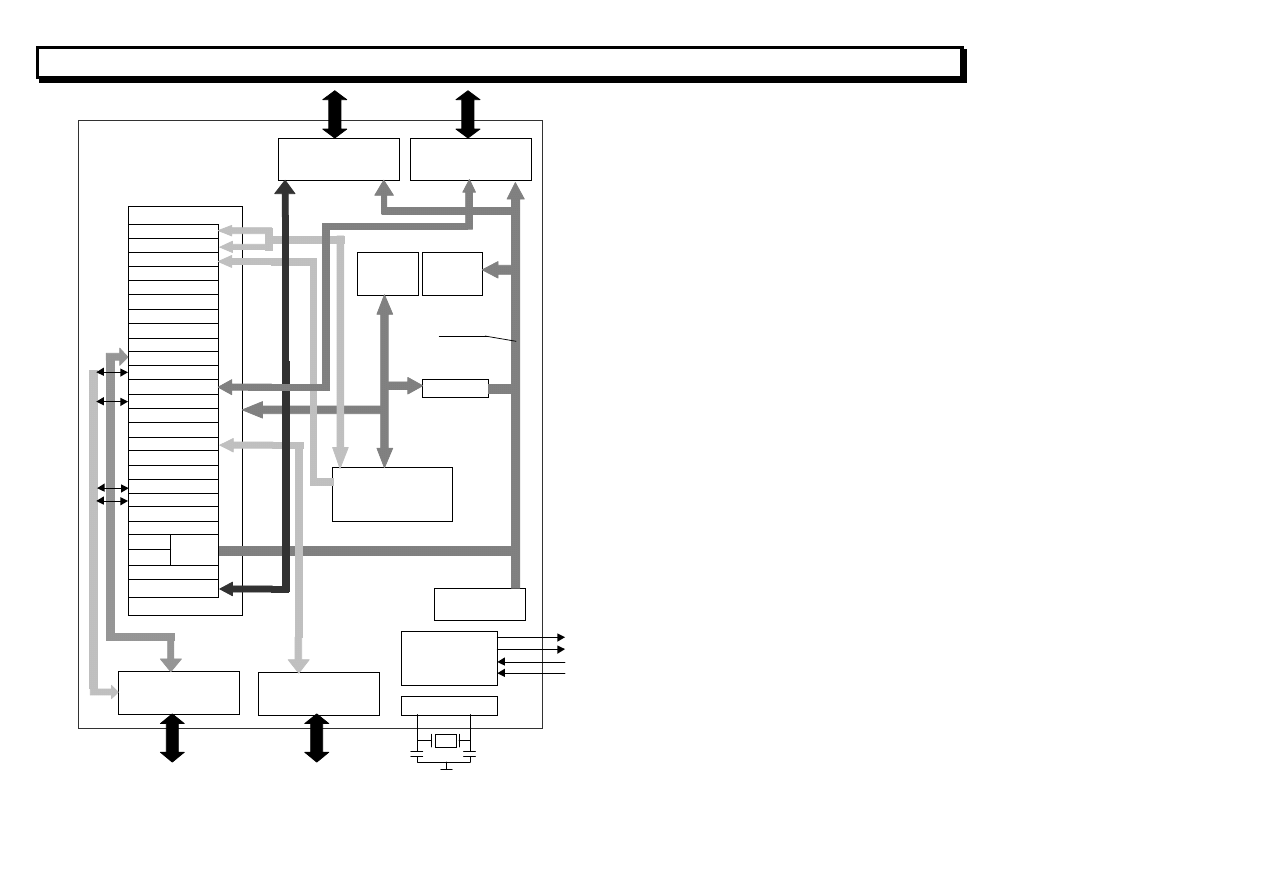

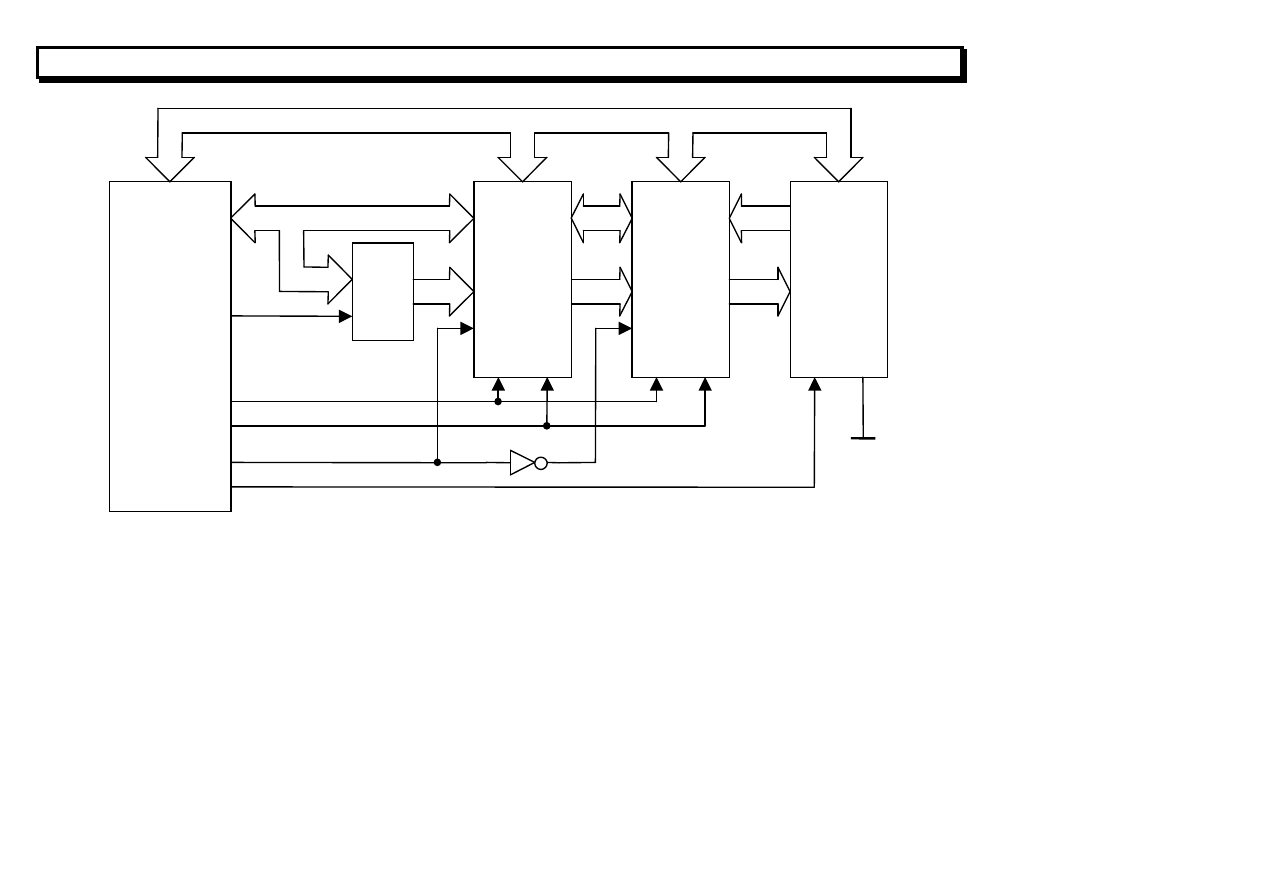

Rejestry Specjalne SFR

PORT 2

we/wy P2.0 - P2.7

adres A8 - A15

PORT 0

we/wy P0.0 - P0.7

adres A0 - A7

PORT 3

we/wy P3.0 - P3.7

funkcje alternatywne

PORT 1

we/wy P1.0 - P1.7

OSCYLATOR

RAM

ROM

EPROM

BUFOR

JEDNOSTKA

ARYTMETYCZNO

- LOGICZNA

UKLADY

KONTROLNE I

TAKTUJ CE

B

ACC

PSW

TH2

TL2

RCAP2H

RCAP2L

T2CON

IP

P3

IE

P2

SBUF

SCON

PCON

P1

TH1

TH0

TL1

TL0

TMOD

TCON

DPH

DPL

SP

P0

S

F

R

DPTR

LICZNIK

ROZKAZOW

ADRES

PSEN

ALE

EA

RST

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

4

KATEDRA ELEKTRONIKI

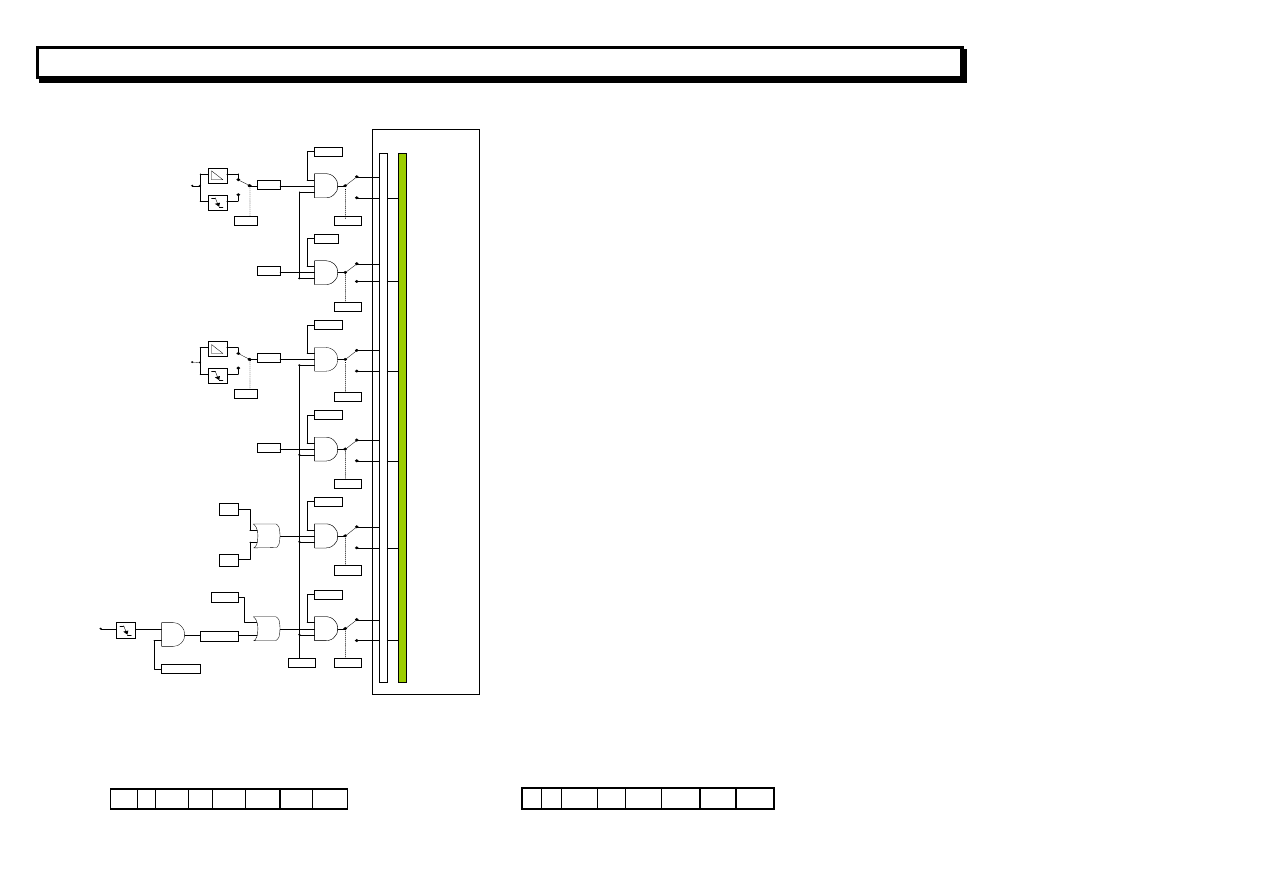

IE

EA X ET2 ES ET1 EX1 ET0 EX0

adres 0A8H IP

X X PT2 PS PT1 PX1 PT0 PX0

adres 0B8H

IT 0

E X 0

0

1

0

1

P X 0

P R IO R Y T E T

P R ZE R W A N

IN T 0

(P 3 .2 )

K O LE J N O S C I

P R IO R Y T E T

O B S LU G I

P R Z E R W A N IA

1

0

na j w yzs zy

na jnizs zy

IE 0

E X 0

0

P X 0

0

1

P X 0

T F 0

0

1

E T 0

l ic zni k 0

E X 1

IE 1

P X 1

IT 1

IN T 1

(P 3 .3 )

0

1

P T 1

T F 1

0

1

E T 1

l ic zni k 1

0

0

1

P S

0

E S

R 1

T 1

0

1

P T 2

0

E T 2

E X F 2

T F 2

E X E N 2

p o r t

s ze r e go w y

li c znik 1

T 2 E X

(P 1 .1 )

E A L

1

0

•

E A

-

b l o k o w a n i e w s z y s t k i c h p r z e r w a > .

E A = 0

@ a d n e p r z e r w a n i e

n i e

m o @ e b y B p r z y j C t e .

E A = 1 k a @ d e

p r z e r w a n i e m o @ e b y B p r z y j C t e

p o d w a r u n k i e m ,

@ e o d p o w i a d a j E c y

m u z n a c z n i k j e s t w s t a n i e 1 .

•

X

-

z a r e z e r w o w a n e .

•

E T 2

-

b l o k o w a n i e ( E T 2 = 0 )

l u b

o d b l o k o w a n i e ( E T 2 = 1 ) p r z e r w a n i a

g e n e r o w a n e g o p r z e z l i c z n i k 2 .

•

E S

-

b l o k o w a n i e ( E S = 0 )

l u b

o d b l o k o w a n i e ( E S = 1 ) p r z e r w a n i a

g e n e r o w a n e g o p r z e z p o r t s z e r e g o w y .

•

E T 1

-

b l o k o w a n i e ( E T 1 = 0 ) l u b

o d b l o k o w a n i e ( E T 1 = 1 ) p r z e r w a n i a

G e n e r o w a n e g o p r z e z l i c z n i k 1 .

•

E X 1

-

b l o k o w a n i e ( E X 1 = 0 ) l u b

o d b l o k o w a n i e ( E X 1 =

1 ) p r z e r w a n i a

z e w n C t r z n e g o

z w e j F c i a I N T 1 .

•

E T 0

-

b l o k o w a n i e ( E T 0 = 0 )

l u b

o d b l o k o w a n i e ( E T 0 = 1 ) p r z e r w a n i a

g e n e r o w a n e g o p r z e z l i c z n i k 0 .

•

E X 0

-

b l o k o w a n i e ( E X 0 = 0 ) l u b

o d b l o k o w a n i e ( E X 0 = 1 ) p r z e r w a n i a

z e w n C t r z n e g o

z w e j F c i a I N T 0 .

•

PT2 - licznik 2

•

PS

- port szeregowy

•

PT1 - licznik 1

•

PX1 - przerwanie zewnCtrzne z

wejFcia INT1

•

PT0 - licznik 0

•

PX0 - przerwanie zewnCtrzne z

wejFcia INT0

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

5

KATEDRA ELEKTRONIKI

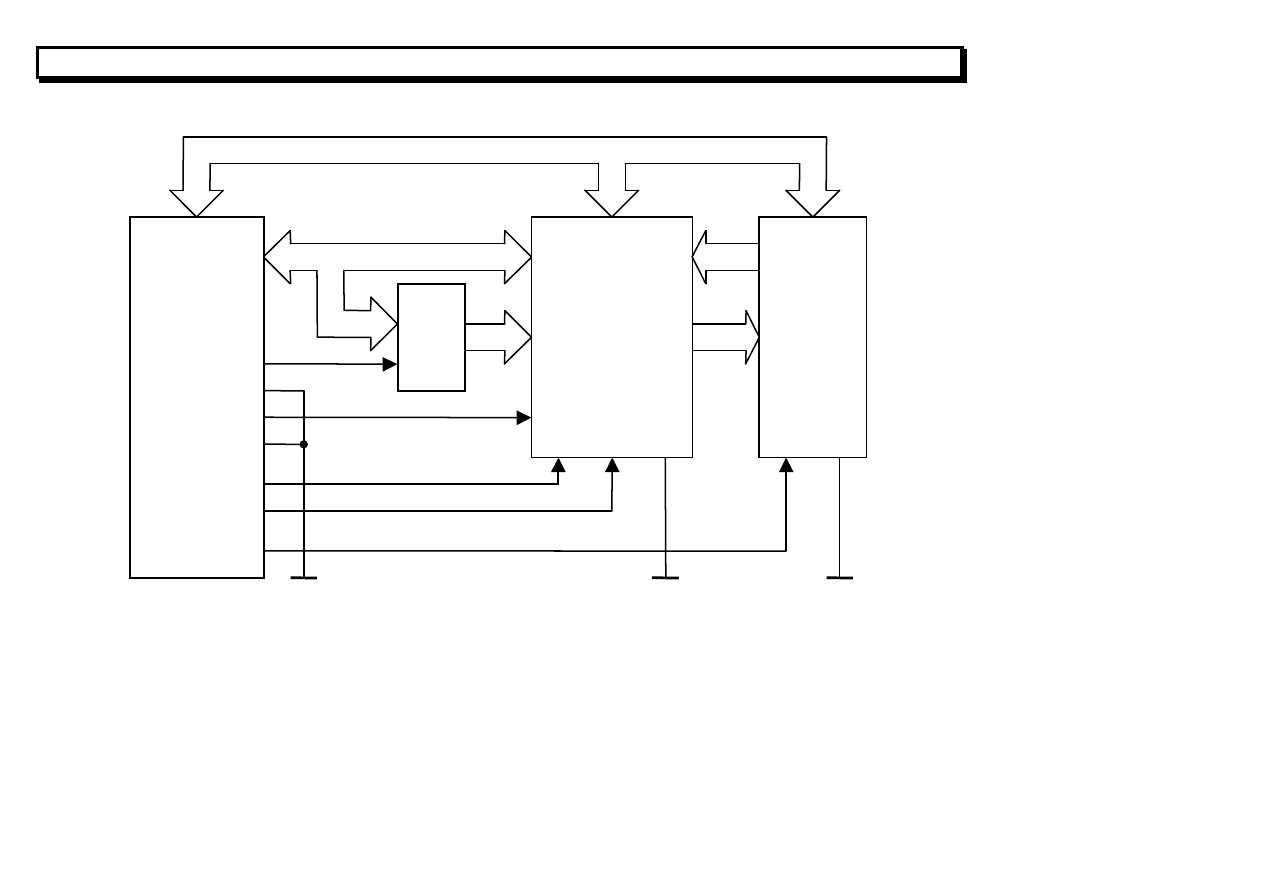

J@DRO 80C51

BEZ PAMIACI

ROM I

RAM

WE

WN

A

T

R

ZN

A

8 –

B

ITO

W

A S

Z

Y

NA

PA

M

IAC

P

ROG

RA

M

U

8k

x

8

PA

M

IAC

DA

N

Y

CH

256k

x

8

P

ODW

Ó

JN

Y

PW

M

AD

C

PO

R

T

S

ZE

R

EG

O

W

Y

I

2

C

8

–

BI

T

O

W

E

P

ORT

Y

I

/O

P4

I

P5

SDA

SCL

P5

P4

P0

P1

P2

P3

A8-15

AD0-7

/RD

/WR

/PSEN

/EA

ALE XTAL2

XTAL1

TXD

RXD

/INT0

/INT1

T0

T1

/PWM0

/PWM1

ADC0-7

AV

REF

AV

DD

AV

SS

STADC

Schemat blokowy mikrokontrolera 80C552

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

6

KATEDRA ELEKTRONIKI

D0 - D7

A9 - A15

/WR

/RD

/PSEN

/OE

A0 - A15

ROM

/OE

A0 - A15

RAM

/CE

/OEROM

/OERAM

/CSRAM

D0 - D7

D0 - D7

/CS1

A0, A1

/CS1

/CS2

/WR

GENEROWANIE SYGNAHÓW CS - PODHJCZENIE LCD

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

7

KATEDRA ELEKTRONIKI

M

IK

RO

K

O

NT

R

O

L

E

R 8

05

1

Bu

fo

r

74

H

C

573

P0

AD0-AD7

EP

R

O

M

27

512

S

RAM

62

256

S

RAM

62

256

A0-A7

ALE

/PSEN

/RD

/WR

P2

A8-A15

/OE

D0-D7

D0-D7

A0-A7

A0-A7

A8-A14

A8-A14

/OE

/OE

/WR

/WR

/CE

P2/A15

/CE

/CE

HC04

Schemat blokowy zewn3trznego 7rodowiska pracy mikrokontrolera 8051

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

8

KATEDRA ELEKTRONIKI

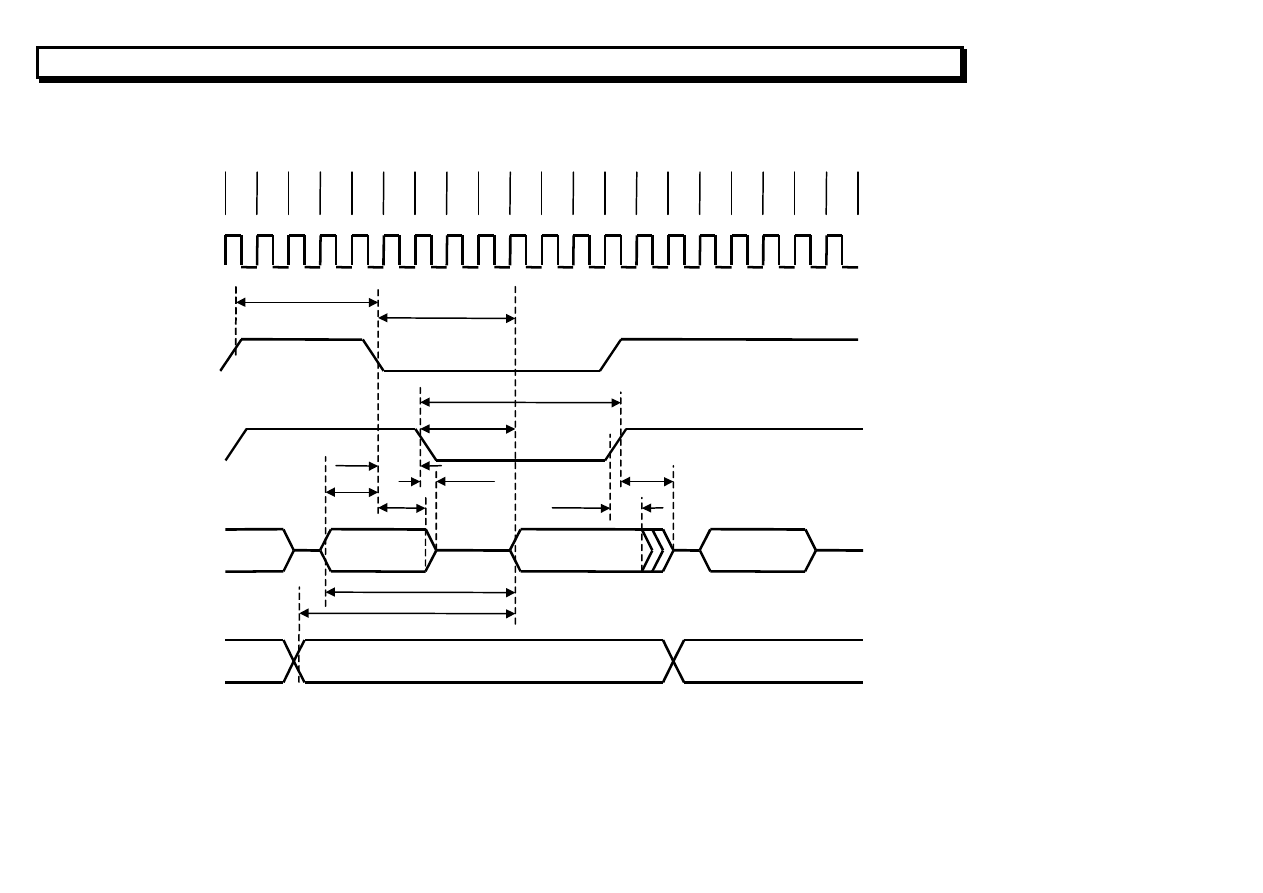

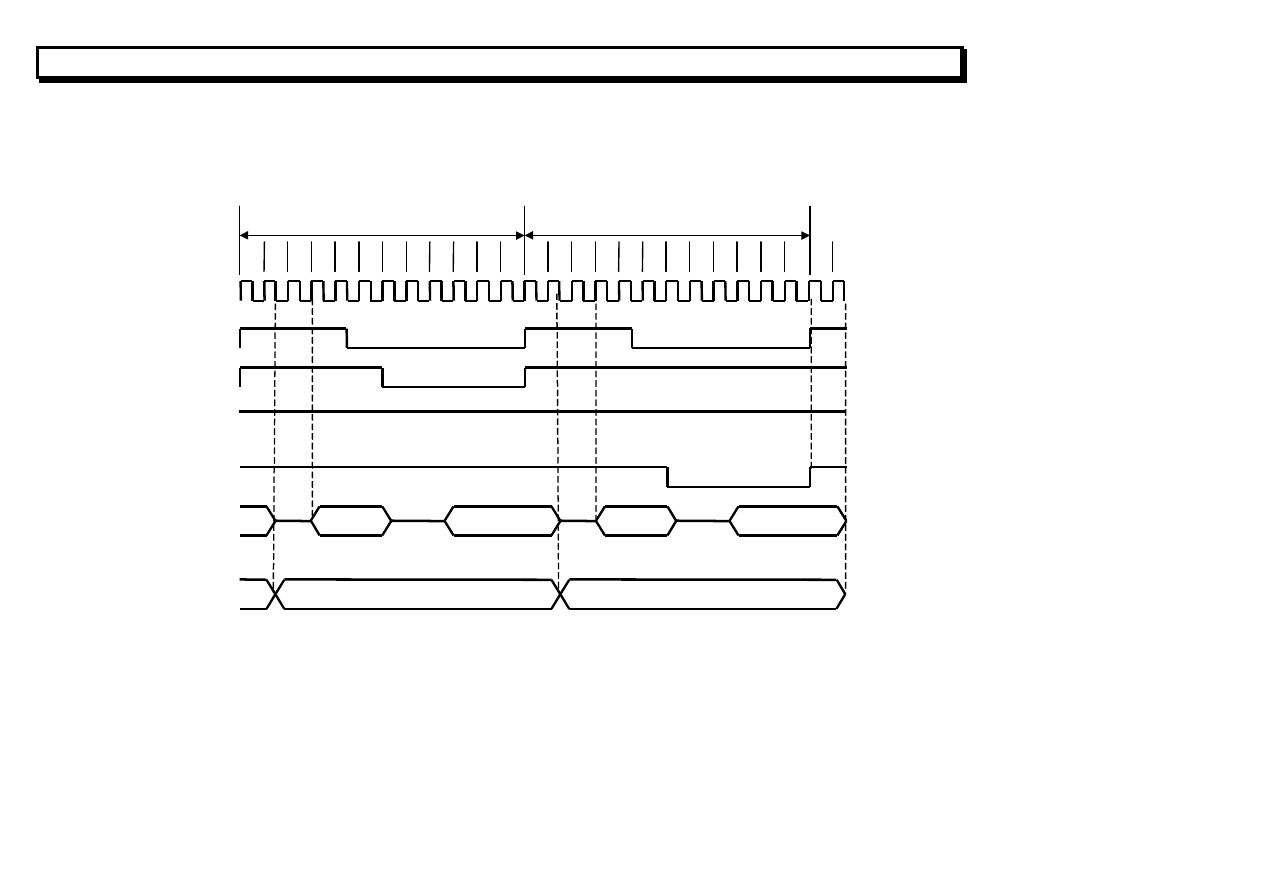

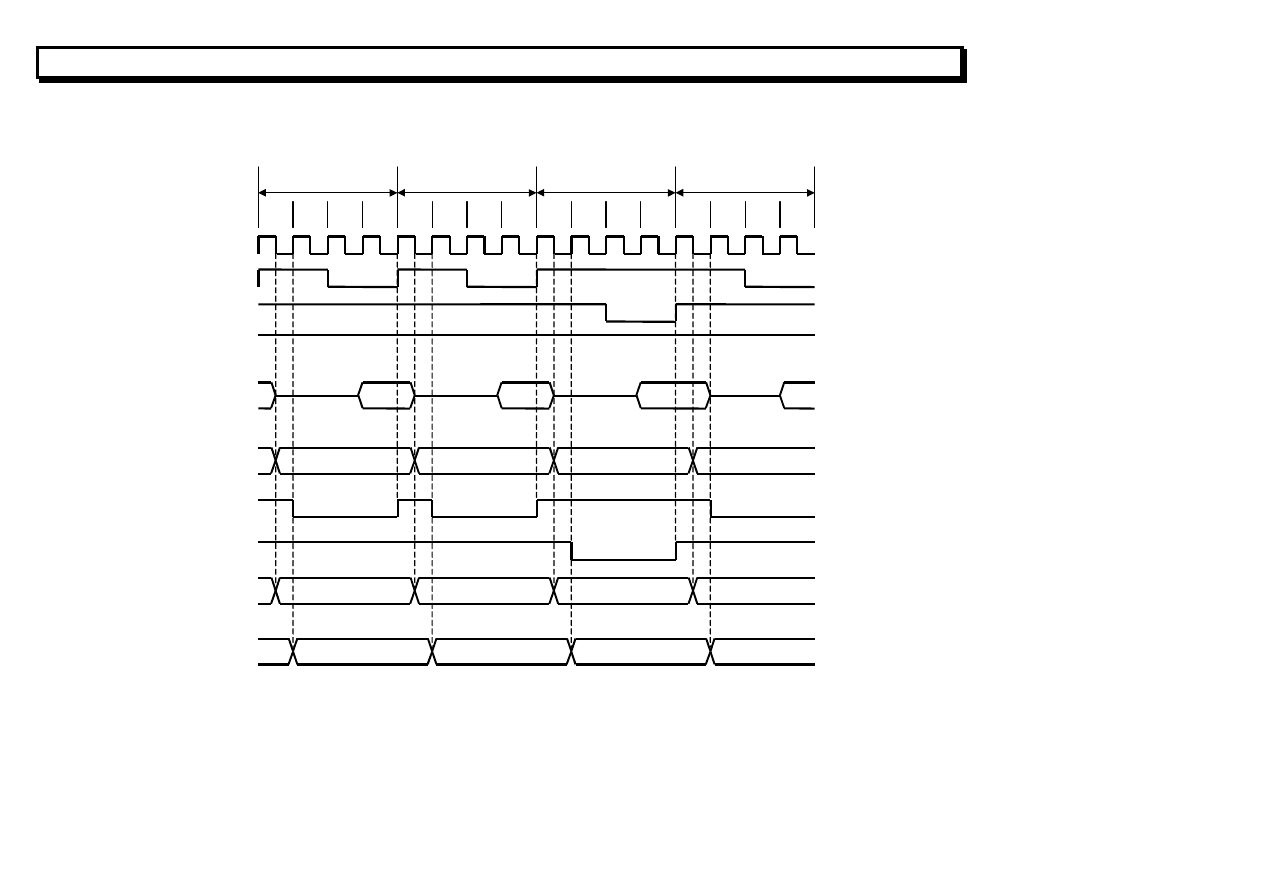

MOVC A, @DPTR.

/PSEN

ADDRESS A8-A15

ADDRESS A8-A15

PORT2

INSTRUCTION

IN

PORT0

t

PLIV

t

PXIZ

t

PXIX

t

AVIV1

t

AVIV2

t

PLPH

ADDRESS

A0-A7

C1

t

LHLL

t

LLIV

t

AVLL

t

LLPL

t

PLAZ

t

LLAX1

ALE

ADDRESS

A0-A7

C2

C3

C4

C5

C6

C7

C8

C9

C10 C11

C12

C1

C2

C3

C4

C5

C6

C7

C8

Cykl odczytu z zewn3trznej pami3ci programu dla mikrokontrolera

8051

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

9

KATEDRA ELEKTRONIKI

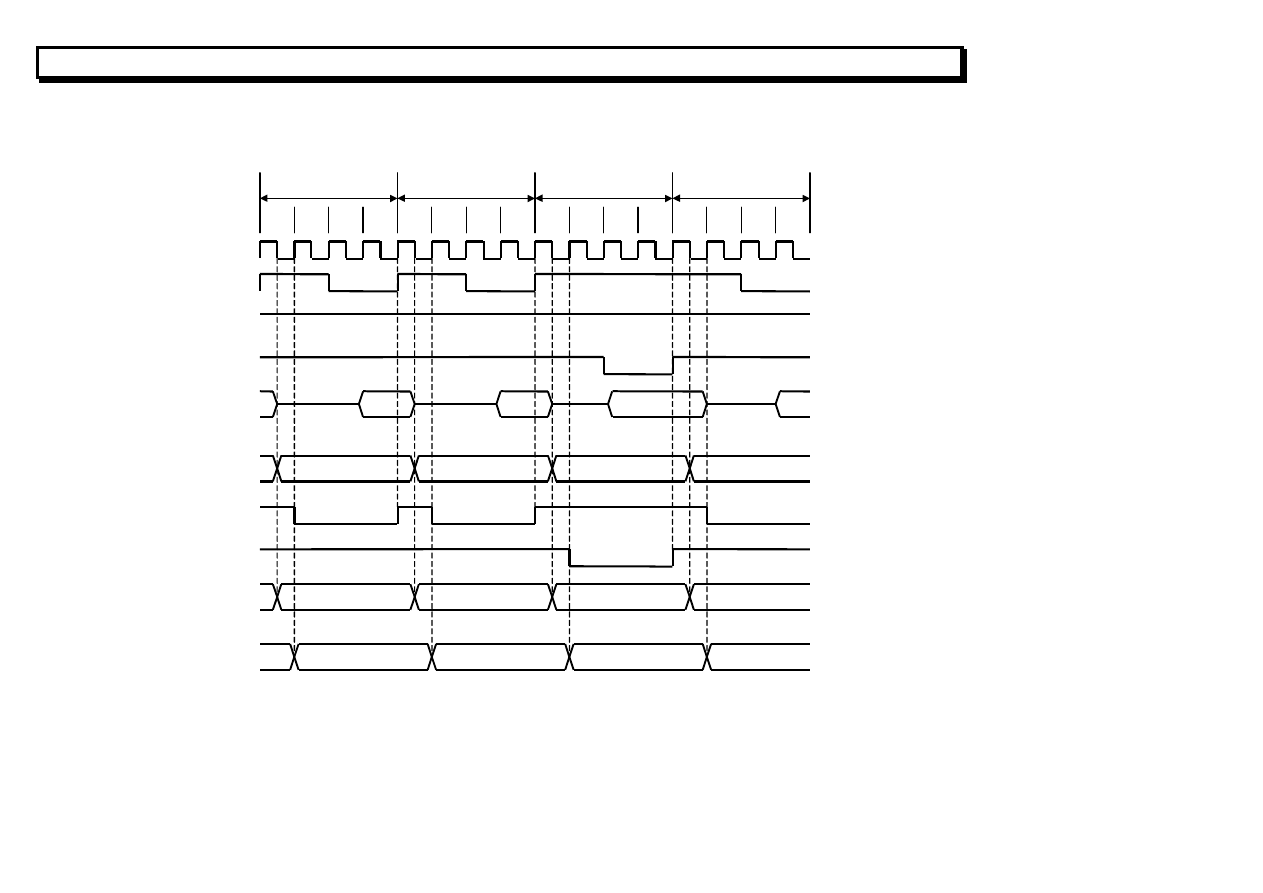

MOVX @DPTR, A.

CLK

ALE

/PSEN

/RD

PORT0

PORT2

A0-A7

A0-A7

D0-D7

D0-D7

A8-A15

A8-A15

ADRES INSTRUKCJI

ADRES DANYCH

ODCZYT DANYCH

PIERWSZY CYKL MASZYNOWY

INSTRUKCJI

DRUGI CYKL MASZYNOWY

INSTRUKCJI

ODCZYT INSTRUKCJI

C1

C3

C4

C5

C7

C8

C9

C11 C12

C2

C6

C10

C1

C3

C4

C5

C7

C8

C11 C12

C2

C6

C10

/WR

C9

Dwa cykle odczytu z pami3ci danych dla mikrokontrolera 8051

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

10

KATEDRA ELEKTRONIKI

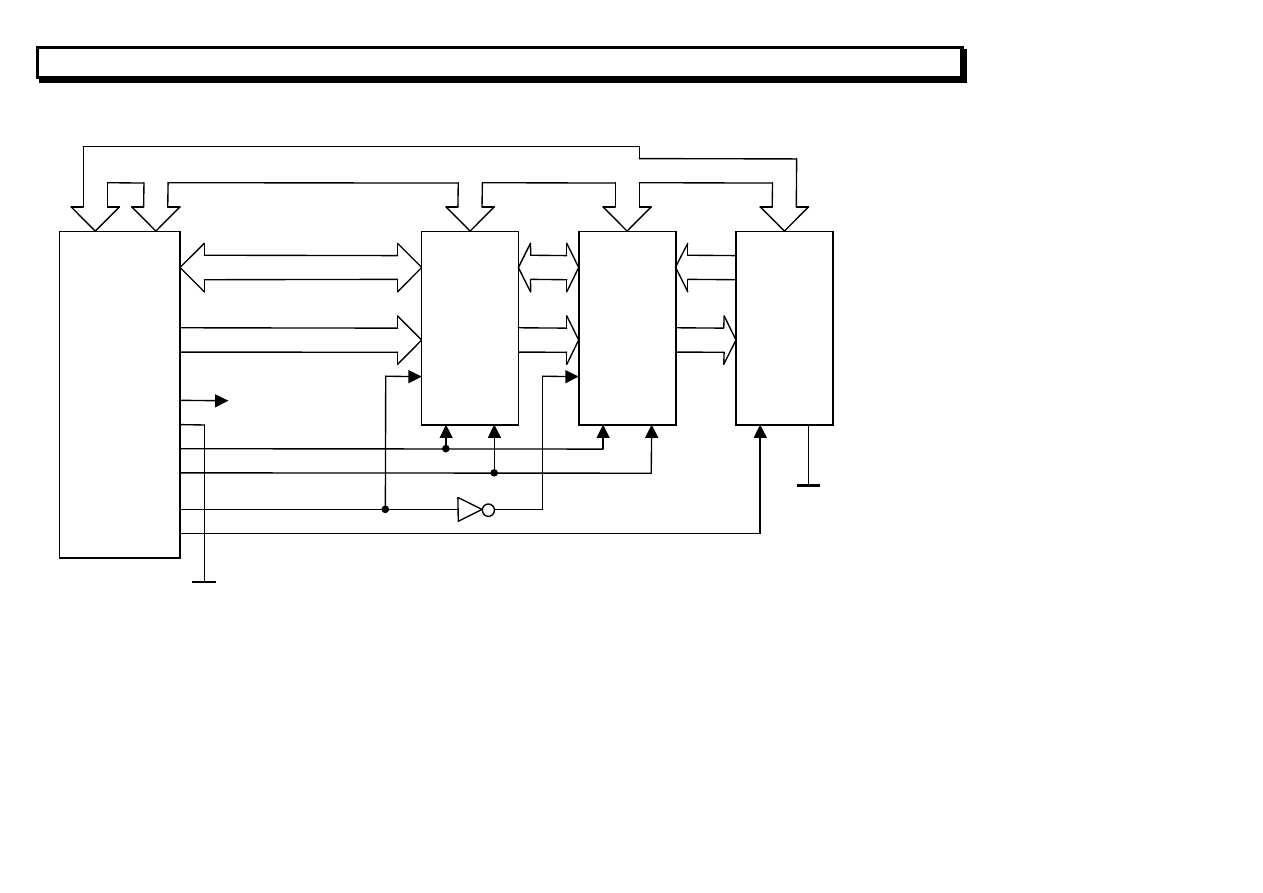

M

IK

R

O

K

O

N

TR

O

LER

D

S

80

C

39

0

Bu

fo

r

74

H

C

57

3

P0

AD0-AD7

EP

R

O

M

27

512

SR

A

M

T

C

55

100

1

A0-A7

ALE

/PSEN

/RD

/WR

P2

A8-A15

D0-D7

A0-A7

/OE

/OE

/WR

/CE

P4/A16

A16

/CE

/MUX

/EA

Schemat blokowy podLMczenia zewn3trznej pami3ci do

mikrokontrolera DS80C390 w trybie pracy 8051

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

11

KATEDRA ELEKTRONIKI

M

IK

RO

K

O

N

T

R

O

L

E

R DS

80

C

390

P0

D0-D7

EP

R

O

M

27

51

2

SR

A

M

6285

12

SR

A

M

6285

12

A0-A7

/PSEN

/RD

/WR

P2

A8-A18

/OE

D0-D7

D0-D7

A0-A7

A0-A7

A8-A18

A8-A18

/OE

/OE

/WR

/WR

/CE

P4/A19

/CE

/CE

HC04

P4.4-P4.6

A8-A15

/EA

/MUX

+5V

Schemat blokowy podLMczenia zewn3trznej pami3ci w trybie

standardowej pracy mikrokontrolera DS80C390

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

12

KATEDRA ELEKTRONIKI

/PSEN

ADDRESS A8-A15

ADDRESS A16-A19

ADDRESS A8-A15

ADDRESS A16-A19

PORT2

PORT4

PORT4

/CE0-3

INSTRUCTION

IN

PORT0

t

PLIV

t

PXIZ

t

PXIX

t

AVIV1

t

AVIV2

t

PLPH

ADDRESS A0-A7

PORT1

C1

C2

C3

C4

C1

C2

Cykl odczytu z pami3ci programu bez multipleksacji szyny adresowej/

danych dla mikrokontrolera DS80C390

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

13

KATEDRA ELEKTRONIKI

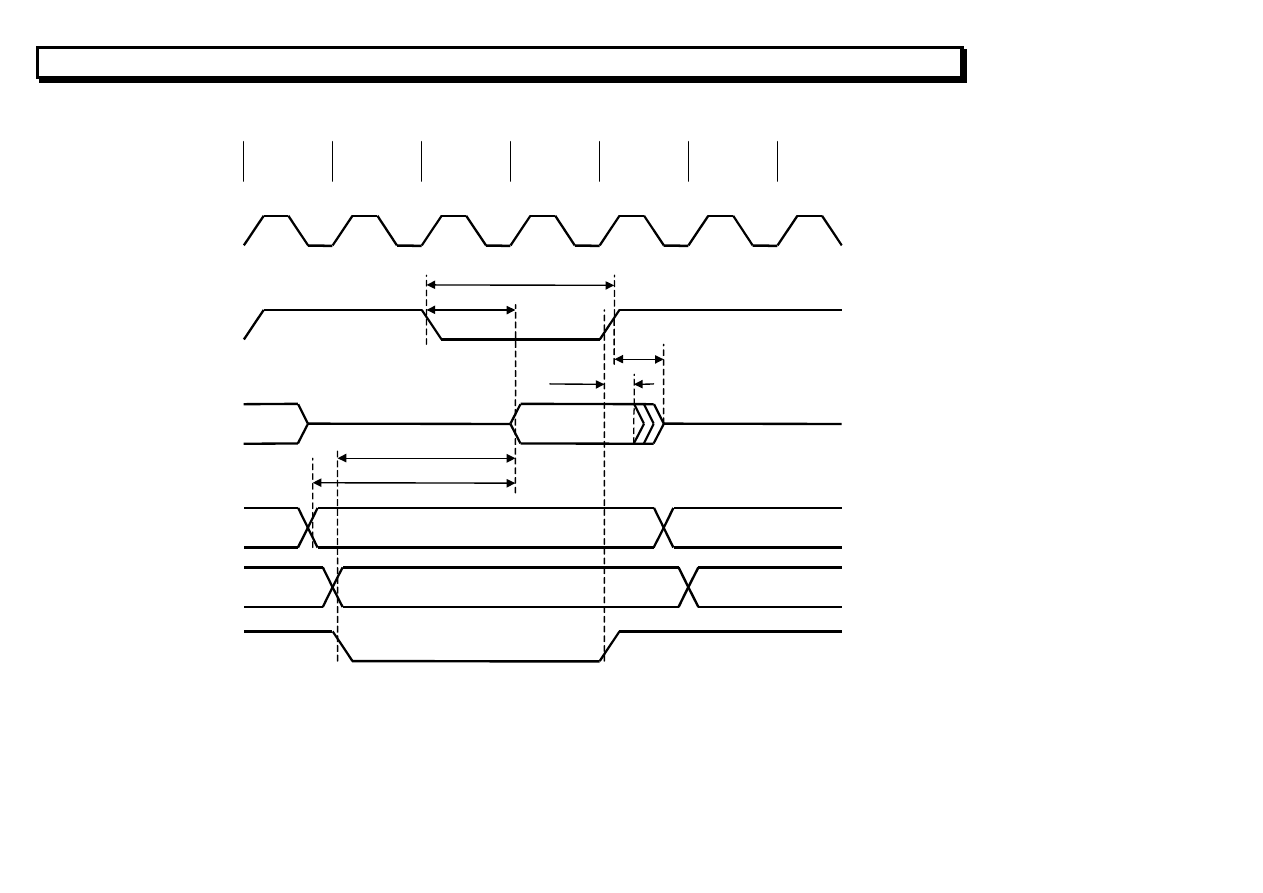

/PCE0-3

CLK

/PSEN

/RD

PORT0

D0-D7

D0-D7

D0-D7

A8-A15

A8-A15

A8-A15

A8-A15

PORT2

A16-A19

A16-A19

A16-A19

A16-A19

PORT4

/CE0-3

ODCZYT

DANYCH

C1

C3

C4

C1

C3

C4

C1

C3

C4

C1

C3

C4

OSTATNI CYKL

POPRZEDNIEJ

INSTRUKCJI

PIERWSZY CYKL

NASTAPNEJ

INSTRUKCJI

PIERWSZY CYKL

MASZYNOWY

INSTRUKCJI

DRUGI CYKL

MASZYNOWY

INSTRUKCJI

C2

C2

C2

C2

ODCZYT

INSTRUKCJI

A0-A7

A0-A7

A0-A7

A0-A7

PORT1

/WR

Cykle odczytu z zewn3trznej pami3ci danych bez multipleksacji szyny

adresowej/ danych dla mikrokontrolera DS80C390

PODSTAWY TECHNIKI MIKROPROCESOROWEJ

Mikrokontrolery C51

14

KATEDRA ELEKTRONIKI

/PCE0-3

CLK

/PSEN

/RD

PORT0

D0-D7

D0-D7

D0-D7

A8-A15

A8-A15

A8-A15

A8-A15

PORT2

A16-A19

A16-A19

A16-A19

A16-A19

PORT4

/CE0-3

ZAPIS

DANYCH

C1

C3

C4

C1

C3

C4

C1

C3

C4

C1

C3

C4

OSTATNI CYKL

POPRZEDNIEJ

INSTRUKCJI

PIERWSZY CYKL

NASTAPNEJ

INSTRUKCJI

PIERWSZY CYKL

MASZYNOWY

INSTRUKCJI

DRUGI CYKL

MASZYNOWY

INSTRUKCJI

C2

C2

C2

C2

ODCZYT

INSTRUKCJI

A0-A7

A0-A7

A0-A7

A0-A7

PORT1

/WR

Cykle zapisu do zewnCtrznej pamiCci danych bez multipleksacji szyny adresowej/ danych dla

mikrokontrolera DS80C390

Wyszukiwarka

Podobne podstrony:

folie dla new C51

gruźlica dla studentów2

Prezentacja 2 analiza akcji zadania dla studentow

1Ochr srod Wyklad 1 BIOLOGIA dla studid 19101 ppt

Kosci, kregoslup 28[1][1][1] 10 06 dla studentow

higiena dla studentów 2011 dr I Kosinska

Parametry życiowe dla WCEM

PREZENTacja dla as

Wyklad FP II dla studenta

badanie dla potrzeb fizjoterapii

9 1 18 Szkolenie dla KiDów

zapotrzebowanie ustroju na skladniki odzywcze 12 01 2009 kurs dla pielegniarek (2)

więcej podobnych podstron