Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

1

Architektura Komputerów

Budowa procesora

(lista rozkazów)

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

2

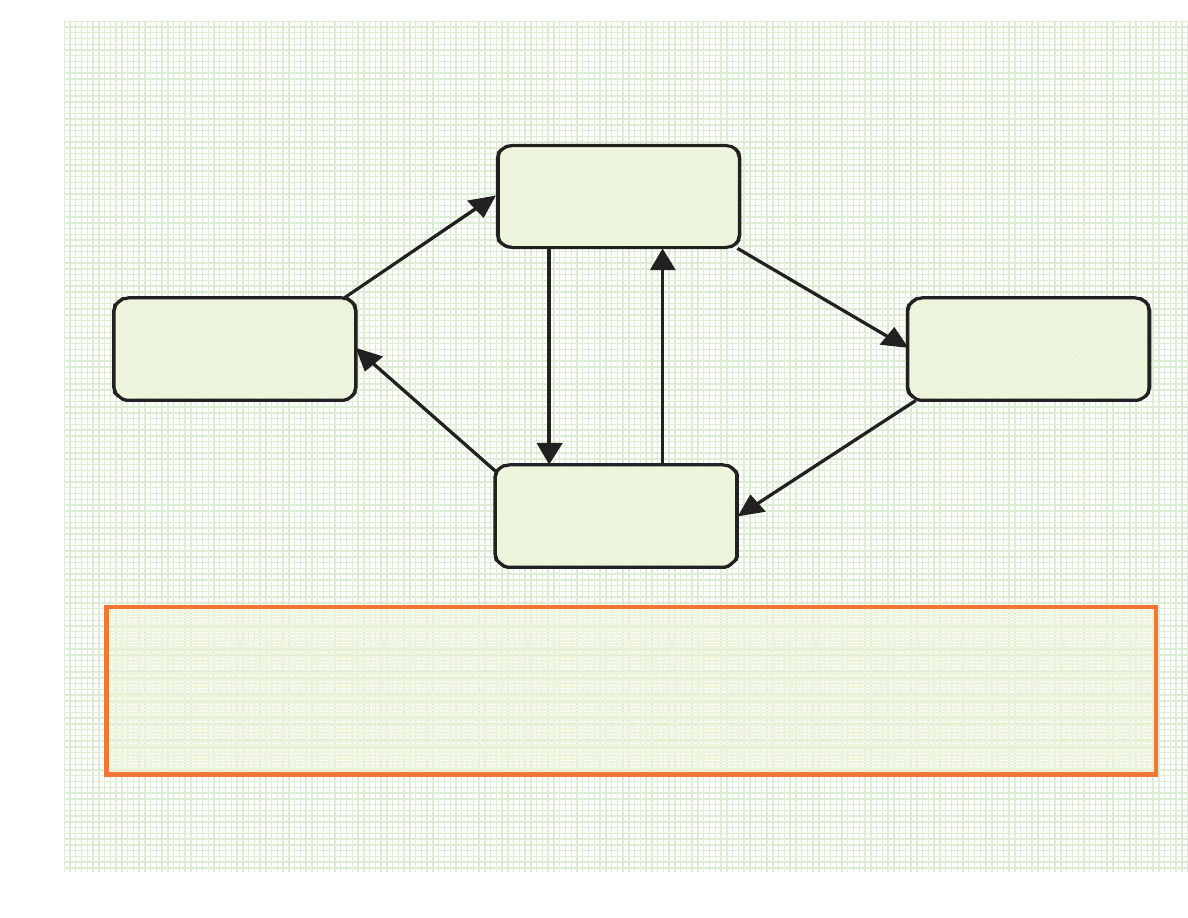

P o bra nie

P obranie

pośred nie

W ykonywanie

P rzerwanie

Cykle pracy procesora

1.

Faza pobrania,

2.

Faza pobrania pośredniego ,

3.

Faza wykonania rozkazu,

4.

Faza przerwania.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

3

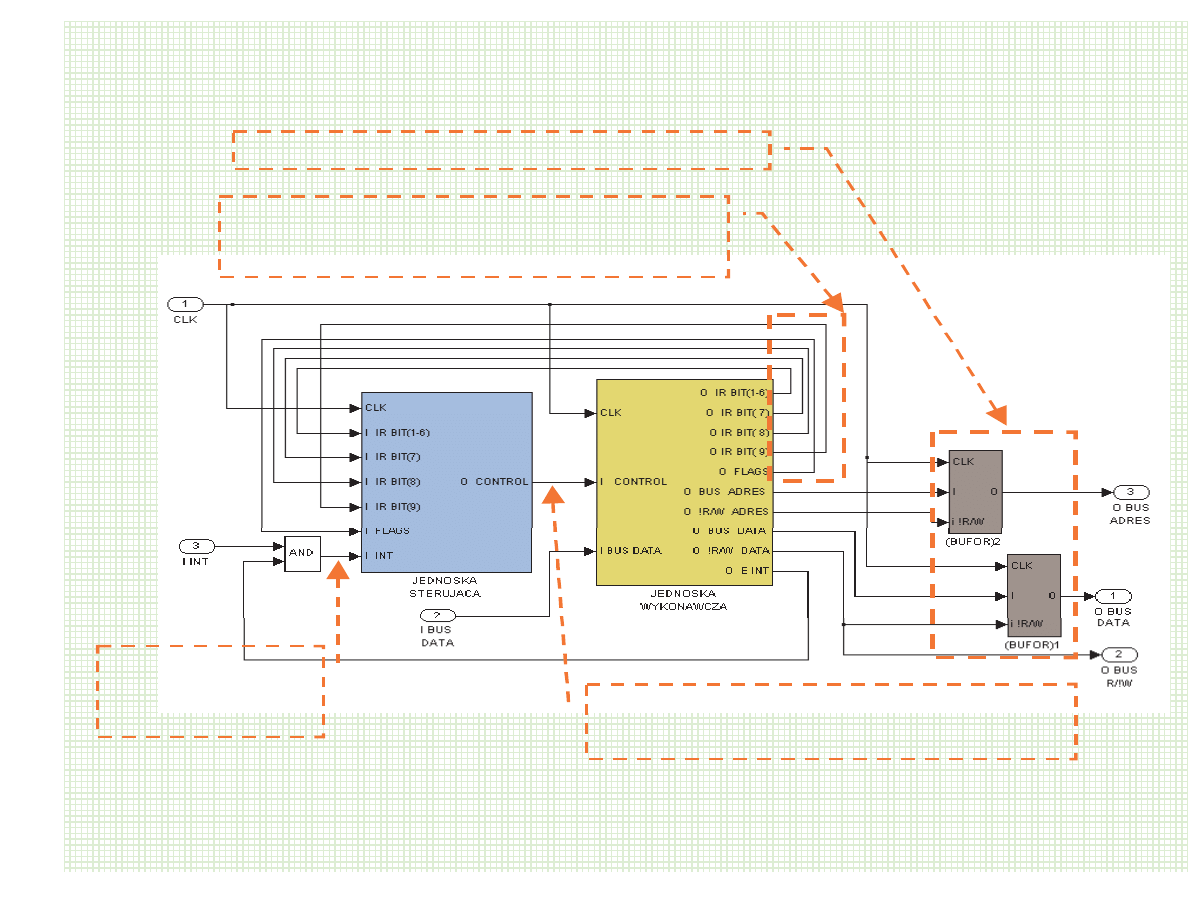

G ru p a sy g n a łó w w e jś c io w y c h d la je d n o s tk i

ste r u ją c e j, k tó ra je st zw ią z a n a z fo rm a te m

ro zk a z u m a sz y n o w e g o

S te r o w a n ie m ik ro p r ze s ła n i a m i

(sy g n a ły w y jśc i o w e je d n o s tk i s te r u ją c e j)

B u fo ry m a g is tra li a d re s o w e j i m a g is tra li d a n y c h

S y g n a liza c ja

p rz e rw a n ia

(sy g n a ły

w e jśc io w e )

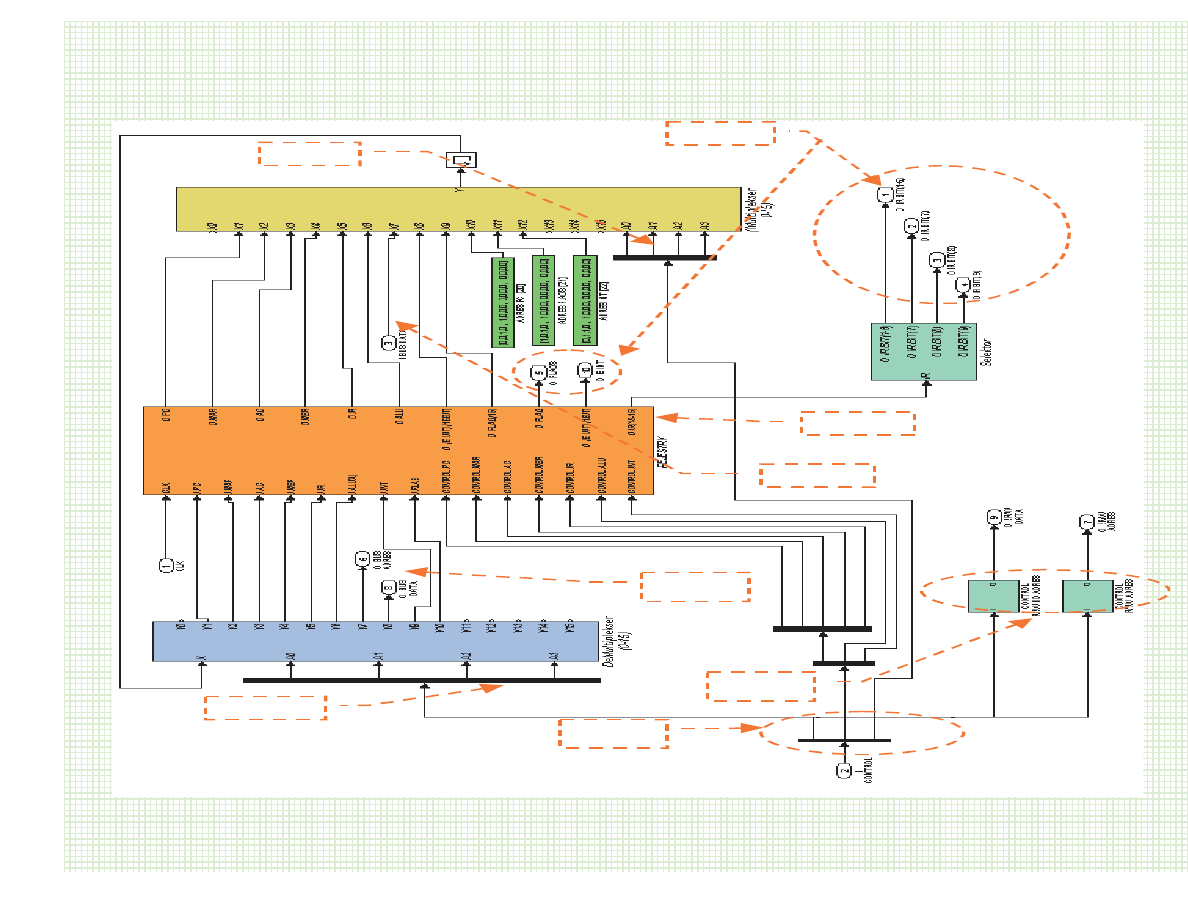

Struktura procesora

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

4

F a z a p o b r a n i a

F a z a a d r e s o w a n i a

p o ś r e d n i e g o

F a z a w y k o n a n i a

F a z a

p r z e r w a n i a

L i c z n i k s e k w e n c j i

c z a s o w y c h

Struktura jednostki sterującej modelowanego procesora

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

5

Faza pobrania – tryby adresowania

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

6

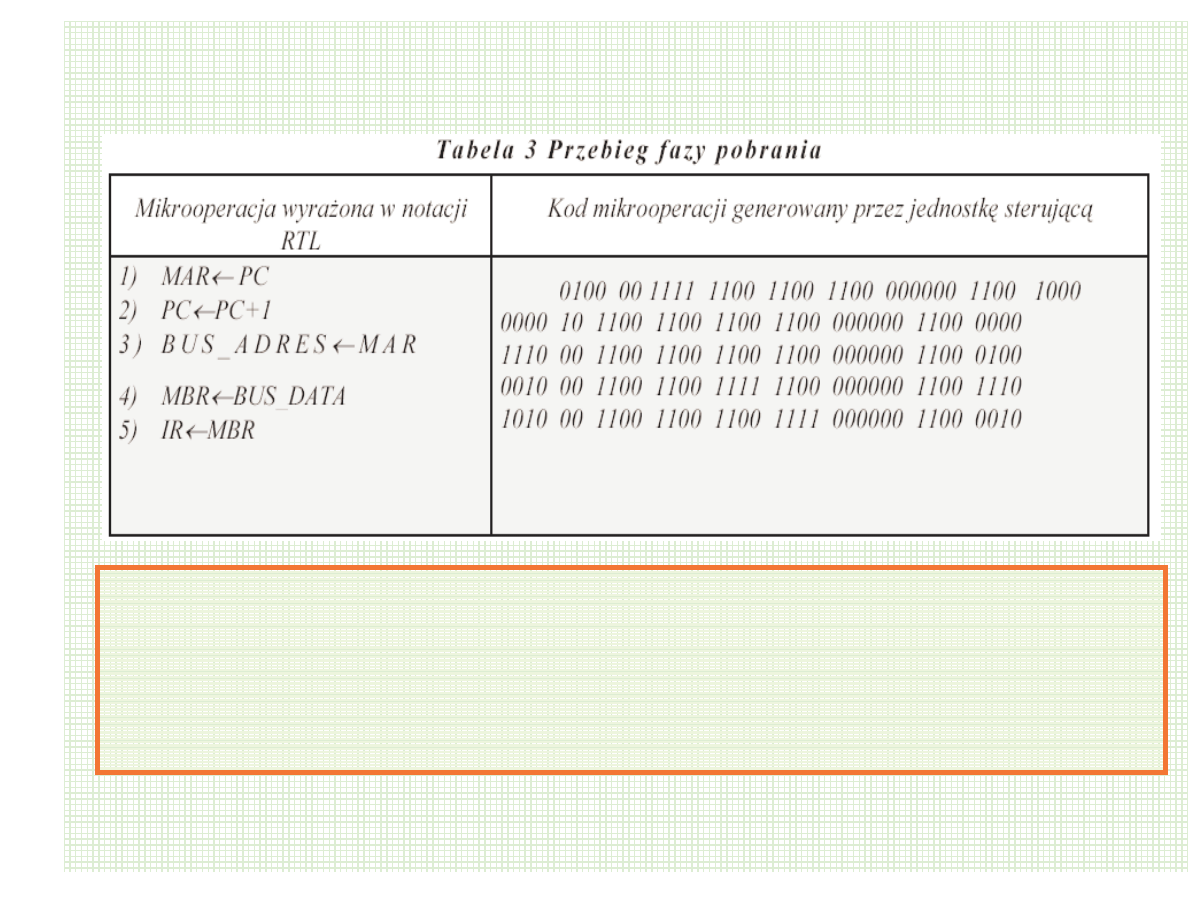

Przebieg fazy pobrania

1.

Wszystkie przesłania między rejestrowe, które wchodzą w skład fazy

pobrania zostały przedstawione w (Tabela 3).

2.

W prawej kolumnie zostały przedstawione sygnały sterujące, które

odpowiadają poszczególnym przesłaniom.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

7

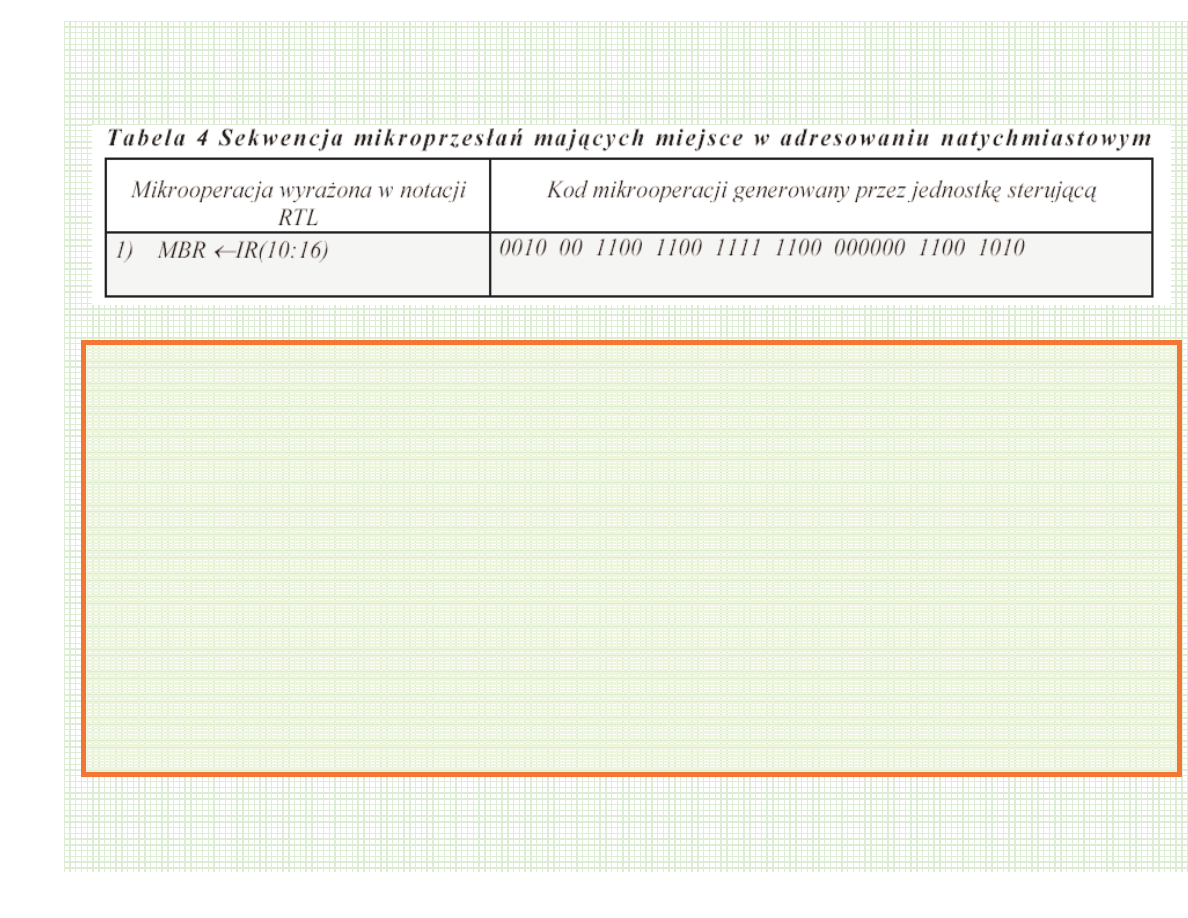

Faza adresowania -Adresowanie natychmiastowe

1.

W przypadku adresowania natychmiastowego argument rozkazu maszynowego

jest reprezentowany za pomocą stałej.

2.

Wartość stałej jest kodowana za pomocą bitów poczynając od bitu o numerze

10, a kończąc na bicie o numerze 16. W tym przypadku bity te reprezentują

wartość liczbową, która jest przedstawiona w notacji NB- w naturalnym kodzie

binarnym.

3.

Z natury tego sposobu przechowywania argumentów, wynika, że przedział

wartości liczbowych, którym można się posługiwać przy wykorzystaniu tego

trybu adresowania jest mocno ograniczony.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

8

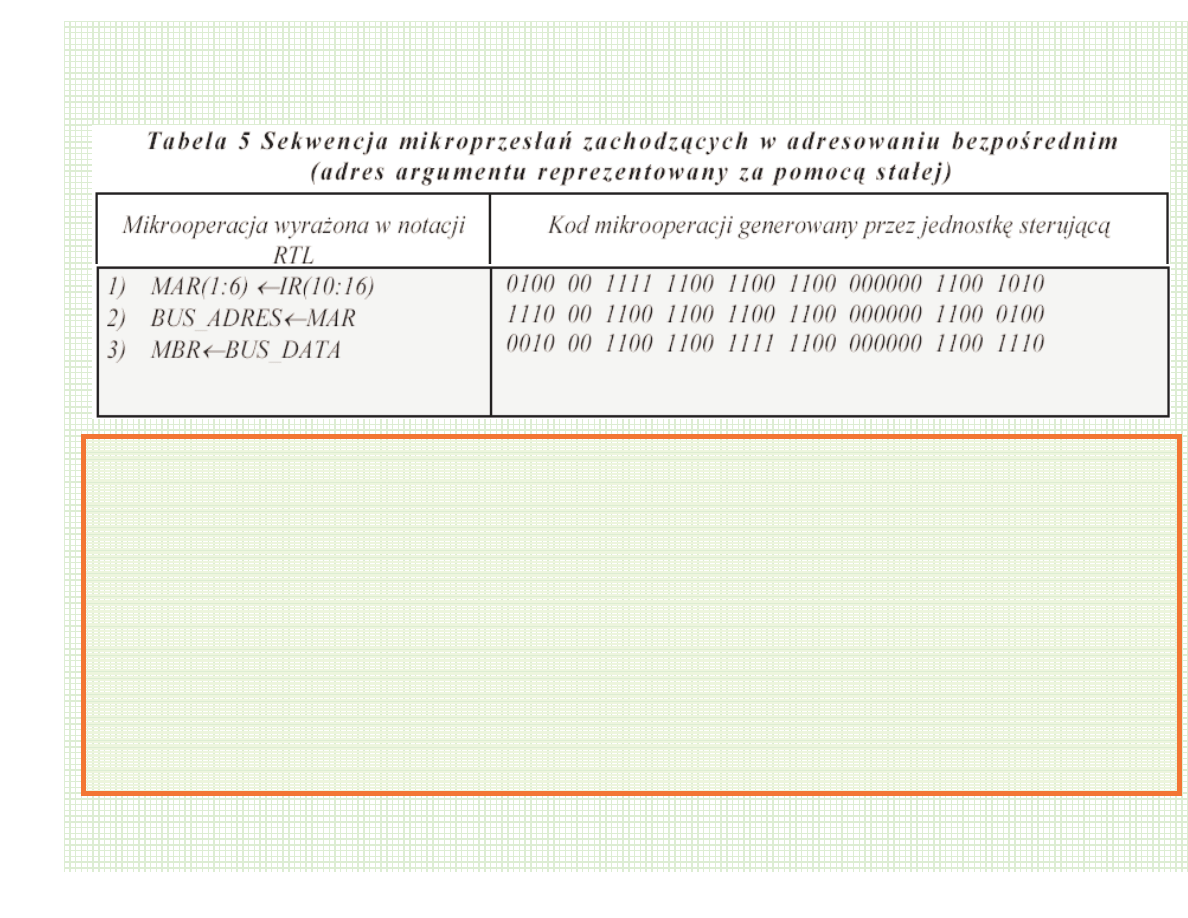

Faza adresowania -Adresowanie bezpośrednie (stała)

1.

W tym przypadku podobnie jak w adresowania natychmiastowym, adres

argumentu jest umieszczony w rejestrze rozkazów (IR) na bitach o numerze 10-

16.

2.

Wartość ta w tym przypadku nie reprezentuje wartości liczbowej tak jak to

miało miejsce w adresowaniu natychmiastowym, lecz adres komórki pamięci

operacyjnej, w której argument jest umieszczony.

3.

W celu sprowadzenia argumentu z pamięci operacyjnej należy, przesłać

odpowiednie bity rejestru (IR) do rejestru (MAR), za pomocą, którego zostanie

zaadresowana pamięć operacyjna

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

9

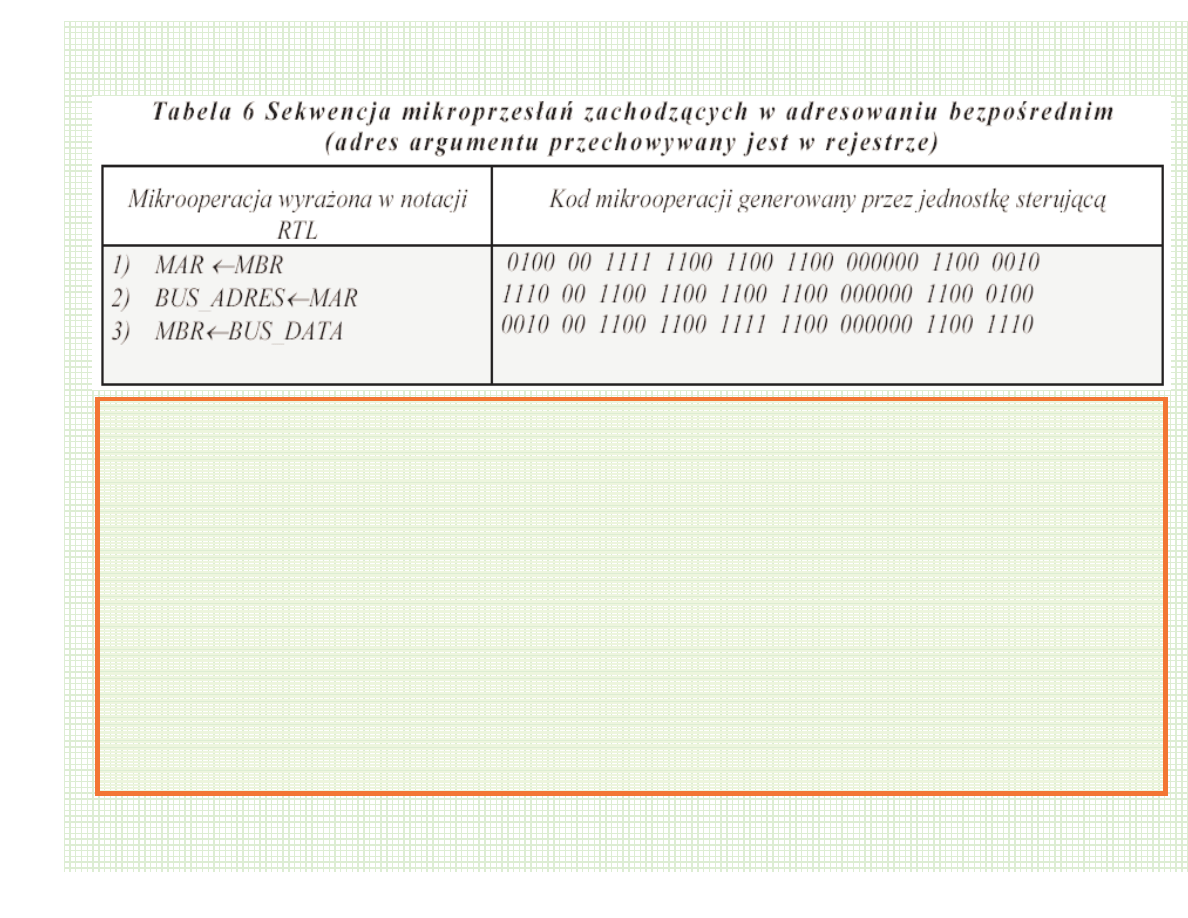

Faza adresowania -Adresowanie bezpośrednie (rejestr)

1.

Typ adresowania bezpośredniego jest związany z przypadkiem, kiedy adres

argumentu nie jest reprezentowany za pomocą stałej, lecz w określonym

rejestrze.

2.

Taki typ adresowania bezpośredniego jest niezbędny w sytuacji, w której

program wykonuje operacje nie na pojedynczej komórce pamięci

operacyjnej, której adres może być określony na etapie pisania programu, ale

na bardziej złożonych strukturach danych np. tablicach.

3.

W przypadku operacji na tablicach indeks elementu tablicy, do którego

odwołuje się program jest obliczany dynamiczne podczas wykonywania

programu.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

10

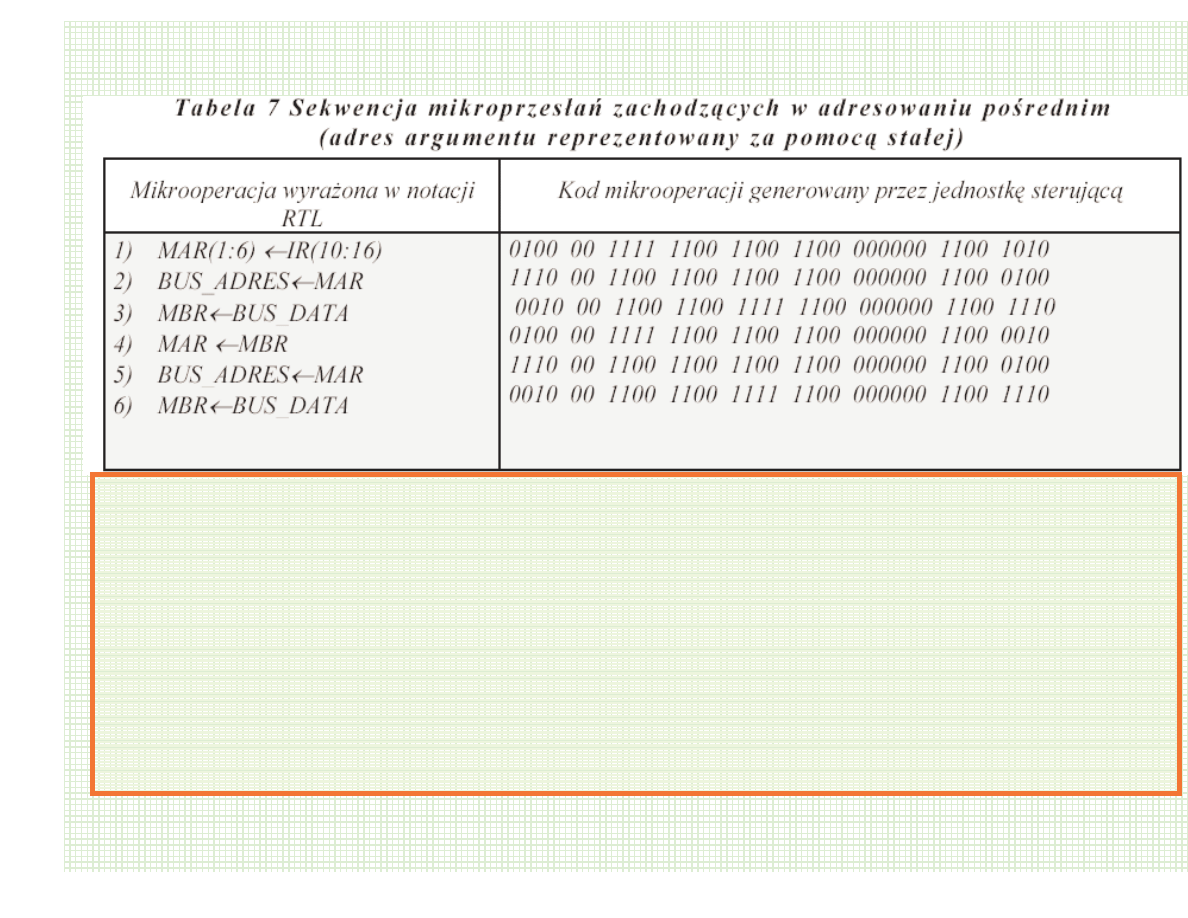

Faza adresowania -Adresowanie pośrednie (stała)

1.

Zasada działania adresowania pośredniego jest następująca: argument

występujący bezpośrednio w rozkazie nie reprezentuje wartości lecz adres

komórki pamięci operacyjnej, która to komórka nie zwiera argumentu tak jak

to miało miejsce w adresowaniu bezpośrednim , lecz zawiera adres komórki

która dopiero zawiera argument.

2.

Wynika stąd, że w celu odczytania argumentu muszą wystąpić dwa odwołania

do pamięci operacyjnej

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

11

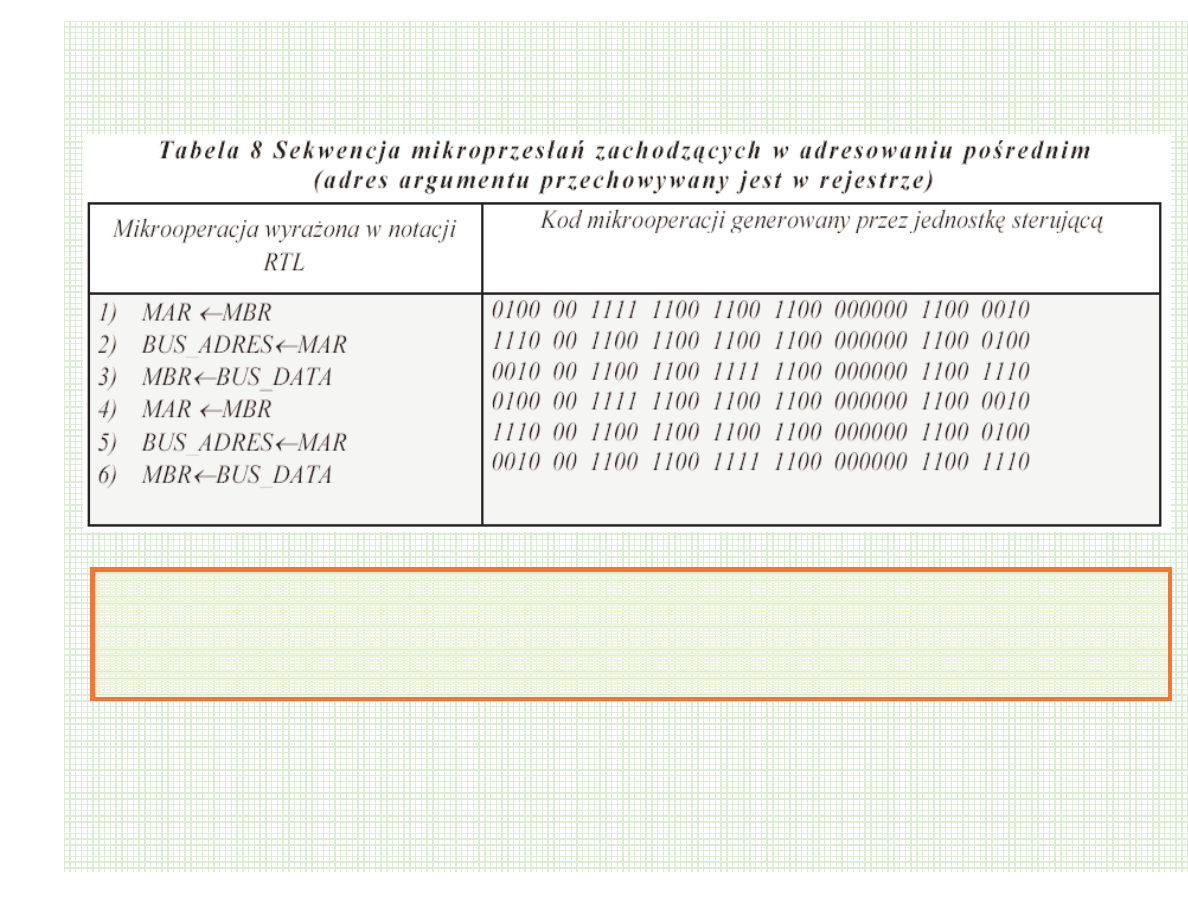

Faza adresowania -Adresowanie pośrednie (rejestr)

Podobnie ja w adresowani bezpośrednim również w tym typie adresowania jest

dopuszczalne, aby początkowy adres argumentu był umieszczony w określonym

rejestrze. Rejestrem tym jest również jest rejestr (MBR).

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

12

Faza wykonania

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

13

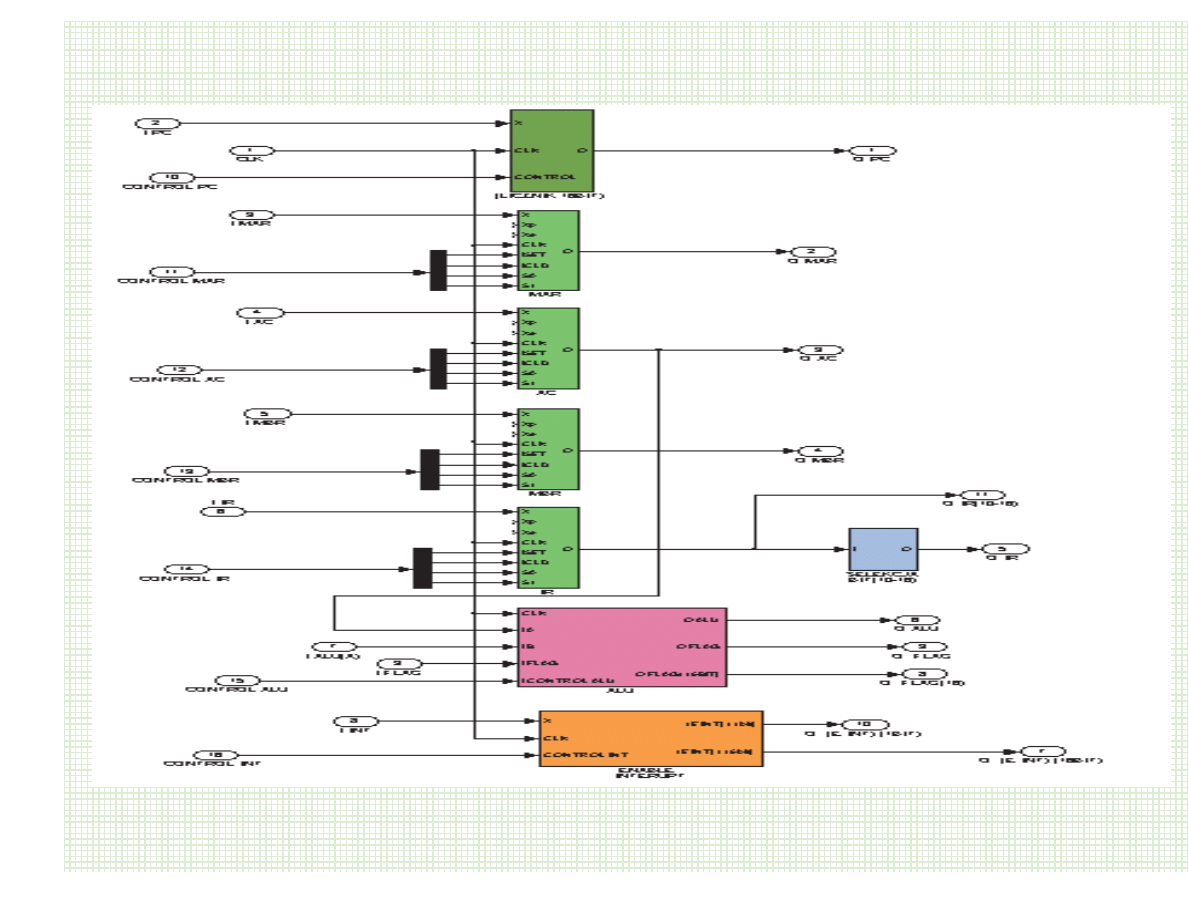

1. Demultiplekser - DEMUX

2. Licznik Rozkazów - PC

3. Rejestr Adresowy - MAR

4. Rejestr akumulacyjny - AC

5. Rejestr Buforowy - MBR

6. Rejestr Rozkazów -IR

7. ALU

8. Multiplekser – MUX

Elementy Jednostki wykonawczej

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

14

C

D

A

E

B

F

G

H

Struktura jednostki wykonawczej procesora

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

15

Struktura jednostki wykonawczej procesora

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

16

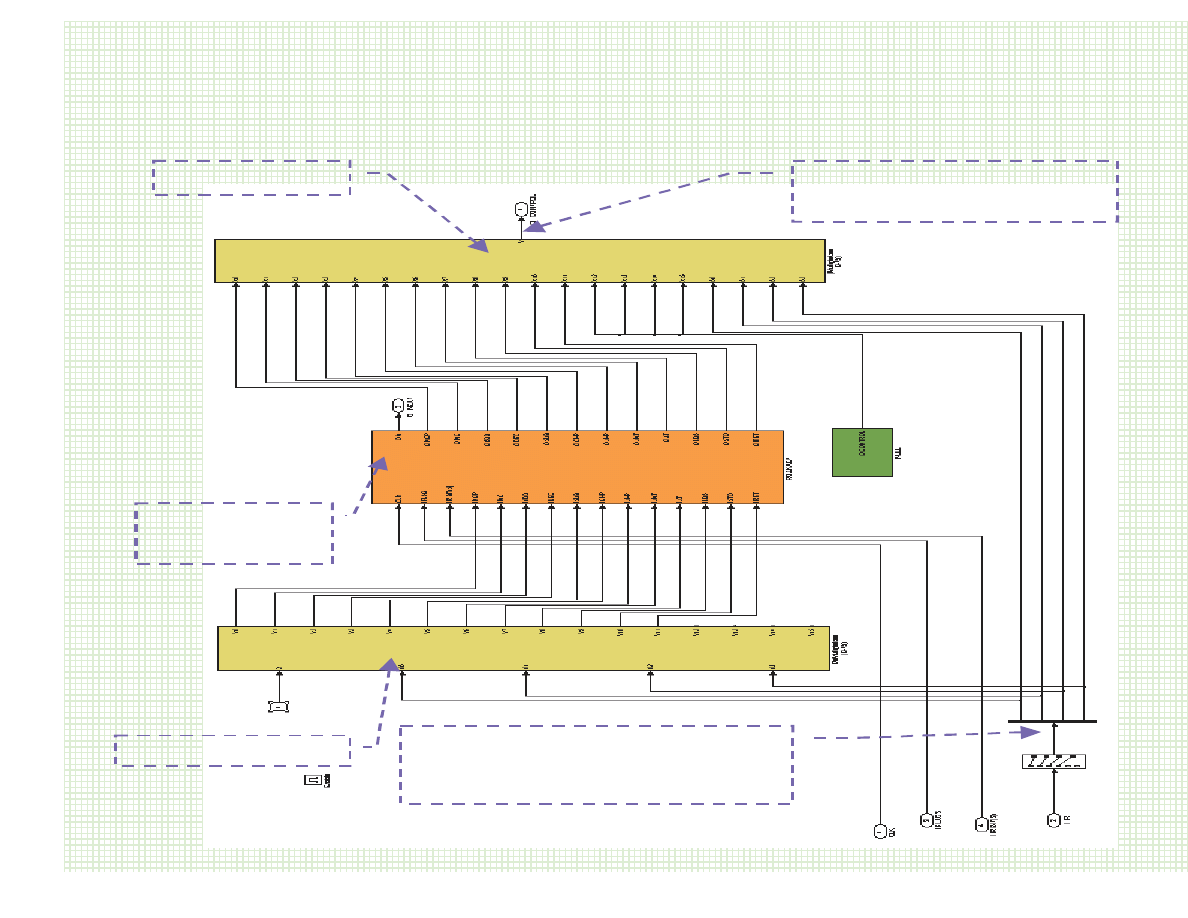

S y g n a ł s t e r u j ą c y d l a

j e d n o s t k i w y k o n a w c z e j

p r o c e s o r a

S z e ś c i o b i t o w y k o d r o z k a z u

p o d a w a n y n a w e j ś c i a

a d r e s o w e m u l t i p l e k s e r a i

d e m u l t i p l e k s e r a

B l o k

i n t e r p r e t a c j

i r o z k a z u

M u l t i p l e k s e r

D e m u l t i p l e k s e r

Organizacja podsystemu odpowiedzialnego za fazę

wykonania – interpreter rozkazów

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

17

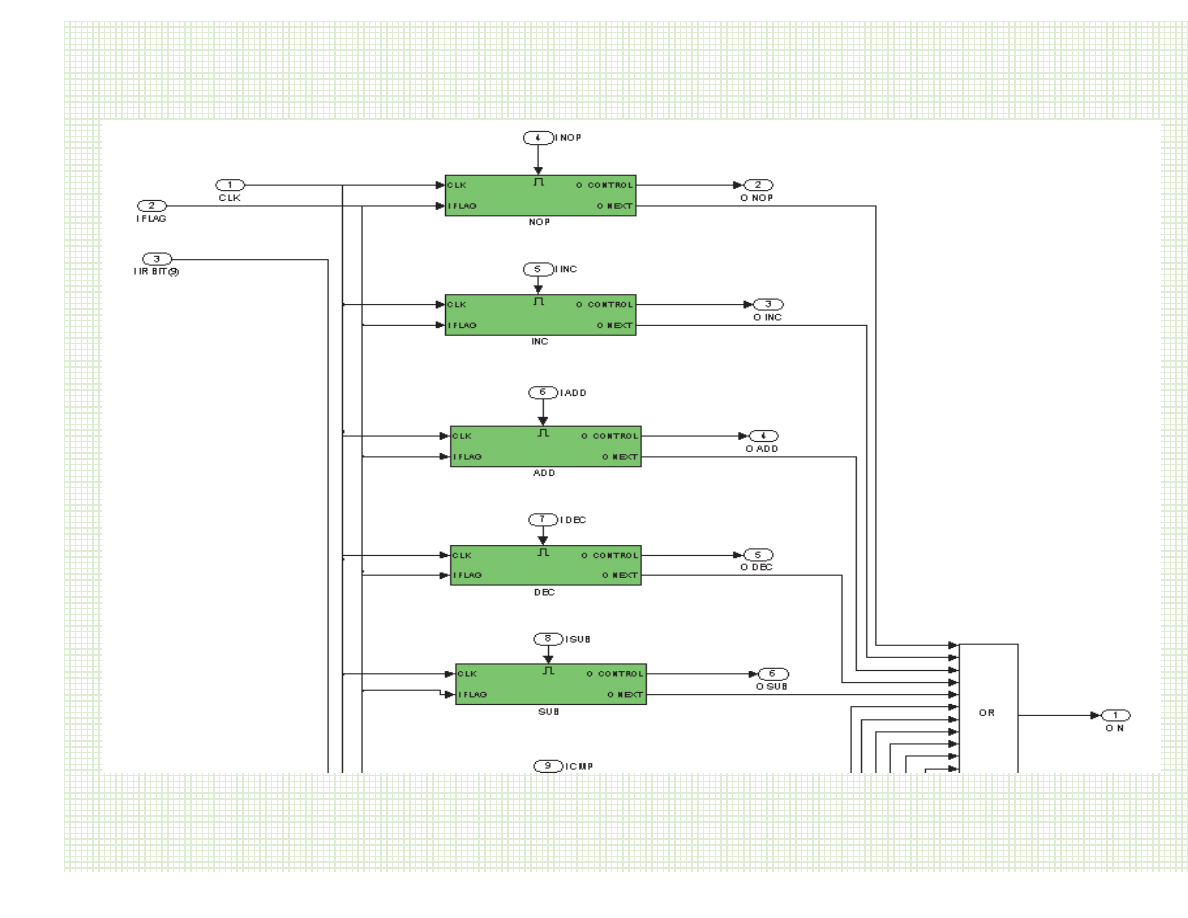

Fragment interpretera rozkazów

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

18

1. Ponieważ w ustalonym formacie rozkazu maszynowego

procesora , zostało przyjęte, że wszystkie rozkazy, w które

będzie wyposażony procesor będą rozkazami posiadającymi

maksymalnie jeden argument.

2. W przypadku rozkazów dwuargumentowych- drugi argument

będzie umieszczony w miejscu domyślnym związanym z

semantyką danego rozkazu

3. Operacja , które wymagają dwóch dwóch argumentów np.

rozkaz dodawania (ADD) zostaje przyjęte, że drugi argument

(domyślny) jest umieszczony w rejestrze akumulatora (AC).

4. Również wynik operacji jest zapisywany w rejestrze (AC).

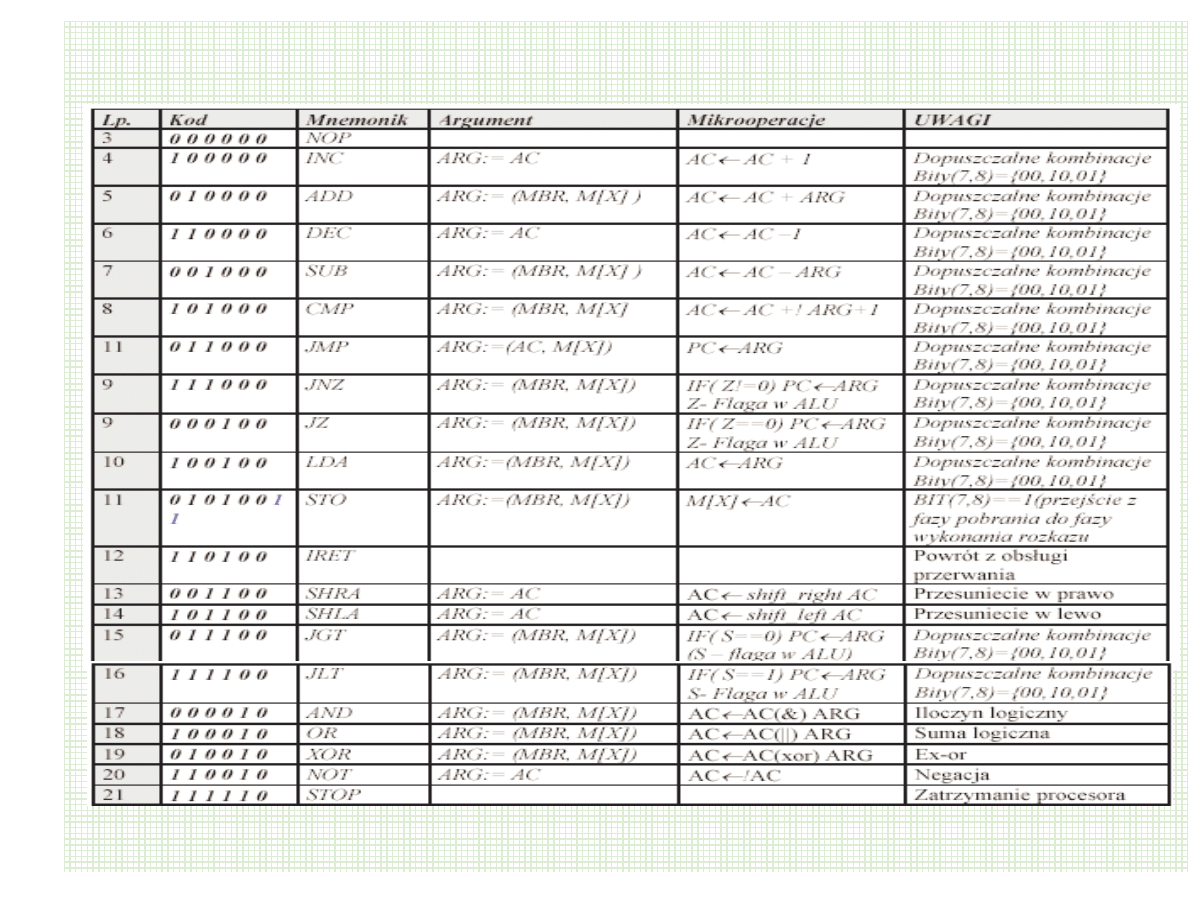

Lista rozkazów procesora - konwencje

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

19

Lista rozkazów procesora

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

20

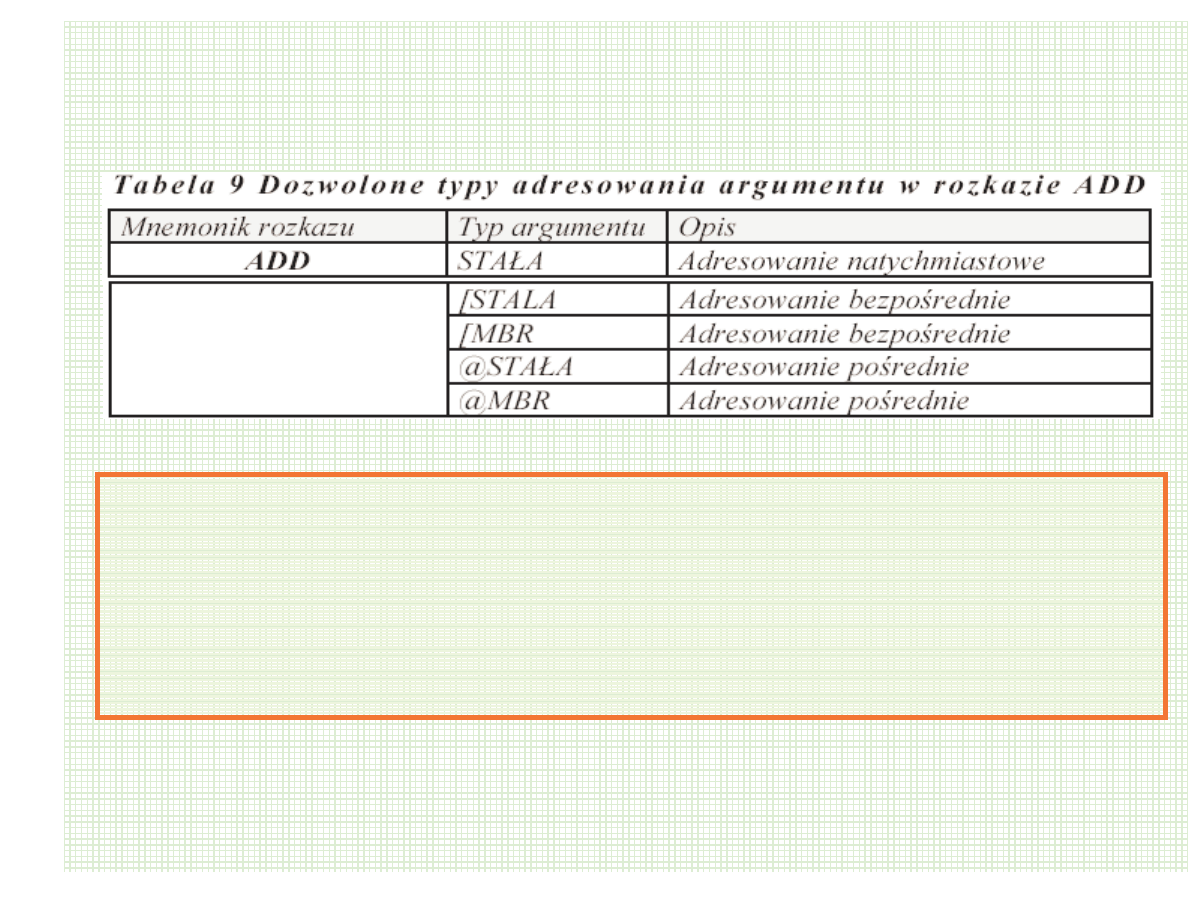

Lista rozkazów procesora (ADD)

1.

Argument rozkazu (ADD) może być dowolnym argumentem należącym do

jednej z wcześniej omówionej kategorii argumentów tzn. może być stałą,

można stosować wszystkie wymienione wcześniej typy adresowania.

2.

Wszystkie typy adresowania, które mogą używane do określenia wartości

argumentu zostały przedstawione w tabeli

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

21

Lista rozkazów procesora (ADD)

1.

Tabela 10 został przedstawiony skrót mnemoniczny rozkazu dodawania oraz

odpowiadającym mu kodem binarnym – sześć bitów, pozostałe bity

szesnastobitowego rozkazu kodują typ adresowania i wartość lub adres

argumentu.

2.

Kolumna środkowa zwiera ciąg operacji, które zachodzą w trakcie

wykonywania rozkazu.

3.

Natomiast ostatnia kolumna omawianej tabeli zawiera sekwencje sygnałów,

które są generowane przez jednostkę stertującą, a właściwie przez podsystem

jednostki sterującej odpowiedzialny za sterowania przebiegiem fazy

wykonania.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

22

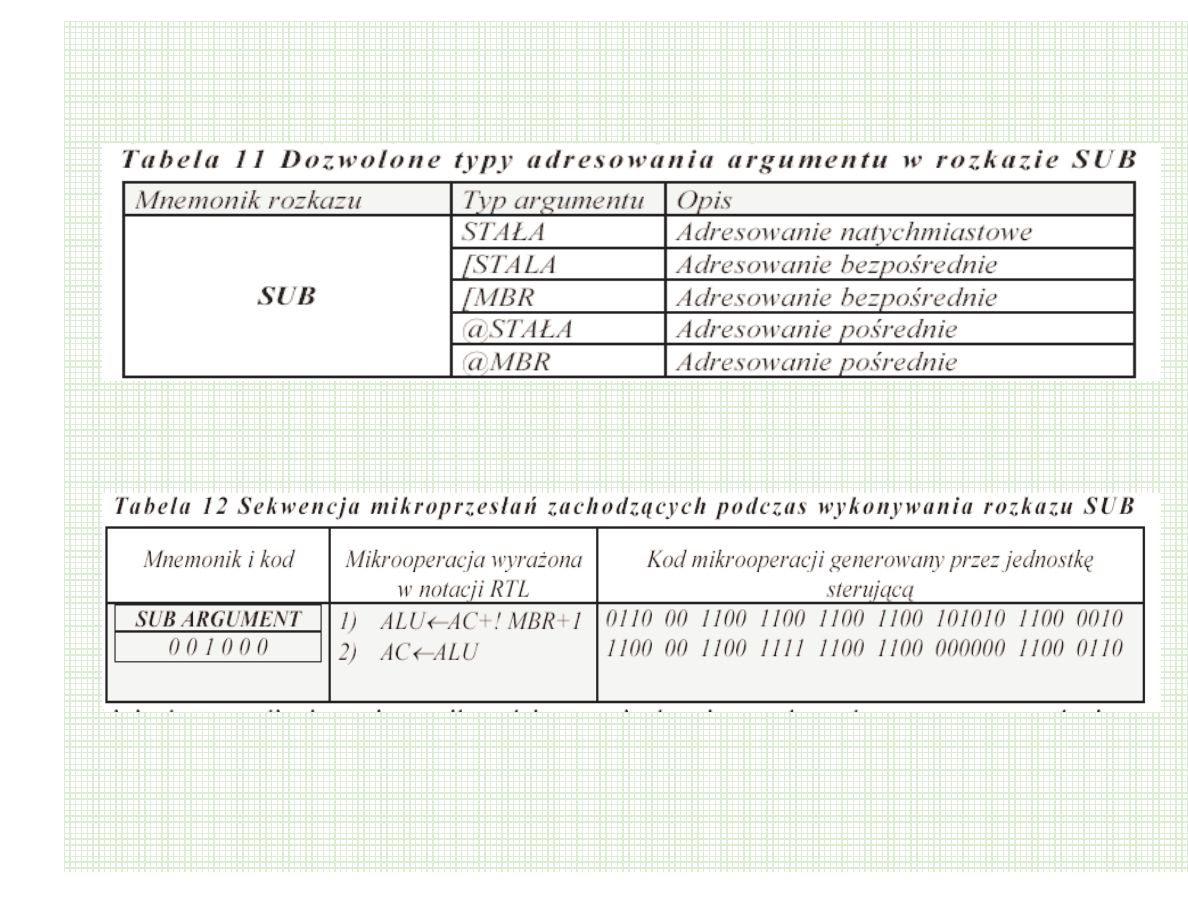

Lista rozkazów procesora (SUB)

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

23

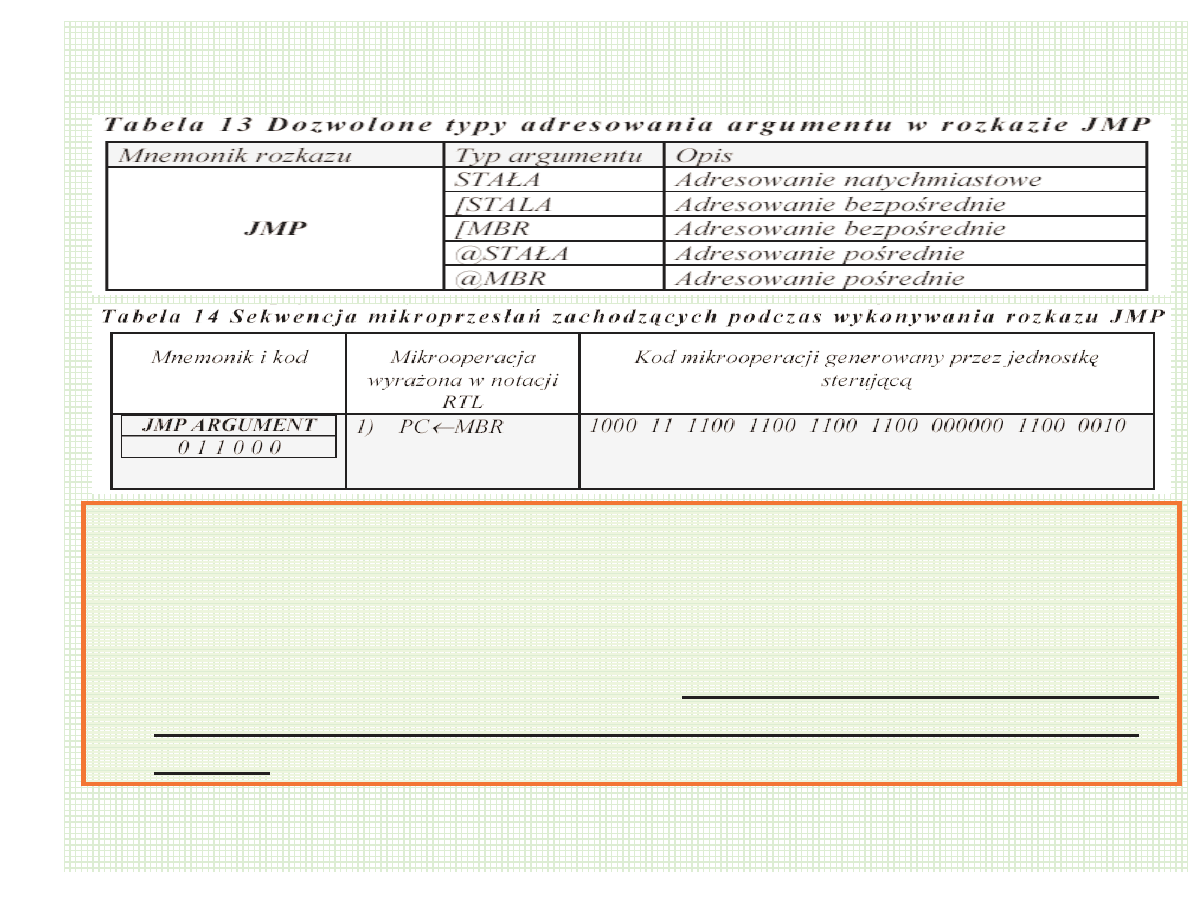

Lista rozkazów procesora (JMP)

1.

Rozkaz skoku bezwarunkowego należy do grupy rozkazów odpowiedzialnych

za sterowanie wykonywanym programem. Do grupy tej zaliczane są rozkazy

skoku bezwarunkowego, warunkowego oraz rozkazy wywołania podprogramu.

2.

Rozkaz skoku bezwarunkowego posiada, jeden argument, który jest adresem

komórki pamięci operacyjnej, do której nastąpi skok w chwili wykonania

rozkazu.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

24

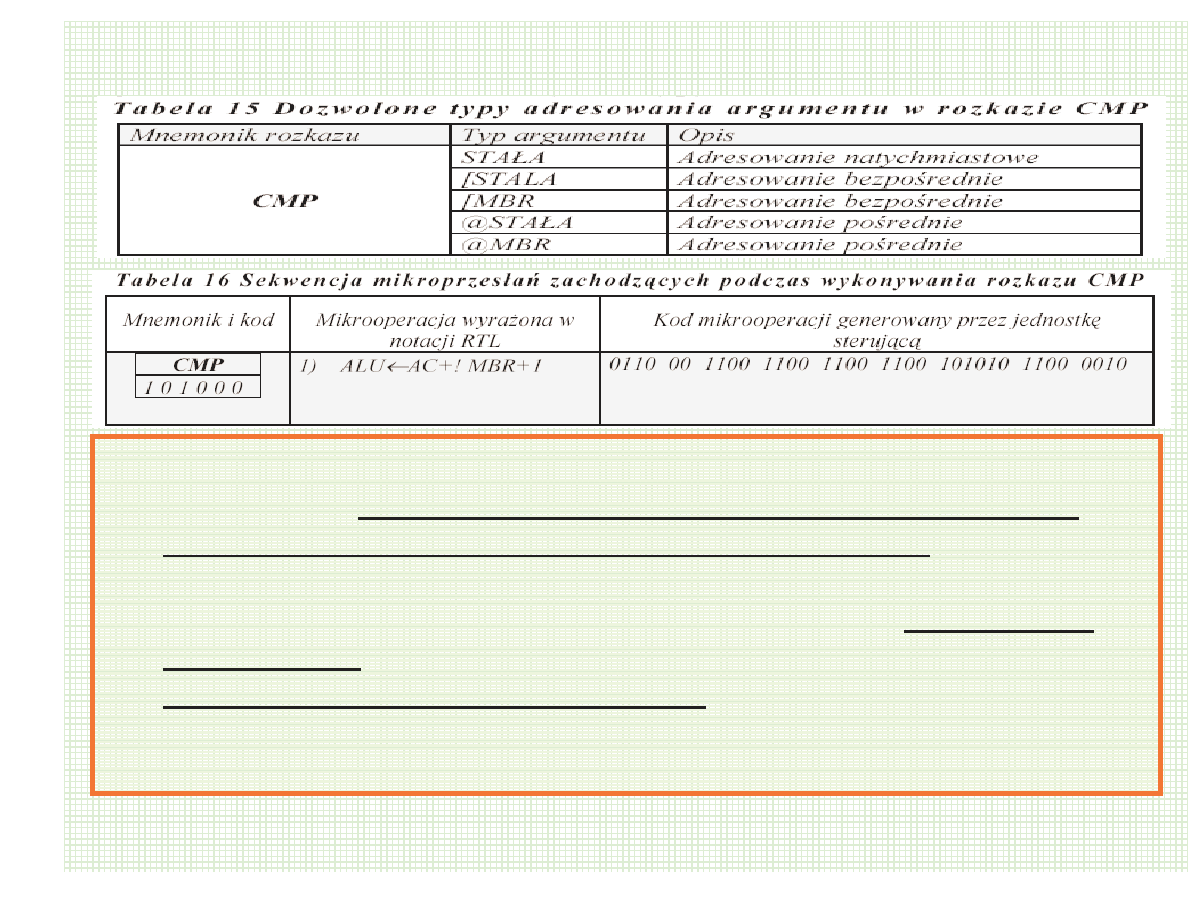

Lista rozkazów procesora (CMP)

1.

Rozkaz porównywania jest rozkazem ściśle powiązanym z rozkazami skoku

warunkowego. W wyniku wykonania tego rozkazu zostaje zmieniona

zawartość rejestru stanu (FLAG) jednostki wykonawczej.

2.

Rozkazy rozgałęzienia warunkowego taki jak rozkazy skoku warunkowego

uzależniają wykonania skoku od wartości poszczególnych bitów rejestru

stanu (FLAG).

3.

Rozkaz ten wymaga dwóch argumentów. Jeden z argumentów jest

przechowywany w rejestrze akumulatora, natomiast drugi jest

przechowywany w rejestrze buforowym.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

25

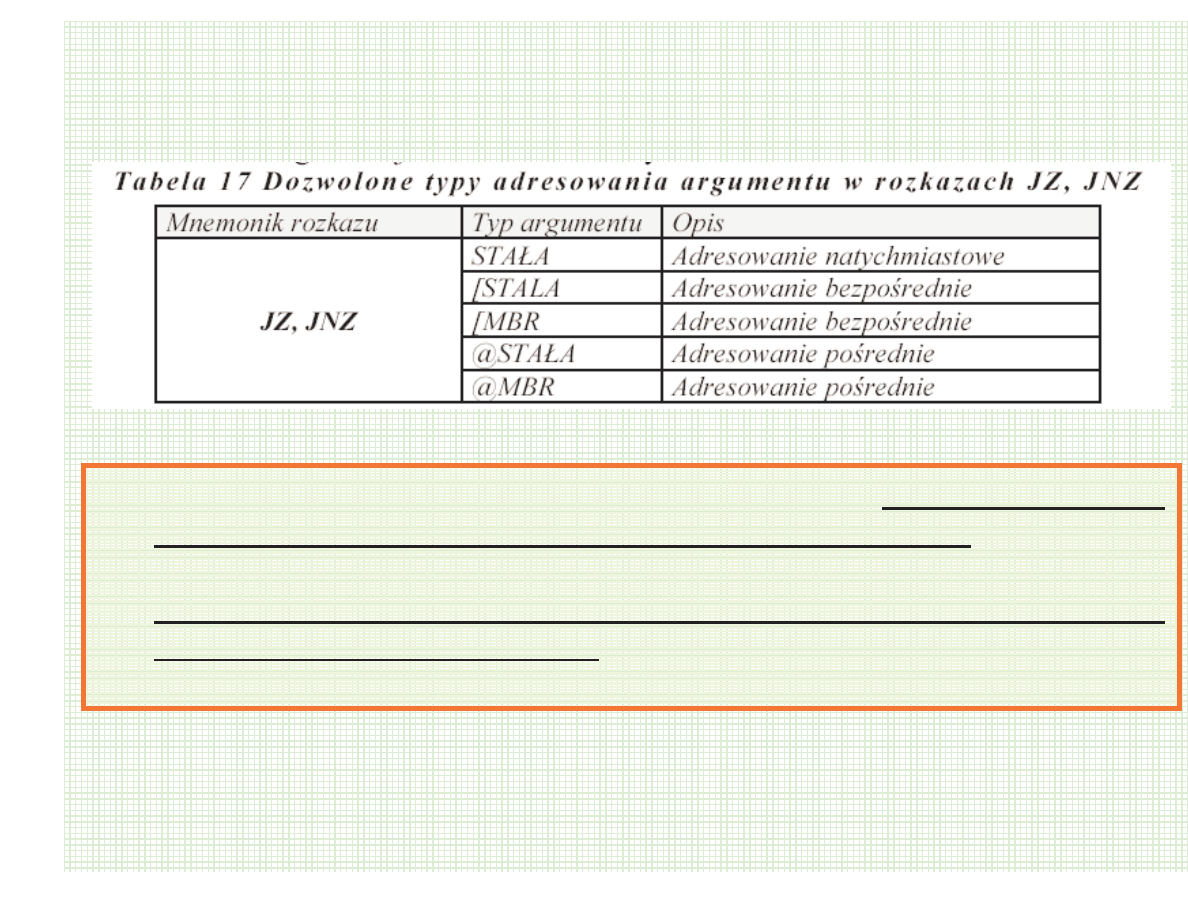

Lista rozkazów procesora (JZ, JNZ)

1.

Rozkazy skoku warunkowego również są zaliczane do grupy rozkazów

odpowiedzialnych za sterowanie wykonywanym programem.

2.

Podobnie jak w przypadku rozkazu skoku bezwarunkowego, rozkazy te są

rozkazami jednoargumentowymi. Tabela 17 zawiera listę typów adresowania,

które mogą być stosowane przy rozkazów skoku warunkowego.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

26

Lista rozkazów procesora (JZ, JNZ)

Tabele Tabela 18,19 i zawierają sekwencje mikrorozkazów, które są generowane

podczas wykonywania odpowiedni rozkazu JZ i rozkazu JNZ.

Proces wykonania rozkazu skoku warunkowego przebiega w sposób następujący:

1.

Rejestr (MBR) zawiera adres komórki pamięci operacyjnej, do której będzie

wykonany skok, gdy zostaną spełnione odpowiedni warunki

2.

Podczas procesu wykonania rozkazu JZ, jak wynika z przedstawionej tabeli

testowany, jest trzeci bit rejestru wskaźników. Jeżeli jest on równy jeden

wtedy następuje przesłanie danych z rejestru (MBR) do rejestru (PC).

JZ. Rozkaz (JZ) ten należy interpretować w sposób następujący, skok do komórki

pamięci operacyjnej o adresie wskazywanej przez argument rozkazu zostanie

wykonany, jeżeli na wyjściu jednostki ALU występują same zera.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

27

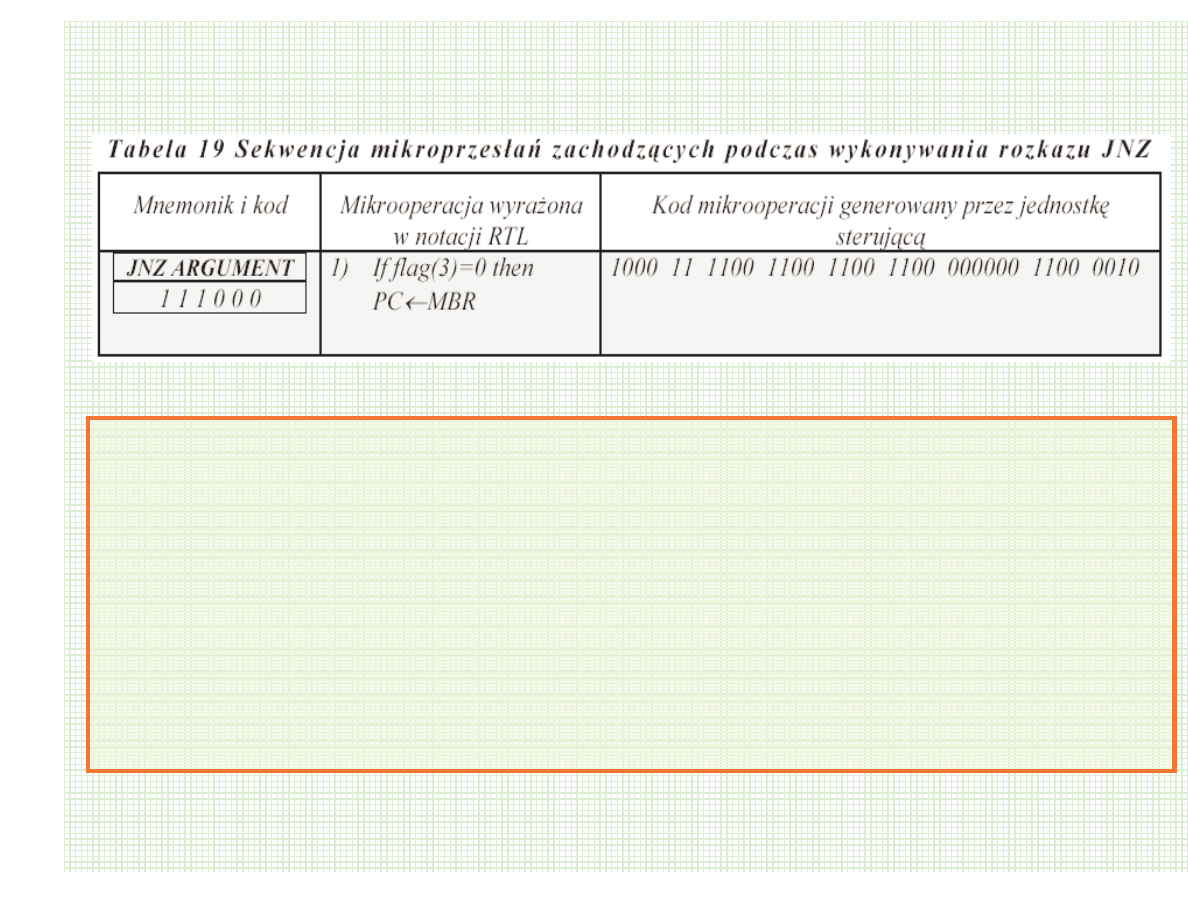

Lista rozkazów procesora (JZ, JNZ)

1.

Wykonanie rozkazu JNZ, przebiega bardzo podobnie. Tak samo jak przy

wykonaniu rozkazu JZ, rejestr (MBR) zawiera adres komórki pamięci

operacyjnej.

2.

Podczas procesu wykonania testowany, jest trzeci bit rejestru wskaźników, tak

samo jak to miało miejsce podczas wykonania rozkazu JZ.

3.

Jeżeli jest on równy zero wtedy następuje przesłanie danych z rejestru (MBR)

do rejestru (PC).

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

28

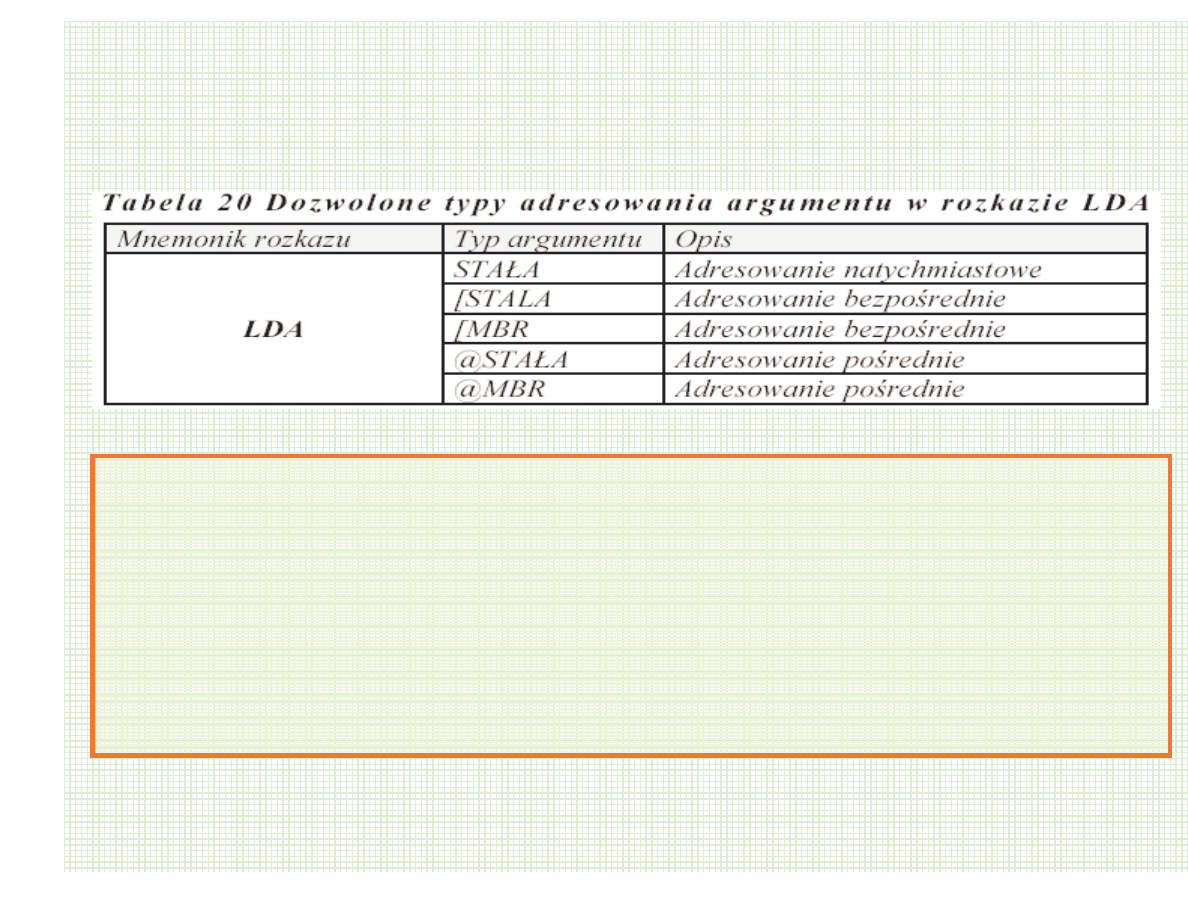

Lista rozkazów procesora (LDA)

1.

Rozkazem, który przesyła dane pamięci operacyjnej do rejestru akumulatora,

jest rozkaz o nazwie LDA.

2.

Rozkaz ten jak już powiedziano, przesyła dane z komórki pamięci

operacyjnej. Adres komórki pamięci jest określony za pomocą argumentu

rozkazu.

3.

Ten adres stanowi jeden argument rozkazu.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

29

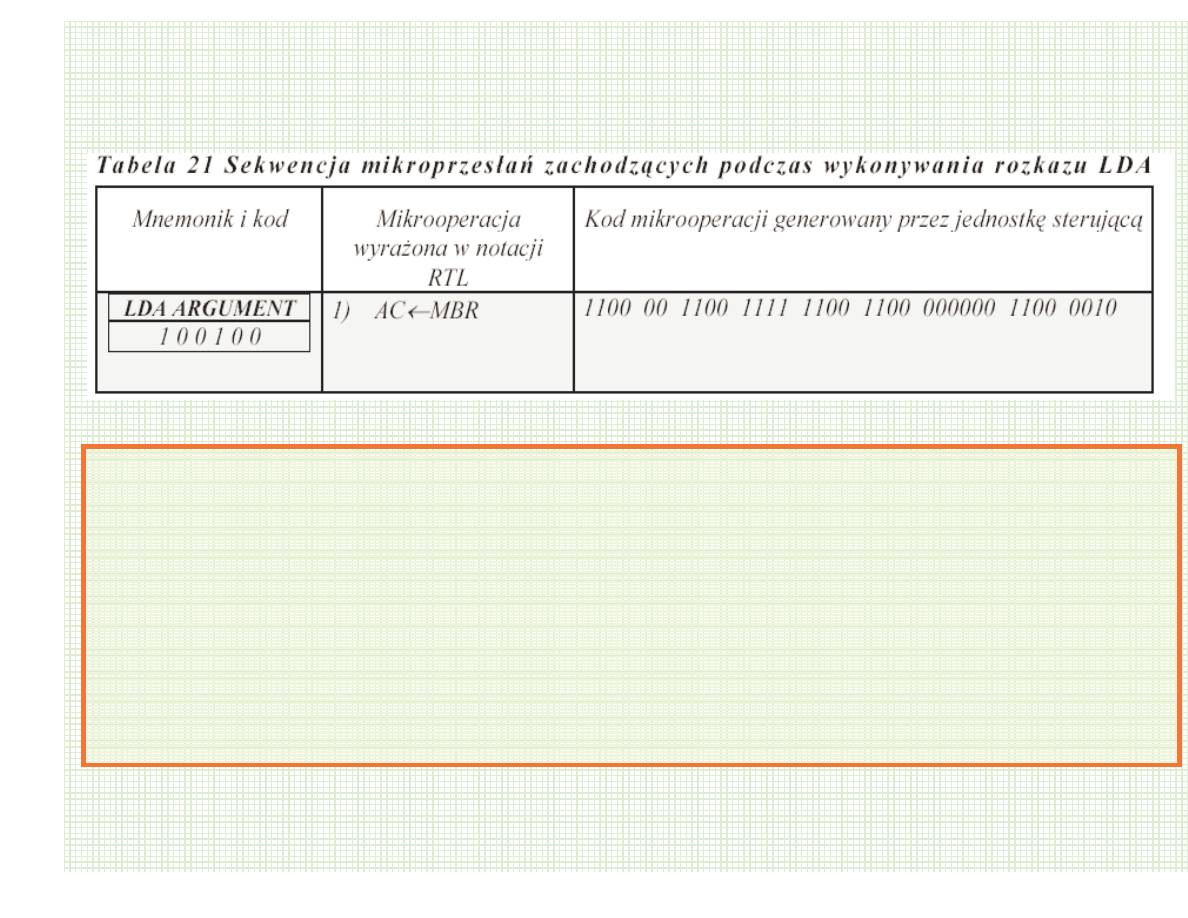

1.

Tabela 21 zawiera sekwencje mikrooperacji mają miejsce w jednostce

wykonawczej w czasie trwania fazy wykonania związanej z omawianym

rozkazem.

2.

W przypadku tego rozkazu w fazie wykonania występuje tylko jedno przesłanie

między rejestrowe – zawartość rejestru (MBR) jest przesyłana do rejestru (AC).

3.

W tym przypadku, występuje tylko jedno przesłanie, ponieważ zawartość

komórki pamięci operacyjnej, została sprowadzona do rejestru (MBR) podczas

fazy adresowania.

Lista rozkazów procesora (LDA)

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

30

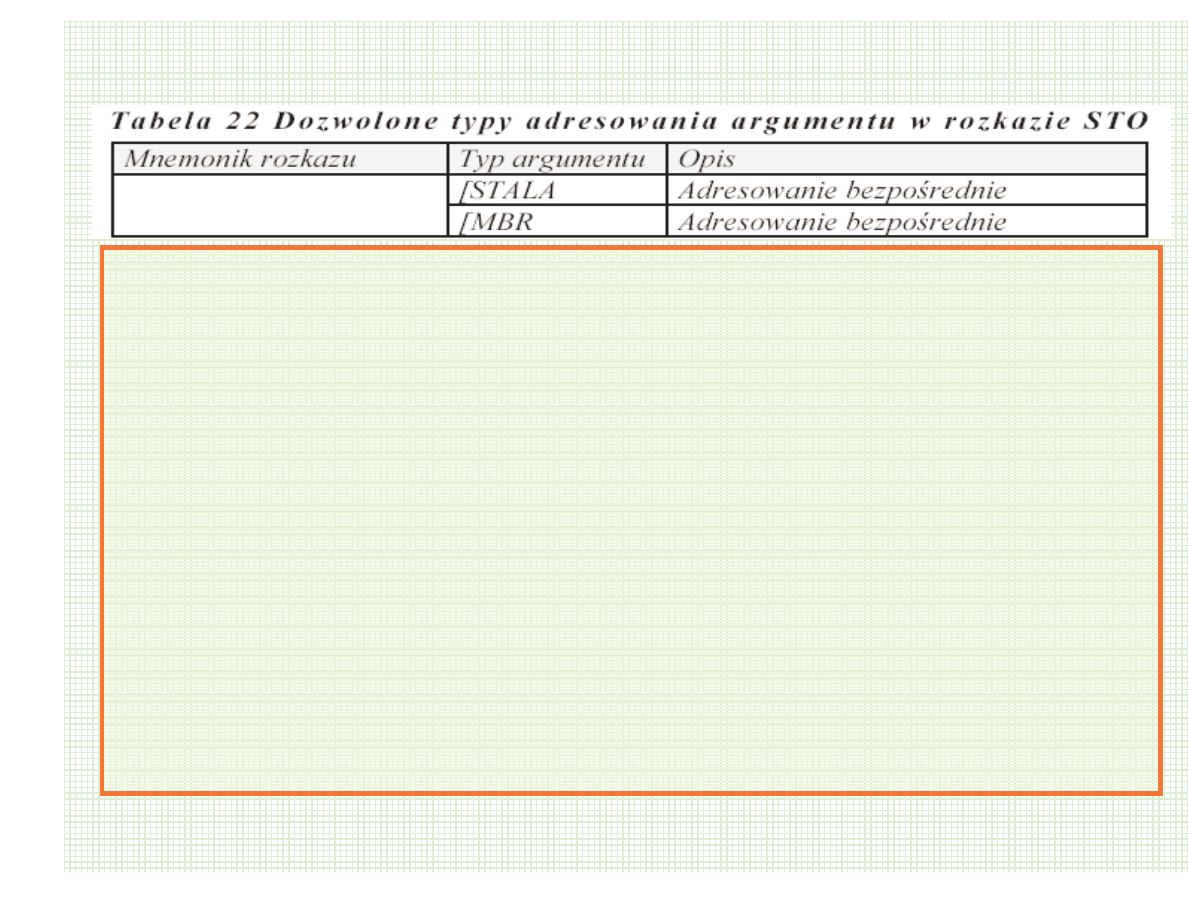

Lista rozkazów procesora (STO)

1.

Rozkaz ten jest rozkazem jednoargumentowym. Argument tego rozkazu

określa adres komórki pamięci operacyjnej, do której ma zostać przesłana

zawartość rejestru akumulatora.

2.

Tabela 22 zwiera dozwolone tryby adresowania, które mogą być stosowane

w przypadku tego rozkazu.

3.

W porównaniu do przednich rozkazów, lista trybów adresowania, które

można stosować w przypadku tego rozkazu została ograniczona – można

tylko stosować adresowanie bezpośrednie. Stosowanie adresowania

natychmiastowego w przypadku rozkazu przesyłającego dane do pamięci

operacyjnej niema sensu, ponieważ z założenia funkcjonowania tego rozkazy

wynika, że argument tego rozkazu określa adres komórki pamięci

operacyjnej.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

31

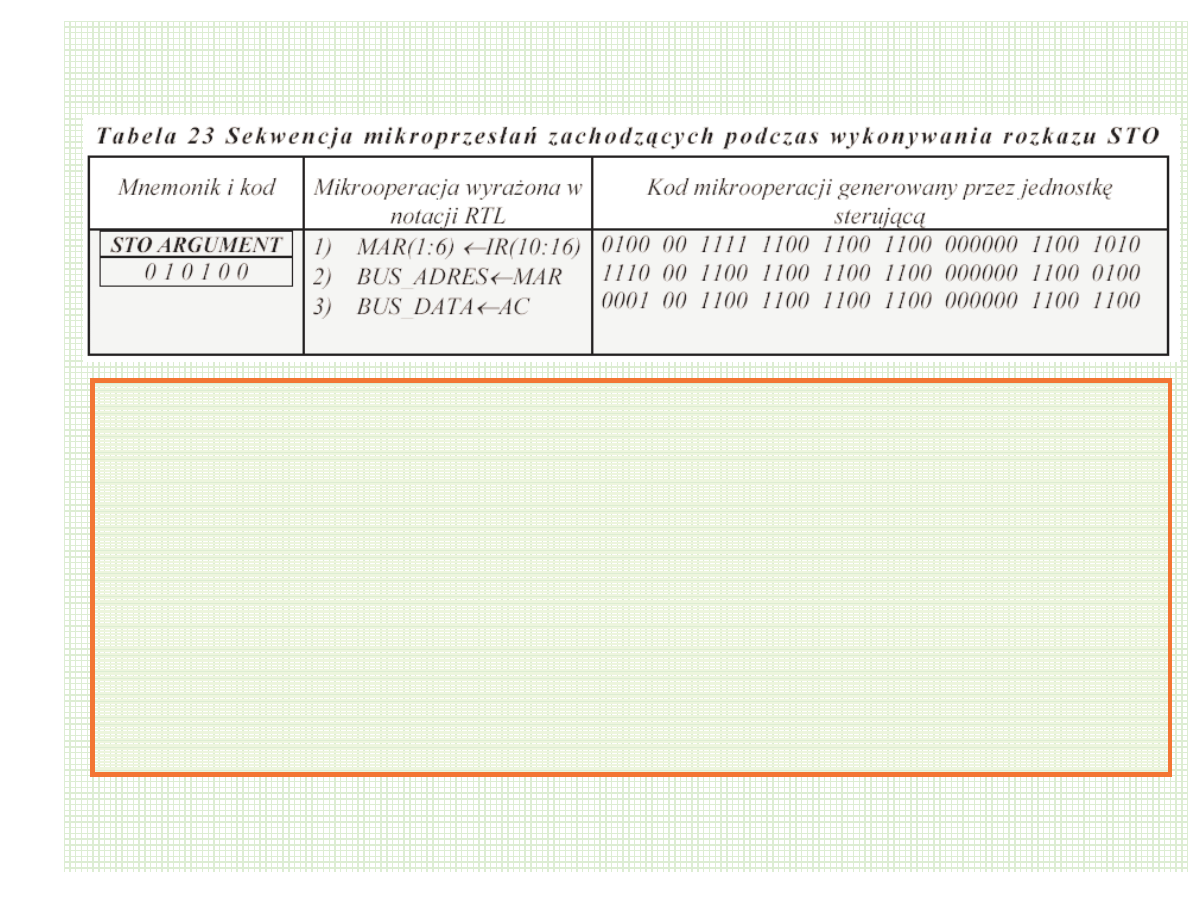

Lista rozkazów procesora (STO)

1.

Do określenia adresu komórki pamięci, do której ma zostać przesłana

zawartość rejestr (AC) może być tylko stosowane adresowanie bezpośrednie:

(stała lub rejestr).

2.

Sam proces adresowania odbywa się w fazie wykonania.

3.

Linia (1) przesłanie części zawartości rejestru rozkazu do rejestru (MAR).

Linia(2) powoduje zaadresowanie pamięci operacyjnej. Ostatnia linia realizuje

proces przesłania zawartości rejestru akumulatora (AC) do pamięci

operacyjnej.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

32

Format rozkazów

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

33

Formaty rozkazów

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

W przedstawionym formacie rozkazu można wyróżnić kilka typów

grup bitów:

1. Bity z pozycji 1-6 są wykorzystywane do reprezentacji kodu

rozkazu procesora

2. Bity z pozycji 7-9 służą do kodowania trybu adresowania

argumentu

3. Bity z pozycji 10-16 służą do reprezentacji stałej lub na tych

pozycjach zawarty jest kod rejestru w przypadku kiedy będzie

stosowane adresowanie rejestrowe.

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

34

Formaty rozkazów – znaczenie bitów

1.

Bity (1-6): Kod rozkazu

2.

Bity(7:9): Bity trybu adresowania

3.

Bit (7,8): Adresowania bezpośrednie (1, 0)

4.

Bit(7,8): Adresowanie pośrednie(0, 1)

5.

Bity(7:8): Procesor ze stanu „faza pobrania” przechodzi bezpośrednio do fazy

„faza wykonania rozkazu” (1, 1), omijając „fazę sprowadzania argumentów”

6.

Bity(7:8): Adresowanie natychmiastowe(0, 0)

7.

Bit(9): Argument jest stałą (0) (argument na pozycjach (10-16) jest stałą)

8.

Bit(9): Argument jest kodem rejestru (1) (argument na pozycjach (10-16) jest

kodem rejestru)

9.

Bity(10-16): Stała lub kod rejestru (zostało przyjęte, że bit 10 jest bitem

najmniej znaczącym, natomiast bit 16 jest bitem najbardziej znaczącym

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

35

Przykłady

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

36

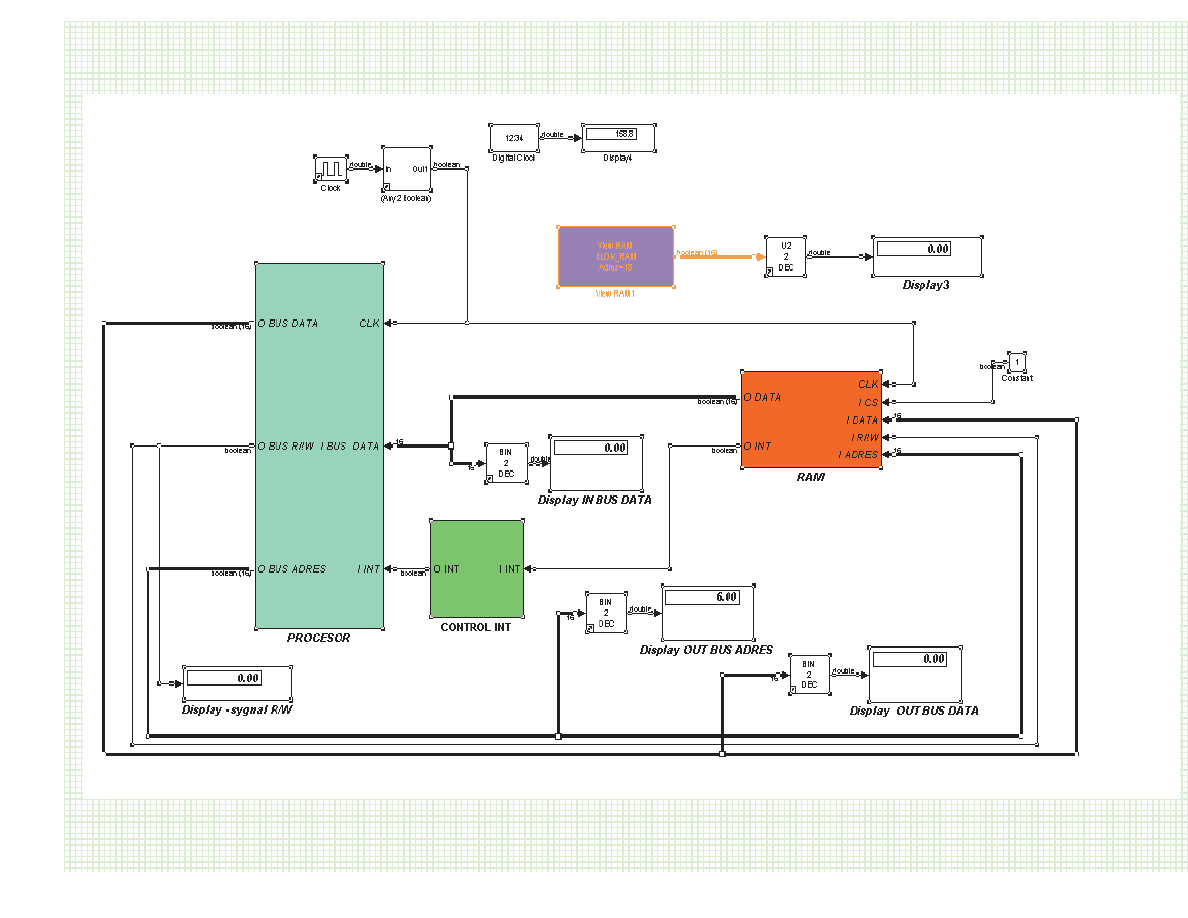

Przykład1- komputer

Architektura Komputerów(Lab) -

Budowa Procesora(lista rozkazów)

37

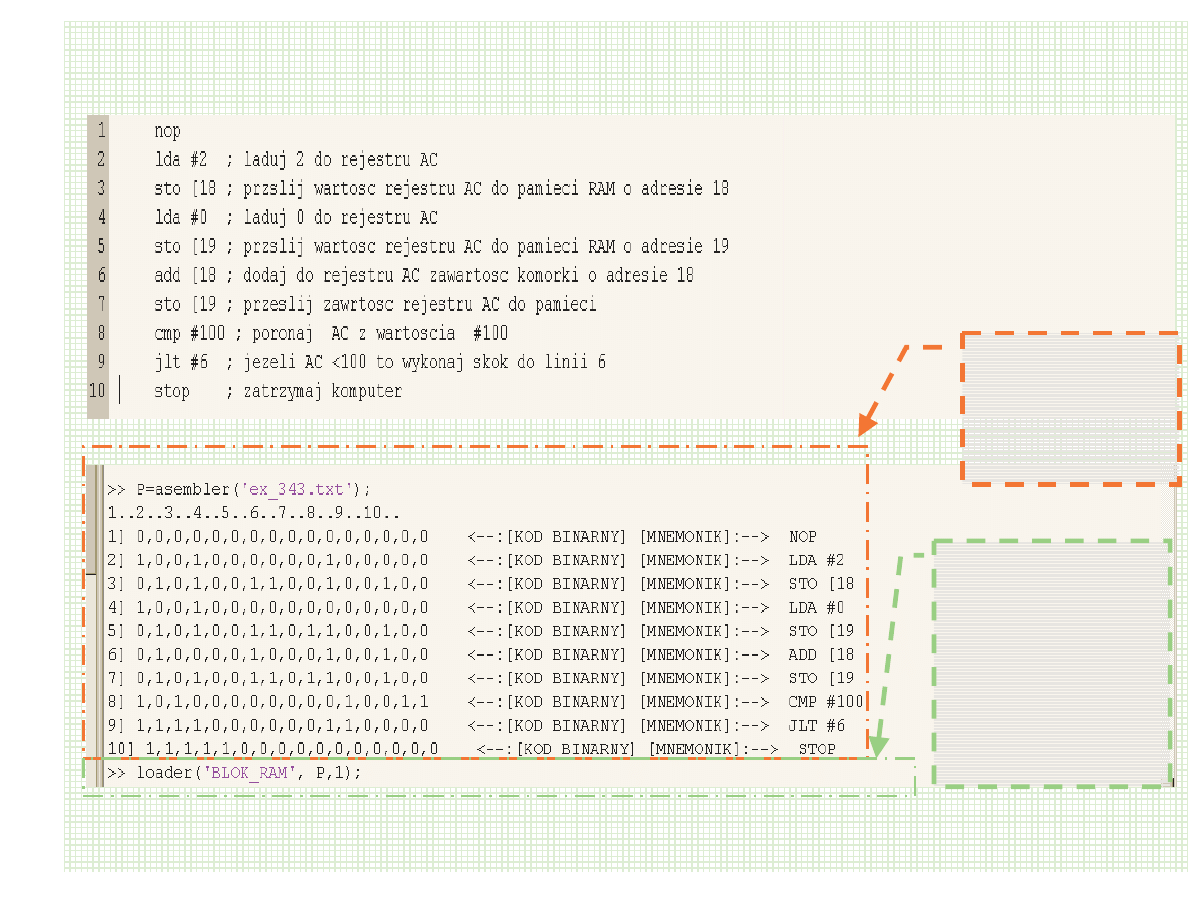

Przykład1 –program

Kompilacja

(wynik kompilacji

jest zapisany w

zmiennej P)

Ładowanie programu

do pamięci

(poczynając od

komórki o adresie 1)

Program jest

ładowany do zmiennej

‘BLOK_RAM’, która

jest skojarzona z

podsystemem RAM)

Wyszukiwarka

Podobne podstrony:

ZPKB wyk ady AK

lab6, SWBlab6

I rok AK Matematyka 2013 2014 (1)

WYKúAD 6, AK, pasemko, PROJEKTOWANIE KONSERWATORSKIE, Skumulowane wszytskie wyklady z Hoff 1 7, Skum

lab6

lab6

lab6 NHIP pyt

lab6 doc

Lab6 PSN cd 2015

AKiSO lab6

rownania nieliniowe, Automatyka i robotyka air pwr, VI SEMESTR, Notatki.. z ASE, metody numeryczne,

7, AK, pasemko, Opracowania na obronę, z roku

Czynności łączne do strzelania szkolnego nr 1 z kbk AK, UZBROJENIE

Lab6 5 id 260087 Nieznany

AK KARTA PRACY 2015 16 T 6 morf pędu

AK D Lab 1

2014 Reforma Narodowych Sił Rezerwowych utworzenie AK

Harcerska Poczta Polowa w Powstaniu Warszawskim polsihresistance ak org

więcej podobnych podstron