LABORATORIUM

„PROCESORY SYGNAŁOWE W

AUTOMATYCE PRZEMYSŁOWEJ”

Przetwornik ADC procesora sygnałowego F/C240 i DAC C240 EVM

Strona 1 z 7 Opracował mgr inż. Jacek Lis (c) ZNE 2004

1.Budowa przetwornika ADC procesora sygnałowego F/C240

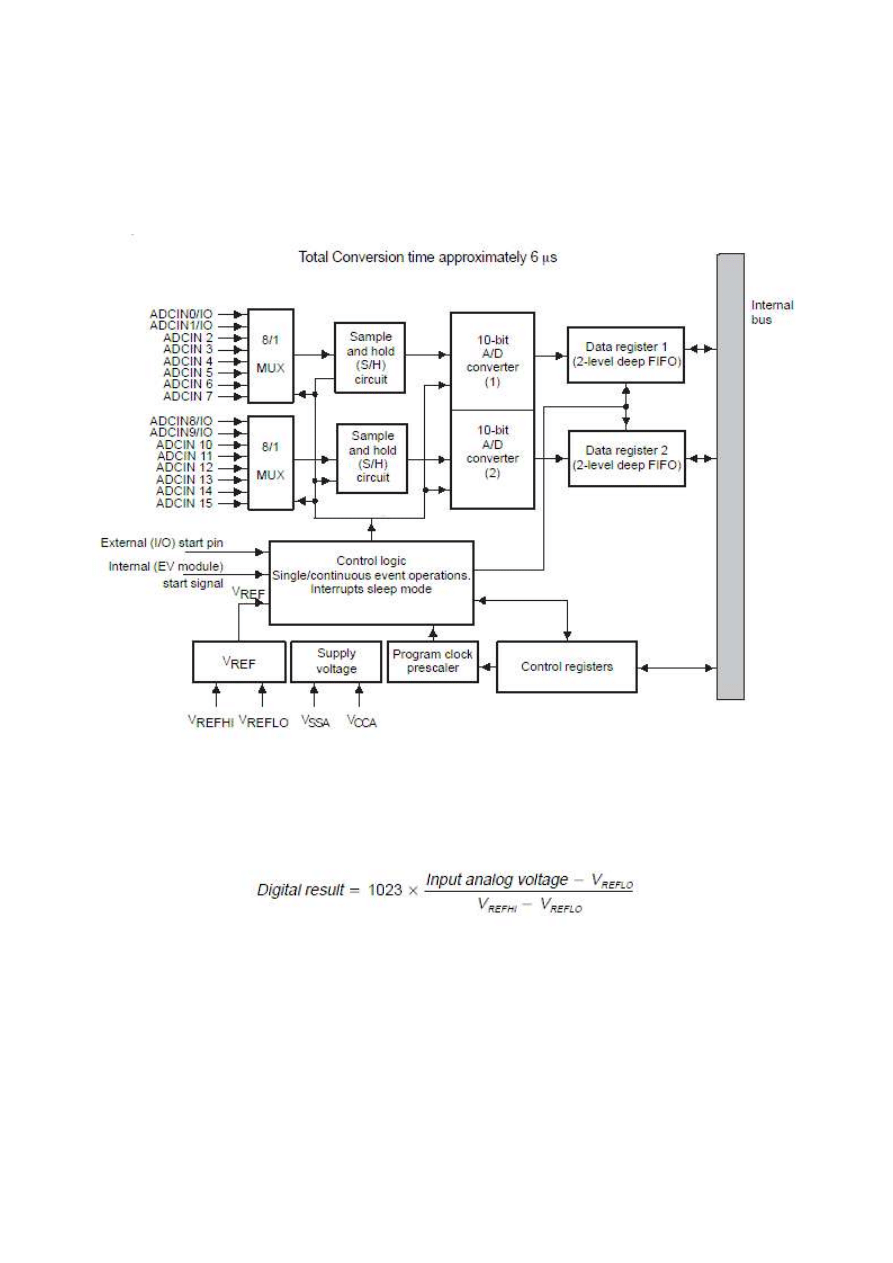

Procesor sygnałowy F/C240 posiada 16 wejściowych kanałów analogowych. Kanały te podzielone

są na 2 grupy po 8 wejść. Wejścia te przyłączone są do 2 multiplekserów (po 8 kanałów do jednego)

do których wyjścia przyłączone są jednostki S&H oraz 10 bitowe przetworniki ADC. Schematyczną

budowę torów przetważania ADC przedstawiono na poniższym rysunku:

Po zakończeniu przetwarzania wynik kierowany jest do dwupoziomowych kolejek FIFO z których

wynik może być odczytywany przez program użytkownika. Przybliżony czas pojedyńczego

przetwarzania wynosi 6μs ( 6*10

-6

- maksymalna teoretyczna częstotliwość przetwarzania ~167kHz

– możliwa do uzyskania tylko w trybie ciągłego przetwarzania ).

Wynik przetwarzania można opisać wzorem:

2.Obsługa przetwornika ADC procesora sygnałowego F/C240

Obsługę przetwornika ADC można podzielić na kilka części ściśle związanych z budową programu

w którym obrabiamy wyniki przetwarzania ADC:

•

inicjalizacja – wpis odpowiednikach wartości do rejestrów konfiguracyjnych ADCTRL1 i

ADCTRL2

Strona 2 z 7 Opracował mgr inż. Jacek Lis (c) ZNE 2004

•

Wyzwalanie przetwarzania – może odbywać się programowo, sprzętowo lub automatycznie (jeśli

przetworniki pracują w trybie ciągłym).

•

Odczyt wyników przetwarzania – może być wyzwalana przez zakończenie przetwarzania i

generowanie specjalnego przerwania lub odbywać się w funkcji obsługi innego przerwania (np.

zegarowego).

•

Obróbka wyników przetwarzania np. filtorwanie, sterowanie itp. - odbywa się najczęściej w tej

samej funkcji co odczyt wyników przetwarzania.

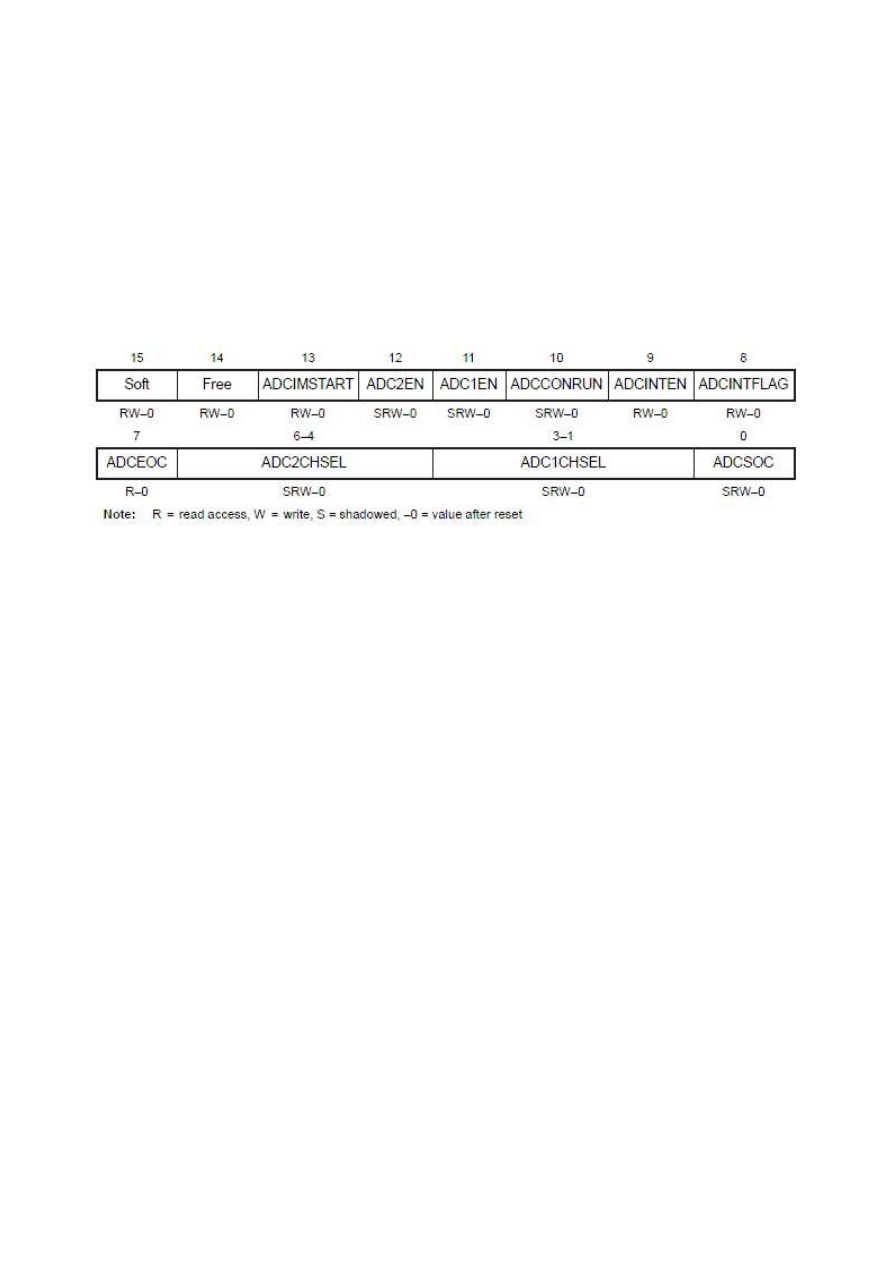

Rejestr ADCTRL1 pozwala wybrać kanały przetwornika (ustawić odpowiednio multiplekser) i

wyzwolić przetwarzanie oraz zdefiniować

Opis:

bit 15 – Soft – bit konfiguracyjny używany tylko w czasie pracy z emulatorem:

0 – Zatrzymanie pracy natychmiast gdy bit 14 = 0.

1 – Zakończeniu konwersji przed zatrzymaniem pracy emulatora.

bit 14 – Free - bit konfiguracyjny używany tylko w czasie pracy z emulatorem:

0 – Praca zależna od ustawienia bitu 15.

1 – Kontynuuj pracę po zatrzymaniu pracy emulatora.

bit 13 – ADCIMSTART – bit powodujący natychmiastowy start konwersji:

0 – Brak reakcji - normalna praca.

1 – Natychmiast rozpocznij konwersję.

bit 12 – ADC2EN – bit włączania/wyłączania 2 przetwornika ADC. Bit buforowany po zmianie

ustawienia efekt jest widoczny dopiero przy następnej konwersji:

0 – Przetwornik ADC2 zablokowany (zawartość odpowiedniej kolejki FIFO nie będzie

się zmieniać).

1 – Przetwornik ADC2 odblokowany.

bit 11 – ADC1EN – bit włączania/wyłączania 1 przetwornika ADC. Bit buforowany po zmianie

ustawienia efekt jest widoczny dopiero przy następnej konwersji:

0 – Przetwornik ADC1 zablokowany (zawartość odpowiedniej kolejki FIFO nie będzie

się zmieniać).

1 – Przetwornik ADC1 odblokowany.

bit 10 – ADCCONRUN – bit umożliwiający włączenie trybu ciągłej pracy przetworników ADC.

Strona 3 z 7 Opracował mgr inż. Jacek Lis (c) ZNE 2004

Bit buforowany po zmianie ustawienia efekt jest widoczny dopiero przy następnej konwersji:

0 – Brak reakcji - normalna praca.

1 – Tryb pracy ciągłej włączony.

bit 9 – ADCINTEN – odblokowanie przerwania, bit definiujący żądanie obsługi przerwania gdy

bit 8 = 1:

0 – Brak reakcji - normalna praca.

1 – Wystąpi żądznie obsługi przerwania gdy bit 8 = 1.

bit 8 – ADCINTFLAG – bit flagi przerwania ADC – występuje gdy choć jedno zdarzenie

przerwanie wystąpiło. Bit niebuforowany:

0 – Zdarzenie żądania obsługi przerwania nie wystąpiło.

1 – Zdarzenie żądania obsługi przerwania wystąpiło.

bit 7 – ADCEOC – bit określa stan procesu konwersacji. Bit niebuforowany:

0 – Konwersja została zakończona.

1 – Konwersja trwa.

bity 6 do 4 – ADC2CHSEL – wybór kanału dla przetwornika ADC2 (ustawienie multipleksera).

Bit buforowany po zmianie ustawienia efekt jest widoczny dopiero przy następnej konwersji.

000 – Kanał 8.

001 – Kanał 9.

010 – Kanał 10.

011 – Kanał 11.

100 – Kanał 12.

101 – Kanał 13.

110 – Kanał 14.

111 – Kanał 15.

bity 3 do 1 – ADC1CHSEL – wybór kanału dla przetwornika ADC2 (ustawienie multipleksera).

Bit buforowany po zmianie ustawienia efekt jest widoczny dopiero przy następnej konwersji.

000 – Kanał 0.

001 – Kanał 1.

010 – Kanał 2.

011 – Kanał 3.

100 – Kanał 4.

101 – Kanał 5.

110 – Kanał 6.

111 – Kanał 7.

bit 0 – ADCSOC – Bit powodujący start przetwornika ADC. Bit buforowany po zmianie

ustawienia efekt jest widoczny dopiero przy następnej konwersji.

0 – Brak reakcji.

Strona 4 z 7 Opracował mgr inż. Jacek Lis (c) ZNE 2004

1 – Rozpocznij konwersie.

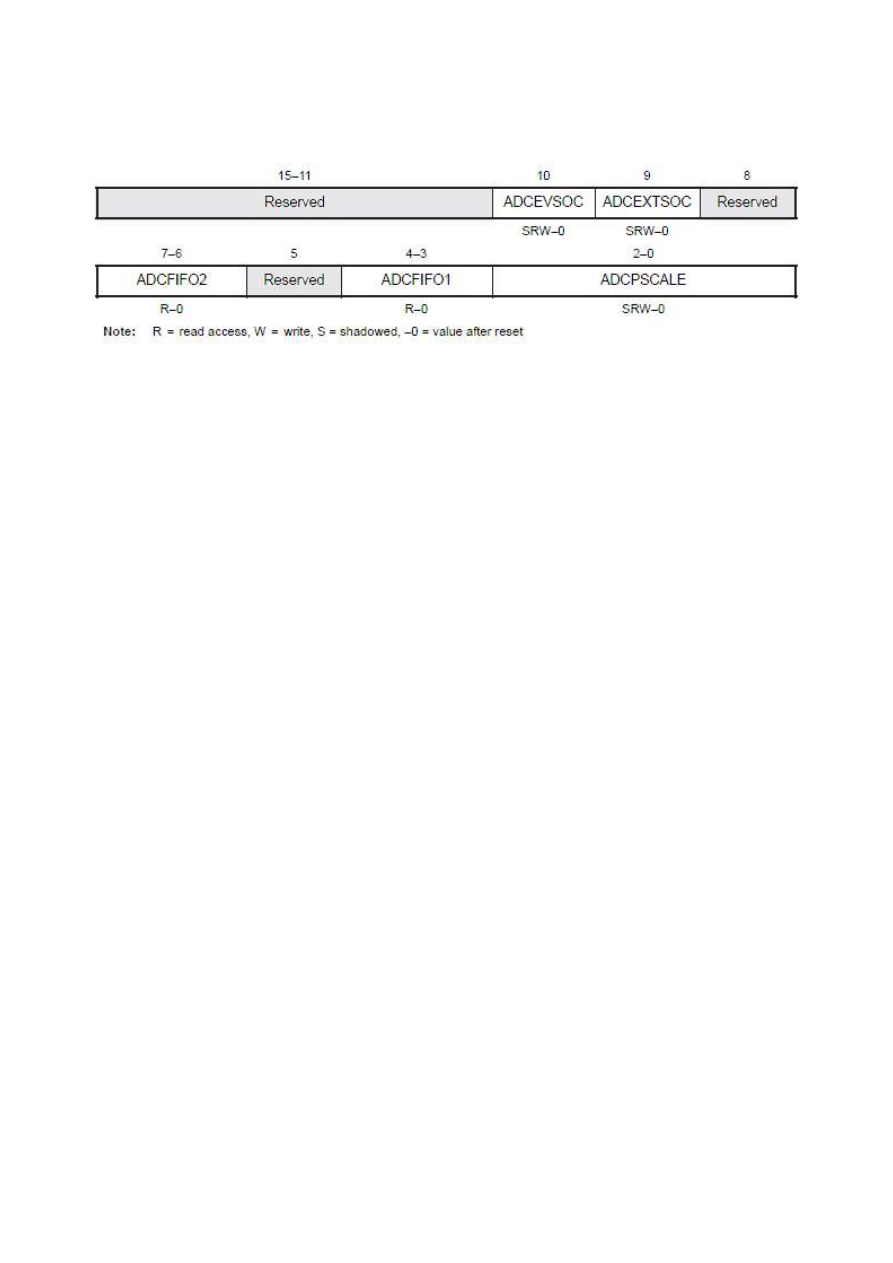

Rejestr ADCTRL2

Opis:

bity 15 – 11 – bity zastrzeżone.

Bit 10 – ADCEVSOC – bit wiążący pracą przetworników ADC z menadżerem zdarzeń (EV).

Kiedy bit jest ustawiony na 1 wtedy praca Przetwornika jest zsynchronizowana z sygnałami z EV

w ten sposób, że EV może rozpoczynać konwersję automatyczne wykożystując jako sygnał

wyzwalający zegary (1,2 lub 3) lub sygnał z detektora sygnałów - wejścia CAP4 procesora.

Wybór sygnału pobudzającego zależy od ustawień GPTCON i CAPCON.

0 – Praca przetworników (start przetwarzania) nie jest powiązana z sygnałami z EV.

1 – Praca przetworników (start przetwarzania) jest powiązana z sygnałami z EV.

bit 9 – ADCEXTSOC – bit konfiguracyjny służący do synchronizacji przetworników ADC z

zewnętrznym sygnałem sterującym. Gdy bit jest ustawiony zbocze rosnące sygnału uruchamia

przetwarzanie.

0 – Brak wpływu sygnału na wejściu ADCSOC procesora na pracę przetworników.

1 – Sygnał na wejściu ADCSOC procesora może wyzwalać przetwarzanie.

bit 8 – bit zastrzeżone.

bity 7 – 6 – ADCFIFO2 – bity informujące o stanie kolejki FIFO2. Kolejka ta przechowuje dwa

ostatnie stany konwersji, zawsze istnieje możliwość odczytania z kolejki tylko 2 ostatnich

wyników, należy pamiętać, że odczyt powoduje cofanie licznika kolejki i zmianę stanu bitów

ADCFIFO2.

00 – Kolejka FIFO2 jest pusta

01 – Kolejka FIFO2 zawiera jeden wynik przetwarzania.

10 – Kolejka FIFO2 zawiera dwa wyniki przetwarzania.

11 – Kolejka FIFO2 zawiera dwa wyniki przetwarzania i następny wynik konwersji został

skierowany do kolejki, najstarszy wynik zostanie utracony.

bit 5 – bit zastrzeżone.

bity 4 – 3 – ADCFIFO1 – bity informujące o stanie kolejki FIFO1. Kolejka ta przechowuje dwa

ostatnie stany konwersji, zawsze istnieje możliwość odczytania z kolejki tylko 2 ostatnich

wyników, należy pamiętać, że odczyt powoduje cofanie licznika kolejki i zmianę stanu bitów

ADCFIFO1.

00 – Kolejka FIFO1 jest pusta

Strona 5 z 7 Opracował mgr inż. Jacek Lis (c) ZNE 2004

01 – Kolejka FIFO1 zawiera jeden wynik przetwarzania.

10 – Kolejka FIFO1 zawiera dwa wyniki przetwarzania.

11 – Kolejka FIFO1 zawiera dwa wyniki przetwarzania i następny wynik konwersji został

skierowany do kolejki, najstarszy wynik zostanie utracony.

bity 2 – 0 – ADCPSCALE – ta grupa bitów definiuje preskaler sygnału taktującego przetwornik

ADC w stosunku do głównego sygnału taktującego (zwykle 10MHz, uwaga nie jest to sygnał

taktujący jądro procesora – 20MHz).

000 – preskaler 4

001 – preskaler 6

010 – preskaler 8

011 – preskaler 10

100 – preskaler 12

101 – preskaler 16

110 – preskaler 20

111 – preskaler 32

3.Budowa i obsługa przetwornika DAC modułu C240 EVM

Moduł C240 EVM został wyposażony w czterokanałowy 12 bitowy przetwornik analogowo

cyfrowy, połączony z procesorem sygnałowym za pomocą programowalnych układów GAL.

Otrzymano w ten sposób mapowanie kanałów przetwornika DAC w przestrzeni adresowej I/O

procesora. Wpisując wartości, które mają być przetworzone na sygnały analogowe (napięciowe) pod

odpowiednie adresy pamięci I/O a następnie rozkaz wymuszający przetwarzanie również pod

odpowiedni adres pamięci uzyskujemy przetworzenie cyfrowo-analogowe.

Adresy w przestrzeni I/O:

0000h – adres pod który wpisujemy wartość która ma zostać przetworzona na sygnał analogowy

w przetworniku DAC0.

0001h – adres pod który wpisujemy wartość która ma zostać przetworzona na sygnał analogowy

w przetworniku DAC1.

0002h – adres pod który wpisujemy wartość która ma zostać przetworzona na sygnał analogowy

w przetworniku DAC2.

0003h – adres pod który wpisujemy wartość która ma zostać przetworzona na sygnał analogowy

w przetworniku DAC3.

0004h – jeśli pod ten adres wpiszemy jakąkolwiek wartość rozpocznie się proces konwersji

wartości cyfrowych na wartości analogowe

Uwaga! Przy pracy z przetwornikami ADC i DAC należy pamiętać o długości słowa

przetwornika. Przetwornik ADC procesorów seri x24x są 10 bitowe, przetwornik DAC modułu

C240EVM jest 12 bitowy.

Strona 6 z 7 Opracował mgr inż. Jacek Lis (c) ZNE 2004

Literatura dodatkowa:

1. TMS320F/C240 DSP Controllers Peripheral Library SPRU161C.PDF – rozdział 7

2. TMS320C240 DSP Controlers Evaluation Module Technical Reference SPRU248B –

rozdział 5.3 (w spisie treści rozdział przez pomyłkę oznaczono jako 5.5)

Strona 7 z 7 Opracował mgr inż. Jacek Lis (c) ZNE 2004

Wyszukiwarka

Podobne podstrony:

LaboratoriumPodstawAutomatyki D Nieznany

materialy do zajec laboratoryjn Nieznany

03 Zastosowanie technik laborat Nieznany

LaboratoriumTeoriiSterowaniaITe Nieznany

1 16 lutego 2011 Laboratorium Nieznany

LaboratoriumPodstawAutomatyki D Nieznany

laboratorium artykul 2010 01 28 Nieznany

5 2 3a CCNA1 Laboratorium pl id Nieznany (2)

Laboratorium metod numerycznych Nieznany

LABORATORIUM 1 id 261484 Nieznany

Laboratorium Podstaw Fizyki id Nieznany

Laboratorium nr 5 wskaYniki Nieznany

instrukcja laboratoryjna id 216 Nieznany

Laboratorium wiczenie6 id 26186 Nieznany

Laboratorium z TM spr1 id 26189 Nieznany

Laboratorium INFORMATYKA ET SEM Nieznany

laboratorium maszyny synchronic Nieznany

więcej podobnych podstron