DATA

DATA

PRODUCENT

PRODUCENT

TYP

TYP

WYGLĄD

WYGLĄD

ZEWNĘTRZNY

ZEWNĘTRZNY

PARAMETRY

PARAMETRY

µP

µP

UWAGI

UWAGI

I GENERACJA

Mikroprocesory 4 i 8 bitowe wykonane w technologii PMOS

15 XI

1971

INTEL

4004

F takt. 108 kHz

Dł. słowa 4

bity

Pamięć adresowalna

640 B

L. rozkazów 46

L. tranzyst. 2250-2300

R 10

µm

Zasilanie +5 V,-9 V

R

- rozmiar charakterysty-

czny, skala projektowania

(stopień scalenia układu)

L. tranzyst. - liczba tranzy-

storów

Pierwszy procesor po-

wstał

na

zamówienie

japońskiej

firmy

ETI.

Przeznaczony do kalku-

latorów zapoczątkował

technologiczną

linię

układów scalonych.

Cena 200 $.

GENERACJE MIKROPROCESORÓW

1972

INTEL

8008

F takt. 200 kHz

Dł. słowa 8

bitów

Pamięć adresowalna 16 KB

L. rozkazów

45 L. tranzyst. 2250-

2300 R

10 µm

Zasilanie +5 V,-9 V

Dane i adresy przesy-

łane jedną dwukieru-

nkową szyną, co wpły-

wało na zmniejszenie

szybkości pracy.

II GENERACJA

Technologia NMOS

1974

INTEL

8080

F takt. 0,5-2

MHz

Dł. słowa 8

bitów

Pamięć adresowalna 64 KB

L. rozkazów

78 L. tranzyst.

6000

R 6

µm

Zasilanie +12 V,+5 V,-5 V

Stos usunięto z mikro-

procesora i umieszczono

go w pamięci RAM.

GENERACJE MIKROPROCESORÓW

1974

MOTOROLA

6800

F takt. 1-2

MHz Dł. słowa

8 bitów

Pamięć adresowalna 64 KB

L. rozkazów

78 L. tranzyst.

4000

R 6

µm

Zasilanie 5

V

Pierwszy mikroprocesor

zasilanym jednym na-

pięciem +5V. Realizuje te

same zadania co Intel

8008, ale ok. 10 razy

szybciej.

Cena 179 $.

1974

MOS

TECHNOLOGIES

6502

F takt. 1

MHz Dł. słowa

8 bitów

Pamięć adresowalna 64 KB

L. rozkazów 52

L. tranzyst.

9000

R 6

µm

Zasilanie 5

V

Rozwinięcie wersji 6800.

Cena 25 $.

1976

ZILOG

Z80

F takt. 2,5-4

MHz Dł. słowa 8

bitów

Pamięć adresowalna 64 KB

L. rozkazów 176

L. tranzyst.

8500

R 6

µm

Zasilanie 5

V

MIKROKONTROLER

Układzie scalonym,

zawie-rającym w jednej

strukturze: jednostkę

centralną, pamięć,

generator sygnału

zegarowe-go oraz układy

wejścia – wyjścia.

Najpopularniejszy mi-

kroprocesor 8 bitowy,

zawierał wszystkie roz-

kazy 8080.Cena 25 $.

GENERACJE MIKROPROCESORÓW

I

kwartał

1976

(III)

INTEL

8085

F takt. 5

MHz Dł. słowa 8

bitów

Pamięć adresowalna 1 MB

L. rozkazów 75

L. tranzyst.

6500

R 3

µm

Zasilanie 5

V

Wzorowany na 8080.

Korzysta

z

jednego

poziomu napięcia co

jest jego główną zaletą.

1976

INTEL

8048

F takt. 6

MHz Dł. słowa

8 bitów

Pamięć adresowalna 1 MB

Pamięć RAM 64 B

Pamięć ROM (1-2 KB)

L. rozkazów

96

L. tranzyst. 19000

R 3

µm

MIKROKONTROLER

Pierwszy

INTEL-owski

mikroprocesor

jedno-

układowy.

Stosowany do obsługi

klawiatury komputero-

wej.

1976

INTEL

8051

F takt. 8-30

MHz Dł. słowa 8

bitów

Pamięć RAM 128

B

Pamięć ROM 4 KB

L. rozkazów

111

L. tranzyst. 50000

R 3

µm

MIKROKONTROLER

Architektura CISC.

Wyposażony w rozkazy

mnożenia i dzielenia.

Bardzo popularny,

również aktualnie

(różnorodne rodziny)

GENERACJE MIKROPROCESORÓW

III GENERACJA

16 bitowa długość słowa

1978

INTEL

8086

F takt. 5-14

MHz

Dł. słowa

16 bitów

Pamięć adresowalna 1 MB

L. tranzyst.

29000

R

3 µm

L. rozkazów 137

Pierwszy z serii x86.

Wyposażone

w

listę

rozkazów 8080, co dało

możliwość przenoszenia

oprogramowania z 8 bi-

towego na 16 bitowy

procesor. Procesory tej

serii jest często mon-

towane w komputerach

IBM klasy XT.

Cena 360 $.

1978

MOTOROLA

68000

F takt. 8

MHz Dł. słowa

16 bitów L. tranzyst.

68000

Pamięć adresowalna 64 MB

L. rozkazów 61

R 4

µm

Znajduje głównie wyko-

rzystanie do urządzeń

gospodarstwa

domowego.

GENERACJE MIKROPROCESORÓW

1978

INTEL

8087

COPROCESOR

F takt. 10

MHz Dł. słowa

16 bitów

Pamięć adresowalna 1 MB

L. rozkazów 137

L. tranzyst. 45 000

R 3

µm

MIKROKONTROLER

Współpracujący z pro-

cesorem

8086,

jego

zastosowanie przyśpie-

szyło trzykrotnie wyko-

nywanie operacji aryt-

metycznych.

1979

INTEL

8088

F takt. 4,7-8

MHz Dł. słowa

16 bitów

Pamięć adresowalna 1 MB

L. rozkazów 137

L. tranzyst. 29000

R 3

µm

Uproszczony 8086.

Stosowany w 8 bito-

wych urządzeniach pe-

ryferyjnych – przyczynił

się do sukcesu kompu-

terów IBM PC.

GENERACJE MIKROPROCESORÓW

1982

INTEL

80186

( zwany też

APX186)

F takt. 6

MHz Dł. słowa

16 bitów

Pamięć adresowalna 1 MB

L. rozkazów 137

L. tranzyst. 100.000

R 1.5 µm

Posiadał zewnętrzną i

wewnętrzną, 16 bitową

szynę danych, kanały

DMA i sterowniki prze-

rwań.

1982

INTEL

80286

F takt. 20

MHz

Dł. słowa 16

bitów

Pamięć wirtualnej 16 B

Pamięć adresowalna 16 MB

L. rozkazów

96

L. tranzyst. 134000

R

1,5 µm

Wykorzystywany w ko-

mputerach typu:

PC (AT).

Jest 3-6 razy szybszy od

8080.

Cena 360 $.

GENERACJE MIKROPROCESORÓW

IV GENERACJA

Pojawienie się 32 bitowej długości słowa

Rozmiar charakterystyczny 1,0µm

1985

[16MHZ]

1987

[20MHz]

1988

[25MHz]

1989

[33MHz]

INTEL

386 DX

F takt. 16-40

MHz

Dł. słowa

32 bitów

Pamięć

cache L2:128 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów 137

L. tranzyst. 275000

R 1 µm

Gniazdo Socket

3

Zasilanie 5

V

Zawiera nowatorski ko-

procesor

matematy-

czny.

Jako

pierwszy

wykorzystuje płyty głó-

wne z pamięcią cache

L2 o wielkości 128 kB i

czasem dostępu 20 ns.

Cena 299 $.

GENERACJE MIKROPROCESORÓW

1989

[25MHz]

1990

[33MHz]

1991

[50MHz]

INTEL

486 DX

F takt. 25-50

MHz Dł. słowa

32 bity Pamięć cache

L1: 8 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów 137

L. tranzyst. 1,2 mln

R 0,8 - 1 µm

Gniazdo Socket

5

Zasilanie 5

V

Zastosowano w nim te-

chnologię przetwarza-

nia potokowego, we-

wnętrzny

koprocesor

numeryczny. Obsługuje

programy inżynierskie

typu CAD, nowe sy-

stemy operacyjne.

1988

[16MHz]

1989

[20MHz]

1992

[25,33

MHz]

INTEL

386 SX

F takt. 16-33

MHz Dł. słowa

32 bitów

Pamięć adresowalna 16 MB

Pamięć wirtualna 256 GB

L. rozkazów 137

L. tranzyst.

275000

R 1,0

µm

1,5

µm

Zasilanie 5

V

Wyposażony w 16 bito-

wą szyną danych. Wię-

kszość płyt głównych

jest bez cache, dopiero

później

pojawiły

się

płyty z 16 kB cachem.

GENERACJE MIKROPROCESORÓW

1990

[20MHz]

1991

[25MHz]

INTEL

386 SL

F takt. 20-25

MHz Dł. słowa

32 bity Pamięć cache

L1: 8 kB L. tranzyst.

355000 R

1 µm

L. rozkazów 137

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

Zasilanie 5 V

Energooszczędny

ro-

dzaj 386 SX (z funkcją

zarządzania

energią),

przeznaczony dla ko-

mputerów

przenoś-

nych. Ma funkcję prze-

jścia w tryb uśpienia

(posiada

zmniejszony

pobór energii w okre-

sach bezczynności, wy-

dziela mniejsza ilość

wydzielanego ciepła).

1991

[16,20,

25 MHz]

1992

[33MHz]

INTEL

486 SX

F takt. 16-33

MHz Dł. słowa

32 bity Pamięć cache

L1: 8 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów 137

L. tranzyst. 900000-0,8 µm

R 1185000-1 µm

Gniazdo Socket

5

Zasilanie 5 V

Procesor 80486 DX bez

koprocesora.

GENERACJE MIKROPROCESORÓW

I

kwartał

1992

[50MHz]

III

kwartał

1992

[66MHz]

INTEL

486 DX2

F takt. 50-80

MHz Dł. słowa

32 bity Pamięć cache

L1: 8 kB

L2: 256

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów 137

L. tranzyst. 1,2 mln

R 0,8

µm

Gniazdo Socket

6

Zasilanie 5

V

RISC

(Reducet Instruction Set

Computer ) – komputer o

zredukowanej liście in-

strukcji. Cechy :

-oddzielne szyny danych

i programu,

-wykorzystanie przetwa-

rzania potokowego,

-zbiór

realizowanych

instrukcji jest ograni-

czony i spełnia warunki

ortogonalności

(symetrii).

1992

INTEL

486SL

F takt. 20-33

MHz Dł. słowa

32 bity Pamięć cache

L1: 8 kB

L2: 256

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów 137

L. tranzyst. 1,4 mln

R 0,8

µm

Zasilanie 5

V

Posiada funkcja przej-

ścia w tryb uśpienia.

GENERACJE MIKROPROCESORÓW

1994

INTEL

486DX4

(P24C)

F takt. 75-100 MHz

Dł. słowa 32

bity Pamięć cache L2:

256 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64

TB

L. rozkazów

137

L. tranzyst. 1,6

mln R

0,6 µm

Gniazdo Socket 6

Zasilanie 3,3

V

RISC

Częstotliwość zegara jest

mnożona cztery razy.

Zwiększono częstotliwości

zegara, (mniejsze napię-

cie mniej ciepła).

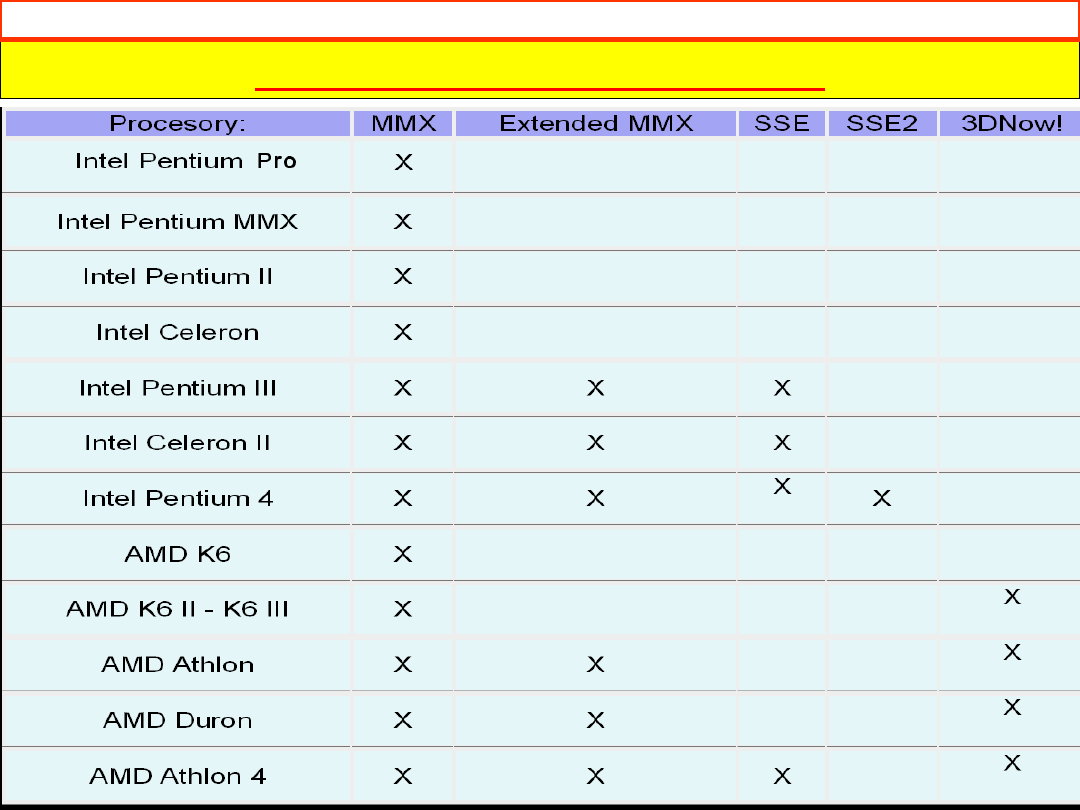

GENERACJE MIKROPROCESORÓW

NOWE TYPY ROZKAZÓW

GENERACJE MIKROPROCESORÓW

MMX (ang. MultiMedia eXtension technology),

Extended MMX (MMX2)

3DNow!

MMX

Standard obsługi instrukcji wspomagających przetwarzanie danych multimedialnych,

opracowana przez firmę Intel. Umożliwia szybszą obsługę poleceń używanych w

programach komputerowych, związanych między innymi z obsługą dźwięku, obrazu

3D oraz klipów filmowych.

MMX2

Dodano 57 nowych instrukcji do znanego już wcześniej standardu MMX. Rozkazy

usprawniają dekodowanie MPEG i AC-3, a instrukcje Cache Control znacząco

przyśpieszają działanie wszystkich aplikacji.

3DNow!

Zestaw 21 instrukcji typu SIMD-FP (Single Instruction Multiple Data – Floating Point)

opracowany przez firmy AMD. Jednostka SIMD-FP wykorzystuje dwa połączone w pary

64-bitowe rejestry MMX w przeciwieństwie do SSE (gdzie jest jeden 128 bitowej). Taka

technika AMD utrudniła automatyczna optymalizacje kodu programów, gdyż

konieczny był podział danych na dwa bloki. Dlatego właśnie programiści początkowo

niezbyt chętnie przystępowali do optymalizacji swych programów pod 3DNow!.

Dopiero włączenie obsługi 3DNow! do bibliotek Microsoft DirectX zmieniło radykalnie

sytuacje.

GENERACJE MIKROPROCESORÓW

SSE

(Streaming SIMD Extension, wcześniej

nazywane KNI (Katmai New Instructions))

SSE2 (Streaming SIMD Extension II)

SSE

Dzięki nim wzrosły możliwości obliczeniowe procesora.

Jednostka SSE to osiem dodatkowych,

- 128 bitowych rejestrów, moduł arytmetyczny realizujący do czterech operacji

zmiennoprzecinkowych

w jednym cyklu zegara.

Zestaw nowych rozkazów usprawnił:

-przetwarzanie grafiki trójwymiarowej (50 instrukcji);

-odtwarzanie plików wideo, audio i wyświetlania grafiki 2D (12 instrukcji MMX);

-przepływy danych pomiędzy CPU i pamięcią (8 instrukcji

Cache Control).

Zmiennoprzecinkowe instrukcje SIMD-FP (Single Instruction Multiple Data - Floating

Point), przyspieszył proces obliczeniowy (nawet cztery razy) i umożliwiły

tworzenie bardziej realistycznej grafiki 3D.

SSE2

Zestaw instrukcji opracowany przez firmę Intel. Wykorzystano jednostki

wykonawcze stało i zmiennoprzecinkowe. SSE2 zawiera 144 nowe instrukcje

wprowadzonych w Pentium4

GENERACJE MIKROPROCESORÓW

V GENERACJA

Długość słowa 32 (64 MD) bity.

1993

INTEL

PENTIUM

( P54 C )

F takt. 60-66

MHz

Dł. słowa rej. -

32 bity

MD – 64

bity

Pamięć cache L1: 16

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L.rozkazów

kilkaset

L. tranzyst. 3,1 mln

R (Bi-CMOS) 0,8 µm

Gniazdo Socket

7

Zasilanie 5

V

RISC

Brak możliwości zas-

trzeżenia znaku handlo-

wego zmusił produce-

nta do odstąpienia od

dotychczasowej nume-

racji procesora, dlatego

też

nową

jednostkę

określono

jako

Pe-

ntium

, choć w nie-

których kręgach spo-

łecznych procesor ten

nieoficjalnie określano

również jako

Intel 586

.

Układ przegrzewał się.

Miał niską wydajność.

Cena 900 $.

GENERACJE MIKROPROCESORÓW

IV

kwartał

1994

INTEL

PENTIUM

F takt. 75

MHz Dł. słowa

32 bity Pamięć cache

L1: 16 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. tranzyst. 3,2 mln

R 0,6

µm Gniazdo

Socket 7

Zasilanie 3,3

V

RISC

Pentium

w

okresie

swojego rozwoju do-

czekał się kilku wersji o

różnych szybkościach i

możliwościach.

I

kwartał

1994

INTEL

PENTIUM

F takt. 90-100

MHz Dł. słowa

32 bity Pamięć cache

L1: 16 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. tranzyst. 3,2 mln

R 0,6

µm

Gniazdo Socket

7

Zasilanie 3,3

V

RISC

Po raz kolejny zwię-

kszono

częstotliwość

taktowania procesora.

GENERACJE MIKROPROCESORÓW

I

kwartał

1994

NEXGEN

NX586

F takt. 70-111

MHz Dł. słowa

32 bity Pamięć

L1: 32 kB

L2: 256

kB

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

L. tranzyst. 3,5 mln

R 0,5

µm

Zasilanie 4

V

Pierwszy konkurent

Pentium.

I

kwartał

1995

INTEL

PENTIUM

F takt. 120

MHz Dł. słowa

32 bity Pamięć cache

L1: 16 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. tranzyst. 3,2 mln

R 0,6

µm

Gniazdo Socket

7

Zasilanie 3,3

V

RISC

To układ superskalarny,

zintegrowana

pamięć

podręczna drugiego po-

ziomu.

GENERACJE MIKROPROCESORÓW

II

kwartał

1995

INTEL

PENTIUM

F takt. 133

MHz Dł. słowa

32 bity Pamięć cache

L1: 16 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. tranzyst. 3,3

mln R

0,35 µm

Gniazdo Socket

7

Zasilanie 3,3 V

RISC

Przeznaczony do kom-

puterów stacjonarnych i

serwerów.

IV

kwartał

1995

NEXGEN

NX586FP

F takt. 70-111

MHz Dł. słowa

32 bity Pamięć cache

L1: 32 kB

L2: 256 kB

Pamięć adresowalna 4 GB

L. rozkazów kilkaset

L. tranzyst. 3,5

mln

R 0,5

µm

Posiada FPU

(Floating Point Units)

odpowiedzialne za szyb-

kie wykonywanie ope-

racji

zmiennoprzecin-

kowych oraz możliwość

pracy

w

konfiguracji

wieloprocesorowej.

GENERACJE MIKROPROCESORÓW

I

kwartał

1996

INTEL

PENTIUM

F takt. 150-166 MHz

Dł. słowa 32

bity Pamięć cache L1:

16 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. tranzyst. 3,3 mln

R 0,35

µm

Gniazdo Socket

7

Zasilanie 3,3

V

RISC

Przeznaczony do kom-

puterów stacjonarnych

i serwerów.

II

kwartał

1996

INTEL

PENTIUM

F takt. 160-200 MHz

Dł. słowa 32

bity Pamięć cache L1:

16 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. tranzyst. 3,3 mln

R 0,35

µm

Gniazdo Socket

7

Zasilanie 3,3

V

RISC

Przeznaczony do kom-

puterów stacjonarnych

i serwerów.

GENERACJE MIKROPROCESORÓW

1996

CYRIX

6x86 M1

F takt. 120-200 MHz

Dł. słowa 32

bity Pamięć cache L1:

16 kB

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

L. tranzyst. 3,3 mln

R 0,35

µm

Gniazdo Socket

7

Zasilanie 3,5

V

RISC

Procesory tej serii mają

kilka

zalet

wyróżnia-

jących je od Pentium

takich jak: przetwarzanie

superpotokowe, przewi-

dywanie wielogałęziowe,

wykonywanie

spekula-

tywne,

superskalarną

architekturę,

zmiana

nazw

rejestrów

oraz

mniejsze

ograniczenia

równoczesnego

wyko-

nywania instrukcji.

1997

CYRIX

6x86 MX

F takt. 233-300 MHz

Dł. słowa 32

bity

Pamięć cache L1:64

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

Gniazdo Socket

7

L. rozkazów

kilkaset

L. tranzyst. 6,5mln

R 0,35

µm

Zasilanie 2.8

V

RISC

Rozbudowana

wersja

serii M1, głównie o

obsługę

standardu

MMX,

siedmiostopniowy

potok

rozkazów

(pi-

peline).

GENERACJE MIKROPROCESORÓW

VI GENERACJA

Wprowadzenie instrukcji multimedialnych w tym instrukcji MMX

Intel wprowadza PENTIUM PRO,MMX i PENTIUM II a AMD K6

IV

kwartał

1995

INTEL

PENTIUM PRO

F takt. 150-200 MHz

Dł. słowa 32 (64) bity

Pamięć cache L1: 16 kB

L2:256

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. Rozkazów kilkaset

L. tranzyst. 5,5 mln

R (CMOS) 0,35-0,6 µm

Gniazdo Socket

8

RISC

Zawiera w jednej obu-

dowie dwie struktury sca-

lone: pamięć podręczną,

obejmującą ok. 15,5 mln i

sam procesor, obejmujący

5,5 mln tranzyst.

GENERACJE MIKROPROCESORÓW

I

kwartał

1997

INTEL

PENTIUM MMX

(P55C )

F takt. 166-200 MHz

Dł. słowa 32

bity Pamięć cache L1:

32 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L.rozkazów

kilkaset

(w tym 57 nowych

MMX i SIMD)

L. tranzyst. 4,5 mln

R 0,35

µm

Gniazdo Socket

7

Zasilanie 2,8/3,4 V

RISC

Opracowane z myślą o

multimedialnych prog-

ramach.

II

kwartał

1997

INTEL

PENTIUM MMX

F takt. 233

MHz Dł. słowa

32 bity Pamięć cache

L1: 32 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. tranzyst. 4,5 mln

R 0,35

µm

Gniazdo Socket

7

Zasilanie 2,8/3,4 V

RISC

Wzbogacono go dodat-

kowo

o

zestaw

57

instrukcji MMX i SIMD.

GENERACJE MIKROPROCESORÓW

III

kwartał

1997

INTEL

PENTIUM PRO

F takt. 200

MHz Dł. słowa

32 bity Pamięć cache

L1: 16 kB

L2: 512

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów

kilkaset

L. tranzyst. 5,5 mln

R 0,35

µm

Gniazdo Socket

8

RISC

W odróżnieniu od po-

przednich wersji zwię-

kszono w nim rozmiar

pamięci cache.

II

kwartał

1997

AMD

K6

F takt. 166-200 MHz

Dł. słowa 32

bity Pamięć cache L1:

64 kB

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

L. tranzyst. 8,8 mln

R 0,25

µm

Gniazdo Socket

7

Zasilanie 2,2/3,3 V

RISC

Pamięć podręczna pier-

wszego poziomu po 32

kB dla danych i pro-

gramu. Obniżono na-

pięcia, zwiększono czę-

stotliwość.

Odpowiadające

wy-

dajnością

procesorom

Pentium Pro tańszych o

25 %.

GENERACJE MIKROPROCESORÓW

II

kwartał

1997

INTEL

PENTIUM II

(Klamath ,

Deschutes)

F takt. 233-300 MHz

Dł. słowa 32

bity Pamięć cache L1:

32 kB

L2:512

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozk kilkaset

(pełny zestaw instrukcji MMX)

L. tranzyst. 7,5 mln

R 0,18 µm

Gniazdo Slot 1

(zamiast Socket)

Zasilanie 2

V

RISC

Pamięć

cache

zinte-

growana w strukturze

procesora – poprawa

wydajności.

Jest połączeniem zalet

Pentium P55C (MMX) i

Pentium Pro

.

I

kwartał

1998

INTEL

PENTIUM II

F takt. 333

MHz Dł. słowa

32 bity Pamięć cache

L1: 32 kB

L2:512

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozk kilkaset

(pełny zestaw instrukcji MMX)

L. tranzyst. 7,5 mln

R 0,18 µm

Gniazdo Slot

1

Zasilanie 2

V

RISC

Po raz kolejny mamy do

czynienia

ze

zwięk-

szeniem częstotliwości

taktowania

względem

pierwowzoru.

GENERACJE MIKROPROCESORÓW

I

kwartał

1998

INTEL

PENTIUM II

XEON

F takt. 450

MHz Dł. słowa

32 bity Pamięć cache

L1: 32 kB

L2:512

kB

Pamięć adresowalna 4 GB

L. rozk kilkaset

L. tranzyst. 7,5 mln

R 0,18

µm

Gniazdo Slot2

RISC

Magistrala

systemowa

obsługuje

niezależne

transakcje – zwiększył to

przepustowość systemu

i zapewnia obsługę do 8

procesorów.

II

kwartał

1998

[266MHz]

II

kwartał

1998

[300MHz]

III

kwartał

1998

[333MHz]

INTEL

CELERON (P6C

Covington)

F takt. 266-400 MHz

Dł. słowa 32

bity Pamięć L1:

32 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. tranzyst. 7,5 mln

R 0,18 µm

Gniazdo Slot

1

Zasilanie 2

V

RISC

Intel skonstruował rodzinę

procesorów Celeron, zwa-

nych:

”Pentium

II

dla

biednych.” aby zapobiec

wyparciu swoich produ-

któw z rynku tanich proce-

sorów,

zdominowanego

przez konkurujące firmy

AMD i IDT. Dla procesorów

Celeron zdefiniowano ta-

kże

nowy

typ

płyty

głównej, tzw. micro ATX

mającej

nieco

mniejsze

wymiary niż standardowe

płyty, ale kompatybilnej z

obudowami ATX.

GENERACJE MIKROPROCESORÓW

IV

kwartał

1998

(X)

AMD

K6-II 3DNOW

(Chomper )

F takt. 300-475 MHz

Dł. słowa 32

bity Pamięć cache

L1:64 kB

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

L. tranzyst. 9,3 mln

R 0,25

µm

Gniazdo Socket

7

Zasilanie 2,2/3,3 V

RISC

Unowocześniona

wer-

sja procesora K6.

3Dnow - 21 dodatko-

wych

instrukcji

zmiennoprzecinkowych

SIMD-FP.

GENERACJE MIKROPROCESORÓW

II

kwartał

1999

(V)

AMD

K6-III

(Sharptooth)

F takt. 400-450

MHz Dł. słowa

32 bity Pamięć cache

L1:64 kB

L2: 256

kB

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

L. tranzyst. 21,3

mln R

0,25 µm

Gniazdo Socket

7

Zasilanie 2,2/3,3 V

RISC

Nowocześniejsza wersja

K6-II. Obsługuje pamięć

cache

trzeciego

poziomu o ile znajduje

się

ona

na

płycie

głównej.

VII GENERACJA

Wprowadzenie nowych rozkazów służących przetwarzaniu grafiki trójwymiarowej.

Wprowadzenie instrukcji MMX2 usprawniających kodowanie i dekodowanie

multimedii. Pojawia się PENTIUM III i AMD K7

III

kwartał

1999

[600MHz]

II

kwartał

1999

[550MHz]

II

kwartał

1999

[450,

500MHz]

INTEL

PENTIUM III

(Katmai)

F takt. 450-600 MHz

Dł. słowa (MD 64) 32 bity

Pamięć cache L1:32 kB

L2: 256

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów

kilkaset

(70 nowych instrukcji: 50 instrukcji

SIMD-FP, 12 instrukcji MMX i 8

instrukcji Cache Control)

L. tranzyst. 9,5 mln

R 0,25

µm

Gniazdo Slot

1

Zasilanie 1,6

V

RISC

Zmiennoprzecinkowe

instrukcje

SIMD-FP,

przyspieszają cały pro-

ces obliczeniowy (nawet

do czterech razy).

GENERACJE MIKROPROCESORÓW

I

kwartał

1999

INTEL

PENTIUM III

XEON

(Tanner)

F takt. 500-550 MHz

Dł. słowa 32

bity Pamięć cache L1:

32 kB

L2:512

kB

Pamięć adresowalna 4 GB

L. tranzyst. 9,5 mln

R 0,25

µm

Gniazdo Slot

1

RISC

Zwiększono

rozmiar

pamięci cache drugiego

poziomu.

III

kwartał

1999

MOTOROLA

G4 PowerPC

7400

F takt. 500-700 MHz

Dł. słowa 32

bity Pamięć cache L1:

32 kB

Pamięć adresowalna 4 GB

L. rozkazów kilkaset

(

162 nowe rozkazy dedykowane

do przetwarznia

strumieniowego

)

L. tranzyst. 6,5 mln

R

0,18 µm

RISC

Wyposażony w wyspe-

cjalizowany wektorowy

moduł AltiVec odpo-

wiedzialny

za

rów-

noległe

przetwarzanie

nieskończenie

długich

strumieni

danych

za

pomocą

pojedynczych

instrukcji.

GENERACJE MIKROPROCESORÓW

III

kwartał

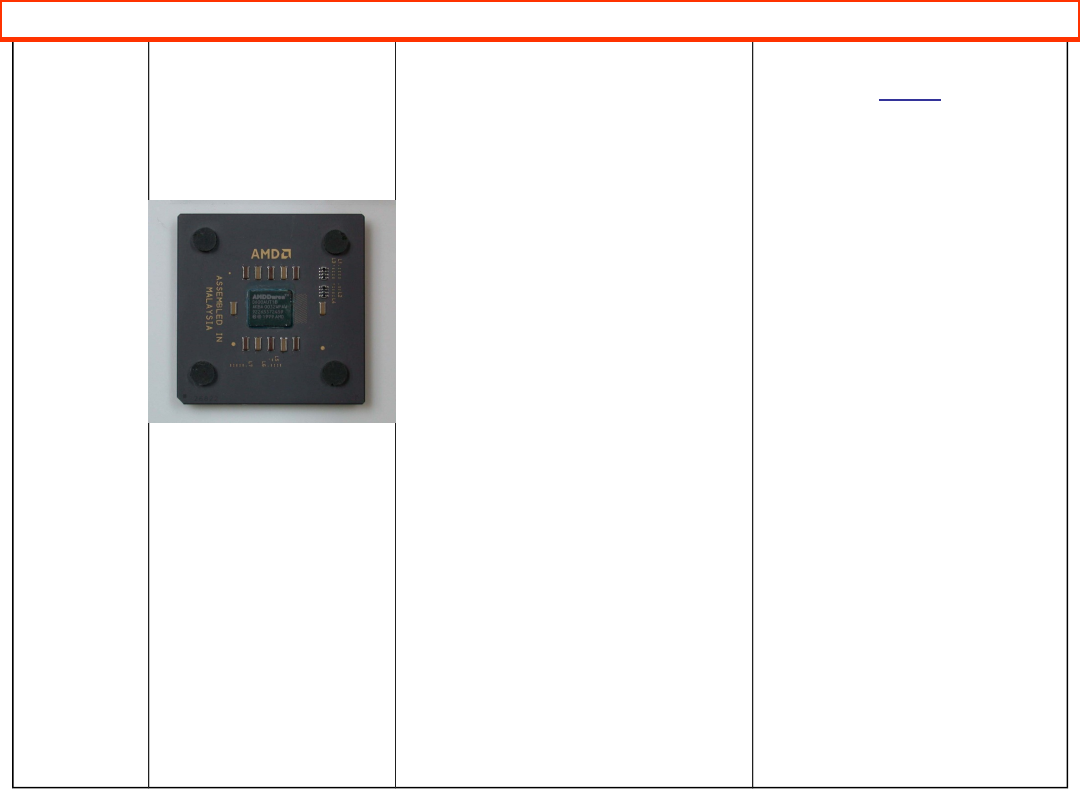

1999

AMD

K7 ATHLON

F takt. 500-1000 MHz

Dł. słowa 32

bity Pamięć L1:

128 kB

L2: 512

kB

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

L. tranzyst. 22 mln

R 0,25

µm Gniazdo

Slot A

Zasilanie 1,8

V

RISC

Alternatywa dla Intel-

owskiego

procesora

Pentium III. Procesor

wyposażono

w

trzy

pracujące

równolegle

podjednostki

wykona-

wcze

FPU

(Floating

Point

Units)

odpo-

wiedzialne za szybkie

wykonywanie

operacji

zmiennoprzecinkowych

oraz możliwość pracy w

konfiguracji wieloproce-

sorowej.

GENERACJE MIKROPROCESORÓW

IV

kwartał

1999

INTEL

PENTIUM III

(Katmai)

F takt. 500-733 MHz

Dł. słowa 32

bity Pamięć cache L1:32 kB

L2: 512

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów

kilkaset

L. tranzyst. 28

mln R

0,18 µm

Gniazdo Socket

370

RISC

Przystosowany do pracy

w konfiguracji wielo-

procesorowej,

zawiera

numer

seryjny

umo-

żliwiający jego identy-

fikację w sieci.

I

kwartał

2000

[850,

866,

1000

MHz]

II

kwartał

2000

[933 MHz]

INTEL

PENTIUM III

(Coppermine)

F takt. 850-1000 MHz

Dł. słowa 32

bity Pamięć cache L1: 32 kB

L2: 512

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów

kilaset

L. tranzyst. 44

mln R

0,18 µm

Gniazdo Socket

370

RISC

Pamięć cache L2 u-

mieszczona została na

wspólnej z procesorem

strukturze krzemowej.

GENERACJE MIKROPROCESORÓW

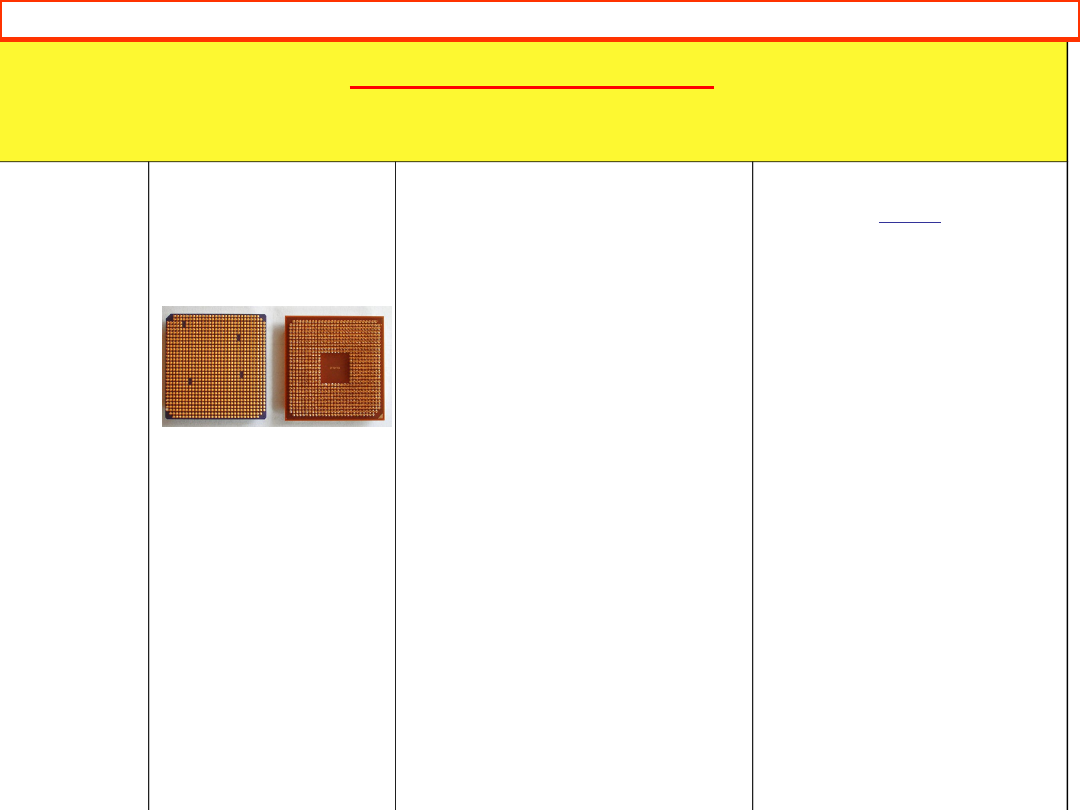

II

kwartał

2000

AMD

ATHLON

(Thunderbird)

F takt. 650-1400 MHz

Dł. słowa 32

bity Pamięć cache L1:

128 kB

L2: 512

kB

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

(24 nowe rozkazy do kodowani

i dekodowania MP3,

dźwięku przestrzenne-

go,MPEG2)

L. tranzyst. 37

mln R

0,18 µm

Gniazdo Slot A/Socket A

Zasilania 1,75

V

RISC

Zastosowano

organi-

zację pamięci o tzw.

wykluczającej się archi-

tekturze dostępu

(exclusive L2 cache

memory) układ pobiera

informacje z RAM-u tak,

że pamięć L2 zawiera

całkowicie inne dane niż

cache L1, przez co sy-

stem zachowuje się tak

jakby był wyposażony w

pamięć L1 o suma-

rycznej pojemności L1 +

L2 (384 kB) średni czas

dostępu -1,5 cyklu ze-

gara.

Szybszy od Athlona o

tym samym zegarze o

27,5%.

GENERACJE MIKROPROCESORÓW

II

kwartał

2000

AMD

DURON

(Spitfire)

F takt. 600-1000 MHz

Dł. słowa 32

bity Pamięć cache L1:

64 kB

L2: 256

kB

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

L. tranzyst. 37 mln

R 0,18

µm

Gniazdo Socket

A

Zasilanie 1,6

V

RISC

Komunikuje się z pa-

mięcią przez magistralę

taktowaną

zegarem

100MHz, pracującą w

trybie DDR, co dało w

efekcie

częstotliwość

FSB

200MHz.

Zasto-

sowanie exclusive cache

- połączenie cache L1 i

L2

(wspólna

pamięć

podręczną o sumary-

cznej pojemności).

Sprawdza się w zasto-

sowaniach

biurowych

oraz obciążających pro-

cesor grach 3D.

Główna

zaleta

jest

stosunkowa niska cena.

GENERACJE MIKROPROCESORÓW

I

kwartał

2000

[566,

600

MHz]

II

kwartał

2000

[633,66,

700

MHz]

IV

kwartał

2000

[733,

766

MHz]

INTEL

CELERON II

F takt. 533-766 MHz

Dł. słowa 32

bity Pamięć cache L1:

32 kB

L2: 128

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozk kilkaset

(pełny zestaw instrukcji MMX)

R 0,18

µm

Gniazdo Socket

370

Zasilanie 2

V

RISC

Unowocześniona wersja

poprzedniej jednostki

Celeron’a.

GENERACJE MIKROPROCESORÓW

I

kwartał

2001

[800

MHz]

II

kwartał

2001

[850

MHz]

II

kwartał

2001

[900

MHz]

III

kwartał

2001

[950

MHz,

1.1GHz]

INTEL

CELERON II

F takt. 800 MHz-1,1 GHz

Dł. słowa 32

bity Pamięć cache L1:

32 kB

L2: 128

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozk kilkaset

(pełny zestaw instrukcji MMX)

R 0,18

µm

Gniazdo Socket

370

Zasilanie 2

V

RISC

Zwiększono

częstotli-

wości

taktowania

w

stosunku do wcześnie-

jszej wersji.

GENERACJE MIKROPROCESORÓW

IV

kwartał

2001

[1.2

GHz]

I

kwartał

2002

[1.3

GHz]

II

kwartał

2002

[1.4

GHz]

INTEL

PENTIUM IV

(Willamette)

F takt. 1,4-1,5 GHz

Dł. słowa 32

bity Pamięć cache L1:

128 kB

L2: 256

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów

kilkaset

(nowe 144 rozkazy SSE2, zwiększa

możliwości procesora w zakresie

kompresji/dekompresji obrazu w czasie

rzeczywistym lub szyfrowania danych)

L. tranzyst. 42

mln R

0,18 µm

Gniazdo Socket

423

RISC

W

odróżnieniu

od

Pentium

III,

posiada

szereg innowacji tech-

nologicznych: m.in.

wy-

dłużenie potoków wy-

konawczych,

przy je-

dnoczesnym zmniejsze-

niu liczby tranzysto-rów.

Dzięki temu możliwe

jest zwiększenie częs-

totliwości zegara zacho-

wując, jednocześnie tę

samą

technologię

wytwarzania.

Inne prze-

łomowe

rozwiązania

konstrukcyjne to me-

chanizm

podwójnego

wspomagania jednostki

stałoprzecinkowej

(Double Pumped Integer

ALU) umożliwiający ta-

ktowanie procesora z

podwójną prędkością.

GENERACJE MIKROPROCESORÓW

III

kwartał

2001

[2GHz]

I

kwartał

2002

[2,2

GHz]

II

kwartał

2002

[2,4

GHz]

III

kwartał

2002

[2,5;

2,6GHz]

INTEL

PENTIUM IV

(Northwood)

F takt. 1,4-1,9 GHz

Dł. słowa 32

bity Pamięć cache L1:

12 kB

L2: 512

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów

kilkaset

L. tranzyst. 55

mln

R

0,13 µm

Gniazdo Socket

478

Zasilanie 1,5

V

RISC

Układ pomniejszono,

zwiększono wydajność

chłodzenia.

GENERACJE MIKROPROCESORÓW

2001

AMD

ATHLON XP+

(Palomino)

F takt. 1333-1733 MHz

Dł. słowa 32

bity Pamięć cache L1:

128 kB

L2: 256

kB

L. rozkazów

kilkaset

L. tranzyst. 38 mln

R 0,18

µm

Gniazdo Socket

A

Zasilania 1,75

V

RISC

Architektura

Quanti-

Speed, liczba operacji w

jednym cyklu zegara: 9,

potoki

stałoprzecinko-

we: 3, potoki zmienno-

przecinkowe: 3, dekode-

ry x86:3. Max. Przepu-

stowość magistrali: 2,1

GB/s, zaległe operacje

magistrali: 24 na proce-

sor, technologia zegara:

Source

Synchronous,

3DNow!™.

II

kwartał

2002

[2,26;

2,4 GHz]

III

kwartał

2002

[2,8GHz]

INTEL

PENTIUM IV

F takt. 2,26-2,8 GHz

Dł. słowa 32

bity Pamięć cache L1:

12 kB

L2: 512

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów

kilkaset

L. tranzyst. 55 mln

R 0,13

µm

Gniazdo Socket

478

RISC

Zwiększono

często-

tliwość taktowania w

stosunku

do

poprze-

dników.

GENERACJE MIKROPROCESORÓW

IV

kwartał

2002

INTEL

PENTIUM IV HT

F takt. 3,06

GHz Dł. słowa

32 bity Pamięć cache L1:

128 kB

L2: 512

kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów

kilkaset

L. tranzyst. 55 mln

R 0,13

µm

Gniazdo Socket

478

RISC

Wbudowana technologia

Hyper-Threading zape-

wnia korzyści umożli-

wiając wykonywanie ró-

wnolegle

dwóch

wą-

tków oprogramowania.

Nie

zmniejszenia

to

wydajności.

II

kwartał

2003

[3GHz]

II

kwartał

2003

[2,4;2,8

GHz]

II

kwartał

2003

[3,2GHz]

INTEL

PENTIUM IV HT

F takt. 2,4-3,2 GHz

Dł. słowa 32

bity Pamięć cache L1:

128 kB

L2:512 kB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów

kilkaset

L. tranzyst. 55 mln

R 0,13

µm

Gniazdo Socket

478

RISC

Zwiększono

częstotli-

wość taktowania w sto-

sunku do poprzedników.

GENERACJE MIKROPROCESORÓW

IV

kwartał

2003

do

chwili

obecnej

INTEL

PENTIUM IV HT

F takt. 3,2

GHz Dł. słowa

32 bity Pamięć cache L1:

128 kB

L2: 512

kB

L3:2

MB

Pamięć adresowalna 4 GB

Pamięć wirtualna 64 TB

L. rozkazów

kilkaset

L. tranzyst. 178 mln

R 0,13

µm

Gniazdo Socket

478

RISC

Zastosowano

techno-

logię hiperpotokowa,

aparat szybkiego wyko-

nywania rozkazów,

pod-

ręczna pamięć śledząca,

zaawansowana pamięć

podręczna przesyłania

,

udoskonalone, szybkie

wykonywanie rozkazów,

udoskonalony koproce-

sor i jednostka multi-

medialna

.

II

kwartał

2003

AMD

ATHLON XP+

(Barton)

F takt. 1466-2166 MHz

Dł. słowa 32

bity Pamięć cache

L1: 64 kB

L2: 512

kB

L. tranzyst. 55

mln R

0,13 µm Magistrala syst.

800 MHz

Gniazdo Socket A

L. rozkazów

kilkaset

Zasilanie 1,75

V

RISC

Wykorzystuje elementy

jądra Hammerów i zo-

stał wyposażony w wię-

kszą,

512-kilobajtową

pamięć cache.

GENERACJE MIKROPROCESORÓW

III

kwartał

2003

AMD

DURON

(Appalloosa)

F takt. 1333-1800 MHz

Dł. słowa 32

bity Pamięć cache L1:

64 kB

L2: 256

kB

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

R 0,13

µm

Gniazdo Socket

A

RISC

Szybkością zbliżone są

do Athlonów.

GENERACJE MIKROPROCESORÓW

VIII GENERACJA

64 bitowa długość słowa

II

kwartał

2003

2004

AMD

HAMMER

AMD

OPTERON

(SledgeHammer)

F takt. 2

GHz

Dł. słowa

64 bity

Pamięć cache

L1: 64 kB

(w różnych

wersjach L2: 1-2 MB)

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

L. tranzyst. 106 mln

R 0,13

µm

Zasilanie

1,75V

F takt. 1,4-2,4 GHz

Dł. słowa 64

bity Pamięć cache L1:

64 kB

(w różnych wersjach

L2: 256-512 kB)

L. tranzyst. 105,9 mln

Pamięć adresowalna 4 GB

L. rozkazów

kilkaset

R 0,13

µm

Zasilanie

1,6V

RISC

Oparty

na

rdzeniu

Thunderbird.

Wbudowany

również

sterownik pamięci RAM.

Oczywiście

jest

to

pamięć

DDR,

a

obsługiwane tryby to

PC1600,

PC2100

i

PC2700.

Obsługa trybu

wieloprocesorowego.

GENERACJE MIKROPROCESORÓW

VIII GENERACJA

64 bitowa długość słowa

2004

II półrocze

2004

AMD

ATHLON64

INTEL

PENTIUM 4F

(Prescott)

F takt. 2,2-3,2 GHz

Dł. słowa 64

bity Pamięć cache L1:

64 kB

(w różnych wersjach

L2: 512kB-1 MB)

L. tranzyst. 68,5 mln

L. rozkazów

kilkaset

R 0,13

µm

Zasilanie

1,5V

F takt. 3,2-3,6 GHz

Dł. słowa 64

bity Pamięć cache L1:

64 kB

L2: 1

MB

L. tranzyst. 125 mln

L. rozkazów

kilkaset

R 90 nm

Zasilanie

1,5V

Brak wbudowanego

sterownika pamięci.

Obsługa trybu

wieloprocesorowego.

GENERACJE MIKROPROCESORÓW

Tendencje rozwojowe

Zwiększenie długości słowa i adresu, zwiększenie częstotliwości taktowania

(szybkość)

Scalenie poszczególnych układów systemu mikroprocesorowego w jednym układzie

scalonym

Mikrokontrolery

•

Mikroprocesorowe systemy modułowe (maszyny cyfrowe, szybkie układy

sterujące)

•

Procesory sygnałowe

(

„mikroprocesory analogowe”

– z szybkim przetwornikiem

A/C i C/A)

•

Mikroprocesorowe układy specjalistyczne

(od układów kalkulatorowych do specjalizowanych układów, w tym do układów

dla celów militarnych)

•

Systemy multimedialne

Tendencje do miniaturyzacji

•

Dążenie do obniżania jednostkowego kosztu tranzystora.

•

Zmniejszanie rozmiarów bramki tranzystora.

GENERACJE MIKROPROCESORÓW

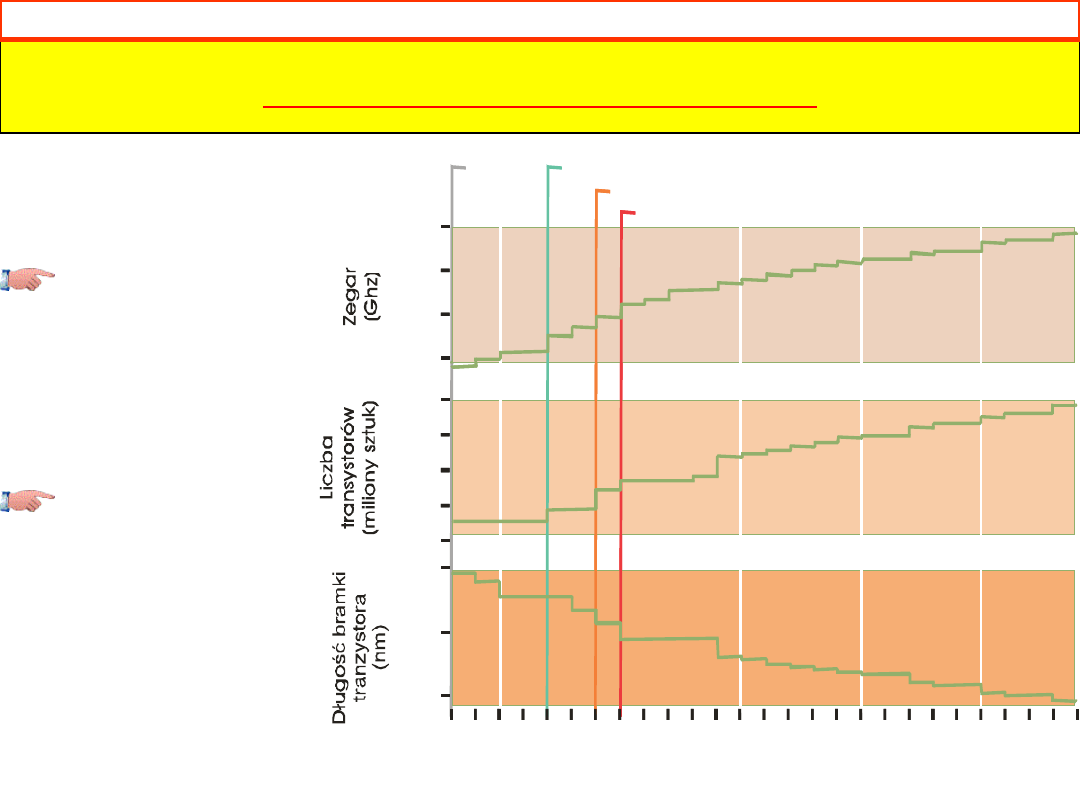

Intel po 2004

ROZMIARY

TRANZYSTORÓW

W ciągu ostatniego

dziesięciolecia

w

zakresie

mikro-

i

nanotechnologii

kilkakrotnie zmniejszono

długość

kanału

tranzysto-ra (co widać na

wykresach

według

analizy

proceso-rów

Pentium firmy Intel).

Niezwykły wzrost

szy-bkości

działania

i

liczby

tranzystorów

następuje

wraz

ze

zmniejszaniem

się

długości kanału tranzy-

stora. Przy prognozowa-

nym postępie technologii

półprzewodnikowej trend

ten utrzyma się jeszcze

przez długie lata

.

Prognozy na przyszłość

GENERACJE MIKROPROCESORÓW

Pentium

Pentium I

Pentium III

Pentium IV

Prognoza

1

10

100

0.1

10000

1000

100

10

1

100

10

1995

2000

2005

Rok

2010

2015

1000

Pentium III

Pentium IV

Prognoza

1

10

100

0.1

10000

1000

100

10

1

100

10

1995

2000

2005

2010

2015

1000

Intel po 2004

Kolejny procesor Pentium 4 (

Tejas

), 2005 rok, produkowany w technologii 90

nanometrów, z zegarem 5.6GHz i magistralą systemową 1066MHz. (Przewidywane

wersje: 6 GHz, 6.40 GHz, 6.80 GHz, 7.20 GHz, 7.60 GHz, 7 GHz, 8.40 GHz, 8.80GHz i

najmocniejsza wersja 9.20 GHz.)

Pod koniec roku 2005 na rynek ma trafić procesor taktowany zegarem 9.6 GHz, (o

nazwie

Nehalem)

z magistralą systemową 1200 MHz. Pierwszym, który przekroczy

barierę 10 GHz będzie 10.2 GHz Ne-halem.

Hermon

, procesor przeznaczony do szerokiego stosowania w telefonach

komórkowych. Produ-kowany w 0,13- mikrometrowej technologii układ zawiera jądro

XScale MSA. Masowa produkcja układu przewidziana jest na 2005 r.

W 2005 Intel przewiduje wprowadzenie do sprzedaży zupełnie nowego procesora

dla notebooków,

Merom

– o zupełnie nowej architekturze, początkowo będzie

produkowany w

technologii 0,09 mikrometra, a od roku 2006 – 0,065 mikrometra.

Planowane wprowadzenie w 2005 roku na rynek procesorów dwurdzeniowych, na

jądrze Prescott. Przy chłodzeniu tych procesorów niezbędne będzie chłodzenie

cieczą. Nie wiadomo, o ile procesory dwurdzeniowe mogą być szybsze od wersji

jednordzeniowych

.

Prognozy na przyszłość

GENERACJE MIKROPROCESORÓW

Intel po 2004

AMD po 2004

Zastosuje metodę

Smart Cut

w procesorach najbliższej generacji. Metoda ta

polega na bomba-rdowaniu utlenionej płytki jonami wodoru (protonami), tak aby

pokonały one warstwę dwutlenku krze-mu i zatrzymały się poniżej.

Pod koniec roku 2004 zadebiutują procesory

Oakville

z 754 nóżkami i rdzeniem

Athlona 64 z 512 KB pamięci cache. Mają one pracować z częstotliwościami 2 GHz i

wydzielać 35 W ciepła. W 2005 roku AMD wprowadzi procesor

Lancaster

. Ma mieć

754 nóżki i zegar 2GHz. Będzie miał 1 MB pamięci cache. Będzie wydzielać 35 W

energii cieplnej.

W tym samym okresie na rynku pojawią się kolejne

Semprony

dla notebooków,

które będą miały 128 bądź 256 KB pamięci cache i będą wydzielały 25 W energii

cieplnej.

Planowane wprowadzenie w 2005 roku na rynek procesorów dwurdzeniowych,

wraz z nimi nowe technologie produkcji i wirtualizacja układów

.

Układy AMD mają posiadać wspólne dla obu rdzeni:

- L2

- szynę HyperTransport.

Procesory te będą mogły przetwarzać dwa razy więcej danych w ciągu jednego

cyklu zegara, niż modele jednordzeniowe

.

Prognozy na przyszłość

GENERACJE MIKROPROCESORÓW

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

- Slide 37

- Slide 38

- Slide 39

- Slide 40

- Slide 41

- Slide 42

- Slide 43

- Slide 44

- Slide 45

- Slide 46

- Slide 47

Wyszukiwarka

Podobne podstrony:

Proces wałka do Wiecha, Zarządzanie i Inżynieria Produkcji Politechnika Lubleska, podstawy technolog

W4 Proces wytwórczy oprogramowania

WEWNĘTRZNE PROCESY RZEŹBIĄCE ZIEMIE

Proces tworzenia oprogramowania

Proces pielęgnowania Dokumentacja procesu

asm skrot prezentacji

19 Mikroinżynieria przestrzenna procesy technologiczne,

4 socjalizacja jako podstawowy proces spoeczny

modelowanie procesˇw transportowych

Proces wdrazania i monitoringu strategii rozwoju

Wykorzystanie modelu procesow w projektowaniu systemow informatycznych

wyklad 12nowy procesy elektrodowe i korozja

więcej podobnych podstron