1

AKADEMIA BYDGOSKA im. KAZIMIERZA WIELKIEGO

WYDZIAŁ MATEMATYKI TECHNIKI I NAUK PRZYRODNICZYCH

KATEDRA FIZYKI

Paweł Kwiatkowski

Budowa oraz zasada działania pamięci RAM

Praca licencjacka

napisana pod kierunkiem

dr Karola Grudzińskiego

Bydgoszcz 2005

2

Pragnę podziękować:

mojemu promotorowi dr. Karolowi Grudzińskiemu, za cenne uwagi, dyskusje i

pomoc na wszystkich etapach powstawania pracy.

2

3

Spis treści

1.Wstęp.............................................................................................................................4

2. Zasada działania pamięci...........................................………………….....................5

3 . Uproszczona budowa pamięci……………………………………………………...6

4. Pamięci dynamiczne……………………………………………………..…………11

4.1. Typ konwencjonalny (Page Mode)...............................................................11

4.2. FPM (Fast Page Mode).................................................................................12

4.3. EDO (Extended Data Out)……………………...……………...…………..14

4.4 BEDO (Burst EDO)………………………………………….….………….15

4.5 SDRAM.........................................................................................................16

5. Moduły pamięciowe...................................................................................................18

5.1 Moduły SIMM-30 (SIP)................................................................................18

5.2 Moduły SIMM PS/2.............................................................….....................19

5.3 Moduły DIMM..............................................................................................20

6. Odświeżanie................................................................................................................22

6.1

RAS Only............................................................................…......................23

6.2 CBR (CAS Before RAS)……………………………………….…………..23

6.3 Hidden...........................................................................................................24

7. Wykrywanie błędów i ich korekcja..........................................................................25

8. DDR SDRAM.............................................................................................................26

9. RDRAM......................................................................................................................28

10. VC-SDRAM.............................................................................................................30

11. HSRAM....................................................................................................................32

12. Najnowsze moduły pamięciowe oraz ich rozwój w przyszłości - podsumowanie

.........................................................................................................................................33

13. Literatura.................................................................................................................34

3

4

1. Wstęp

Pamięć PC jest jedną z podstawowych części komputerów PC, praktycznie

komputer bez pamięci operacyjnej nie mógł by poprawnie funkcjonować . Na początku

rozwoju komputerów PC jedynymi dostępnymi pamięciami były pamięci pracujące w

trybie PM (Page Mode) a później FPM (Fast Page Mode) . Wraz z rozwojem

architektury komputerów wzrosła także szybkość prezentowanych na rynku kości

pamięci. Obecnie na rynku dostępne są różne typy pamięci dostosowane do płyt

głównych jak i do procesora oraz chipsetu płyty głównej. Najbardziej

rozpowszechnionymi w ostatnich latach są RAM (Fast Page Mode RAM), EDO-RAM

(Extended Data Out RAM), SDRAM (Synchronous Dynamic Random Access

Memory), RDRAM (Rambus Direct RAM) czy wreszcie DDR SDRAM (Double Data

Rate SDRAM). Pomimo ciągłego przyśpieszania częstotliwości pracy modułów

pamięci okazują się one stale za wolne, powodem tego jest stały rozwój szybkości

procesorów za którym nie nadąża pamięć, która stanowi wąskie gardło dla całego

systemu. Mimo że na rynku dostępne są nawet pamięci operacyjne o szybkości

DDR600 i pojemności 2048MB (2GB) to i tak jest za mało dla współczesnych

komputerów. Teoretycznie cały czas moc obliczeniowa CPU zmniejszana jest przez

wydłużony czas dostępu do pamięci.

Pamięć operacyjna dzisiejszych komputerów to głównie DRAM (Dynamic

RAM). Wraz z rozwojem rynku komputerowego powstawały nowsze technologie i

usprawnienia : PM, FPM, EDO, BEDO, SDRAM, DDR, RDRAM, VC-SDRAM,

HSDRAM przyszłość to natomiast : XDR DRAM (eXtended Direct Rambus DRAM).

Pamięci PC to także pamięci innych typów występujące w komputerach PC.

Występują pamięci EPROM w których przechowywane są procedury BIOS-u, takiego

typu moduły wykorzystywane są do programowania jednorazowego i bez

odpowiedniego osprzętu nie możliwa była modyfikacja. Obecnie pamięć ta została

wyparta przez EEPROM, którą można w prosty sposób modyfikować sam użytkownik

PC. Pamięć tego typu można spotkać najczęściej na płytach głównych ale także w

urządzeniach peryferyjnych np. (kontrolery SCSI, modemy, karty sieciowe, dyski

twarde czy karty graficzne) oraz w procesorach. Charakterystyczne jest to że pamięć

EEPROM nie ulega zamazaniu po wyłączeniu zasilania.

4

5

2. Zasada działania pamięci RAM

Pamięć operacyjna komputera zwana pamięcią RAM służy do przechowywania

danych aktualnie przetwarzanych przez program oraz ciągów rozkazów, z których

składa się dany program. Pamięć RAM jest tak zwaną pamięcią ulotną co oznacza, że

po wyłączeniu komputera informacje w niej zawarte są tracone. Pamięć ta często jest

nazywana DRAM ze względu na zasadę działania: pojedyncze komórki pamięci

zawierają kondensatory, które naładowane do pewnego napięcia, przechowują jeden bit

danych. Kondensator jednak za szybko się rozładowuje i trzeba go systematycznie

odświeżać przez zaadresowanie i ponowne naładowanie kondensatora, proces ten nosi

nazwę odświeżania pamięci i musi być realizowany cyklicznie. Pamięć

charakteryzowana jest przez dwa parametry:

•

pojemność - jest funkcją liczby linii adresowych i wielkości komórki

•

czas dostępu

Pojemność pamięci jest funkcją liczb linii adresowych i wielkości komórki, jeśli

pamięć jest adresowana za pomocą 10-liniowej (10 bitowej) szyny adresowej, a każda

komórka może przechować 8 bitów pojemność wynosi 1024 bajty (1 kilobajt – 1KB).

Czas jaki upłynie od momentu zaadresowania komórki pamięci do uzyskania zapisanej

w tej komórce informacji nazywa się czasem dostępu. Czas dostępu współczesnych

pamięci DRAM wynoszą kilka nanosekund, co oznacza, że w ciągu tych kilku

nanosekund, zanim nie zostanie odczytana informacja, nie można zaadresować

następnej komórki. Nowsze typy pamięci tzw. EDO-RAM zostały wyposażone w

mechanizm pozwalający już w trakcie odczytu wystawić na szynie adresowej kolejny

adres. Pamięć ta posiada więc krótszy czas dostępu. Natomiast pamięci SDRAM

uzyskują jeszcze krótszy czas dostępu, dzięki zastosowaniu najnowszych rozwiązań

technologicznych tzw. synchronicznemu przesyłaniu danych z taktem zegara płyty

głównej.

Jednak najnowszym typem pamięci z jeszcze szybszym czasem dostępu są

współczesne kości pamięci DRAM, które posiadają multipleksowaną szynę adresową.

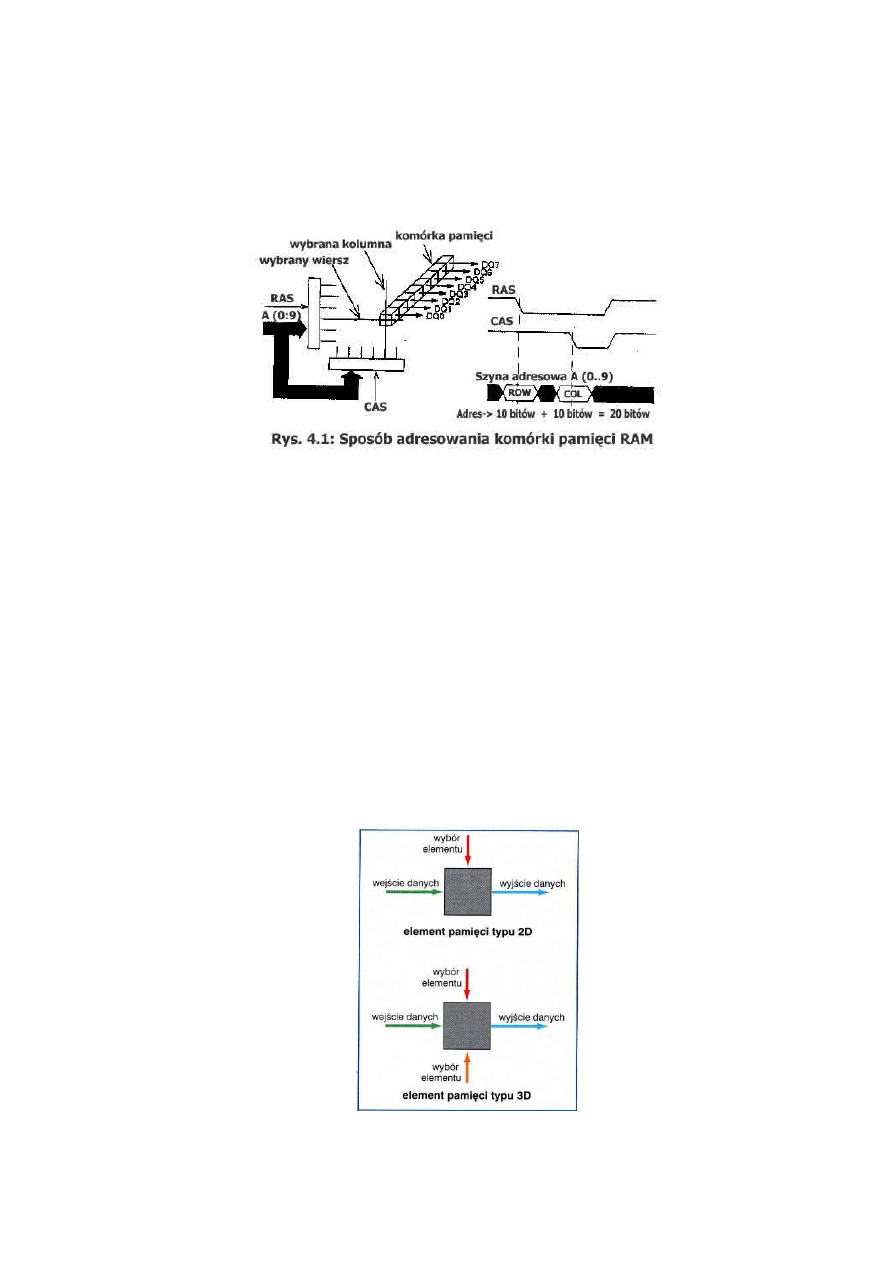

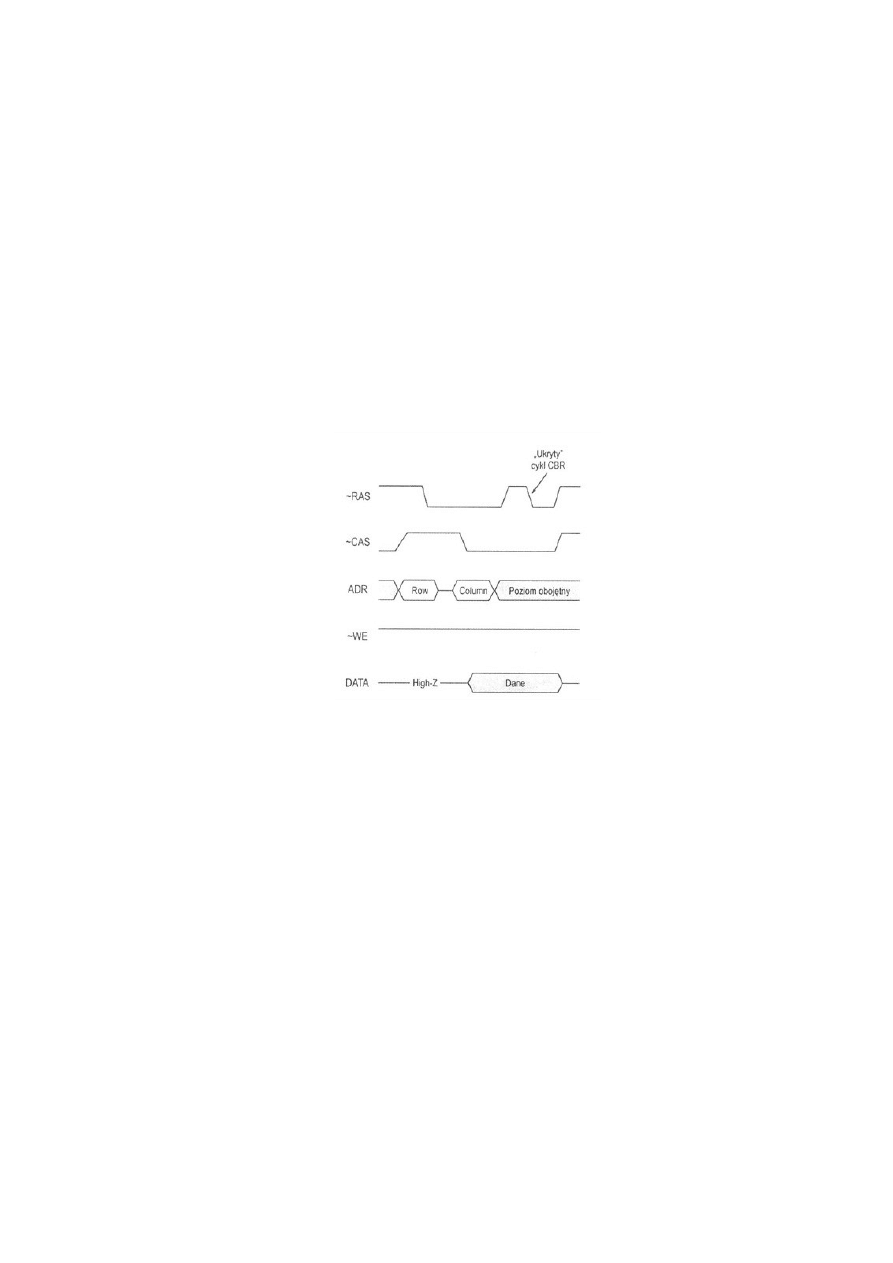

Adresowanie komórki pamięci następuje w dwóch fazach: w pierwszej, wraz z

opadającym zboczem impulsu RAS (Row Adress Strobe- strob adresu wiersza) na

szynie adresowej wystawiany jest adres (wiersza ROW), w fazie drugiej przy

5

6

opadającym zboczu sygnału CAS (Column Adress Strobe) wystawiany jest adres

kolumny COL. W ten sposób za pomocą 10 linii adresowych A [0..9] oraz linii RAS,

CAS uzyskuje się 20 bitowy adres , który jest zdolny zaadresować 1 MB.

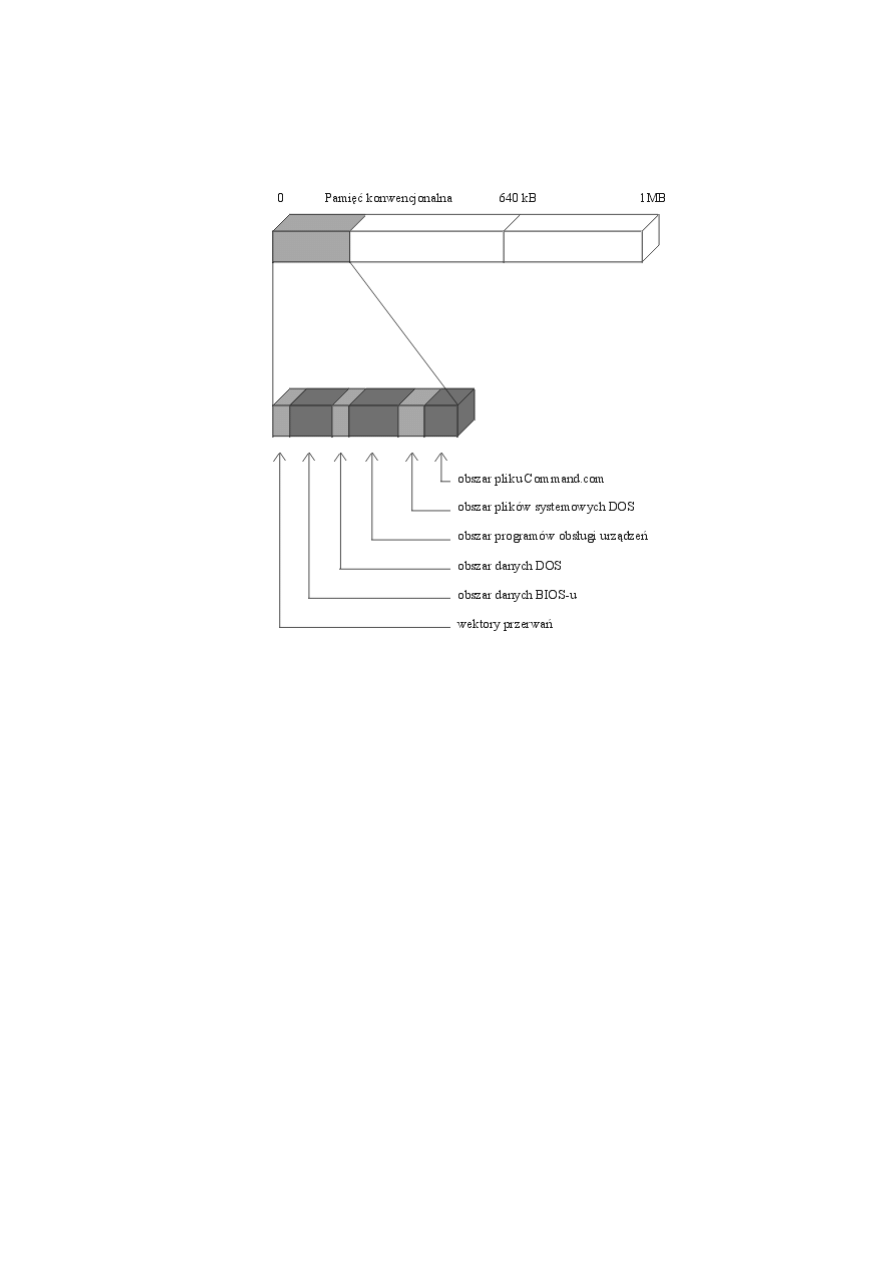

Rys. 1 Sposób adresowania komórek pamięci RAM

3. Uproszczona budowa pamięci

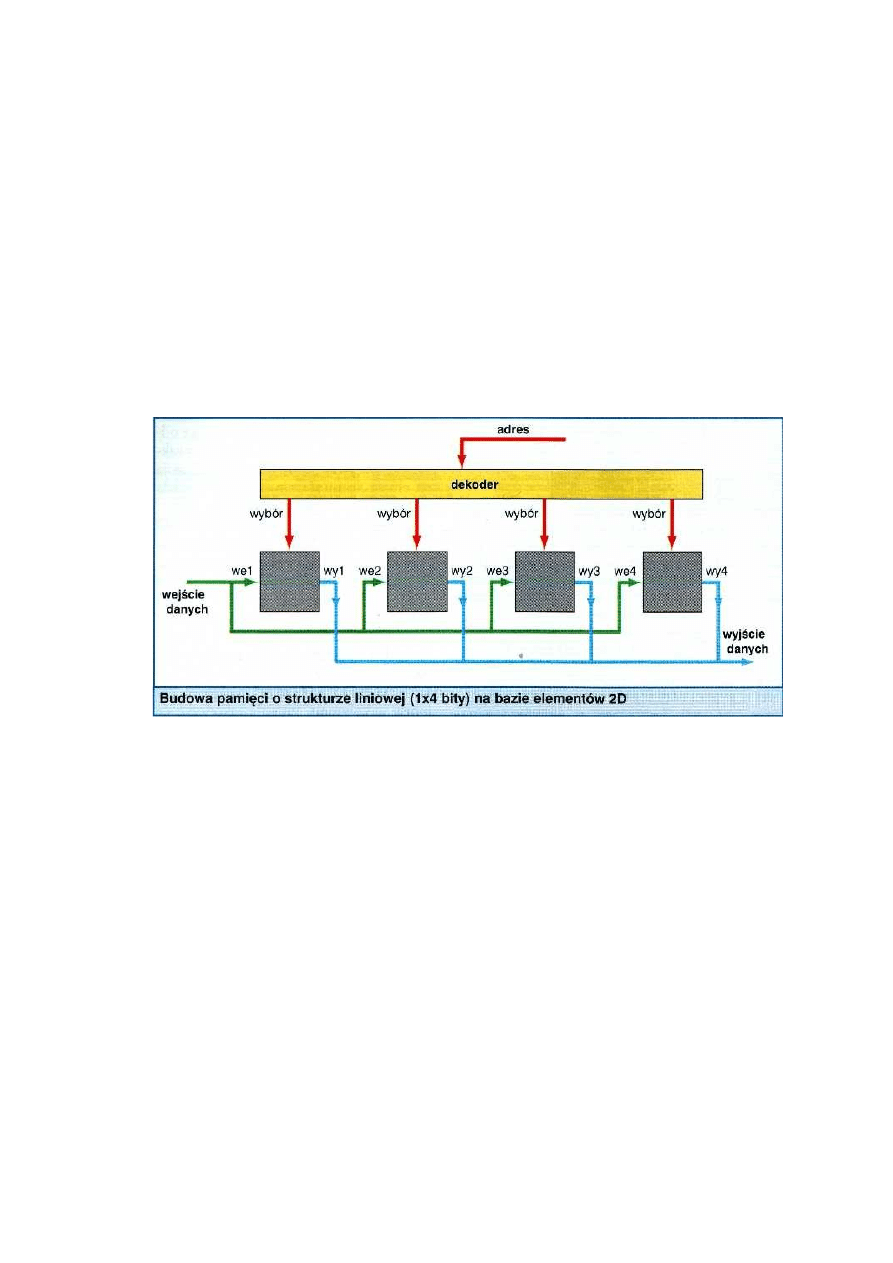

Aby komórki pamięci mogły funkcjonować w poprawny sposób trzeba je

odpowiednio zaadresować. Najlepszym sposobem na zorganizowanie pamięci jest tzw.

Adresowanie 2D. Do każdej z komórek podłączone jest wejście, sygnały te pochodzą z

dekodera i wyjścia. Istnieje też inny sposób adresowania 3D. Elementy dostępne w tym

przypadku dzielą się na wiersze i kolumny. Dlatego też komórka RAM musi posiadać

także dwa dodatkowe sygnały wybierania z dekodera dla kolumny i dla wierszy, oprócz

wyjścia i wejścia.

6

7

Rys. 2 Elementy pamięci typu 2D i 3D.

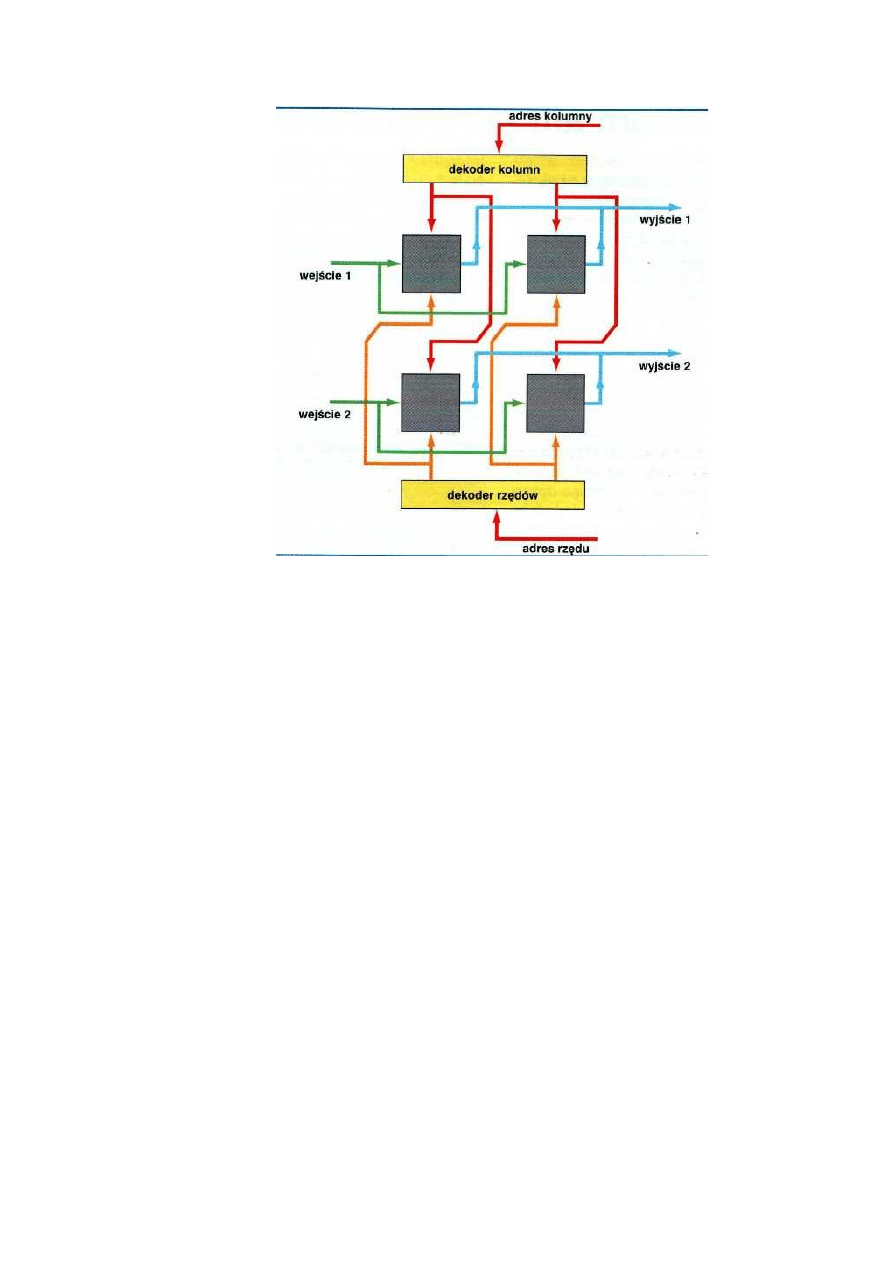

W przemyśle wykorzystywane układy pamięciowe zorganizowane w matrycę 3D, mimo

iż są bardziej skomplikowane i prezentują wolniejszy dostęp do poszczególnych bitów,

ale ich budowa w większe moduły RAM jest prostsza. W komputerach PC procesor

uzyskuje dostęp do danych zawartych w pamięci PC w pakietach o długości 4 bitów,

które są przesyłane sekwencyjnie lub naprzemiennie (inaczej zwane Interleave),

pomimo że ostatnie trzy bity są dostarczane wraz z taktem zegara, to konieczne jest

odpowiednie przygotowanie transmisji danych co wymusza przed pierwszym bitem

wstawienie jednego cyklu oczekiwania. Taki cykl oznacza się jako cykl 2-1-1-1.

Rys. 3 Budowa pamięci o strukturze liniowej

Wielkość oraz typ pamięci RAM jaką możemy zainstalować we współczesnych

komputerach PC zależy w dużym stopniu od tego z jakich podzespołów składa się nasz

komputer (płyta główna, procesor) oraz zależności od szerokości magistrali adresowej.

W zależności od typu pamięci głównej możliwe są następujące wielkości pamięci np.

dla procesora 8086 jest to tylko 1MB, dla 80286 jest to 16MB, a dla 80386/486 jest to

aż 4GB. Pierwsze komputery IBM PC z popularnym na tamte czasy procesorem

8086/88 tzw. XT posiadały pewien podział pamięci, który stał się wyznacznikiem a

później standardem w komputerach nowszej generacji. Obszar 1MB RAM został

podzielony przez konstruktorów IBM na dwa obszary

7

8

.

Rys. 4

Pierwszy z nich obejmował zakres 0 – 9FFFF (0 – 640 KB) tzw. pamięć

konwencjonalną. Drugi obszar miał zakres A0000 – FFFFF (640 KB – 1MB) i stanowił

tzw. pamięć górną. Obszar pamięci konwencjonalnej używany był przez sprzęt oraz

system operacyjny do przechowywana wektorów przerwań sprzętowych, danych BIOS-

u, obszarów buforów, plików DOS-u, plików systemowych, programów do obsługi

urządzeń (np. myszy, klawiatury, CD-ROM-u, itp.), popularnie zwanych driverów oraz

pierwszej kopii pliku command.com. Obszar ten może mieć różną wielkość w

zależności od konfiguracji komputera oraz ilości zainstalowanego osprzętu, konfiguracji

systemu, wersji systemu operacyjnego. Obszar ten może zajmować od około 60 KB do

8

9

160 KB, w niektórych przypadkach nawet ponad 200KB. Pozostała niewykorzystana

przestrzeń do granicy 640KB może zostać wykorzystana prze aplikacje.

Rys. 5 Obszary pamięci konwencjonalnej.

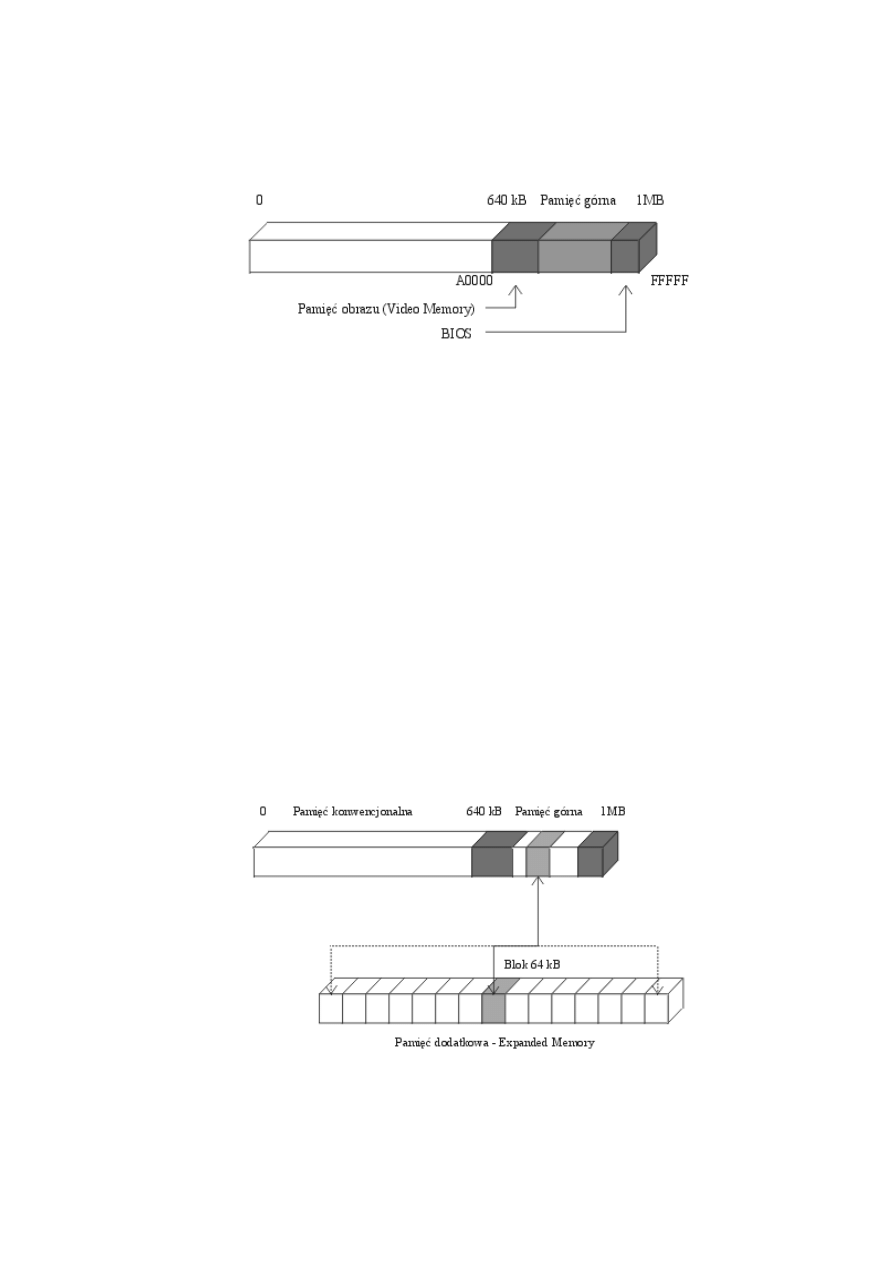

Pamięć górną (Upper Memory), która zajmuje obszar adresu od A0000 do FFFFF tzn.

640KB- 1MB jest niedostępna dla oprogramowania użytkownika. Obszar ten jest

podzielony na kilka części o ściśle podzielonym przeznaczeniu w sumie 384KB:

•

Obszar A0000 – BFFFF 128KB jest przeznaczony dla pamięci ekranu

•

Końcowa część obszaru pamięci górnej przeznaczona jest na ROM BIOS

9

10

•

Reszta pozostaje niewykorzystana w zależności od wielkości BIOS-u, typu

monitora i karty graficznej jest to około 190KB.

Rys. 6 Obszary pamięci konwencjonalnej.

Pamięć dodatkowa tzw. Expanded Memory

Jest to dodatkowa karta pamięci z układami RAM, stosowano ją do komputerów z

procesorem typu 8086, który miała ograniczoną liczbę pamięci RAM do 1MB.

Fizycznie adresowanie tej dodatkowej pamięci realizował standard LIM 3.2. Polegało to

na tym że w wolnym nie wykorzystanym dotąd obszarze Upper Memory wydzielono

specjalny obszar (okno) tzw. Page frame za pomocą którego możliwe jest odwoływanie

się do dowolnego segmentu zainstalowanej pamięci dodatkowej Expanded Memory.

Dzięki tej funkcji możliwe jest ściąganie w porcjach po 64KB zawartości dodatkowej

pamięci do pamięci konwencjonalnej i używanie zawartych w nich danych.

10

11

Rys. 7 Obszary pamięci dodatkowej.

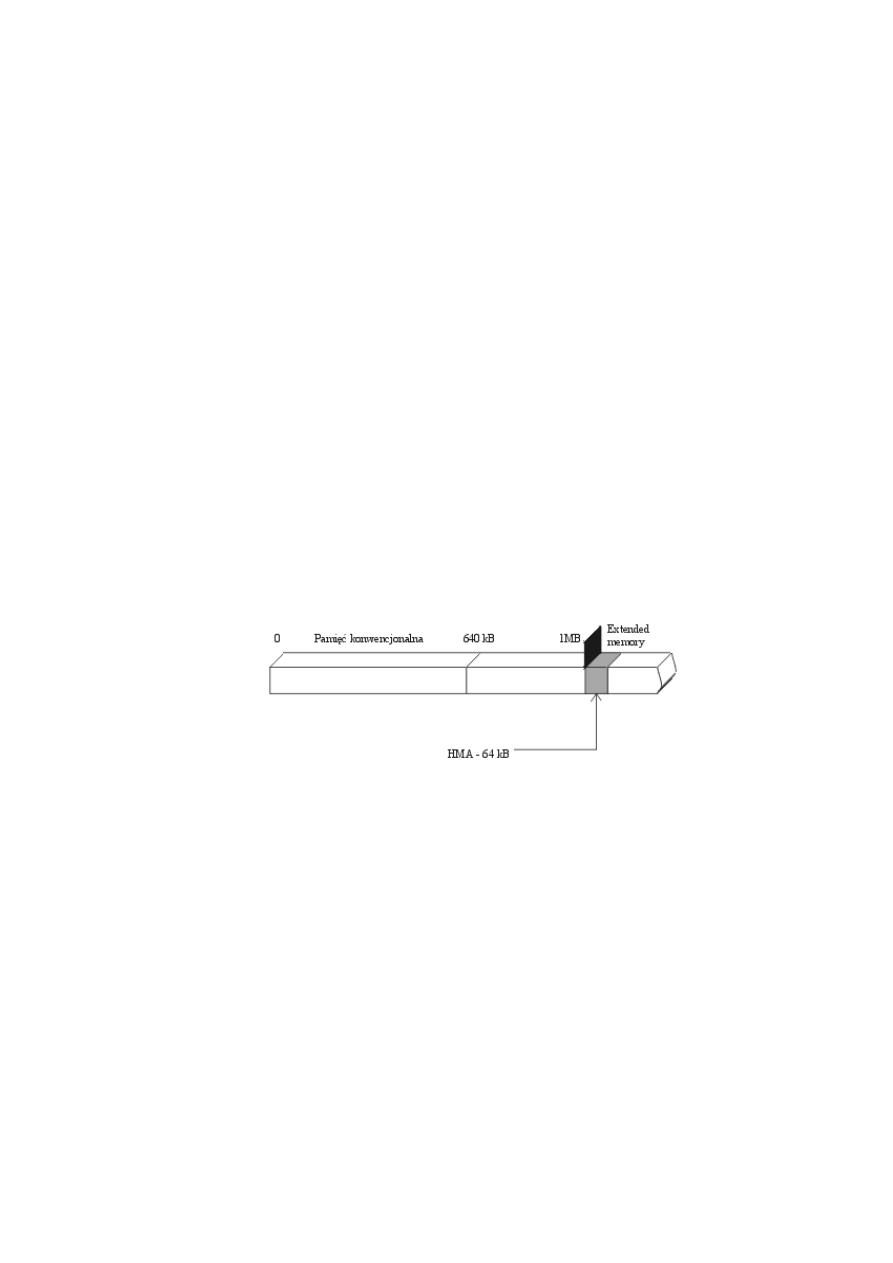

Pamięć rozszerzona (Extended Memory)

Dzięki nowszym technologiom możliwe jest zwiększenie szybkości magistrali co

umożliwia bezpośrednie adresowanie pamięci RAM, tak jest w przypadku procesora

286 oraz nowszych, które posiadają 20 bitową magistralę adresową. Obszar pamięci PC

jest wykorzystywany do dowolnych celów poza uruchamianiem procesów , ponieważ te

mogą być uruchamiane tylko w obszarze pamięci konwencjonalnej . Wynika to z

specyfikacji systemu DOS, który może pracować tylko w trybie rzeczywistym.

Zdecydowanie lepiej prezentują się systemy operacyjne WINDOWS i OS, które pracują

w trybie chronionym. Pierwszy blok 64KB powyżej granicy 1MB ma szczególne

znaczenie w obszarze Extended Memory, jest to tzw. obszar wysokiej pamięci High

Memory Area. W komputerach z procesorami 286 i nowszymi , przy zainstalowaniu

pamięci RAM większej niż 1MB, w wyniku segmentowego sposobu adresacji pamięci

RAM, istnieje możliwość umieszczenia w nim zasobów systemowych

wykorzystywanych przez DOS.

Rys. 8 Obszary pamięci rozszerzonej.

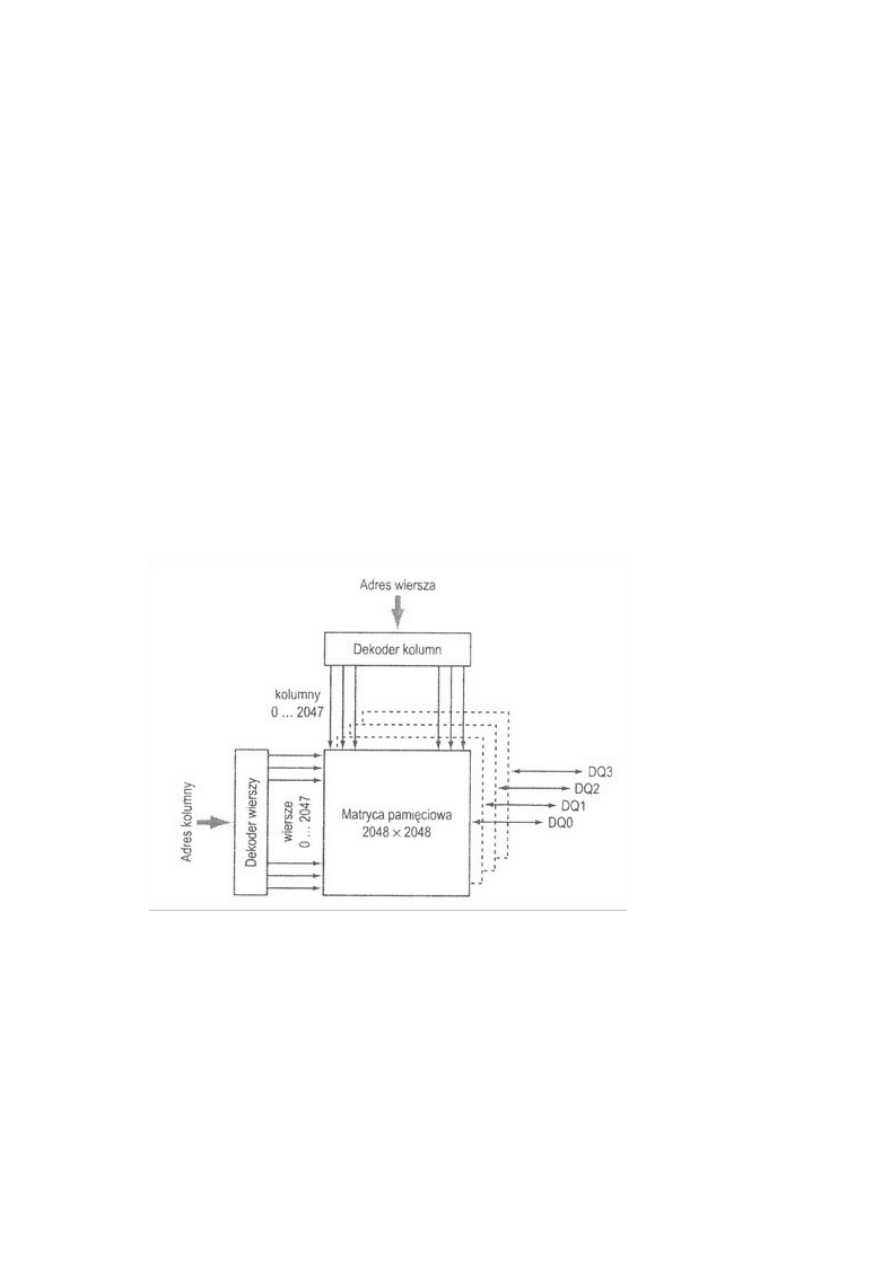

4. Pamięci dynamiczne:

Nieustanny rozwój komputerów PC wymusza na producentach wprowadzanie

na rynek coraz to nowszych, szybszych i bardziej sprawnych pamięci. Współczesna

architektura komputerów kładzie wielki nacisk na wymianę pamięci między procesorem

a pamięcią komputera. Połączenie między CPU a pamięcią PC jest głównym kanałem

informacyjnym i ma duży wpływ na szybkość pracy całego komputera. Elementarną

jednostką pamięci jest prosta struktura półprzewodnika składająca się z tranzystora i

11

12

kondensatora, prosta konstrukcja tego urządzenia powoduje że jest ono niezwykle mały

i możliwe jest umieszczenie go w dużej ilości na niewielkiej płaszczyźnie krzemu.

Wadą jest możliwość utraty ładunku, dlatego stosuje się tzw. odświeżanie jej zawartości

(wartości bitów 1 i 0 opowiadają kondensatorowi naładowanemu lub nie). Układy tego

typu nigdy nie odpoczywają dlatego nazywane są pamięcią dynamiczną, bez względu

na to czy pamięć jest wykorzystywana w cyklu zapisu lub odczytu w jej wnętrzu ciągle

trwa ruch mający na celu zapamiętanie posiadanej informacji. Obecnie używane

pamięci komputerowe posiadają wiele setek milionów pojedynczych komórek. Aby

pamięci te były poprawnie wykorzystywane grupuje się je w macierze prostokątne.

Pojedyncza macierz nazywana jest płatem pamięciowym. Liczba tzw. Płatów decyduje

o szerokości szyny danych danego układu. Jedna płyta jest to X*Y*1 bit, aby osiągnąć

szerokość jednego bajtu jest potrzebnych osiem płatów. Tzw. macierz pamięciowa jest

sercem współczesnych układów pamięciowych. Ważną rolę odgrywają także układy

dekoderów adresujących daną komórkę. Dostęp do układu pamięci jest dość prosty,

dzięki sygnałom kontrolnym określa się tryb dostępu do danego cyklu. Końcówki

adresowe danego układu scalonego są multipleksowane tzn. adresy komórek są

przekazywane w dwóch partiach (pierwszy wiersz, drugi kolumna) stosowanie do

aktualnego trybu dostępu, doprowadzając informację do portu danych lub do odbierając

ją (odczyt lub zapis). Pamięci dynamiczne dzielimy na typ konwencjonalny, FPM,

EDO, SDRAM.

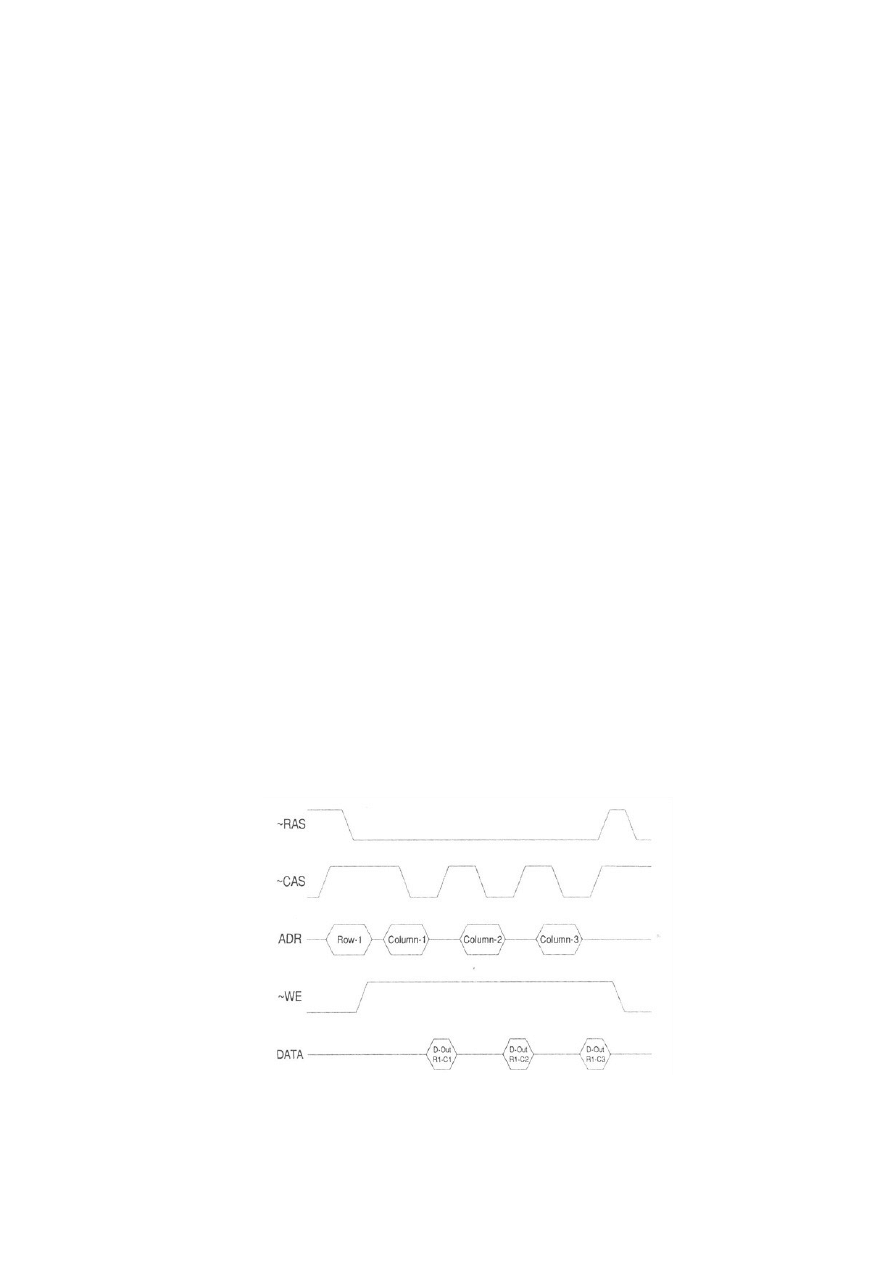

4.1.Typ konwencjonalny (Page Mode)

Jest to najstarszy typ dostępu do pamięci dynamicznej polegający na oddzielnym

adresowaniu wierszy oraz kolumn dla każdego z cykli. Adres wiersza jest zdejmowany

przez układ pamięciowy z szyny adresowej w momencie opadającego zbocza sygnału

sterującego tzw. RAS (Row Address Select. Po zatrzaśnięciu tego fragmentu adresu w

rejestrze wejściowym następuje krótkotrwałe zwolnienie szyny adresowej, a następnie

odkłada się na niej część adresu odpowiedzialnego za numer kolumny. Adres ten

wprowadzany jest do układu pamięciowego w momencie zakodowania opadającego

zbocza sygnału sterującego tzw. CAS (Column Address Select). Odczyt następuje w

momencie zdejmowania adresu kolumny, również stan końcówki wejścia, jeżeli jest

wysoki, rozpoznawany zostaje jako cykl odczytu i zaadresowana wartość komórki

zostaje wprowadzana na szynę danych. Zapis natomiast następuje jeżeli sygnał na linii

12

13

sterującej wejścia znajduje się na poziomie niskim, układ wtedy rozpoznaje cykl zapisu

i pobiera dane z szyny danych. Tryb adresowania komórki jest taki sam jak w

przypadku odczytu.

4.2 FPM (Fast Page Mode)

Tryb FPM jest lepszym i szybszym dostępem do pamięci dynamicznej. Czas

dostępu jest krótszy, różnica między typem konwencjonalnym a FPM polega na

uproszczeniu mechanizmu adresowania. Dostęp do dowolnej komórki pamięci

operacyjnej komputera nie odbywa się poprzez odczytywanie lub zapis tylko jednej

wartości, architektura magistrali narzuca bardziej racjonalny styl postępowania.

Wymiana danych między pamięcią operacyjną a komputerem odbywa się w porcjach po

kilka bajtów równocześnie. Przetwarzane przez komputer dane oraz programy skupione

są w pewnym spójnym odcinku przestrzeni adresowej i w dużej mierze przylegają do

siebie. Adres wierszy przekazywany jest do układu pamięciowego tylko raz na cztery

cykle dostępu, które razem tworzą swego rodzaju pakiet tzw. BURST. Pozostałe cykle

domyślnie mają ten sam adres wiersza tylko zmieniony adres kolumny, czas trwania

takiego cyklu podaje się często w formie czterech liczb oddzielonych od siebie kreską.

Na przykład x-x-x-x: pierwsza z liczb informuje o czasie trwania pierwszego cyklu

(przekazywany jest adres wiersza i kolumny) a pozostałe liczby odpowiadają kolejnym

serjom cykli w obrębie tego samego wiersza, im mniejsze są zadane liczby, np. 1-1-1-1,

tym wymiana danych jest szybsza. Pamięć FPM umożliwia osiągnięcie w najlepszym

razie stanu 5-3-3-3 przy taktowaniu zegarem 66 MHz.

13

14

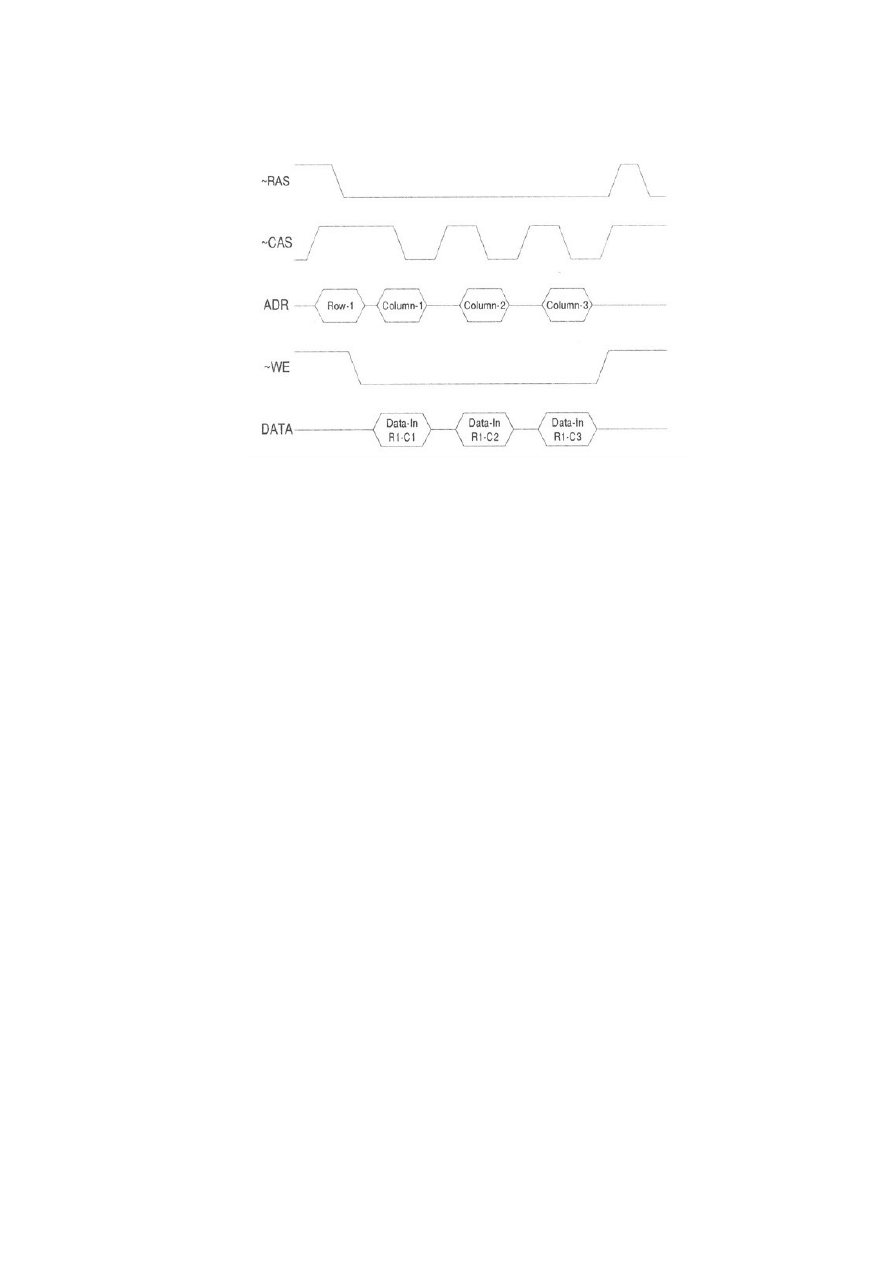

Rys. 9 Cykl odczytu pamięci dynamicznej – FPM.

Rys. 10 Cykl zapisu pamięci dynamicznej – FPM.

4.3. EDO (Extended Data Out)

Pamięć dynamiczna EDO była kolejnym etapem rozwoju prowadzącego do

skrócenia czasu dostępu, nie było to z pewnością rozwiązanie nowatorskie a raczej

drobna poprawka w układach sterowania w buforach wyjściowych. Wprowadzone na

rynek układy EDO były początkowo dużo droższe od konwencjonalnej pamięci ale ich

szybka popularność spowodowało zwiększony popyt i spadek cen. Sytuacja ta uległa

odwróceniu i pamięć konwencjonalna była droższa w wyniku znikomej produkcji.

Dzięki prostej i sprawdzonej konstrukcji oraz niskim kosztom produkcji kości EDO

zdobyły akceptację rynku. Charakterystyczne dla EDO jest to iż aktualny cykl dostępu

do pamięci może się rozpocząć przed zakończeniem cyklu poprzedniego a dane

utrzymywane są na wyjściu przez czas dłuższy niż w przypadku pamięci

konwencjonalnej lub FPM. W trybie konwencjonalnym oraz FPM wzmacniacze

wyjściowe odcinały dane w momencie wykrycia narastającego zbocza CAS. Parametry

14

15

dostępu do EDO w tzw. trybie BURST mogą osiągnąć w optymalnych warunkach

wartość 5-2-2-2, sekwencja zapisu pamięci jest jednak identyczna z tą, jaka ma miejsce

w pamięci konwencjonalnej.

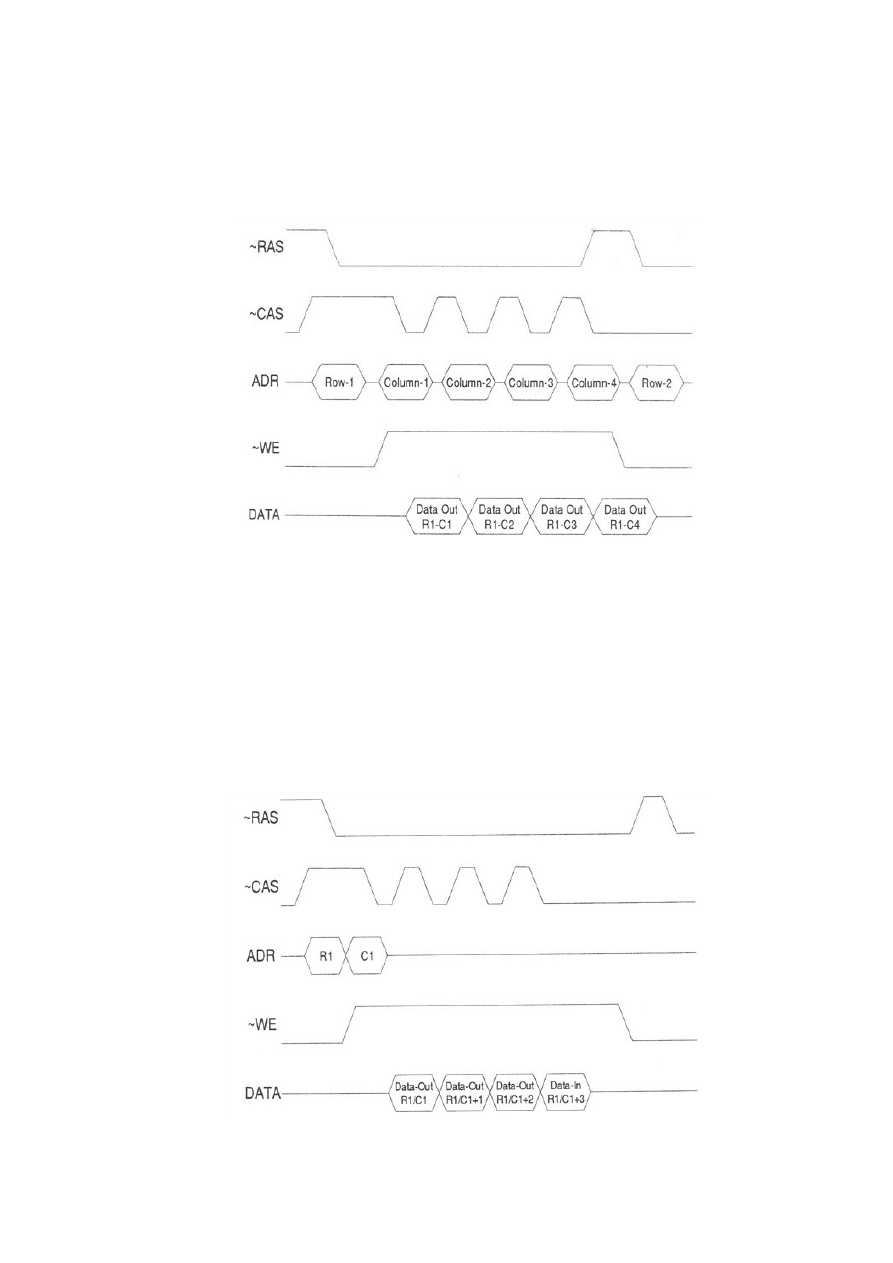

Rys. 11 Cykl zapisu pamięci dynamicznej – EDO.

15

16

Rys. 12 Cykl odczytu pamięci dynamicznej – EDO.

4.4 BEDO (Burst EDO)

Pamięci BEDO stanowią połączenie dwóch idei pamięci: wydłużenie czasu

obecności danych na końcówkach wyjściowych (EDO) oraz strumieniowanie tzw.

Pipelining. Pamięci te mimo iż były szybsze nigdy nie doczekały się masowej

akceptacji, główną przyczyna jest to iż produkowane wówczas płyty główne nie

obsługiwały tego typu pamięci. Były to głównie płyty Intela 430VX oraz 430TX, gdzie

w/w płyty były nastawione na obsługę pamięci synchronicznej SDRAM, a obsługa

BEDO nie została w nich w ogóle zaimplementowana. Parametry Burst dla BEDO 5-1-

1-1 sięgają wartości typowych dla pamięci synchronicznych. Taki wynik mógł być

możliwy dzięki uproszczonemu sposobowi adresowania. Adres przekazuje się tylko raz

na cały poczwórny cykl Burst i odnosi się on do początku obszaru. Pozostałe trzy

adresy generowane są już w układzie, sygnał CAS pełni od momentu przekazania

adresu funkcję zegara kluczującego, a chip BEDO reaguje podobnie do pamięci

SDRAM, udostępniając dane z trzech kolejnych komórek.

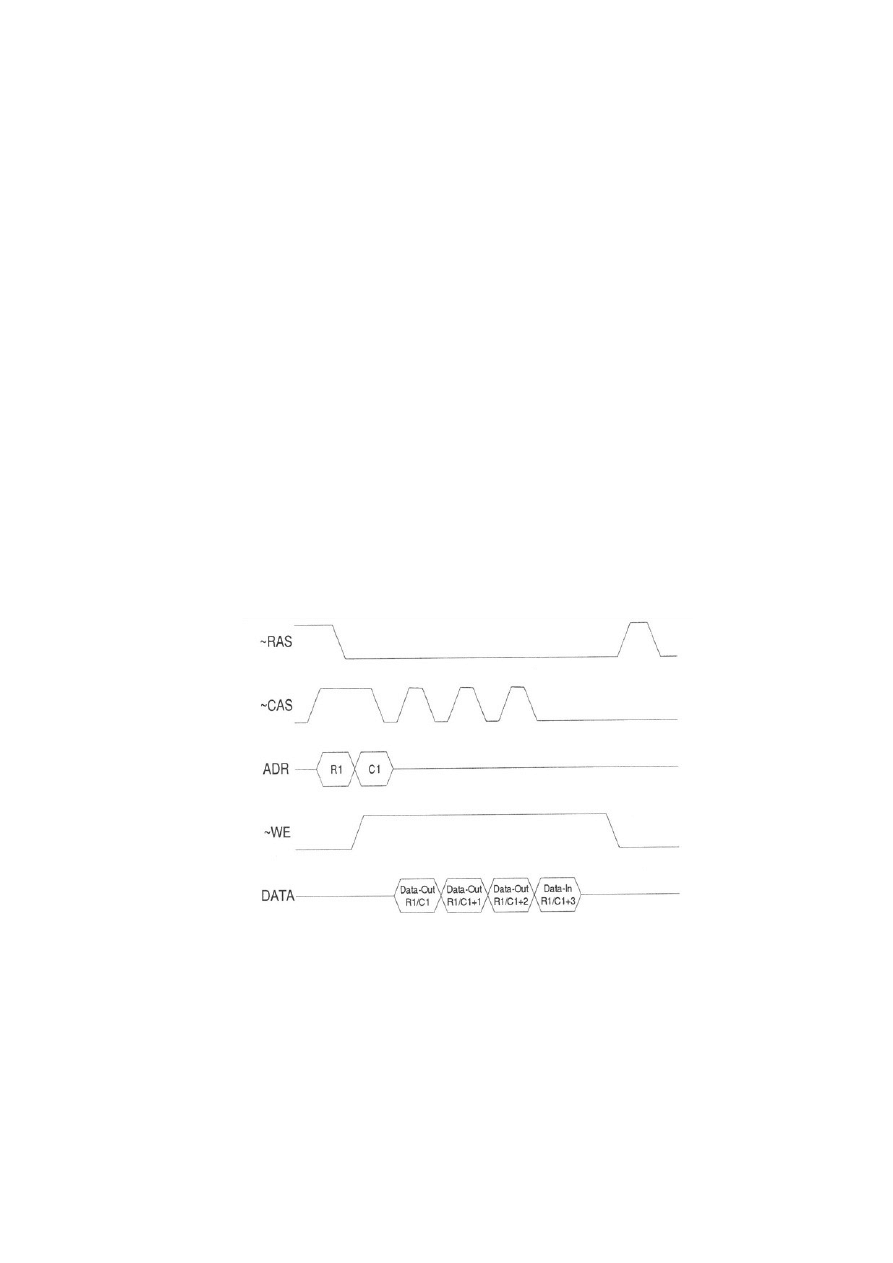

Rys. 13 Cykl odczytu pamięci dynamicznej – BEDO.

4.5 SDRAM

16

17

Coraz nowsze komputery wymuszały na producentach wprowadzanie coraz to

szybszych i wydajniejszych pamięci operacyjnych. I tak z wprowadzeniem procesorów

Pentium II stało się jasne że modele taktowane zegarem powyżej 350 MHz nie mogą

efektywnie współpracować z magistralą pamięciową 66MHz. Nie mniejszy nacisk

wywołało pojawienie się podstawki Super 7, której specyfikacja dopuszczała

podwyższenie przepustowości poza zakres oferowany przez szynę 66MHz. Głównym

problem polegał na tym, że niemożliwe było podniesienie częstotliwości pracy

dotychczasowych pamięci PC. Pamięci dynamiczne SDRAM nie różnią się w specjalny

sposób od innych pamięci dynamicznych. Nadal nośnikiem informacji jest matryca

komórek bazujących na kondensatorach i tranzystorach wykonanych w technice

CMOS. Inne są sposoby sterowana matrycą oraz technika dostępu. Wszystkie sygnały

sterujące SDRAM synchronizowane są przez jeden przebieg zegarowy, ułatwia to pracę

pamięci oraz integrację pamięci w systemie. Dostęp do pamięci SDRAM ma miejsce z

reguły w formie cykli zgrupowanych (Burst). Dostęp taki obejmuje swoim zasięgiem 2,

4, 8 kolejnych cykli albo też rozciąga się na cały wiersz, może mieć charakter

sekwencyjny i przemierzać kolejne adresy logiczne (choć niekoniecznie musi zaczynać

się na początku) lub przebiegać według określonego szablonu np. w kolejności 2, 3, 0, 1

w obrębie grupy poczwórnej. Burst może zostać przerwany (tryb Suspend) i ponownie

wznowiony a jego poszczególne elementy opuszczane (sygnał DQM). Układ SDRAM

przed przystąpieniem do pracy musi zostać odpowiednio przygotowany, odbywa to się

podczas uruchamiania komputera i dokonywane jest na polecenie BIOS-u. W tym

procesie do pamięci PC przekazywane są dane o charakterze konfiguracyjnym, takie jak

długość i typ dostępu oraz niektóre parametry czasowe. Dane te są umieszczane w

specjalnym rejestrze konfiguracyjnym. (Mode Register). SDRAM to krok naprzód w

dziedzinie rozwoju układów pamięci ale z pewnością nie rozwiązuje jeszcze wszystkich

problemów. Zalety tej techniki stają się widoczne i mierzalne w określonych

warunkach. Czas opóźnienia mierzony od momentu przyłożenia do momentu

pojawienia się pierwszych danych jest nadal stosunkowo długi, wynosi on około 5

cykli zegarowych, czyli jest cały czas porównywalny z wartościami typowymi dla

pamięci EDO oraz FPM, poza tym Burst 5-1-1-1 możliwy był do osiągnięcia przez

pamięć BEDO, która mogła dużo wcześniej zostać wdrożona. Przewaga SDRAM nad

starszymi braćmi uwidacznia się dopiero poprzez wzrost taktowania częstotliwości

magistrali powyżej 66MHz. Pojedynczy cykl dostępu do SDRAM przy częstotliwości

100MHz trwa zaledwie 10 ns, a Burst swym zasięgiem obejmuje cały wiersz pamięci

zapewniając potężny strumień danych w tym właśnie tempie. Pamięć SDRAM

17

18

wymienia dane z otoczeniem najchętniej w dużych porcjach. Pod pewnymi względami

chip SDRAM można traktować jako programowalny sterownik obsługujący swe własne

matryce pamięciowe. Lista rozkazów tego sterownika obejmuje pozycje umożliwiające

konfigurację urządzeń, operacje zapisu i odczytu oraz manipulacje bankami. Układ

SDRAM musi zostać odpowiednio zaprogramowany przed podjęciem pracy.

Programowanie układu pamięci odbywa się poprzez następujące operacje:

•

Wymiar opóźnienia pomiędzy przełożeniem adresu kolumny a wprowadzeniem

pierwszej pozycji danych (CAS Latency). Parametr ten podaje się w jednostkach

CLK a dopuszczalne wartości to 2 lub 3.

•

Długość pakietu (Burst Lenght), dopuszczalna wartość to 1, 2, 4, 8

•

Format pakietu (sekwencja lub z przeplotem)

Układ SDRAM rozpoznaje fazę programowania dzięki określonej konfiguracji

sygnałów sterujących RAS = CAS = WE = 0. Dane na liniach A0 – A9 sprawdzane są

pod względem swojej poprawności i jeśli nie spełniają przyjętych kryteriów, zostają

odrzucone a stan układu nie ulega zmianie. Zapis i odczyt najlepiej przebiegają w

formie pakietów Burst. Ponieważ parametr transmisji jest określony w fazie

programowania, wystarczy podać tylko adres początkowy obszaru pamięci, a kolejne

obszary zostaną zdefiniowane w sposób jednoznaczny. Adresy wierszy nadawane są w

momencie aktualizacji banku, tak że zmienia się adresy kolumn, a konkretnie kilku

ostatnich bitów. Pierwszy zestaw danych przesyłany jest zgodnie z definicjami

zawartymi w fazie programowania po 2 lub 3 cyklach zegarowych od momentu podania

polecenia. Cykl zapisu następuje bez opóźnienia.

5. Moduły pamięciowe

Moduły pamięciowe to podłużne płytki, na których umieszczono tzw. kostki

pamięci wyposażone są w 168 stykowe złącze i mogą dysponować od 16 poprzez 32 do

64 bitową magistralą danych. Niezbędna liczba kostek określonego typu wynika z ich

własnej organizacji – liczby wprowadzonej linii danych. Dla zagwarantowania pokrycia

magistrali 64 bitowej potrzeba co najmniej 16 kostek w formacie x4 lub 8 kostek w

formacie x8. Choć uzyskanie określonej pojemności narzuca resztę elementów

architektury modułu. Nie jest obojętne czy dany moduł zawiera 16 kostek x4 czy 8

18

19

kostek x8, należy bowiem pamiętać iż ma to wpływ na niezawodność danego układu. W

pewnych konfiguracjach zmienia się prawdopodobieństwo pojawienia się błędów

pojedynczych (łatwiejszych do wykrycia i usunięcia). Różnie zachowują się moduły,

które pobudzają na module wszystkie układy scalone a inaczej zachowują się moduły

które pobudzają część układów scalonych. Ma to wpływ na pobór prądu,

charakterystykę obciążenia, a w konsekwencji generację zakłóceń na liniach danych i

liniach sterujących. Korzystny rozkład obciążeń owocuje zwiększoną podatnością na

błędy. Moduły można podzielić na trzy podstawowe typy : SIMM-30-końcówkowy,

SIMM PS/2 (72 końcówkowy) oraz DIMM.

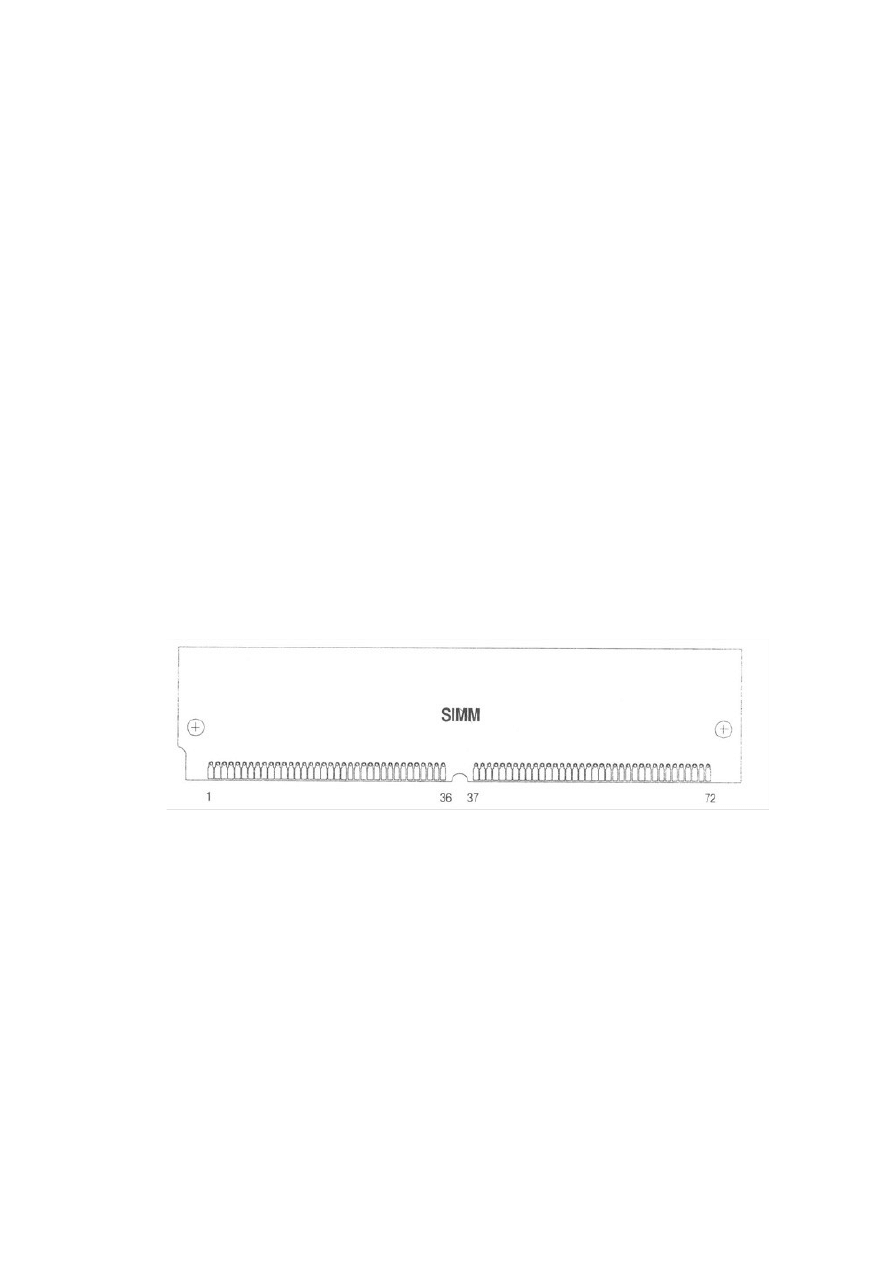

5.1 Moduły SIMM-30 (SIP)

Listwa połączeniowa płytki ma tylko 30 styków, pierwotnie role styków

odgrywały krótki szpilki (odmiana SIP), później zaczęto stosować pola kontaktowe na

płycie drukowanej. Moduły tego rodzaju były produkowane z kontrolą parzystości lub

bez tej opcji. SIMM 30 dysponują 11 bitową szyną adresową, dwukierunkowa 8 bitowa

magistrala danych uzupełniana oraz dwiema dodatkowymi liniami DP-Out oraz DP-In.

Moduły te były głównie stosowane na płytach głównych procesorów x86 – x486, lecz

dla uzyskania odpowiedniego szerokości magistrali (16 bitów) stosowano co najmniej

dwie jednostki. Do masowej produkcji trafiały głównie wersje o pojemności 256 kB a

później również pojemności zwiększone 1 MB oraz 4 MB. Większych modułów nigdy

nie produkowano.

19

20

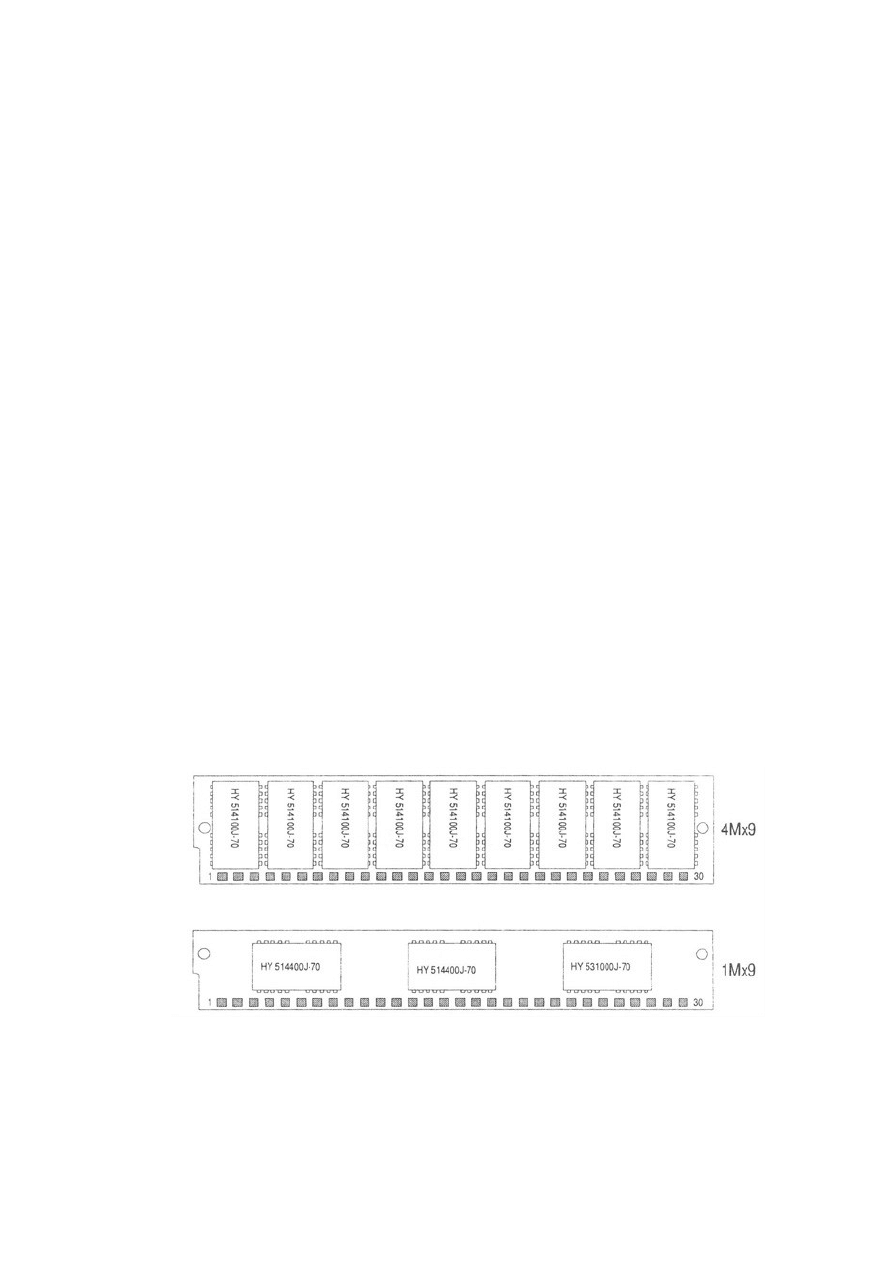

Rys. 14 Najczęściej spotykana konfiguracja modułów SIMM.

5.2 Moduły SIMM PS/2

Moduły tego typu były skonstruowane aby wykorzystać 32 bitową magistralę

nowych procesorów, moduły produkowane były w formie 36 bitowej bez bitów

parzystości (FPM oraz EDO). Kształt a w szczególności wysokość płytki zależała od

ilości zainstalowanych na niej układów scalonych, SIMM posiadają 72 stykowe złącze.

Moduły SIMM PS/2 bez parzystości (FPM i EDO) wprowadzają magistralę danych o

szerokości 32 bitów (DQ0 – DQ31) bez dodatkowych linii na parzystość.

Najważniejszym parametrem określającym charakterystykę modułu to czas dostępu

tzw. T RAC (Access Time from ~RAS), jest to miara opóźnienia wprowadzonego przez

moduł do momentu przyłożenia adresu wiersza do pojawienia się danych. Średnie

wartości wahają się w przedziale od 50ns do 80ns, typową było 70ns. Identyfikacja

modułu pamięci odbywa się przez program BIOS w poszczególnych fazach

konfiguracji komputera.

Rys. 15 Przykładowa płytka modułu SIMM PS/2.

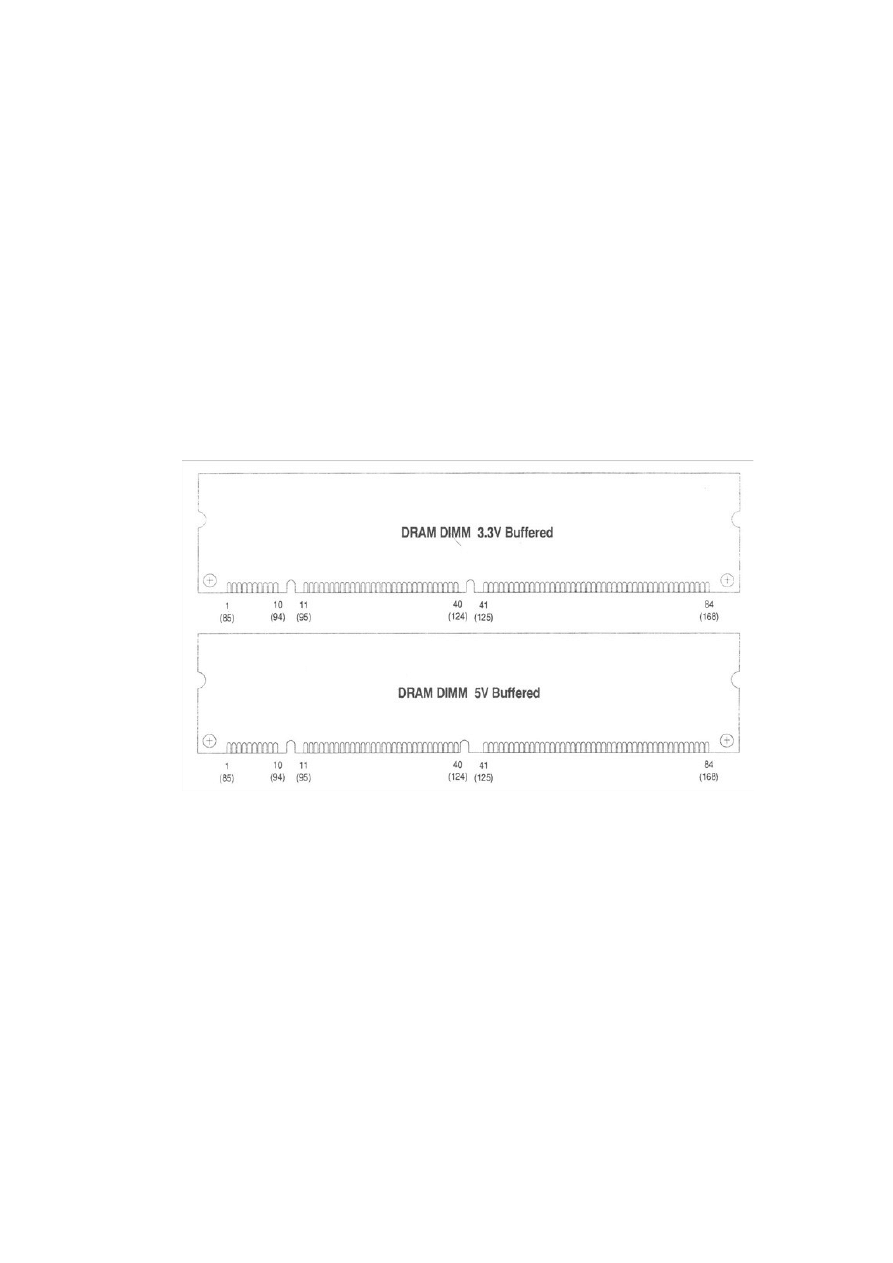

5.3 Moduły DIMM

Moduły pamięci DIMM mają 168 stykowe złącze i dysponują 64-bitową magistralą

danych, do rozszerzenia pamięci na płycie głównej potrzebny jest tylko 1 moduł (3

sekcje styków oddzielone wcięciami w płytkę). Listwa połączeniowa jest dwustronna,

pamięci te mogą stanowić nośnik klasyczny DRAM – FPM, EDO lub nowszy SDRAM.

20

21

Pamięci te mają specyficzny kształt, system wcięć w płytce który umożliwia ich

mechaniczne odróżnienie. Moduły można podzielić na dwa typy:

•

niebuforowane

(unbuffered)

Moduły niebuforowane są powszechnie stosowane w systemach nie wymagających

pamięci większych niż 768 MB i wykonywane są w 2 wersjach : 64 bitowej-bez

kontroli

ECCi

72

bitowe

-

z

kontrolą

ECC

•

buforowane

(buffered)

moduły buforowane zawierają dodatkowe rejestry umożliwiające dostęp w trybie

stronicowania, stosowane są w systemach wymagających dużych pojemności

pamięci operacyjnej - powyżej 1 GB i wykonywane są jedynie w wersjach z 72

bitową szyna danych. Są większe od niebuforowanych i posiadają dodatkowe

rejestry i układy scalone.

Współczesne pamięci SDRAM są taktowane częstotliwościami sięgającymi 100 MHz,

tak szybkie pamięci i pochodzące od różnych producentów mogą nawet znacznie różnić

się parametrami częstotliwości. Firma Intel przewidując problemy płyt głównych z

pamięciami różnych producentów opracowała specyfikację o nazwie PC 100

oznaczającą precyzyjne cechy i parametry form pamięci. Zgodnie z ta specyfikacją

każdy moduł DIMM SDRAM powinien posiadać niewielką, szeregową pamięć

EEPROM, w której zapisane będą przez producenta parametry modelu.

Podczas restartu komputera BIOS płyty głównej odczytuje zawartość tej pamięci i

dokonuje odpowiedniej konfiguracji systemu uwzględniającej parametry zainstalowanej

pamięci. Operacja odczytu danych z pamięci EEPROM nosi nazwę SPD (Serial

Presence Detect). Specyfikacja PC 100 narzuca producentom stosowanie jednolitego

sposobu oznaczenia pamięci wg wzoru: "PC 100-abc-def"

•

CL (CAS Latency) - minimalna liczba cykli sygnału taktującego podczas operacji

odczytu, od momentu uaktywnienia sygnału CAS do momentu pojawienia się

danych na wejściu modułu DIMM (wartość CL wynosi zwykle 2 lub 3)

•

tRDC (RAS to CAS Delay) - nieodzowne małe opóźnienie pomiędzy sygnałami

RAS/CAS, wyrażone w cyklach zegara systemowego (zwykle wart. 2)

•

tRP (RAS Precharge) - czas wyrażony w cyklach zegara taktującego określający

minimalną pauzę, pomiędzy kolejnymi komendami wykonywanymi przez pamięć

21

22

•

tAC (Access from Clock) - maksymalny czas dostępu wyrażony w nanosekundach i

wynoszący zwykle 6 lub 7.

•

SPD Rev - specyfikacja komend SPD - parametr może nie występować- jest

opcjonalny

•

parametr zapasowy

np. scalona pamięć modułu DIMM PC100-322-60 informuje użytkownika, że przy

częstotliwości 100 MHz parametry tego modelu są następujące- CL-3, tRDC-2, tRP-2,

tAC-6, SPDRev - nie występuje, f=0, rezerwowy=0. Uwaga: Wartości parametru CL= 2

lub 3 praktycznie nie mają żadnego wpływu na szybkość systemu z procesorami

zaopatrzonymi w cache L2, także bardzo niewielki wpływ mają na szybkość

procesorów bez Cache L2.

Rys. 16 Przykładowa płytki modułu DIMM dla zasilania 3,3V i 5V.

22

23

6. Odświeżanie

Konieczność odświeżania komórek pamięci dynamicznej wynika z zasady jej

działania oraz budowy samego modułu. Pojedyncze komórki układu scalonego

zgrupowane są w grupie prostokątnych matryc o pewnej określonej liczbie wierszy

(Rows) oraz kolumn (Columns). Liczba matryc odpowiada szerokości słowa, które

można przechowywać w takim układzie. Każda z matryc odpowiada jednemu bitowi

szyny danych doprowadzonej do układu pamięci. Linie adresowe wierszy i kolumn są

wspólne

dla

wszystkich

matryc.

Rys. 17 Wewnętrzna organizacja scalonego układu pamięciowego.

23

24

Odświeżanie sprowadza się jedynie do pobudzenia linii wierszy czyli wszystkich

komórek z danego wiersza a jest ich ponad 16 milionów. Proces pobudzenia zasadniczo

nie różni się znacznie od procesu zapisu odczytu lecz dotyczy całego wiersza a nie

określonych komórek w zadanym czasie. Jednak pamięć aby poprawnie działała musi

być odświeżana co pewien okres. Kolejność pobudzenia wierszy macierzy jest obojętna,

ważne jest aby wszystkie z nich otrzymały przynależny do siebie impuls nie rzadziej niż

raz na pewien jasno zdefiniowany okres zwany cyklem odświeżania (Refresh Time).

Okres między dwoma kolejnymi impulsami nie może być dłuższy od cyklu

odświeżania. We współczesnych pamięciach taki cykl określa się na od kilku do

kilkudziesięciu milisekund i zależy zarówno od rozmiarów jak i od organizacji

logicznej (liczby wierszy). Podział cyklu odświeżana na odcinki równej wielkości daje

w wyniku okres przebiegu zegarowego (Refresh Rate) koniecznego do spełnienia

wymogu czasowego, narzuconego przez cykl odświeżania. np. 16Ms/1024 = 15,6μs,

która jest typowy dla większości układów pamięci. Niektóre kości pamięci mają

specjalnie wydłużony cykl odświeżania (Extended Refresh) wynoszący 125μs.

Pojedyncze impulsy można zgrupować w pakiet tzw. Burst Refresh lub możliwe jest

rozłożenie równomierne tzw. Distributed Refresh. Matryce grupujące komórki są

połączone z resztą komputera PC za pośrednictwem układów pośrednich. Wspomniane

układy odpowiedzialne są za dekodowanie adresów i analizę impulsów ale nie

odpowiadają za odświeżanie pamięci. System odświeżania pracuje według

harmonogramu narzuconego przez inne elementy architektury komputera np. system

przerwań. Sygnalizacja momentu odświeżania odbywa się za pomocą pewnej umownej

sekwencji impulsów sterujących ~RAS oraz ~CAS. W praktyce przyjęły się trzy główne

metody: RAS – RAS Only, CBR – CAS-Before-RAS oraz ukryty – Hidden.

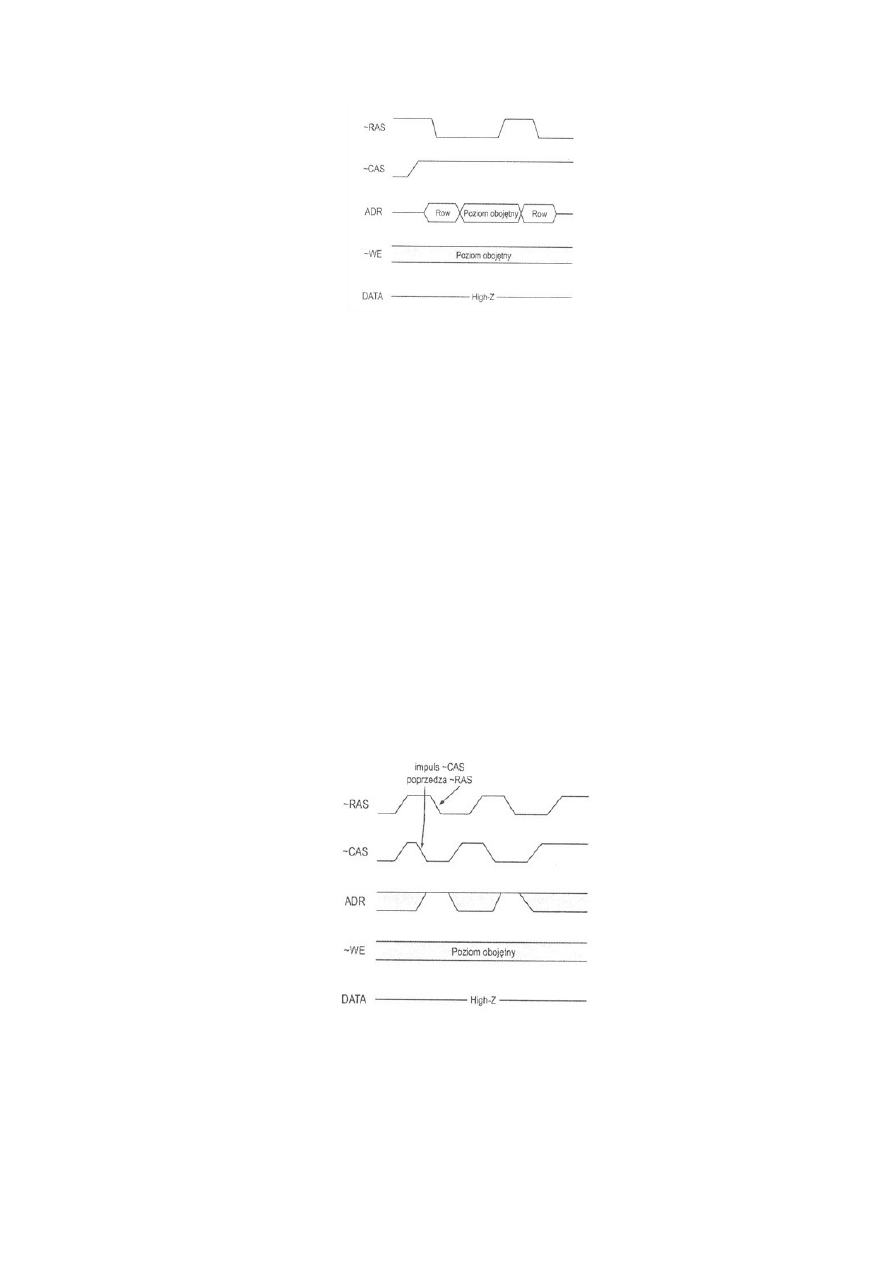

6.1 RAS Only

Odświeżanie w trybie RAS Only osiąga się poprzez podanie adresu na wejściu

adresowym i aktywowaniu linii ~RAS, odświeżaniu poddawane są wszystkie komórki

zaadresowanego wiersza. Jak długo sygnał ~CAS utrzymuje się na poziomie wysokim,

sterowniki wyjściowe odcinają układ od magistrali danych poprzez przejście w stan

wysokiej impedancji. Kontroler pamięci musi sam decydować o tym, aby w czasie

narzuconym przez wymiar cyklu wygenerowane zostały wszystkie adresy wierszy. Stan

linii adresowych zatrzaskiwany jest w rejestrze w momencie wykrycia opadającego

zbocza ~RAS. Cykle mogą łączyć się w pakiety.

24

25

Rys. 18 Odświeżanie w trybie RAS Only.

6.2 CBR (CAS Before RAS)

Odświeżanie w tym trybie jest najczęściej wykorzystywane. Jest to najprostsza

metoda a poza tym zapewnia oszczędność energii, jej skuteczność polega na tym, iż

adres aktualnie odświeżanego wiersza generowany jest we wnętrzu samego układu

pamięciowego. Sygnałem do wejścia w tryb odświeżania CBR jest wykrycie odwrotnej

kolejności adresowanych impulsów sterujących, pierwszy ~CAS a potem ~RAS,

normalny cykl dostępu do pamięci wygląda inaczej. Na początku podawany jest

fragment adresu identyfikujący wiersz (~RAS) a później uzupełnienie odnoszące się do

zadanych kolumn w chwili opadającej (~CAS). Możliwe jest łączenie cykli w pakiety.

25

26

Rys. 19 Odświeżanie w trybie CAS before RAS.

6.3 Hidden

Jest to tryb dołączenia cyklu CBR do zwykłego cyklu dostępu (odczytu lub

zapisu). Klasyczne wyjście z cyklu dostępu pozostawia adresowe sygnały kluczujące na

poziomie niskim: ~RAS = ~CAS = 0, następnie ma miejsce podniesienie sygnału ~RAS

i powrót do stanu początkowego. Przy zachowaniu odpowiednich uzależnień

czasowych właściwych dla danego układu, system rozpoznaje CBR i dokonuje

odświeżania. Korzyść jaką można osiągnąć pracując w tym osiąga się dowiązując

sekwencję CBR do cykli odczytu. Dzięki temu układ utrzymuje dane na końcach

wyjściowych w trakcie CBR.

Rys. 20 Odświeżanie w trybie Hidden.

7. Wykrywanie błędów i ich korekcja

Zjawisko przekazu informacji jest znane człowiekowi od zawsze, odwieczna

była także chęć zagwarantowania pewności tego przekazu. Sposoby na zabezpieczenie

przekazu były różne od samego faktu potwierdzenia przekazu typu „OK wiadomość

doszła” do odsyłania oryginału, tzw. echo. Mimo opracowania coraz to nowych i

lepszych metod wymiana danych nadal narażona jest na działanie różnych czynników.

Protokoły transmisyjne zabezpieczone są różnymi metodami zapobiegającymi

pojawieniu się błędów.

26

27

Informacje przechowywane w pamięci operacyjnej PC są również narażone na

wystąpienie błędów. Pamięci dynamiczne stosowane w komputerach nie dają 100%

pewności że dane nie będą przekłamane, źródła przekłamań można podzielić na dwie

grupy: błędy powtarzalne oraz błędy sporadyczne.

•

Błędy powtarzalne (HE)

Błędy te spowodowane są przez uszkodzenia układów elektronicznych lub połączeń

między nimi. Przykładem takiego błędu może być zwarcie w stopniu wyjściowym

jednego z buforów magistrali danych. Kostka pamięci wystawiona na takie działanie

daje zawsze sygnał o tym samym poziomie logicznym.

•

Błędy sporadyczne (SE)

Źródłem błędów tego rodzaju jest skutek promieniowania jonizacyjnego (głównie

α), emitowane przez zanieczyszczenia struktury krzemowej, izolacji oraz

promieniowanie kosmiczne. Czynni SER (Software Error Rate) określa

częstotliwość występowania błędów SE. Wraz z rozwojem technologii

komputerowej ilość błędów została poważnie zmniejszona i tak dawne komputery o

pojemności pamięci 1MB zbudowanej z kostek o pojemności 64KB, błędy SE

pojawiały się średnio co 120 godzin pracy. Natomiast w dzisiejszych komputerach

np. Z 128 MB pamięci SDRAM zbudowanej z kostek 16MB, błędy SE pojawia się

średnio co 8 lat ciągłej pracy. Jednak niedopracowana konstrukcja komputera PC

np. wyższa temperatura czy niedokładność wykonania oraz zawyżona częstotliwość

taktowania skraca czas bez wystąpienia błędu. Średnio ocenia się że statystyczny

komputer PC w warunkach normalnego użytkowania ulega jednemu błędowi SE na

rok nieprzerwanej pracy, nie jest to wartość zbyt wysoka ale dla przeciętnego

użytkownika PC wystarczająca.

8. DDR SDRAM

27

28

Pamięci DDR SDRAM przekazują w każdym takcie zegara dwa słowa danych.

Obecnie są dość popularne wykorzystywane są między innymi przez magistralę EV6

procesorów Athlon, karty graficzne AGP-2x oraz RAMBUS. Double Data Rate, czyli

technika przesyłania danych na obu zboczach sygnału zegarowego, pozwalająca na

podwojenie przepływności bez przyspieszania zegarów, stosowana jest obecnie w wielu

rozwiązaniach, w tym również w dynamicznych pamięciach DDR SDRAM. Pamięci

DDR są obecnie najtańszym z rozwiązań, pozwalających na zwiększenie przepływności

pamięci RAM, z 800 MB/s w PC100 do 2,1 GB/s w PC266. Testy wydajnościowe

Rys. 21 Porównanie prędkości pamięci SDRAM, RDRAM i DDR.

najnowszych konstrukcji nie pokazują jednak, by zwiększenie przepływności pamięci

RAM przynosiło znaczący wzrost wydajności. Zwłaszcza w przypadku procesora

Pentium III trudno się dopatrzyć tego, aby pamięci DDR dawały jakąkolwiek korzyść.

Dysproporcja między przepływnością pamięci RAM a wydajnością współczesnych

procesorów jest ogromna: pracujący w trybie SIMD procesor Pentium III jest w stanie

wygenerować w jednym cyklu pracy cztery 32-bitowe wyniki operacji. A procesor

pracuje z blisko dziesięciokrotnie szybszym zegarem niż pamięć RAM. Chwilowe

spiętrzenia danych buforowane są co prawda przez system pamięci podręcznych cache,

jednak potrzebę pamięci o większej przepływności widać wyraźnie. Przyspieszenie

zegara pamięci SD-RAM byłoby najlepszym rozwiązaniem, gdyż oprócz zwiększenia

przepływności przyniosłoby również skrócenie opóźnień przesłań danych. Pamięci

28

29

DDR SDRAM, podobnie zresztą jak pamięci Rambus, stworzono głównie na potrzeby

grafiki, domagającej się możliwie dużej przepływności. "Konkurencyjną" dla DDR

SDRAM miała być architektura pamięci Rambus DRAM, pozwalająca na uzyskanie

przepływności 1,6 GB/s, jednak duże opóźnienia transmisji w tej architekturze "zjadają"

praktycznie cały zysk, osiągany dzięki większej przepływności. W przypadku pamięci

DDR SDRAM problem opóźnień przesłań pozostaje nie zmieniony w stosunku do

klasycznych pamięci SDRAM: opóźnienia i czasy dostępu do danych są praktycznie

takie same jak w pracujących w "pojedynczym" trybie pamięciach SDRAM. Ważnym

elementem współpracy procesora z pamięcią RAM jest, oprócz przepływności szyny

pamięci, także przepływność interfejsu FSB procesora. Maksymalna przepływność

szyny GTL+ procesora Pentium III to 1066 MB/s, przy taktowaniu FSB 133-

megahercowym zegarem. Taką samą przepływność zapewniają pamięci PC-133, zatem

transmisja danych pomiędzy procesorem a pamięcią odbywa się z maksymalną

osiągalną szybkością. Zwiększenie przepływności pamięci wcale nie pozwoli

procesorowi na transmisję szybszą niż umożliwia to jego interfejs. Nieco inaczej mają

się sprawy w przypadku Athlona. Interfejs EV6 tego procesora, pracujący ze 100- lub

133-megahercowym zegarem w trybie DDR, zapewnia teoretycznie taką samą

przepływność jak pamięci DDR SDRAM taktowane tym samym zegarem. Pełna

harmonia pamięci DDR pozwalają zatem Athlonowi na pracę z maksymalną

wydajnością. I rzeczywiście, w odróżnieniu od Pentium III, Athlon wyraźnie zyskuje w

testach, współpracując z pamięciami DDR. Zysk ten nie jest jednak aż tak duży, jakiego

użytkownicy PC oczekiwali. Rozwój kolejnych generacji mikroprocesorów oraz

zwiększenie częstotliwości taktowania wymusił na producentach wprowadzenie

nowych pamięci operacyjnych z zegarem o taktowaniu powyżej 133MHz. I tak

powstały dwa standardy: PC-2700 oraz PC-3200.

•

PC-2700 taktowanie zegara o częstotliwości do 166MHz, przepustowość

magistrali do 2,7GB/s

•

PC-3200 taktowanie zegara o częstotliwości do 200MHz, przepustowość

magistrali do 3,2GB/s

Faktyczna wartość prezentowanych kości jest jednak daleka od teoretycznych założeń,

wartości zależą w dużej mierze od chipsetu i jego zdolności do implementacji protokołu

magistrali. Producenci wprowadzali również wiele jeszcze szybszych pamięci lecz nie

uzyskały one aprobaty rynku np. PC-4200.

29

30

Systemy dwukanałowe – niektóre z chipsetów np. NVIDIA nForce2 czy Intel E7205

akceptują systemy dwukanałowe, które wymagają obecności dwóch modułów DDR.

Maksymalne teoretyczne pasmo systemów DDR zależy od kombinacji częstotliwości

taktowania i szerokości magistrali. Jednakże wykorzystanie tej technologii w dużym

stopniu zależy od architektury całego komputera, jego procesora i płyty głównej.

Kolejnym krokiem do coraz szybszego taktowania pamięci operacyjnej jest DDR2

SDRAM. Istotą działania tych kości jest to iż mogą przesyłać nie 2 bity danych lecz aż

4 bity danych w jednym cyklu. Podyktowane jest to dwukrotnym obniżeniem

częstotliwości pracy układów pamięci. Dwustu megahercowym zegarem taktowany

jest tylko blok interfejsu, sama pamięć pracuje na połowie tego co interfejs. Niestety

pamięć DDR2 będzie sprawną i szybką modułem dopiero kiedy będzie możliwe

korzystanie z modułu PC-6400 o częstotliwości zegara 400MHz. Mniejsza

częstotliwość pracy modułu wymusza obniżenie poziomu zasilania układu pamięci

zamiast 2,5V do 1,8V.

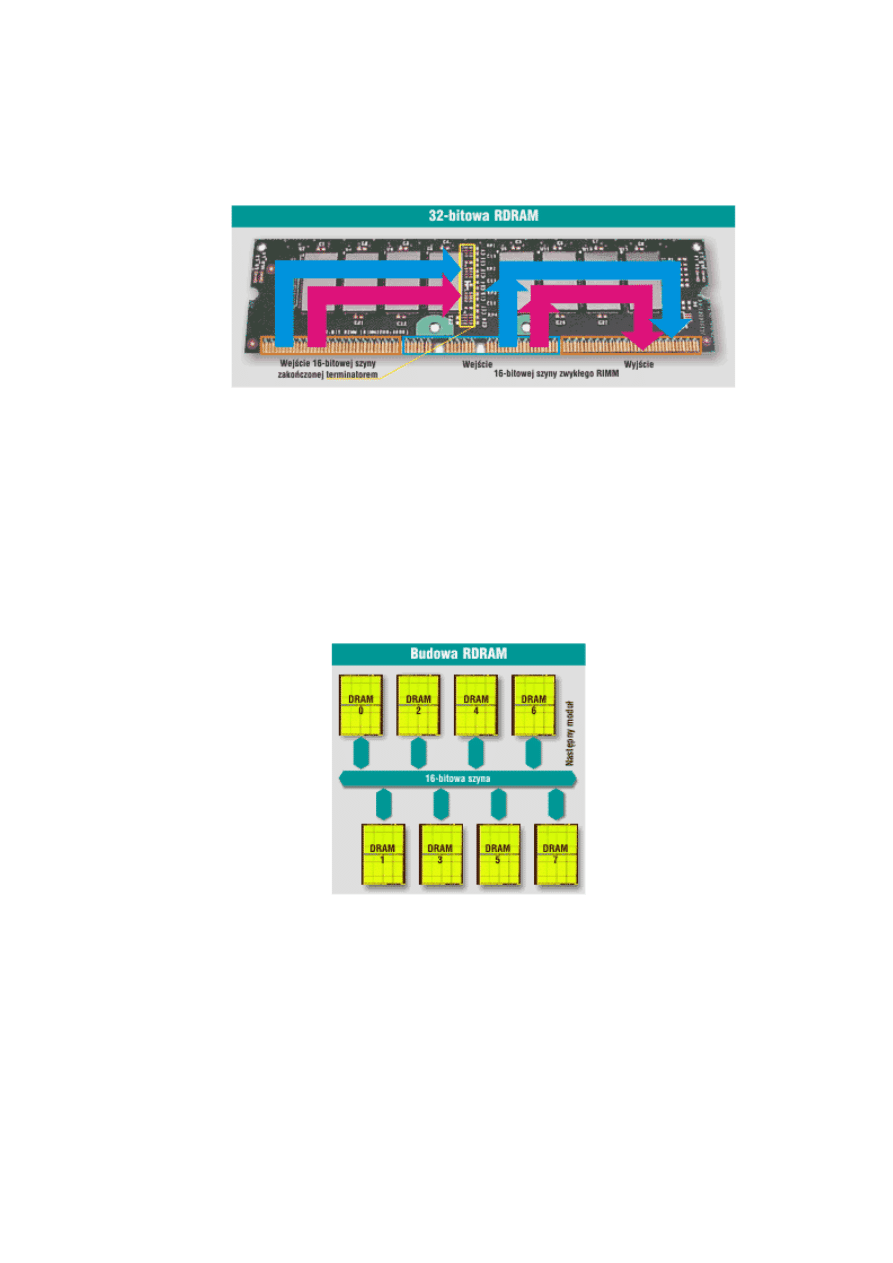

9. RDRAM

Technologia RDRAM (Direct Rambus DRAM) opracowany i opatentowana

została przez firmę RAMBUS. Miało to negatywny wpływ na rozwój tej technologii

ponieważ inni producenci musieli uiszczać opłatę licencyjną. Obecnie dostępne są trzy

standardy Base, Concurrent oraz Direct. Standardy Base oraz Concurrent stosuje się w

stacjach roboczych oraz w konsolach Nintendo 64. Ostatni standard jest dostępny dla

użytkowników PC. Wewnętrzna konstrukcja nie różni się w dużym stopniu od zwykłej

pamięci SDRAM ma tylko nieco inną organizację. Cechą która najbardziej różni

RDRAM od innych typów pamięci to pakietowy tryb pracy, którego początek stanowi

kontroler RAMBUS we wnętrzu chipsetu, zamiast jednej matrycy DDRAM, w układzie

RDRAM umieszczono aż osiem niezależnych matryc, dołączonych do wspólnej szyny i

odczytywanych po kolei. Pozwoliło to na pracę z wręcz gigantyczną częstotliwością

zegara szyny pamięci (ośmiokrotnie wyższą od zegara pamięci SDRAM o takim samym

czasie dostępu) i obiecywało proporcjonalną do częstotliwości zegara przepływność.

Nie bez znaczenia były również dodatkowe możliwości, uzyskiwane dzięki podziałowi

matrycy pamięci – najistotniejszą z nich stanowi możliwość równoczesnego

utrzymywania kilku (do ośmiu) otwartych stron pamięci (zaadresowanych wierszy

matryc). Możliwość taka znacznie usprawnia proces odczytu dzięki temu, że

przeważająca część odczytów danych następuje z już otwartych stron. Bardzo

30

31

obiecująca architektura okazała się jednak obarczona licznymi wadami. Wysoka

efektywna częstotliwość transmisji w szynie pamięci pociągnęła za sobą konieczność

zredukowania jej szerokości do zaledwie 16 bitów, czterokrotnie mniej niż w przypadku

pamięci SDRAM i DDR SDRAM. Dla uzyskania przepływności, która mogłaby

Rys.22 Przykładowy wygląd pamięci RDRAM.

rywalizować z przepływnością DDR SDRAM, konieczne jest więc stosowanie dwu

równoległych szyn pamięci. Ponadto protokół komunikacji pomiędzy RDRAM i

procesorem wnosi bardzo duże opóźnienie przesłań, które w większości typów aplikacji

niweczą korzyści uzyskiwane dzięki ogromnej przepływności.

Rys. 23 Budowa RDRAM.

Pamięć RAMBUS okazała się zbyt kosztowna w stosunku do standardowych pamięci

DDR SDRAM a ich zastosowanie jako pamięci RAM w PC nastręcza nieoczekiwanych

trudności co spowodowało przegraną rywalizacje rynkową. Jednak ten typ pamięci jest

produkowany i używane w np. kartach graficznych od przeszło dwu lat.

31

32

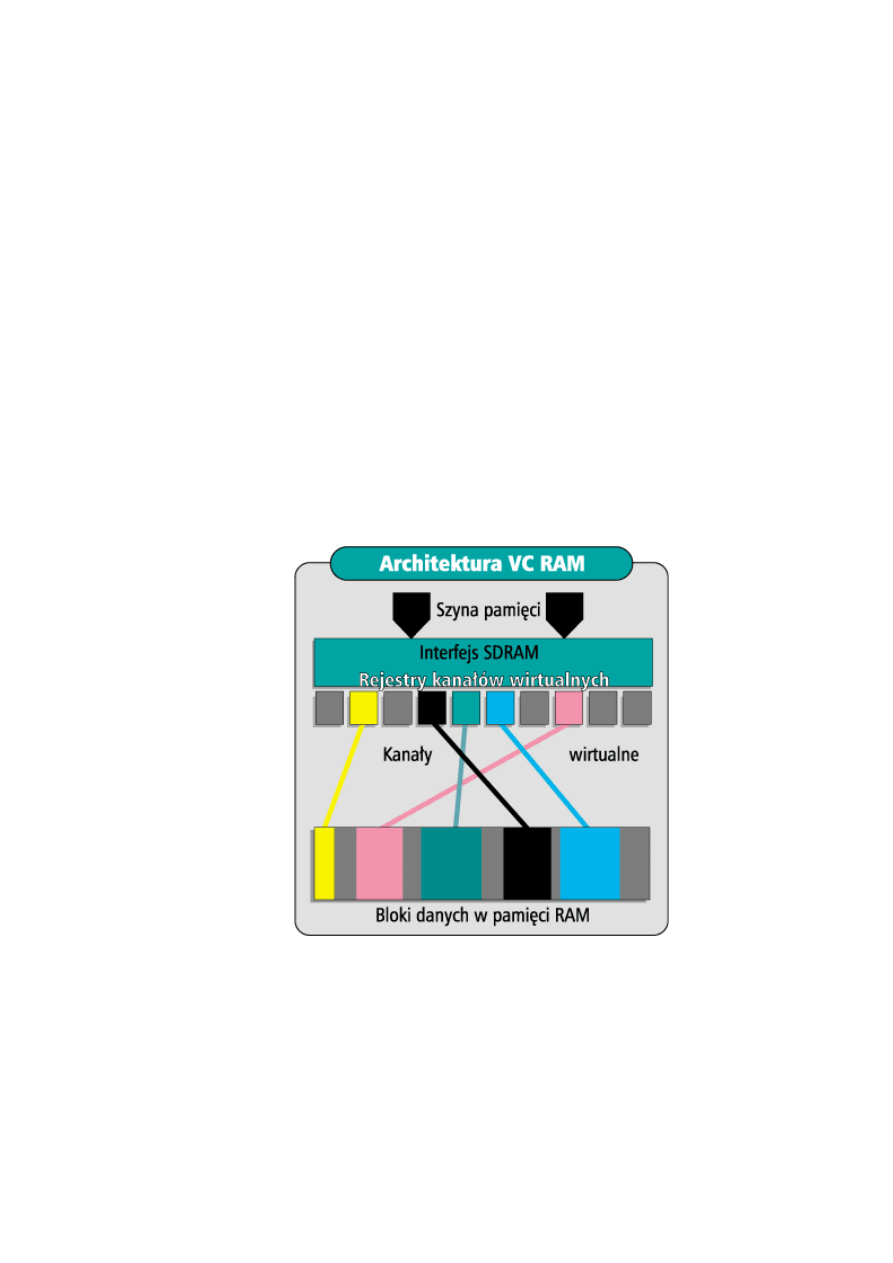

10. VC-SDRAM

Po pamięciach RAMBUS i DDR SDRAM kolejną propozycję, już dostępną na

rynku, stanowią układy Virtual Channel. VC-SDRAM były promowane przez firmę

NEC, jednakże nigdy nie uzyskały powszechnej akceptacji i zniknęły z rynku. Rozwój

architektury komputerów spowodował szereg zmian. Cały czas rośnie liczba urządzeń,

które mogą komunikować się bezpośrednio z pamięcią. Taki dostęp mają np. dodatkowe

procesory, układy AGP, kanały DMA lub kontrolery graficzne. Zmienił się również

proces przetwarzania aktualnych programów, procesor musi wybiegać daleko poza

aktualnie przetwarzany obszar i śięgać po partie kodu, które nie zostały jeszcze

sprowadzone do pamięci podręcznej. Styl programowania preferuje implementację

daleko idącej wielozadaniowości i wielowątkowości a systemy operacyjne stają się

coraz bardziej złożone. Do pamięci RAM w systemie komputerowym odwołuje się nie

tylko procesor – występują również przesłania danych pomiędzy RAM a urządzeniami

peryferyjnymi przez szynę PCI, a także, zwłaszcza w grach, liczne przesłania dużych

bloków danych pomiędzy RAM a podsystemem graficznym. Taki sposób korzystania z

pamięci SDRAM powoduje nieuchronnie znaczące straty w przepustowości. Każde

spośród korzystających z pamięci urządzeń pracuje niezależnie od pozostałych, stąd

możliwość częstych kolizji, a co za tym idzie – konieczność oczekiwania na dostęp do

pamięci. Dane, wymieniane z pamięcią przez poszczególne urządzenia, zlokalizowane

są w różnych jej obszarach, co dodatkowo pogarsza efektywność, ze względu na

konieczność częstego przełączania pomiędzy stronami i bankami pamięci. Takimi

właśnie „władcami pamięci” (ang. memory masters) są, oprócz procesora, szyny AGP i

PCI, a właściwie dołączone do nich urządzenia. Każde z urządzeń korzystających z

pamięci to memory master, używający fragmentu RAM i przesyłający w określonym

przedziale czasu bloki danych o określonej długości, wykonujący pewną liczbę ciągłych

połączeń z pamięcią. A taka klasyfikacja daje podstawę do uporządkowania. Istotę

rozwiązania Virtual Channel SDRAM stanowi przypisanie każdemu z korzystających z

pamięci urządzeń memory master, wirtualnego kanału do komunikacji z używanym

przez to urządzenie obszarem pamięci. Dla każdego kanału są definiowane:

-urządzenie

memory

master,

-zakres

adresów

RAM,

-wielkość

przesyłanego

bloku

danych,

-ilość

ciągłych

dostępów,

32

33

-czas

ważności

kanału.

Tak sformalizowane opisy kanałów umożliwiają stosunkowo łatwą ich realizację

praktyczną. W tym celu układy pamięci zostały wyposażone w szybkie, 128-bitowe

rejestry statyczne, pełniące rolę buforów kanałów. Matryca pamięci jest obsługiwana za

pośrednictwem 16 takich rejestrów, a konieczna logika zarządzania musi zostać

wbudowana

w

chipset

płyty

głównej.

Wirtualne kanały nie są oczywiście przyporządkowywane na stałe do poszczególnych

urządzeń memory master. Organizacja kanału trwa zaledwie jeden cykl zegara pamięci,

przy pierwszym dostępie do danego obszaru – dla późniejszych przesłań wirtualny

kanał jest „przezroczysty”, z tą jedynie różnicą, że transmisja danych występuje bez

charakterystycznych dla SDRAM wstępnych cykli oczekiwania, tj. w trybie 1-1-1-1,

zamiast jak dotychczas np. 3-1-1-1. Ważne jest, że nawet przy niekolejnych adresach

wewnątrz bloku obsługiwanego przez wirtualny kanał nie są potrzebne wstępne cykle

oczekiwania – skraca to znacznie średni czas dostępu do danych, pozwalając na

Rys. 24 Architektura VC-RAM

zwiększenie wydajności systemu. Według NEC pamięci VC-SDRAM pozwalają na

zwiększenie efektywnej przepływności podsystemu pamięci o 90%, ale jest to,

oczywiście, zależne od charakteru aplikacji i od tego, w jaki sposób korzystają z

pamięci wykorzystywane w tej aplikacji urządzenia memory master. Skrócenie

33

34

średniego czasu dostępu do danych o ok. 30%, w stosunku do typowych pamięci

SDRAM, to tylko jeden ze sposobów, w jaki pamięci VC-SDRAM mogą przyspieszyć

działanie komputera. Drugim, bardziej istotnym, jest „porządkowanie” w wirtualnych

kanałach przepływu danych pomiędzy pamięcią a resztą systemu, pozwalające na pełne

wykorzystanie przepustowości szyny pamięci. Trzeba bowiem zwrócić uwagę na fakt,

że maksymalne możliwe wykorzystanie przepustowości szyny pamięci, jakie

zapewniają stosowane obecnie pamięci SDRAM, to zaledwie 2/3 jej teoretycznej

przepływności, w praktyce zaś jest dużo gorzej – wykorzystywana jest zaledwie nieco

ponad 1/3 przepustowości. Zastosowanie VC SDRAM pozwala na wykorzystanie

przepływności szyny pamięci w blisko 90%. To naprawdę wiele, zwłaszcza że

technologia Virtual Channel, w odróżnieniu od DDR SDRAM, nie wymaga

przyspieszania działania samej matrycy pamięci, a co za tym idzie, tylko w niewielkim

stopniu podnosi koszt produkcji. Obsługę nowych pamięci zaimplementowano w

chipsetach VIA: Apollo Pro 133 i Apollo KX-133. Niestety pamięć VC-SDRAM nie

uzyskała aprobaty producentów sprzętu komputerowego i nigdy nie została

wykorzystana na masową skalę przez użytkowników PC.

11. HSDRAM

Pamięci HSRAM (High Speed DRAM) produkowane były przez firmę EMS

(Enhanced Memory System) należącą do przedsiębiorstwa Ramtor. Oprócz tego firma

EMS oferuje jeszcze dwa typy pamięci ESDRAM oraz EDRAM. Integracja pamięci

SDRAM wymagała pewnych zmian w architekturze SDRAM, zmiany polegały na

skróceniu parametru TAC, który dla pamięci HSDRAM wynosił tylko 4,6ns gdy dla

PC-100 – 6ns a PC-133 – 5,4ns. Znacznemu skróceniu uległ czynnik TRCD (RAS to

CAS Delay) i TRP (RAS Prechenger Time). Moduł HSRAM był w 100% kompatybilny

z innymi modułami SDRAM i pasował do tego samego 168-końcówkowego gniazda.

Mógł więc z pewnością umieszczany tam gdzie inne moduły SDRAM PC-100 oraz

PC-130. Ale aby wykorzystać jego szybkość konieczne jest posiadanie płyty głównej z

odpowiednim chipsetem. Tak jak moduły VC-SDRAM tak i moduły HSDRAM mimo

nowatorskiej technologii nie doczekał się popularyzacji.

34

35

12. Najnowsze moduły pamięciowe oraz ich rozwój w przyszłości - podsumowanie

Współczesne kości pamięci rozwijają się bardzo szybko i wkrótce używane

przez większość pamięci DDR SDRAM zostaną wyparte przez nowsze i bardziej

wydajne moduły. Na dziś za pretendenta uważa się pamięci DDR2, mimo iż w

pierwszych testach i opiniach pamięci te wypadały gorzej od swych poprzedników.

Wraz z pojawieniem się układu Intel 925XE z FSB 1066 MHz (4 x 266 MHz), w

wypadku której pamięci DDR2 533 MHz taktowane są synchronicznie (1:1), logiczne

wydawało się wykorzystanie modułów DDR2 667 MHz. Mimo że organizacja JEDEC

odpowiedzialna za standardy pamięci zatwierdziła oficjalnie kości DDR2-PC5300 (667

MHz), Intel nie zdecydował się na uwzględnienie ich w specyfikacji nowego chipsetu.

Okazuje się jednak, że również procesory z szyną FSB taktowaną zegarem 800 MHz

mogą skorzystać z możliwości nowego chipsetu i szybszych kości. Ostatnie testy

nowych kości pokazują, że DDR2 szybko może się stać dominującym standardem,

szczególnie na rynku najbardziej wydajnych komputerów PC. Niestety firma AMD,

której procesory Athlon 64 wyposażone są we wbudowany kontroler pamięci, do tej

pory nie zdecydowała się na produkcję układów współpracujących z modułami DDR2.

Decyzję o podjęciu tego kroku przesunięto na rok 2006. Wiele firm zapowiada, że nowe

układy będą osiągały prędkość powyżej 800MHz a po podkręceniu nawet 1GHz. .Po

opanowaniu i zoptymalizowaniu procesu wytwarzania modułów DDR2 ich ceny spadły,

a wydajność wzrosła. Jednak czy kości te zyskają akceptację większości producentów i

użytkowników pokaże czas. W przyszłości mają być wprowadzone nowe kości z

nowego standardu DDR3, będą początkowo produkowane w technologii 90 nm. Po

uruchomieniu masowej produkcji zostanie wdrożony proces technologiczny 70 nm.

Producenci informują, że początkowo prędkość przetwarzania danych w układach

DDR3 będzie wynosiła 1067 megabitów na sekundę, by wzrosnąć do 1600 Mb/s.z

Najnowsze pamięci mają działać szybciej i odznaczać się mniejszym zapotrzebowaniem

na energię. DDR3 ma być dwukrotnie bardziej wydajne od swych poprzedników. Nad

DDR3 pracują inżynierowie Samsunga oraz Infineon, a przedstawiciele Intel mówią, że

w 2007 roku będzie on sprzedawał platformę wykorzystującą nową generację DDR-ów.

Ale czy DDR3 jak i DDR2 stanie się tak popularny i tak masowo używany zweryfikuje

rynek oraz możliwości przeciętnego użytkownika współczesnego komputera.

35

36

13. Literatura

[1]

Piotr Metzger, Anatomia PC WydanieIX, Helion, Gliwice 2004.

[2] Zdzisław Kolan, Urządzenia techniki komputerowej, Centrum Wdrożeń

Komputerów „SCREEN”, Wrocław 2001.

[3] Maciej Wieńszczak , Komputer Świat Ekspert, 03/2004, 20-27.

[4] Wojciech Kiełt , Komputer Świat Ekspert, 06/2003, 23.

[5] Piotr Lisowski , Komputer Świat Ekspert, 05/2005, 28-32.

[6] http://www.komputerswiat.pl/ - pamięci RAM.

[7] UTK

http://members.lycos.co.uk/angelshaven/

- pamięci RAM.

- pamięci RAM.

- pamięci RAM.

- pamięci RAM.

[11]

http://www.kingston.com/plroot/

- pamięci RAM.

36

Document Outline

Wyszukiwarka

Podobne podstrony:

Pami c4 99ci RAM

Pami c4 99 c4 87 RAM

Sezonowość, Studia UMK FiR, Licencjat, II rok - moduł Rachunkowość, Ekonometria M.Osińska (w) J.Kwia

Ekonometria kolokwium 1, Studia UMK FiR, Licencjat, II rok - moduł Rachunkowość, Ekonometria M.Osińs

ekonometria-zadania-ODPOWIEDZI, Studia UMK FiR, Licencjat, II rok - moduł Rachunkowość, Ekonometria

Ekonometria - wykład dot. funkcji Cobba-Douglasa, Studia UMK FiR, Licencjat, II rok - moduł Rachunko

pyatnia-z-egzaminu-ekonometria, Studia UMK FiR, Licencjat, II rok - moduł Rachunkowość, Ekonometria

2 Realizacja pracy licencjackiej rozdziałmetodologiczny (1)id 19659 ppt

kwiatKi 2

Gatunki dziennikarskie licencjat PAT czesc 2

PamiŕŠ

III ROK licencjackie

Praca licencjacka

Dyplom (kwiatki)

praca licencjacka K Siek

podmioty rynku pienięznego, studia licencjackie administracja I semestr

Ze wszystkich kwiatków świata, dzień mamy i taty

więcej podobnych podstron