1. Podać i omówić przeznaczenie rejestrów procesora.

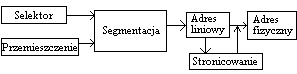

Selektor – pole bitowe, max 16 bitów. Umieszczony w rejestrach segmentowych, wskazuje

8086 – 14 rejestrów (80486 + 2 rejestry GS i FS)

deskryptor w tablicy deskryptorów.

4 rejestry ogólnego przeznaczenia (16 bitowe):

Deskryptor – rekord 64 bitowy opisujący położenie segmentu w pamięci w 4GB pamięci (32

AX = AH+AL – akumulator, wykorzystywany głównie do operacji arytmetycznych i logicznych. bitowa baza), jego wielkość (20 bitowy rozmiar) i inne własności segmentu (16bitowe BX = BH+BL - rejestr bazowy do adresowania pamięci.

atrybuty).

CX = CH + CL – rejestr zliczający, wykorzystywany jako licznik.

Przemieszczenie – max. 32bity.

DX = DH + DL - rejestr danych, używany przy operacjach wysyłania i odbierania danych z Adres liniowy – 32 bitowy adres tworzony wg formuły: baza z deskryptora wskazanego przez portów we/wy.

selektor + przemieszczenie. Jest to odpowiednik adresu logicznego z trybu rzeczywistego.

Rejestry indeksowe:

Adres fizyczny – powstaje z adresu liniowego w procesie stronicowania, 32 bitowy.

SI – indeksuje pamięć, oraz oraz wskazuje na obszar, z którego przesyła się dane.

Podobieństwa i różnice:

DI – indeksuje pamięć, oraz wskazuje na obszar, do którego przesyła się dane.

O ile algorytmy tworzenia adresu fizycznego wyglądają podobnie na schematach to jednak

Rejestry wskaźnikowe:

istnieje wiele różnic. Tryb chroniony ma dodatkowo wiele udogodnień.

SP – wskaźnik stosu, obsługujący stos (zapis/odczyt stosu).

Tryb rzeczywisty

Tryb chroniony

BP – rejestr bazowy, używany dla pewnych operacji na stosie, np. przy pobieraniu informacji Adres fizyczny 20 bitowy, 1MB pamięci.

Adres fizyczny 32 bitowy, 4GB pamięci.

przekazywanych przez stos.

SEGMENT wskazujący bezpośrednio na Selektor wskazujący na segment pośrednio,

Rejestry segmentowe, służą do adresowania pamięci operacyjnej:

CS – rejestr segmentu kodu, wskazuje początek segmentu kodu. Wraz z rejestrem IP tworzy początek segmentu.

poprzez deskryptor.

pełen adres logiczny.

Segment max. wielkości 64kB.

Segment dowolnej wielkości.

DS – rejestr segmentowy danych, wskazuje początek segmentu danych.

Brak stronicowania.

Stronicowanie umożliwiające odwoływanie się

SS – rejestr stosu, wskazuje początek segmentu stosu.

do większej ilości pamięci operacyjnej.

ES – rejestr dodatkowy, wskazuje dodatkowe segmenty danych.

Brak obsługi wielozadaniowości.

Obsługa wielozadaniowości.

Wskaźnik rozkazów:

Brak ochrony zasobów na poziomie sprzętu.

Ochrona zasobów na poziomie sprzętu.

IP – rejestr ten jest wskaźnikiem rozkazów i wraz z rejestrem CS adresuje kolejne rozkazy do Procesor działa w tym trybie po uruchomieniu. Procesor działa w tym trybie dopiero po wykonania.

przejęciu kontroli przez system operacyjny.

Rejestr znaczników FLAGS:

Rejestr znaczników, rejestr rejestr stanu, rejestr flagowy, to 16bitowy rejestr służący do

informowania o różnych cechach wykonywanych operacji logicznych i arytmetycznych. Jego 5. Stronicowanie.

bity mogą informować o takich rzeczach jak: parzystość (PF), przeniesienie (CF), przeniesienie To mechanizm dzielący pamięć na strony (zwykle 4kB) i dokonujący transferu stron pomiędzy pomocnicze (AF), czy jest zerem (ZF), znak liczby (SF), nadmiar (OF), praca krokowa (TF), pamięcią operacyjną, a dodatkowym magazynem do ich przechowywania np. dyskiem zezwolenie na przerwanie (IF), kierunek zmian (DF).

twardym. Główną zaletą tego mechanizmu jest łatanie dziur w pamięci stronami, które są

najmniejszymi niepodzielnymi blokami. Problem może być rozłożony na strony, a nie wrzucany

2. Omów poszczególne bloki w budowie procesora.

do pamięci jako jeden blok.

Mikroprocesor to układ cyfrowy zdolny wykonywać operacje arytmetyczno-logiczne w sposób Pamięć dzielona jest na bloki 4kB zwane stronami. Gdy program odwołuje się do pamięci to programowalny (wg dostarczonego ciągu instrukcji). Zawiera on następujące, podstawowe adres komórki tej pamięci jest opisany za pomocą adresu liniowego jednoznacznie zespoły funkcjonalne:

wyznaczającego adres fizyczny.

ALU – układ arytmetyczno-logiczny, służący do wykonywania działań arytmetycznych i Katalog w adresie liniowym wskazuje na element w katalogu tablic. Następnie element logicznych.

katalogu wskazuje na tablicę stron, a adres liniowy wyznacza element z tej tablicy stron.

Szyna danych – od 8 do 64 bitów, co najmniej 3 przewody, przekazująca dane do pamięci Element tablic stron wskazuje na nr strony w pamięci. Następnie najmłodsze 12 bitów z operacyjnej.

adresu liniowego wskazuje na adres w obrębie danej strony.

Szyna adresowa – od 16 do 64 bitów, przekazująca adres do/z pamięci operacyjnej.

Rejestr sterujący CR3 wskazuje na początek katalogu stron. Ma też dodatkowo atrybuty

Szyna sterująca – kontroluje przesyłanie informacji między CPU i pamięcią.

zapamiętujące strony w pamięci podręcznej i głównej.

Dekoder instrukcji – dekoduje dostarczone procesorowi instrukcje i steruje pozostałymi

blokami.

6. Selektor.

Rejestry – komórki pamięci umieszczone wewnątrz procesora, służące głównie do Selektor to jedna z dwóch składowych (obok przemieszczenia), które w procesie segmentacji przechowywania danych lub adresów. Niektóre ważne rejestry to: akumulator – przechowuje tworzą adres liniowy w trybie chronionym pracy procesora. Przechowywany jest w rejestrach wyniki działań ALU; licznik rozkazów – wskazuje na adres komórki zawierającej następny segmentowych (CS, DS, SS, ES). Jest to pole bitowe przyjmujące wartości 0...FFFFh, z czego rozkaz do wykonania.

kilka bitów to pewne atrybuty (TI – czy tablica deskryptorów lokalna czy globalna, RPL –

Zegar – zespół dostarczający procesorowi sygnały o określonej częstotliwości (taktowanie). mechanizm ochrony), a pozostałe wyznaczają indeks w tablicy deskryptorów. Selektor jest Procesor wykonuje operacje w rytm zegara.

więc wskaźnikiem na pewien deskryptor (opisującego położenie i wielkość segmentu). Dopiero

w deskryptorze zawarty jest właściwy adres (baza), który po dodaniu do niego

3. Kodowanie w alfabetach stron kodowych.

przemieszczenia tworzy adres liniowy.

Danej ilości bitów odpowiada konkretna litera alfabetu lub znak pisarski. Najczęściej używane

kodowania to:

7. Deskryptor.

1 Deskryptor to rekord w tabeli deskryptorów przez selektor, wykorzystywany do tworzenia 2

ASCII = ISO646, 1 znak na 7 bitach, 128 znaków (32 specjalne, kontrolne; 96 pisarskie); ISO adresu liniowego. Deskryptor opisuje własności segmentu takie jak jego położenie w pamięci, 8859-1÷15 (2 - "latin 2", polskie znaki), 1 znak na 8 bitach; ISO 10646 = UNICODE v.4 – ok. 14 rozmiar.

tys. znaków (65 tys. możliwość), 1 znak na 16 bitach; UTF-8 - uniwersalny format transmisyjny. Baza – opisuje adres początku segmentu w 4GB pamięci.

ASCII, jest to 7bitowy kod przyporządkowujący liczbom z zakresu 0-127 litery (alfabetu Ang.), Rozmiar – opisuje wielkość tego segmentu.

cyfry, znaki przestankowe, symbole i inne polecenia sterujące.

Atrybuty – opisuje dodatkowe własności takie jak: ziarnistość, typ deskryptora,

- 95 znaków drukowanych o kodach 32-126

uprzywilejowanie, domyślny obraz operacji, pole dodatkowe.

- 33 pozostałe (0-31, 127) to kody sterujące.

Deskryptor może leżeć w lokalnej lub globalnej tablicy deskryptorów. Są one wskazywane

ASCII jest 8 bitowe, a że większość komputerów operuje na 8 bitach pozostaje możliwość przez rejestry systemowe LDTR i GDTR.

rozszerzenia zbioru znaków. Tym sposobem powstało m. in. strony kodowe, ISO 8859.

Strona kodowa – przyjęty sposób na przypisanie poszczególnym kodom binarnym różnych 8. Rejestry GDTR i LDTR (do czego służą).

znaków pisarskich.

Rejestry te służą do wskazywania na tablice deskryptorów w trybie chronionym.

ISO/IEC 8859 to zestaw standardów służących do kodowania znaków 8 bitowych: 0-127 znaki Rejestr GDTR (48bitów) – wskazuje gdzie leży globalna tablica deskryptorów (GDT) w ASCII; 128-159 kody sterujące. Polskie znaki: ISO 8859-2 (Polska norma); 8859-13 i 8859-16 pamięci (32bity) i jaką ma wielkość (16bitów).

zawierają poprawne znaki, których brak w 8859-2.

Rejestr LDTR (16bitów) – to selektor, który wskazuje, gdzie w GDT leży wskaźnik na LDT.

CP852 (DOS Latin-2, DOS 5.0-1991r.)

Kodowanie 8 bitowe używane w systemach: - MS-DOS; - PC-DOS; - DR-DOS; - Free-DOS.

9. Selektor a deskryptor (różnice).

W zamyśle zawierające znaki języków Europy Wschodniej opartych o alfabet łaciński. Zawiera Selektor znajduje się w rejestrach segmentowych (CS, DS, SS, ES), jest wskaźnikiem na też polskie znaki.

deskryptor znajdujący się w tablicy deskryptorów. Selektor jest ponadto polem bitowym,

CP1250 (Windows-1250) Kodowanie (strona kodowa) używane przez system Microsoft wielkości 16 bitów, składającym się z atrybutów i indeksu w tablicy deskryptorów. Deskryptor Windows do reprezentacji tekstów w językach środkowoeuropejskich używających alfabetu wskazywany przez selektor to 64 bitowy rekord, składający się z: łacińskiego. Również zawiera polskie znaki.

- adresu bazowego (32bity), opisującego położenie segmentu pamięci w 4 GB pamięci,

Unicode Zestaw znaków w zamierzeniu mający obejmować wszystkie pisma używane na - rozmiaru (20 bitów) – wielkość tego segmentu, świecie. Unicode obejmuje przydział przestrzeni numerycznej poszczególnych grup - dodatkowych atrybutów (16bitów).

znakowych, nie obejmuje sposobu bajtowego kodowania znaków. Najważniejsza metoda

kodowania Unicode to: UTF-8.

10. Atrybuty adresowania (bezpośrednie, pośrednie, przykłady).

Adresowanie bezpośrednie – adres zakodowany jest bezpośrednio w instrukcji (po

4. Podobieństwa i różnice w segmentacji pamięci w trybie rzeczywistym i chronionym.

przecinku). Adresem tym może być nazwa rejestru lub identyfikator zawartości jakiejś komórki

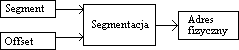

Segmentacja w trybie rzeczywistym:

pamięci, co ilustrują poniższe przykłady:

Prześlij zawartość BX do AX: mov ax,bx

Prześlij zawartość komórki, której OFFSET wynosi wynosi 7654d do AX: mov ax,[7654d]

Adresowanie pośrednie rejestrowe – adres znajduje się w rejestrze ogólnego

przeznaczenia. Przykład:

Prześlij do AX liczbę spod adresu [CX]: mov ax,[cx]

Adresowanie pośrednie bazowe i bazowe z przemieszczeniem – adres znajduje się w

rejestrze bazowym BX lub BP, lub jest sumą zawartości rejestru bazowego i wartości podanej

w instrukcji. Przykłady:

Prześlij do AX jakąś liczbę spod adresu DS:BX: mov ax,[bx]

Prześlij pod adres SS:BP liczbę z AX: mov [bp],ax

SEGMENT – adres początku segmentu właściwego rejestru segmentowego, 16 bitowy.

OFFSET – adres przesunięcia względem początku segmentu, 16 bitowy.

Prześlij do AX jakąś liczbę spod adresu DS:BX+1: mov ax,[bx+1]

Adresowanie pośrednie indeksowe i indeksowe z przeniesieniem – adres znajduje się

Adres logiczny – połączenie SEGMENTu i OFFSETu, zapisywany jako SEG:OFFS, 32 bitowy.

Adres fizyczny – adres, gdzie dane są przechowywane po przekazaniu ich do pamięci w rejestrze indeksowym SI lub DI, lub jest sumą zawartości rejestru indeksowej i wartości podanej w instrukcji. Przykłady:

operacyjnej (1MB), tworzony wg formuły: 16*SEG+OFFS, 20 bitowy.

Segmentacja w trybie chronionym:

Prześlij do AX jakąś liczbę spod adresu DS:SI: mov ax,[si]

Prześlij do AX jakąś liczbę spod adresu ES:DI+1: mov ax,[di+1]

Adresowanie pośrednie indeksowo-bazowe i indeksowo-bazowe z przeniesieniem –

adres jest sumą zawartości rejestru bazowego (BP lub BX) i indeksowego (SI lub DI) oraz

ewentualnego przeniesienia. Przykłady:

Prześlij do AX jakąś liczbę spod adresu DS:SI+BP: mov ax,[si+bx]

Prześlij do AX jakąś liczbę spod adresu SS:DI+BX+2: mov ax,[di+bp+2]

11. Program typu COM i EXE (porównanie struktury).

Program typu COM:

- Posiada jeden wspólny segment, CS=DS=SS=ES.

2 4

- Segment ma maksymalny rozmiar 64kB.

16. W jaki sposób procesor wykonuje obsługę przerwania sprzętowego.

- Początek w offset 100h.

Poprzez następujący fragment kodu:

- Zakończenie przez powrót do systemu.

obsluga PROC FAR

prog SEGMENT

STI

ASSUME cs:prog, ds:prog, ss:prog

...

ORG 0100h

MOV AL,020h

start: ...

OUT 020h,AL

mov AH,04Ch

IRET

int 021h

obsluga ENDP

prog ENDS

END start

17. Omówić budowę mechanizmu przerwań sprzętowych dostępnych w komputerze PC/AT,

Program typu EXE:

PC/XT.

- Osobne segmenty: CS:kod, DS:dane, SS:stos.

Istnieją dwa typy przerwań sprzętowych:

- Segment dowolnego rozmiaru.

NMI – przerwanie niemaskowalne, występują przy poważnym błędzie sprzętowym (zanik

- Początek w dowolnym miejscu.

napięcia, błąd parzystości RAM).

- Zakończenie prze powrót do systemu.

INTR – przerwanie maskowalne, pochodzą ze sterownika przerwań który zajmuje się

dane SEGMENT ;segment danych

przekazywaniem przerwań od urządzeń zewnętrznych (np. klawiatura, mysz, zegar) do

...

procesora.

dane ENDS

Przerwanie NMI nie może zostać zablokowane przez procesor. Związany jest z nim wektor 2

stos1 SEGMENT STACK ;segment stosu

(INT 2).

...

Przerwania sygnalizowane na INTR pochodzą ze sterownika przerwań zewnętrznych, tzw.

stos1 ENDS

PIC. Procesor może odmówić przyjęcia tych przerwań (jeśli flaga IF=0). PIC przekazując

prog SEGMENT ;segment kodu

procesorowi przerwanie podaje mu wektor tego przerwania. Informacje zwrotne od procesora

ASSUME cs:prog, ds:dane, ss:stos1

przekazywane są poprzez sygnał potwierdzający: INTA.

ORG 0h

start: ...

W komputerze PC XT znajduje się tylko jeden PIC (PIC I8259), do którego można połączyć 8

mov ah,04Ch

urządzeń (IRQ0...IRQ7). IRQ0 ma najwyższy priorytet, a IRQ7 najnizszy.

int 021h

prog ENDS

W komputerach typu PC AT używany jest układ PIC podłączony do INTR na procesorze, a do

END start

niego podłączony jest drugi PIC. Są więc dwa PIC o łącznej sumie 16 przerwań dla różnych

urządzeń. Linie IRQ wg priorytetu: IRQ0, IRQ1, IRQ8...IRQ15, IRQ3...IRQ7

12. Stos zrealizowany (obsługiwany) w procesorze iAPX86.

Stos to fragment pamięci przydzielonej dynamicznie przez programy, w której informacje są W komputerach PC ATX pojawiły się zaawansowane kontrolery przerwań: APIC oraz przechowywane i pobierane wg reguły: ostatnia wprowadzona informacja jest pierwszą dodatkowe linie zgłoszeń: PIRQ by dodatkowo zwiększyć wydajność mechanizmu przerwań.

informacją odczytywaną. Zatem stos rośnie w kierunku malejących adresów. Stos może

służyć do tymczasowego przechowywania pamięci, jest też wykorzystywany przez różne 18. Na czym polega tryb PIO pracy interfejsu ST506.

instrukcje. Elementy stosu mają wielkość 16bitów.

Transfer danych przy użyciu instrukcji in/out.

Rejestry związane ze stosem: SS – rejestr wskazujący segment stosu; SP – rejestr wskazujący Są tryby PIO-0,1,2,3,4, różniące się parametrami transmisji od 3.33 do 16.66 MB/s.

na szczyt stosu.

Najważniejsze instrukcje związane ze stosem:

19. Omówić poszczególne bloki funkcyjne płyty głównej komputera PC-AT.

PUSH xx ;połóż xx na stos

- Procesor

POP xx ;zdejmij xx ze stosu

- Koprocesor, pamięć podręczna

PUSHF ;wrzuć flagi 16 bitowe

- Pamięć operacyjna RAM: charakteryzuje się dużą pojemnością i małym poborem prądu,

POPF ;zdejmij flagi 16 bitowe

wymaga odświeżania.

PUSHFD / POPFD ;j.w. 32 bitowe

- Pamięć ROM: PROM, EPROM, EEPROM, Flash; w komputerach PC zawiera program SETUP

PUSHA ;wrzuć wszystkie rejestry 16 bitowe

- Elektronika wspomagająca

POPA ;zdejmij wszystkie rejestry 16 bitowe

- Interfejs: system umożliwiający przesyłanie informacji między urządzeniami,

PUSHAD / POPAD ;j.w. ale 32 bitowe

oprogramowany protokołem transmisji. Wyróżniamy interfejsy: - szeregowe, synchroniczne

Segment stosu w przypadku programu COM jest wspólny z innymi segmentami. W przypadku (np. USB); - szeregowe, asynchroniczne (np. RS232C); - równoległe (np. Centronics/IEEE1284, programu EXE można go zadeklarować w ten sposób:

SCSI); - Magistrala systemowa;

stos1 SEGMENT STACK

- Kontroler klawiatury: do obsługi klawiatury i myszki

dw 1024 dup(?)

- Układ CTC, do odmierzania czasu

stos1 ENDS

5

7

13. INT xxx i CALL xxx (różnice i podobieństwa).

20. Na czym polega idea płaskiego chronionego modelu pamięci?

CALL xxx

INT xxx

Płaski model pamięci "wyłącza segmentacje" - tzn. rejestry segmentowe ustawia się raz i nie

Argument xxx to adres procedury.

Argument xxx no numer wektora przerwań: trzeba ich ruszać. dostępne jest maksymalnie 4GB pamięci. Adresowanie zaczyna się od 0...255.

komórki o adresie 0. Mechanizm stronicowania który jest obecny w przypadku modelu

Odkłada na stos tylko adres IP (lub CS:IP).

Odkłada na stos FLAGS i adres CS:IP.

płaskiego, pozwala na sprzętową realizację pamięci typu swap (plik/partycja wymiany) -

jeden z bitów charakteryzujący stronę pamięci to bit który mówi czy ta strona jest

Po wykonaniu flagi mogą się zmienić.

Po wykonaniu flagi się nie zmienią.

rzeczywiście obecna - jeśli nie jest obecna a program próbuje odwołać się do tej pamięci,

Kończy się instrukcją ret (retn / retf).

Kończy się instrukcją iret.

generowany jest wyjątek, a obsługą tego wyjątku może być procedura obsługująca pamięć

Stos przed i po wykonaniu procedury jest taki Stos przed i po wykonaniu przerwania jest taki swap.

sam.

sam.

21. Na czym polega przetwarzanie potokowe.

14. Przerwania programowe, przerwania sprzętowe.

Przetwarzanie potokowe polega na równoległym przetwarzaniu danych. Każdy fragment

Najogólniej przerwania można rozumieć jako zbiór najczęściej używanych procedur danych przechodzi przez kilka bloków, aż osiągnie ostatni blok całego cyklu.

niezbędnych do pracy komputera.

Na ogół cykl składa się z 5 kroków:

1) Przerwanie programowe to pewna procedura przechowywana w pamięci. Wywoływanie PF – pobranie instrukcji,

przerwania w programie wstrzymuje kod aktualnie wykonywanego programu, następnie D1 – dekodowanie instrukcji: analiza kodu, program obsługi przerwań uruchamia procedurę przerwania. Każde przerwanie posiada swój D2 – dekodowanie instrukcji: obliczanie adresu argumentów, nr (0...255), który musimy podać jeśli chcemy je wywołać. Wywołujemy instrukcją: int xx. Nr EX – pobranie argumentów, ten jest wskaźnikiem na 4bajtowy adres pamięci zwany wektorem przerwań. Adres ten WB – zapisanie wyniku instrukcji.

ładowany jest do rejestru CS:IP i procedura zaczyna się wykonywać. Powrót do programu jest Liczba pięciu bloków sprawia, że w tym samym czasie może być obsługiwanych 5 instrukcji.

możliwy dzięki przechowaniu starego CS:IP na stosie. W trybie rzeczywistym wektory Zwiększa to znacznie efektywność działania procesora. Wykonanie całej instrukcji zajmuje 5

przerwań znajdują się w obszarze pamięci zwanym tablicą wektorów przerwań. Jest on okresów zegara, w każdym takcie zegara wykonywana jest jedna instrukcja w potoku.

zlokalizowany w pierwszym kilobajcie pamięci: od 0h do 3FFh. W trybie chronionym obszar

ten jest zwany tablicą deskryptorów przerwań, na którą wskazuje rejestr IDTR.

22. Przerwanie potokowe, a superskalarne (różnice).

2) Wyjątki, są to przerwania wywoływane przez procesor podczas napotkania różnorakich W przetwarzaniu potokowym instrukcje są pobierane, dekodowane i wykonywane tylko za błędów i niepowodzeń.

pomocą jednego potoku. Czyli wraz z każdym taktem zegara wykonywana jest jedna

3) Przerwania sprzętowe od programowych i wyjątków różnią się tym, że są wywoływane instrukcja.

przez sygnały płynące z urządzeń zewnętrznych w stosunku do procesora. Dzielą się na W przetwarzaniu superskalarnym mamy do czynienia z kilkoma, równolegle działającymi niemaskowalne (sygnał NMI) i maskowalne (sygnał INTR, programowalne).

potokami. Oznacza to, że kilka rozkazów jest wykonywanych w ciągu jednego taktu zegara.

Jest to możliwe dzięki zwielokrotnieniu jednostek wykonawczych.

15. W jaki sposób dokonuje się przerwań programowych.

By efektywnie działać, przetwarzanie superskalarne wymaga istnienia w procesorze

Jest ono dokonane w kilku krokach:

zduplikowanych podsystemów (np. dwóch ALU, podwójnej pamięci cache), z których każde

1) Zapamiętanie oryginalnego wektora.

mogłoby wykonywać rozkaz z przydzielonego mu potoku. Jednak nawet wtedy, niektóre

mov AH,035h

instrukcje (np. mogące zadziałać tylko po otrzymaniu wyniku z poprzedniej instrukcji) nie

mov AL,wektor

będą mogły być wykonane superskalarnie.

int 021h

mov [int_seg],ES

23. Fazy wykonania rozkazu (poszczególne kroki cyklu instrukcji).

mov [int_off],BX

Na ogół cykl dzielimy na 5 kroków:

I gdzieś w pamięci:

PF – pobranie instrukcji, do kolejki rozkazowej procesora dodawania jest instrukcja z pamięci

int_seg DW ?

podręcznej procesora.

int_off DW ?

D1 – dekodowanie instrukcji: analiza kodu, przedrostków, argumentów.

2) Ustawienie nowego wektora.

D2 – dekodowanie instrukcji: obliczanie adresu argumentów.

3) Wywołanie oryginalnego przerwania.

EX – pobranie argumentów, wykonanie instrukcji.

obsluga PROC FAR

WB – zapisanie wyniku instrukcji w określonym miejscu w pamięci lub rejestrze, dodatkowo

...

pewne ukryte rejestry procesora są ustawiane do stanu początkowego, a inne (FLAGS)

JMP old_addr

ustawiane zgodnie z wykonaną instrukcją.

obsluga ENDP

Przykład: mov ax,[bx]

4) Przywrócenie oryginalnego przerwania.

- faza PF – pobranie kodu instrukcji,

5) Rezydent segment kodu obsługi.

- fazy D1, D2 – określenie czynności do wykonania, obliczenie adresu efektywnego dla

start: ...

drugiego argumentu: (16xDS)+BX,

mov DX,offset end

- faza EX – dostęp do komórki pamięci o adresie (16xDS)+BX, operacja dodawania do AX,

INT 027h

- faza WB – umieszczenie wyniku w AX, ustawienie flag.

end EQU

6

8

24. Adres logiczny, fizyczny, liniowy.

36. Czego dotyczy i na czym polega różnica pomiędzy trybami pracy SPI a PS/2.

Adres logiczny – 32 bitowy adres tworzony w trybie rzeczywistym pracy procesora poprzez SPI (lub Centronics) umożliwia transfer tylko w jedna stronę w trybie simplex (do drukarki lub połączenie SEGMENTu i OFFSETu, ma postać SEG:OFFS. Adres fizyczny tworzony jest wg innego urządzenia), natomiast PS/2 (lub bitronics) umożliwia transfer w dwie strony w trybie formuły: 16*SEG+OFFS i ma 20 bitów.

polduplex, czyli możliwa jest transmisja raz w jedna, raz w druga stronę, ale nie w dwie

Adres liniowy – 32 bitowy adres tworzony w trybie chronionym pracy procesora poprzez jednocześnie. W trybie PS/2 jest tez możliwa obsługa za pomocą przerwań.

połączenie Selektora i Przemieszczenia wg formuły: baza z deskryptora wskazanego przez

selektor + przemieszczenie. Adres fizyczny tworzony jest z adresu liniowego w procesie 37. Różnice miedzy SPI i EPP.

stronicowania. Gdy mechanizm ten jest wyłączony to adres liniowy i fizyczny są równoważne.

Są to dwa typy portów równoległych Centronics drukarek LPT:

Adres fizyczny – powstaje z adresu logicznego lub liniowego w procesie stronicowania. Jest SPI pozwala na przesyłanie tylko w jedną stronę (simplex), drukarka odpowiada za używany do każdej wymiany danych między procesorem a pamięcią czy urządzeniami drukowanie

wejścia /wyjścia.

EPP pozwala na przesyłanie dużych ilości danych do drukarek (GDI), w systemie fullduplex.

Za drukowanie odpowiada jadro systemu.

25. Ile pamięci może zaadresować procesor 80286.

Procesor ten posiada 24 bitową szynę adresową. Dlatego może on zaadresować: 224 bitów = 38. Czego dotyczą i co oznaczają określenia: RTS-CTS i XON/XOFF.

216 bajtów = 214 kilobajtów = 16 megabajtów

Są to protokoły transmisji danych interfejsu szeregowego.

Dla porównania: 80868 220 bitów = 1MB; 80386 232 bitów = 4GB.

Xon/Xoff – działa w trybie transmisji półduplexowym (naprzemienna transmisja w jednym

kablu). Znak Xon zezwala na transmisję, a Xoff ją zatrzymuje.

26. W jakich technologiach można zrealizować i co zawiera w sobie ROM systemowy RTS-CTS – działa w trybie duplexowym (dwa kable: jeden odbiera dane RxD, drugi je komputera PC.

transmituje TxD). Sygnał RTS to prośba o wysłanie danych, sygnał CTS zezwala na

Można go zrealizować w technologiach:

transmisję.

PROM: może zostać zaprogramowany specjalnym programatorem PROM, ale tylko raz;

EPROM: można wymazać jego zawartość przy pomocy światła ultrafioletowego i 39. Na czym polega transmisja asynchroniczna.

programować wiele razy;

Jest to przesył danych, w którym czas pomiędzy przesłaniem znaków może być różny (dane

EEPROM: może zostać wymazany programowo, więc nie trzeba go w tym celu wyjmować z mogą pojawiać się w dowolnej chwili i będą natychmiast transmitowane do odbiorcy). Inaczej komputera;

mówiąc nie używa się sygnału zegarowego, lecz sterowanie transmisją odbywa się przez bit

Flash: współcześnie stosowana wersja EEPROM-u, pozwalająca na bardzo szybkie startu na początku każdego znaku i przez jeden lub dwa bity stopu na końcu każdego wymazywanie i zapisywanie pamięci;

przesłania znaku.

FRAM: pamięć ferrytowa.

ROM w komputerach PC zawiera BIOS, oprogramowanie obsługujące i konfigurujące Dla porównania

transmisja synchroniczna

to sposób przesyłania danych

najbardziej podstawowe urządzenia komputera.

synchronizowanych przez sygnał zegarowy nadawany osobnym przewodem łącza

szeregowego albo, w przypadku modemu, zakodowany wraz z danymi.

27. Na czym polega różnica w adresowaniu CHS i LBA.

Adresowanie CHS określa adres sektora dysku przez trzy liczby: cylinder, głowicę, sektor. 40. Procesory iAPX86.

Adresowanie LBA przyjmuje jeden liniowo określony numer sektora, który jest tłumaczony na Kolejne procesory Intela różniły się m. in. rejestrami wewnętrznymi procesora, szyną danych fizyczny adres przez sam dysk.

(sposobem przesyłania informacji poza procesor), szyną adresową (przesyłanie adresów),

trybami pracy czy koprocesorem.

28. Co to jest maszyna von Neumann'a.

System komputerowy von Neumanna nie posiada oddzielnych pamięci do przechowywania Procesor

Rejestry

Szyna

Szyna

Tryb pracy

Koprocesor

danych i instrukcji. Instrukcje jak i dane są zakodowane w postaci liczb. Bez analizy programu

wewnętrzne danych

adresowa

trudno jest określić czy dany obszar pamięci zawiera dane czy instrukcje. Przeciwieństwem 80868

16bit.

16bit.

20bit.

rzeczywisty

87

jest architektura Harvardzka, gdzie dane i kod są dwoma oddzielnymi obszarami pamięci.

80286

16bit.

16bit.

24bit.

rzeczywisty,

287

chroniony

29. Ile rejestrów 8 bitowych posiada procesor Pentium.

Osiem: AH, AL, BH, BL, CH, CL, DH, DL.

80386

32bit.

32bit.

32bit.

rzeczywisty,

387

chroniony,

30. Podać format ramki i parametry konfiguracyjne interfejsu RS232C.

wirtualny

Na ramkę składają się, oprócz właściwych bitów danych, znacznik początku ramki (tzw. bit Pentium

32bit.

64bit.

32bit.

rzeczywisty,

zintegrowany

startu), bit kontroli parzystości (Odd, Even, NONE, MARK, SPACE) i znacznik końca ramki (bit

chroniony,

stopu). Czas trwania jednego bitu ramki, tj. okres wyimaginowanego przebiegu

wirtualny

synchronizującego wynika ściśle z uzgodnionej prędkości transmisji. W ogólności ramka może

zawierać 5, 6, 7 lub 8 bitów danych (LSB...MSB). Bit startu jest obowiązkowy, a liczba bitów

stopu może wynosić 1 lub 2.

9

11

31. Wymień obszary pamięci.

41. Omówić dostępne technologie realizacji półprzewodnikowych układów pamięciowych.

RAM dzieli się na:

Pamięć półprzewodnikowa – rodzaj pamięci będącej cyfrowym układem scalonym i

TPA 640 kB - pamięć konwencjonalna DOS (gdzie jest ładowana tablica wektorów przerwań przechowującej informacje w postaci binarnej. Zaliczamy do niej pamięć RAM i ROM. Pamięci zajmująca 1kB).

są jednymi z podstawowych stosowanych w komputerach PC.

UMB - tzn. pamięć wyższa, umowna nazwa obszaru pamięci zaczynającego się od 640 kB i Punktem pamięci półprzewodnikowej statycznej jest przerzutnik sr, zbudowany w oparciu o mającego rozmiar 384kB. Obszar ten zarezerwowany jest dla kart i pamięci stałych.

technologię bipolarną lub unipolarną. Zasada działania takiej pamięci polega na podaniu

ROM - gdzie mieści się BIOS.

sygnału jedynki logicznej na odpowiednią linię słowa zapisu (lub odczytu) oraz sygnału '1' lub

HMA - pamięć górna.

'0' na linię bitu zapisywanego (odczytywanego). W odróżnieniu od pamięci statycznej pamięć

XMS - tylko w trybie chronionym (z HMA).

dynamiczna wymaga dodatkowego działania jakim jest odświeżanie.

32. Tryb rzeczywisty (mechanizm segmentacji).

42. Co to jest CTC i do czego służy.

Tryb zgodny z najstarszymi procesorami rodziny x86 z Intel 8086 włącznie. W trybie tym CTC to układ służący do odmierzania odcinków czasu (podstawa to kwarc). Posiada 3

występuje segmentacja pamięci, rozmiar segmentu jest stały i wynosi 64 KB. Przestrzeń identyczne 16 bitowe liczniki: Gate, CLK i OUT. Może pracować w 6 niezależnych trybach adresowa ograniczona jest do 1 MB, do adresowania wykorzystuje się rejestry segmentowe pracy.

oraz offset. W trybie tym współczesne procesory pracują jedynie od chwili uruchomienia do

przekazania kontroli systemowi operacyjnemu.

43. Mechanizmy ochrony zasobów, na czym polegają i jakie są ich reguły.

Zasoby chronimy stosując następujące mechanizmy:

33. Tryb chroniony (mechanizm segmentacji).

- Separacja zadań – każde zadanie dysponuje wirtualną przestrzenią adresową.

Tryb inicjalizowany i w znacznej mierze kontrolowany przez system operacyjny. Pamięć może - Poziomy ochrony (segmentacja) – dane mają cztery stopnie uprzywilejowania 0,1,2,3 (0-być zorganizowana w segmenty dowolnej wielkości, fizyczna przestrzeń adresowa dane najbardziej uprzywilejowane).

ograniczona jest z reguły do 64 GB, liniowa przestrzeń adresowa do 4 GB. Rodzaj - Poziomy ochrony (stronicowanie) – dane mają poziomy nadrzędne i podrzędne.

adresowania zależy od systemu operacyjnego - może być stosowany tzw. model płaski (bez Poziomy ochrony często prezentowane są w formie pierścieni, gdzie w wewnętrznym (0-segmentacji), model z segmentacją analogiczną do trybu rzeczywistego, lub - najczęściej - najbardziej uprzywilejowanym) znajduje się jądro systemu, w zewnętrznym (3-najmniej adresowanie nieliniowe (tzw. logiczne). W adresowaniu nieliniowym adres fizyczny jest uprzywilejowanym) aplikacje użytkownika. Ważnym aspektem ochrony jest możliwość zależny od wpisu w systemowej tablicy deskryptorów, na który wskazuje selektor. W trybie odwołania się do danych i kodu z wyższych. Reguły mówią: chronionym procesor wspiera wielozadaniowość, chroni przed nieupoważnionym dostępem - nie możesz odwołać się do danych na bardziej wewnętrznym pierścieniu, do urządzeń wejścia/wyjścia.

- nie możesz odwoływać się do kodu (procedur) z bardziej zewnętrznego pierścienia (bo są

mniej chronione).

34. Omówić różnice i podobieństwa w kodowaniu informacji metodą FM i MFM.

FM czyli modulacja częstotliwości jest sposobem kodowania informacji stosowanym przy 44. Na czym polega specyfikacja urządzeń legacy.

kodowaniu informacji na dyskietkach pojedynczej gęstości. Przy odczycie sygnału z nośnika W komputerach PC rejestry (komórki pamięci) sterujące urządzeniami znajdują się w osobnej magnetycznego odczyt namagnesowania jest dość trudny, znacznie łatwiejszy jest odczyt przestrzeni adresowej. Urządzenia legacy są adresowane liniami A9...A0, które mieszczą się zmian namagnesowania (pola magnetycznego), gdyż wywołuje ono powstanie prądu w 1kB. Specyfikacja tych urządzeń jest dobrze udokumentowana w standardach (dana linia indukcyjnego w głowicy magnetycznej. Przy zapisie FM kierunek pola magnetycznego odpowiada konkretnemu urządzeniu).

zmieniany jest na początku komórki bitowej, oraz w jej środku ale tylko wtedy gdy kodowana

jest jedynka (binarna).

45. Wymienić i opisać parametry konfiguracyjne transmisji szeregowej.

MFM pozwala na zwiększenie, w stosunku do FM ilości kodowanej informacji przy zadanej - liczba bitów na sekundę częstotliwości maksymalnej sygnału. Kodowanie informacji odbywa się według zasady: - parametry ramki nadawanie jedynki zmienia kierunek prądu głowicy zapisującej w środku komórki bitowej, - ilość bitów danych w ramce nadawanie zera zmienia kierunek prądu na początku ale tylko wtedy gdy poprzednio - sposób kontroli parzystości (czy liczba bitów "1" razem z bitem parzystości ma być nadawanym bitem nie była jedynka. W zapisie występują ciągi o dwóch lub trzech czasach parzysta, nieparzysta, czy bit parzystości zawsze na "0" albo na "1" (brak kontroli)) jednostkowych o takim samym kierunku prądu, co pozwala dwukrotnie zwiększyć - ilość bitów stopu

częstotliwość zmian w stosunku do metody FM.

- rodzaj sterowania przepływem (RTS/CTS i Xon/Xoff)

Ramka może zawierać się od 5 do 8 bitów danych (jednak większość urządzeń posługuje się

35. Na czym polegają różnice w konfiguracji interfejsu IEEE1284.

słowem 7 lub 8 bitowym) poprzedzonym bitem startu oraz zakończonym bitem parzystości i

IEEE 1284 może operować w pięciu trybach pracy:

jednym lub dwoma bitami stopu.

- Centronics (Compatibility mode, SPI): najprostszy tryb, pozwalający przesyłać dane w jedną

stronę w trybie simplex

46. Do czego służy dyrektywa ARG.

- Nibble Mode

ARG zm1:WORD, zm2:WORD ; ustalenie parametrów procedury

- Byte Mode (bitronics, PS/2): przesył danych w dwie strony halfduplex

RETURNS wynik:WORD ; ustalenie wartości zwracanej przez procedurę

- EPP: przesył danych w dwie strony w trybie fullduplex

- ECP: szybszy od EPP, dzięki bezpośredniemu dostępowi do pamięci

10

12

47. Działanie instrukcji jmp i jz (różnice/podobieństwa).

jmp bezwarunkowo skacze do danej etykiety w kodzie, a jz jest skokiem warunkowym,

wykonywanym jeśli wynik ostatniej operacji wynosi zero.

48. Wypełnij słowem jednym.

a) Pentium posiada 8 rejestrów 8 bitowych.

b) PIC w komputerze AT obsługuje 15 przerwań.

c) W kodzie ASCII jest 95 znaków pisarskich.

d) Instrukcja mov ax,[1234] używa domyślnie rejestru DS.

e) Wskaźnikowi 1234H:5678H odpowiada bajt o adresie 1234h * F0h + 5678h

f) GDTR przechowuje adres początku globalnej tablicy deskryptorów (global descriptor table

register).

g) 80286 ma 24 bitowa szynę adresową.

13

1. Podać i omówić przeznaczenie rejestrów procesora............................................................. 1

2. Omów poszczególne bloki w budowie procesora.................................................................. 1

3. Kodowanie w alfabetach stron kodowych............................................................................. 1

4. Podobieństwa i różnice w segmentacji pamięci w trybie rzeczywistym i chronionym........... 2

5. Stronicowanie....................................................................................................................... 3

6. Selektor................................................................................................................................ 3

7. Deskryptor............................................................................................................................ 3

8. Rejestry GDTR i LDTR (do czego służą)................................................................................ 4

9. Selektor a deskryptor (różnice)............................................................................................ 4

10. Atrybuty adresowania (bezpośrednie, pośrednie, przykłady)............................................. 4

11. Program typu COM i EXE (porównanie struktury)............................................................... 4

12. Stos zrealizowany (obsługiwany) w procesorze iAPX86...................................................... 5

13. INT xxx i CALL xxx (różnice i podobieństwa)...................................................................... 6

14. Przerwania programowe, przerwania sprzętowe................................................................ 6

15. W jaki sposób dokonuje się przerwań programowych........................................................ 6

16. W jaki sposób procesor wykonuje obsługę przerwania sprzętowego.................................. 7

17. Omówić budowę mechanizmu przerwań sprzętowych dostępnych w komputerze PC/AT,

PC/XT........................................................................................................................................ 7

18. Na czym polega tryb PIO pracy interfejsu ST506............................................................... 7

19. Omówić poszczególne bloki funkcyjne płyty głównej komputera PC-AT............................. 7

20. Na czym polega idea płaskiego chronionego modelu pamięci?......................................... 8

21. Na czym polega przetwarzanie potokowe.......................................................................... 8

22. Przerwanie potokowe, a superskalarne (różnice)............................................................... 8

23. Fazy wykonania rozkazu (poszczególne kroki cyklu instrukcji)........................................... 8

24. Adres logiczny, fizyczny, liniowy......................................................................................... 9

25. Ile pamięci może zaadresować procesor 80286................................................................. 9

26. W jakich technologiach można zrealizować i co zawiera w sobie ROM systemowy

komputera PC........................................................................................................................... 9

27. Na czym polega różnica w adresowaniu CHS i LBA............................................................ 9

28. Co to jest maszyna von Neumann'a................................................................................... 9

29. Ile rejestrów 8 bitowych posiada procesor Pentium............................................................ 9

30. Podać format ramki i parametry konfiguracyjne interfejsu RS232C................................... 9

31. Wymień obszary pamięci................................................................................................. 10

32. Tryb rzeczywisty (mechanizm segmentacji)..................................................................... 10

33. Tryb chroniony (mechanizm segmentacji)........................................................................ 10

34. Omówić różnice i podobieństwa w kodowaniu informacji metodą FM i MFM.................... 10

35. Na czym polegają różnice w konfiguracji interfejsu IEEE1284.......................................... 10

36. Czego dotyczy i na czym polega różnica pomiędzy trybami pracy SPI a PS/2.................. 11

37. Różnice miedzy SPI i EPP................................................................................................... 11

38. Czego dotyczą i co oznaczają określenia: RTS-CTS i XON/XOFF........................................ 11

39. Na czym polega transmisja asynchroniczna..................................................................... 11

40. Procesory iAPX86.............................................................................................................. 11

41. Omówić dostępne technologie realizacji półprzewodnikowych układów pamięciowych... 12

42. Co to jest CTC i do czego służy......................................................................................... 12

43. Mechanizmy ochrony zasobów, na czym polegają i jakie są ich reguły............................ 12

44. Na czym polega specyfikacja urządzeń legacy................................................................. 12

45. Wymienić i opisać parametry konfiguracyjne transmisji szeregowej................................ 12

46. Do czego służy dyrektywa ARG........................................................................................ 12

47. Działanie instrukcji jmp i jz (różnice/podobieństwa)......................................................... 13

48. Wypełnij słowem jednym.................................................................................................. 13

0

3

4

1

Wyszukiwarka

Podobne podstrony:

ZINTEGROWANE RATOWNICTWO MEDYCZNE - teoria, Farmacja, Kwalifikowana pierwsza pomoc

teoria literatury- pomoc naukowa, FILOLOGIA POLSKA, teoria literatury

PIERWSZA POMOC J L

teoria bledow 2

sroda teoria organizacji i zarzadzania

01 Pomoc i wsparcie rodziny patologicznej polski system pomocy ofiarom przemocy w rodzinieid 2637 p

Zatrucia pierwsza pomoc(1)

PIERWSZA POMOC PRZEDMEDYCZNA

PIERWSZA POMOC

W10b Teoria Ja tozsamosc

Teoria organizacji i kierowania w adm publ prezentacja czesc o konflikcie i zespolach dw1

Pomoc rodzinie dziecka niepełnosprawnego

Pomoc psychologiczna w chorobie stres a zdrowie

więcej podobnych podstron