Paweł Deryło 3P24

Zespół 8

Elementy i Uk --> [Author:R.D.T] łady Elektroniczne -Laboratorium

Bramki Logiczne.

1.Charakterystyka przejściowa inwerterów:

Charakterystyka przejściowa inwertera TTL typu 74LS04 (0V ≤ UIN ≤ 4V):

Na otrzymanej charakterystyce wyznaczono wartości napięć odpowiadające poziomom logicznym L i H.

- napięcie w punkcie T: UT ≅ 1,2096 V

- napięcie wyjściowe stanu wysokiego: UOH ≅ 3,667V

- napięcie wyjściowe stanu niskiego: UOL ≅ 0,399V

- margines zakłóceń dla stanu „1”: UZH ≅ 3,7V - 1,3V ≅ 2.4V

- margines zakłóceń dla stanu „0”: UZL ≅ 0,85V - 0,4V ≅ 0,45V

Charakterystyka przejściowa inwertera 74HCU04 (0V ≤ UIN ≤ 5V):

Z otrzymanej charakterystyki wyznaczam:

- napięcie punktu T: UT ≅2,52V

- napięcie stanu wysokiego: UH ≅5V

- napięcie stanu niskiego: UL ≅15mV

- margines zakłóceń dla „1”: UZH ≅4,5V - 2,94V ≅ 1,56V

- margines zakłóceń dla „0”: UZL ≅ 2,06 - 0,45 ≅ 1,61V

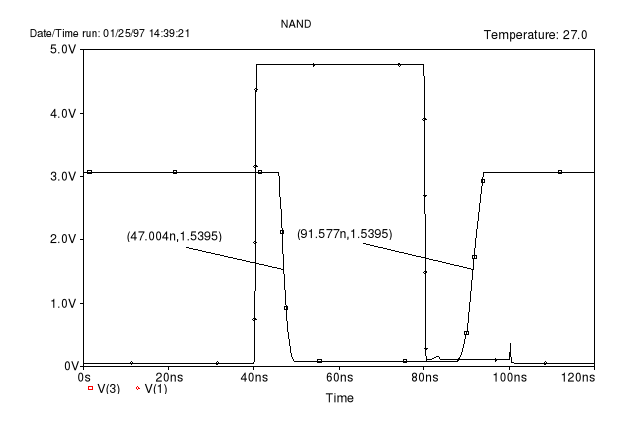

3. Przebiegi wejściowe i wyjściowe bramki NAND.

Przebiegi wejściowe i wyjściowy bramki dla MNTYMXDLY = 1.

Dla MNTYMXDLY = 1 wyznaczono wartości czasów opóźnień :

przy przejściu z „L” na „H”: tdLH = 85,1ns - 80ns ≅ 5,1ns

przy przejściu z „H” na „L”: tdHL = 42,8ns - 40ns ≅2,8ns

Przebiegi wejściowe i wyjściowy bramki dla MNTYMXDLY = 2.

Dla parametru MNTYMXDLY = 2 czasy opóźnień wynoszą odpowiednio:

przy przejściu z „L” na „H”: tdLH = 91,6ns - 80ns ≅11,6ns

przy przejściu z „H” na „L”: tdHL = 47,0ns - 40ns ≅7,0ns

Przebiegi wejściowe i wyjściowy bramki dla MNTYMXDLY = 3.

Dla parametru MNTYMXDLY = 3 czasy opóźnień wynoszą odpowiednio:

przy przejściu z „L” na „H”: tdLH = 102,7ns - 80ns ≅ 22,7ns

przy przejściu z „H” na „L”: tdHL = 55,0ns - 40ns = 15,0ns

Otrzymane wyniki czasów opóźnienia bramki NAND TTL przy trzech różnych wartościach parametru MNTYMXDLY odpowiadają czasom dla standardowej bramki NAND TTL.

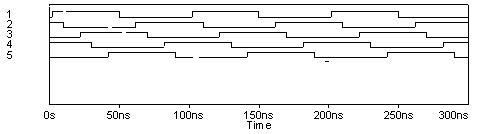

4. Pomiar uśrednionego czasu propagacji.

Usredniony czas propagacji pojedynczego invertera można znaleźć mierząc okres generatora zbudowanego z inwerteró połączonych w szereg. Jeśli przez Tg oznaczymy okres generatora

przez k liczbe inwerterow w tym generatorze to wtedy:

tpd=

Dla pojedynczego inwertera tpd=0.5(tdHL+tdLH) = 0.5(11,6+7)=9,3ns (dla wartości parametru MNTYMXDLY=2), okres generatora powinien wynosić wtedy:

Tg=2tpdk= 2 * 9,3ns* 5= 93ns (dla 5 inwerterów).

Aby sprawdzić jak ma się to do rzeczywistości zasymulować należy generatora z pliku gen_cyf.cir. Jak widać na poniższym rysunku okres generatora zgadza się z obliczoną wartością Tg.( Uk --> [Author:R.D.T] ład symulowany dla MNTYMXDLY=2 )

Z dość dobrą dokładnością widzimy zgodność z obliczeniami - Tg ok. 95 ns.

1

3

Wartości parametru MNTYMXDLY wyznaczają opóźnienia propagacji sygnału bramki.

1 - opóźnienie minimalne,

2 - opóźnienie typowe,

3 - opóźnienie maksymalne.

Wyszukiwarka

Podobne podstrony:

Stare projekty, P BRAMKI, Pawe˙ Dobro˙ gr. 3P23

Sprawozdania przerobione, Pomiar prądu stałego przyrządami analogowymi i cyfrowymi 1, ZESPÓŁ SZKÓŁ I

Sprawozdania przerobione, Pomiar napięcia stałego przyrządami analogowymi i cyfrowymi 2, ZESPÓŁ SZKÓ

Wykład XII Struktury cyfrowych zespołów funkcjonalnych

Pomiar parametrów statycznych bramki NAND, Zespół Szkół Elektrycznych nr 1 w Poznaniu

Synteza układów cyfrowych, Zespół Szkół Elektrycznych nr 1 w Poznaniu

Dysleksja cyfrowa, zespół NLD, różnorodne postaci rozwojowej dyskalkulii oraz mechanizmy wyjaśniając

Sprawko napedy elektryczne gr 3 7 zespol 1(1)

01.Podstawowe bramki logiczne instrukcja poprawiona, Akademia Morska, III semestr, technika cyfrowa,

sprawozdanie z TLC gr 34T1 zespół 3

bramkilogiczne, 1 STUDIA - Informatyka Politechnika Koszalińska, muniol, I rok, Technika cyfrowa, TC

Sprawozdanie MB2 gr 3 8 zespół 1 podz 1 ogarnijtemat com

Sprawozdanie gr 3 4 zespolA

bp B 3 w tył gr AGA Robert

NOTAKI Z TECHNIKI CYFROWEJ

więcej podobnych podstron