ZESPÓŁ SZKÓŁ NR 9 im. ROMUALDA TRAUGUTTA

W KOSZALINIE

Temat: Badanie bramek CMOS

Rok szkolny 2002/2003

Wstęp.

Układy logiczne CMOS (ang. Complementary MOS) są to układy zawierające komplementarne pary wzbogacanych tranzystorów n-MOS i p-MOS wytworzone w jednym procesie technologicznym na tej samej płytce półprzewodnikowej.

Podstawową zaletą układów SMOS jest znikomy pobór mocy w warunkach pracy statycznej układu. Główne źródło strat stanowią wówczas prądy upływu elementów. Natomiast podczas przełączania, pobór mocy przez element jest związany przede wszystkim ze zjawiskiem przeładowania pojemności obciążającej i wzrasta proporcjonalnie do częstotliwości pracy układu.

Ogólna charakterystyka rodziny układów CMOS serii 4000.

Cyfrowe układy scalone CMOS zbudowane są z tranzystorów polowych z izolowaną bramką - MOSFET. Sterowanie pracą takich tranzystorów odbywa się przy pomocy napięcia doprowadzonego do elektrody sterującej (bramki ang. gate). Rezystancja wejściowa tranzystorów MOSFET jest bardzo duża i wynosi ok. 1012 Ω. Pojemność wejściowa tych tranzystorów ma wartość 5 pF. W układach serii CD 4000 sterowane są komplementarne tranzystory z kanałem typu p i n. Aby w pełni scharakteryzować rodzinę układów CMOS serii CD 4000 przytaczamy podstawowe parametry układów scalonych. Większość z danych odnosi się do wszystkich układów i pozwala zorientować się w możliwościach tej rodziny.

Napięcie zasilania 3 ÷ 18 V

Spoczynkowy prąd zasilania (na jedną bramkę) 10 ÷ 100pA

Maksymalna wartość prądu zasilania dla UDD = 5V

- Układy SSI (mała skala integracji) 0,25 μA

- Przerzutniki 1 μA

- Układy MSI (średnia skala integracji) 5 μA

Prąd wejściowy 10 ÷ 10 pA

Prąd wyjściowy w stanie niskim UDD = 5V 1 mA

UDD = 10V 2,6 mA

UDD = 15V 6,8mA

Prąd wyjściowy w stanie wysokim UDD = 5V - 1 mA

UDD = 10V - 2,6 mA

UDD = 15V - 6,8mA

Topowa obciążalność 2 układy TTL-L

1 układ TTL-LS

Napięcie wejściowe

w stanie niskim UIlmax UDD = 5V 1,5 V

UDD = 10V 3 V

UDD = 15V 4 V

Napięcie wejściowe

w stanie wysokim UIHmax UDD = 5V 3,5 V

UDD = 10V 7 V

UDD = 15V 11 V

Napięcie wyjściowe

w stanie niskim UOlmax UDD = 5V 0,05 V

UDD = 10V 0,05 V

UDD = 15V 0,05 V

Napięcie wyjściowe

w stanie wysokim UOhmin UDD = 5V 4,95 V

UDD = 10V 9,95 V

UDD = 15V 14,95 V

Czad propagacji (dla bramki CD 4000)

obciążenie pojemnościowe 50 pF UDD = 5V 125 ns

UDD = 10V 70 ns

UDD = 15V 40 ns

Częstotliwość pracy (max.) 12 MHz

Zakres temperatury pracy -40 ÷ 85 0 C

W zależności od producenta parametry układów mogą się różnic nieznacznie od podanych powyżej.

Z danych tych wynika szereg wniosków dotyczących układów CMOS:

parametry układów zależą wyraźnie od napięcia zasilania

obciążalność wyjść jest niewielka i zależy od napięcia zasilania

przy wyższych napięciach zasilania układy mogą pracować na wyższych częstotliwościach

prąd zasilania w warunkach statycznych jest bardzo mały, lecz wzrasta wraz z częstotliwością przełączania bramek i dla częstotliwości 1 ÷ 2 MHz moc pobierana przez układy CMOS ze źródła zasilania jest większa niż w przypadku układów serii TTL-LS

napięcia wyjściowe są bliskie napięciu zasilania (dla stanu wysokiego), oraz napięciu 0 V (dla stanu niskiego)

krótkotrwałe zwarcia wyjścia do masy lub napięcia zasilania nie powodują uszkodzenia układu

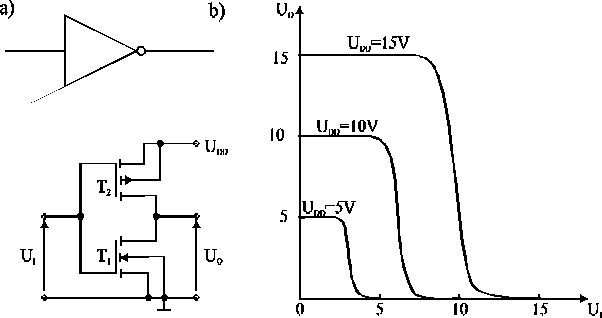

Na rysunku 1. przedstawiono podstawowy układ inwertera CMOS.

Rys. 1. Inwerter CMOS a) schemat elektryczny b) charakterystyka przejściowa.

Jeśli napięcie wejściowe jest równe napięciu zasilania UI = UDD, to tranzystor T1 przewodzi, a tranzystor T2 nie przewodzi. Wówczas napięcie wyjściowe jest, praktycznie biorąc, równe zeru.

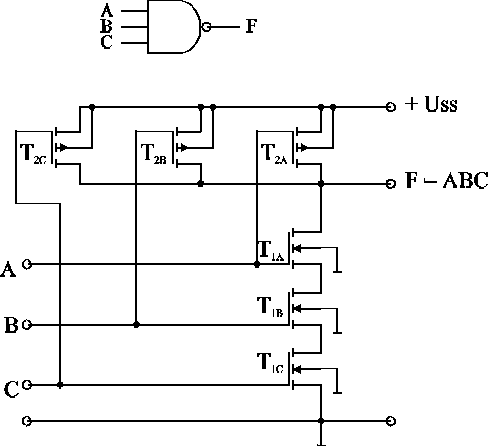

Wynika to z dzielnika napięcia, jaki tworzą tranzystor sterowany (przewodzący) i tranzystor obciążający (nieprzewodzący). Wartości rezystancji kanału tranzystorów przewodzącego i nieprzewodzącego wynoszą odpowiednio 500...700Ω i 5000MΩ. Z kolei gdy napięcie wejściowe jest równe zeru, to tranzystor T1 nie przewodzi, a tranzystor T2 jest w stanie przewodzenia. W tym przypadku napięcie wyjściowe jest, praktycznie biorąc, równe napięciu zasilania UDD. Charakterystykę przenoszenia układu CMOS przedstawiono na rysunku 1b. Korzystną cechą układów CMOS jest to, że wartość napięcia zasilania, można wybierać z przedziału 3...15V i niekoniecznie musi być ono stabilizowane. Warto podkreślić, że ze wzrostem napięcia zasilania ulega skróceniu (kilka razy)czas propagacji bramki, jednocześnie jednak zwiększa się też kilka razy moc tracona na bramkę, przy czym wskaźnik energetyczny nieznacznie wzrasta. Układy CMOS wymagają większej liczby tranzystorów niż funkcjonalnie analogiczne układy MOS z tranzystorami o jednakowym typie przewodnictwa kanałów, czego przykładem może być bramka NAND/CMOS, przedstawiona na rys. 2.

Rys. 2. Schemat elektryczny bramki NAND/CMOS.

Para komplementarna tranzystorów wymaga również stosowania wyspy izolującej, dlatego zajmuje większą powierzchnię płytki półprzewodnikowej niż para tranzystorów o jednakowym typie przewodnictwa. Układy CMOS charakteryzują się dużą impedancją wejściową (ok. 1012 Ω), a małą impedancją wyjściową (ok. 500 Ω) oraz dużą odpornością na zakłócenia (margines zakłóceń wynosi przeciętnie 45% napięcia zasilania). Są one produkowane we wszystkich stopniach scalenia. Typowym przykładem masowych zastosowań techniki CMOS mogą być układy zegarowe lub układy kalkulatorowe.

Negatory i bramki Schmitta.

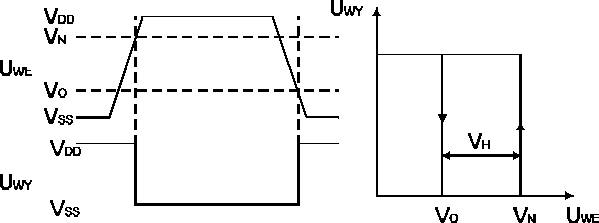

Charakterystyka przejściowa tych układów ma pętlę histerezy (rys. 3). Podstawowym zadaniem stawianym funktorom z wejściami Schmitta jest zamiana wolnozmiennych sygnałów wejściowych na sygnały cyfrowe o szybkim czasie narastania.

Zmiana stanów negatora lub bramki dla zbocza narastającego następuje przy przekroczeniu przez napięcie wejściowe progu Un niższego niż połowa napięcia zasilania. Różnica napięć pomiędzy progami Un i Uo nazywa się szerokością pętli histerezy UH. Funktory z wejściami Schmitta charakteryzują się większą odpornością na zakłócenia niż zwykłe bramki. W tabeli 1 podano napięcia progów, przy których następuje przełączenie negatorów CD 40106 i bramek CD 4093 z wejściami Schmitta.

Rys. 3. Charakterystyki przejściowe negatorów z wejściami Schmitta.

Tabela 1.

|

Napięcie zasilania |

||

|

5V |

10V |

15V |

Napięcie progu Un |

2,9V |

5,9V |

8,8V |

Napięcie progu Uo |

1,9V |

3,9V |

5,8V |

Opracowano także serie układów CMOS będące funkcjonalnymi zamiennikami odpowiednich układów TTL o identycznych z nimi konfiguracjach wyprowadzeń. Są to serie 74HCTxxx oraz 74ACTxxx. Do współpracy z układami TTL powinny być stosowane układy HCT i ACT. Natomiast układy serii HC i AC powinny być używane do innych zastosowań np. do systemów mikroprocesorowych (układy te mają szerszy zakres napięć przełączania i napięcia zasilania).

Bibliografia:

„Układy scalone w pytaniach i odpowiedziach” R. Ćwirko, M.Rusek, W. Marciniak.

Praktyczny elektronik 9/1993

Elektronika praktyczna 10/1993

4

5

Teoria.

6

Badanie bramek CMOS.

Wyszukiwarka

Podobne podstrony:

Teoria(3), elektronika

Teoria z Elektrotechniki, Teoria 3

Teoria z Elektrotechniki, 2 Kanały Radiowe, Kanały Radiowe (cyfrowe)

Teoria z Elektrotechniki, Teoria 2

Teoria z Elektrotechniki, 5 Kanały przewodowe, Przewody Telekomunikacyjne

Rozdzial 5 ObwodyTrojfazowe teoria2, Elektra

elektronika teoria, elektronika

Rozdzial 5 ObwodyTrojfazowe teoria1, Elektra

Rozdzial 5 ObwodyTrojfazowe teoria3, Elektra

Rozdzial 1 ObwodyPraduStalego teoria, Elektra

Teoria(6), elektronika

Rozdzial 4 Czworniki teoria, Elektra

Teoria(9), elektronika

10. Dyfrakcja i Polaryzacja - Teoria, Elektrotechnika AGH, Semestr II letni 2012-2013, Fizyka II - L

sprawozdanie badanie mikroskopowe-teoria!!!!!!!!!!, Elektrotechnika, dc pobierane, Podstawy Nauk o m

TS teoria, Elektronika i Telekomunikacja, semestr 3, teoria systemow

PÓŁPRZEWODNIKI – TEORIA, Elektrotechnika, Ćwiczenia instrukcje i teoria

Rozdzial 7 PradniceSilniki teoria, Elektra

więcej podobnych podstron