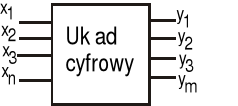

Ogólny schemat układu cyfrowego:

x - zmienne wejściowe

y -zmienne wyjściowe

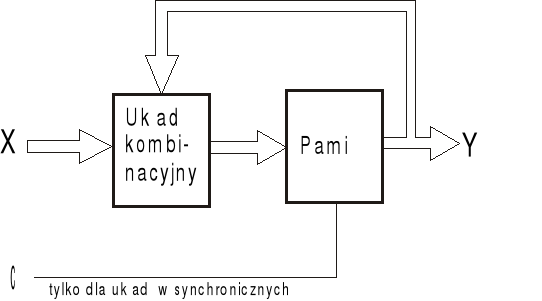

Układ sekwencyjny:

Podstawowe funkcje logiczne:

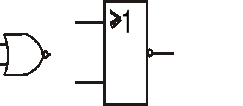

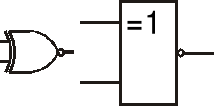

Suma logiczna a+b

a |

b |

a+b |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

OR

NOR

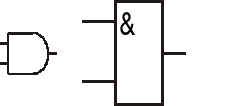

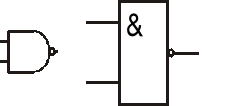

Iloczyn logiczny a⋅b (AND)

a |

b |

a⋅b |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

AND

NAND

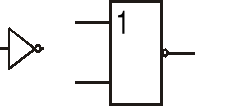

Negacja zmiennej a czyli ![]()

a |

|

0 |

1 |

1 |

0 |

NOT

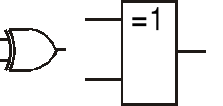

Nietożsamość⋅a ⊕ b (EX-OR)

A |

B |

a⋅b |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

EX-OR

EX-NOT (tożsamość)

ALGEBRA BOOLE'A

1o Prawa przemienności

![]()

![]()

2o

![]()

![]()

3o

![]()

![]()

![]()

![]()

4o

![]()

![]()

5o ![]()

6o Prawa rozdzielności

![]()

![]()

7o Prawa łączności

![]()

![]()

8o

![]()

![]()

![]()

![]()

9o Prawa negacji (twierdzenia de Morgana)

![]()

![]()

TYP |

Zasilanie [V] |

Prąd zasilania na bramkę |

Moc Na bramkę |

Prąd wyjściowy |

fmax [MHz] |

Obciążalność (fan out) |

||

|

|

|

|

1 |

0 |

|

|

|

74... |

5 |

40μA |

10mW |

500μA |

16mA |

35 |

10 |

|

74LS… |

5 |

20μA |

2mW |

300μA |

8mA |

45 |

20 |

|

4000BE |

3-18 |

10pA |

0.6μW |

1mA |

2.5mA |

5 |

50 |

|

74HC… |

2-6 |

10pA |

1μW |

4mA |

4mA |

40 |

>500 |

|

74HCT… |

5 |

10pA |

1μW |

4mA |

4mA |

45 |

>500 |

|

74AC… |

2-6 |

10pA |

1μW |

24mA |

24mA |

100 |

>500 |

|

LS- seria oparta o TTL Schottky'go - wieksza szybkość, mniejszy pobór mocy

HCT - CMOS-owe odpowiedniki układów TTL

AC- znacznie większa szybkość niż HCT

fan out - obciążalność wyjść mierzona liczbą możliwych do dołączenia na wyjściu bramek logicznych

Moc strat:

![]()

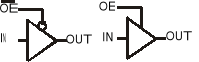

BRAMKI TRÓJSTANOWE:

Do realizacji połączeń szynowych (np. magistrali danych czy adresów w systemach cyfrowych)

Występowanie trzeciego stanu (oprócz zera i jedynki) tzn. dużej impedancji wyjściowej

Wejście OE (output enable) umożliwia przełączenie układu w stan dużej impedancji wyjściowej

Po włączeniu sygnału OE następuje przeniesienie sygnału z wejścia na wyjście (z ew. negacją)

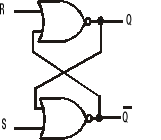

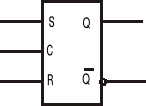

PRZERZUTNIKI ASYNCHRONICZNE:

![]()

S - set

R -reset

S |

R |

|

|

|

|

0 |

0 |

|

|

Stan poprzedni |

|

0 |

1 |

0 |

1 |

|

|

1 |

0 |

1 |

0 |

|

|

1 |

1 |

0 |

0 |

Stan logicznie Zabroniony! |

|

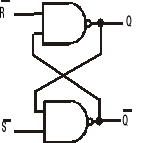

![]()

|

|

|

|

|

|

0 |

0 |

1 |

1 |

Stan logicznie Zabroniony! |

|

0 |

1 |

1 |

0 |

|

|

1 |

0 |

0 |

1 |

|

|

1 |

1 |

|

|

Stan poprzedni |

|

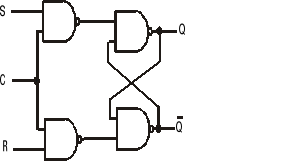

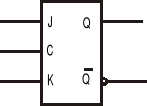

PRZERZUTNIKI SYNCHRONICZNE:

RS

|

|

|

|

|

|

0 |

0 |

1 |

1 |

Stan logicznie Zabroniony! |

|

0 |

1 |

1 |

0 |

|

|

1 |

0 |

0 |

1 |

|

|

1 |

1 |

|

|

Stan poprzedni |

|

PRZERZUTNIKI SYNCHRONICZNE:

JK

|

|

|

|

0 |

0 |

|

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

|

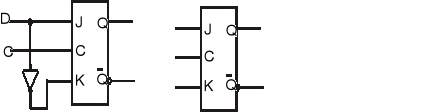

PRZERZUTNIKI SYNCHRONICZNE:

D

D |

|

|

0 |

0 |

1 |

1 |

1 |

0 |

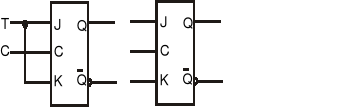

T

T |

|

|

0 |

|

|

1 |

|

|

Wyszukiwarka

Podobne podstrony:

Podstawy elektroniki i miernictwa2

Podstawy elektroniki i energoelektroniki prezentacja ppt

Modul 3 Podstawy elektroniki cyfrowej

podstawy elektrotechniki

lista 4a, Elektrotechnika, PODSTAWY ELEKTROTECHNIKI, ćwiczenia

stale, Elektrotechnika, dc pobierane, Podstawy Nauk o materialach, Przydatne, Sprawka

zadania na egzaminie czerwcowym 2009, Elektrotechnika, PODSTAWY ELEKTROTECHNIKI, pytania

Rodzaje pracy silników elektrycznych, 04. 01. ELECTRICAL, 07. Elektryka publikacje, 07. Electrical M

Zagad NE09, Politechnika Wrocławska, PWR - W10- Automatyka i Robotyka, Sem3, Elektro, Podstawy elekt

25 Podstawy działania przetworników opto, Elektrotechnika-materiały do szkoły, Pomiary elektryczne w

ćw 2, Studia, Podstawy elektroniki, sprawozdania elektronika

Cw 7 Pomiary Podstawowych wielkości w polu elektromagnetycznym

Laboratorium Podstaw Elektroniki

Podstawowe wielkosci elektromagnetyczne i mechaniczne

Podstawy elektroniki str 101 141

zaliczenie - pytania i odp2, Politechnika Lubelska Wydział Mechaniczny, Semestr II, Podstawy Elektro

instrukcja 06, sem 3, Podstawy elektrotechniki i elektroniki, Laboratoria, instrukcje do cwiczen 201

sc5 druk, Politechnika Wrocławska, PWR - W10- Automatyka i Robotyka, Sem3, Elektro, Podstawy elektro

więcej podobnych podstron