163 2

320

sumator muszą mieć po 2n bitów. Znacznie dogodniejszy układ można uzyskać na podstawie następującego wzoru:

n-1

n 1 2n B

i=0

i=0

2n 3 a,

- * 2n B a,

+ 2“ B a.

+ 2" B a.

n-1

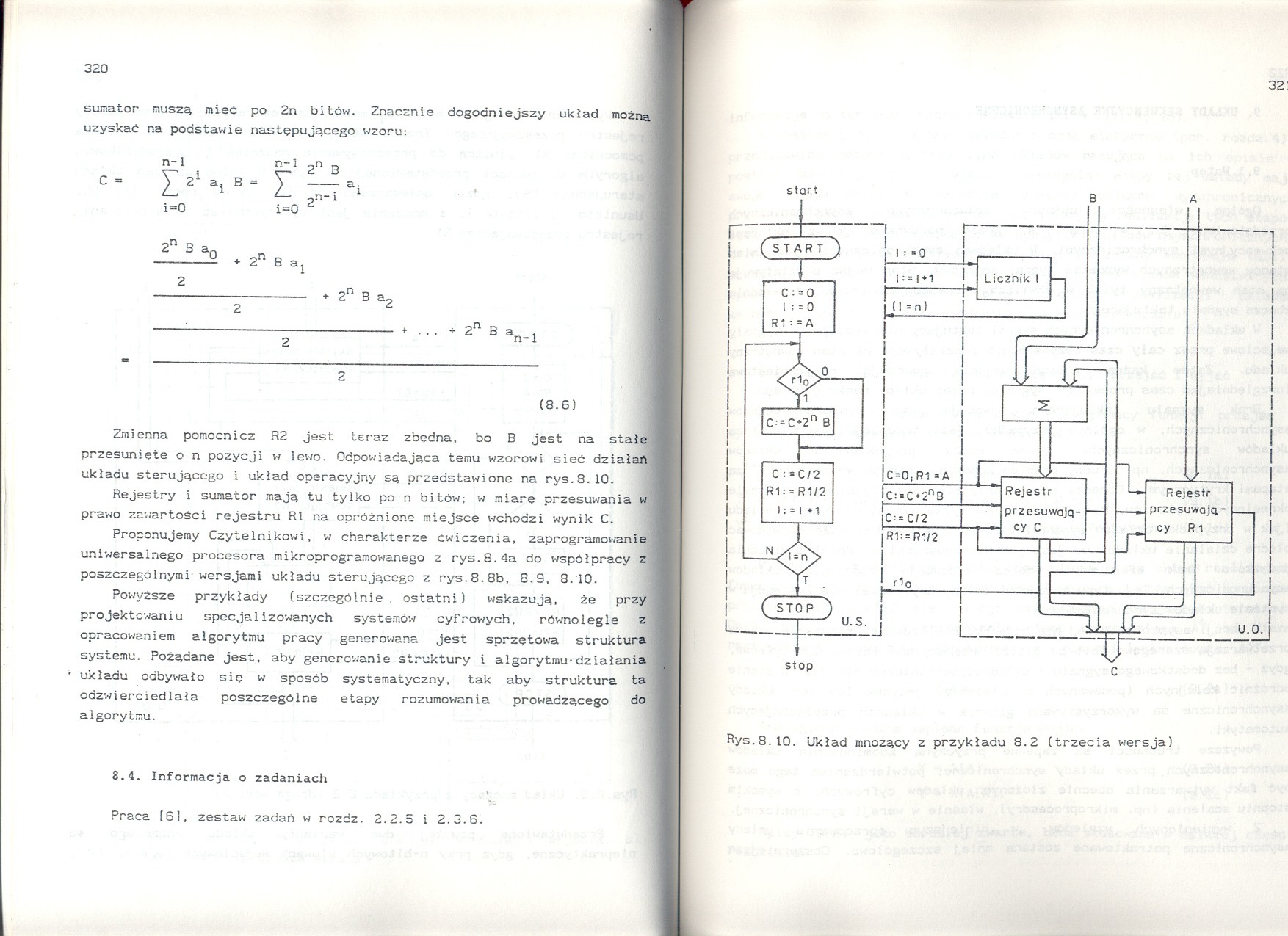

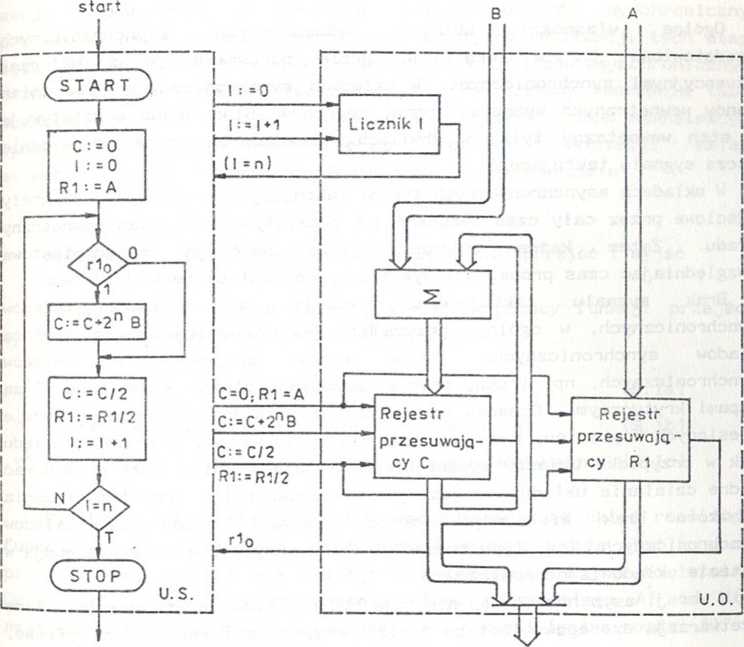

Zmienna pomocnicz R2 jest teraz zbędna, bo B jest na stałe przesunięte o n pozycji w lewo. Odpowiadająca temu wzorowi sieć działań układu sterującego i układ operacyjny są przedstawione na rys.8.10.

Rejestry i sumator mają tu tylko po n bitów; w miarę przesuwania w prawo zawartości rejestru R1 na opróżnione miejsce wchodzi wynik C.

Proponujemy Czytelnikowi, w charakterze ćwiczenia, zaprogramowanie uniwersalnego procesora mikroprogramowanego z rys.8.4a do współpracy z poszczególnymi wersjami układu sterującego z rys.8.8b, 8.9, 8.10.

Powyższe przykłady (szczególnie ostatni) wskazują. że przy projektowaniu specjalizowanych systemów cyfrowych, równolegle z opracowaniem algorytmu pracy generowana jest sprzętowa struktura systemu. Pożądane jest, aby generowanie struktury i algorytmu-działania układu odbywało się w sposób systematyczny, tak aby struktura ta odzwierciedlała poszczególne etapy rozumowania prowadzącego do algorytmu.

8.4. Informacja o zadaniach

Praca [6], zestaw zadań w rozdz. 2.2.5 i 2.3.6.

stop c

Rys.8.10. Układ mnożący z przykładu 8.2 (trzecia wersja)

Wyszukiwarka

Podobne podstrony:

Po zakończeniu skanowania pierwszej strony lub obrazu umieść na szybie następną stronę i kliknij prz

cy, którzy przyjmują odpowiedzialność za dany proces, muszą mieć odpowiednie kwalifikacje po to, aby

rysunek? bmp TWÓJ TORNISTER ORAZ UBRANIE MUSZĄ MIEĆ ZNACZKI ODBLASKOWE - JESTEŚ WIDOCZNY NAWET PO ZM

po 48 bitów każdy. Sposób tworzenia podkluczy dla kolejnych rund jest z góry określony i został opub

skanuj0031 (93) 5. Międzynarodowe aspekty ochrony przyrody182 Rezerwaty biosfery muszą mieć zapewnio

page0059 49 nia, które muszą mieć punkt zastosowania; chcemy czegoś, nie myślimy o próżni, ale myśli

dziennik ustaw krwiodawstwo (7) Dziennik Ustaw -7- Poz. 5 9. Używane pompy mu

18709 skanuj0005 (216) 114 6. Zagospodarowanie turystyczne • hotele (niem. Hotel),

Monitor Uniwersytetu Warszawskiego nr 6C 30 maia 2006 Kandydaci, którzy zdali „nową maturę”, muszą m

28 muszą mieć zajęcia praktyczne ciągle, nawet podczas pobytu w Szkole. Jest to zrozumiałe, gdyż zad

RODZAJE DZIAŁAŃ ADMINISTRACJI x Działania o charakterze faktycznym - luźne związanie, muszą mieć jed

HPIM4502 Robert Bogdan 268 wymazać lata życia w społeczeńsrwic, w którym ludzie muszą mieć jakąś

IMAG0286 (5) 30 EWA WOLAŃSKA 163) BBNews: Irek wyraźnie posmutniał po wyjściu Ilony z domu BB

88.36 4C> łD, +320-80 El ~ 2 El a po rozwiązaniu układu równa

Certyfikaty te są emitowane przez banki handlowe, które muszą mieć na to zgodę Banku Centralnego. Są

Wygasanie zobowiązań przy płatności pieniądzem bezgotówkowym - obie strony muszą mieć rachunki bakow

więcej podobnych podstron