skanuj0006 (260)

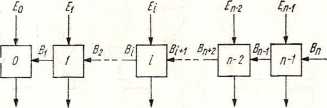

kod 1 z n, z uwzględnieniem priorytetu wejść, objaśnia tablica wartości przedstawiona na rys. 4.368b. Z wiersza np. drugiego tej tablicy wynika, że jeśli wejście Et jest w stanie 1 i nie ma przeniesienia blokującego

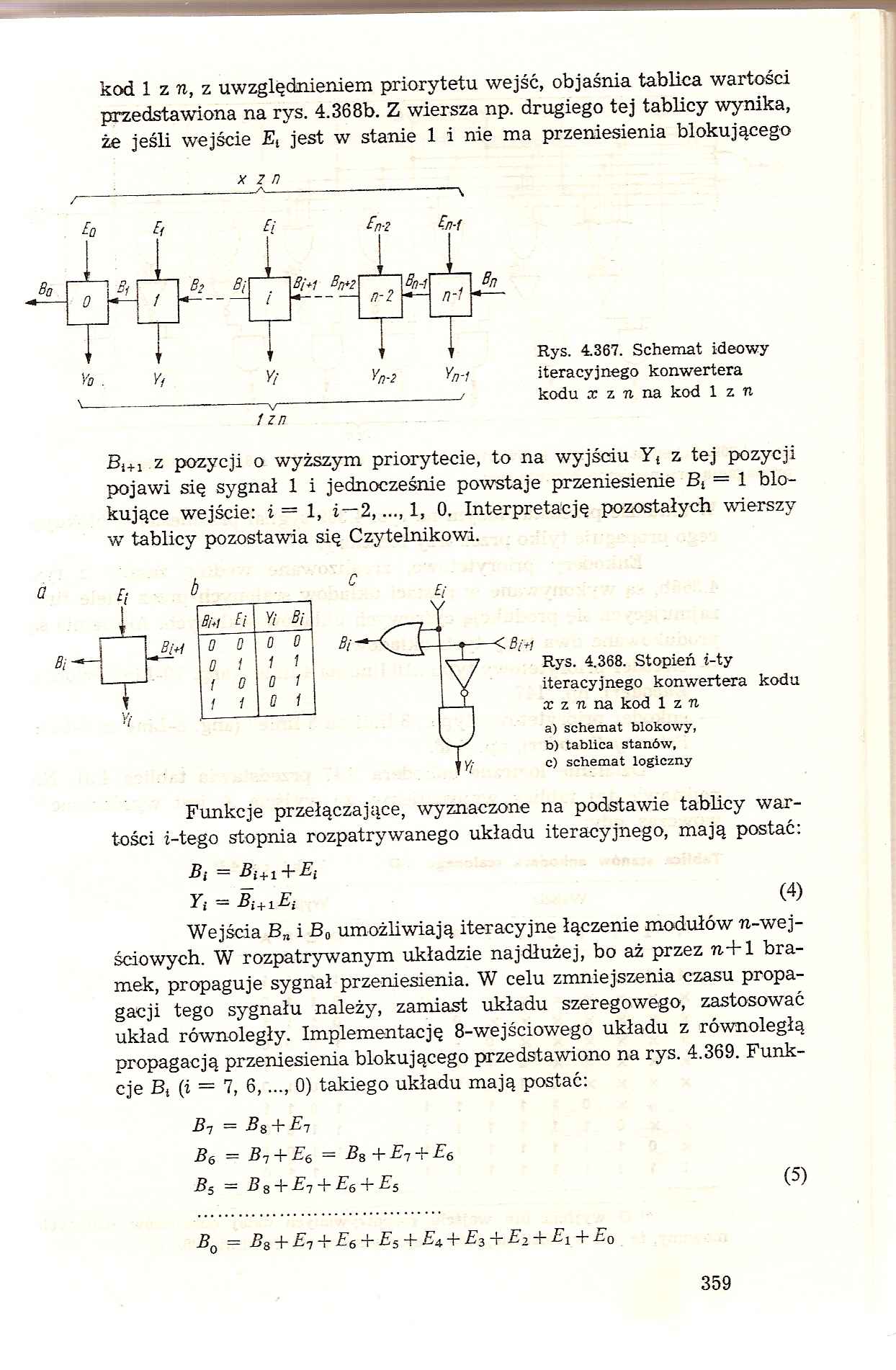

x 2 n

Vo . Yf Yf Yn.2 Yn-f

~7zn

Rys. 4.367. Schemat ideowy iteracyjnego konwertera kodu x z n na kod lz n

Bi+1 z pozycji o wyższym priorytecie, to na wyjściu Y{ z tej pozycji pojawi się sygnał 1 i jednocześnie powstaje przeniesienie Bt = 1 blokujące wejście: i = 1, i—2,..., 1, 0. Interpretację pozostałych wierszy w tablicy pozostawia się Czytelnikowi.

Rys. 4.368. Stopień i-ty iteracyjnego konwertera kodu x z n na kod 1 z n

a) schemat blokowy,

b) tablica stanów,

c) schemat logiczny

Funkcje przełączające, wyznaczone na podstawie tablicy wartości i-tego stopnia rozpatrywanego układu iteracyjnego, mają postać:

Bi = Bi+i + Ei

Yt = Bi+1Ei (4)

Wejścia Bn i B0 umożliwiają iteracyjne łączenie modułów n-wej-ściowych. W rozpatrywanym układzie najdłużej, bo aż przez n+l bramek, propaguje sygnał przeniesienia. W celu zmniejszenia czasu propagacji tego sygnału należy, zamiast układu szeregowego, zastosować układ równoległy. Implementację 8-wejściowego układu z równoległą propagacją przeniesienia blokującego przedstawiono na rys. 4.369. Funkcje Bt (i = 7, 6,..., 0) takiego układu mają postać:

By = B 8 + Ey

Bq = By+Eę = Bs+Ey + E^

Bs = B8+Ey + E6 + E5 (5)

B0 — Bq + Ey + jEg + Es + Eą. + £3 4- Ei + Ei + Eq

359

Wyszukiwarka

Podobne podstrony:

Rotation of? 176 Przykład 3.13 [4] Należy znaleźć rozwiąanie tablicy implikantów przedstawionej na r

skanuj0004 ^4L

Image075 Karnaugha. Sklejając tak, jak w tablicy przedstawionej na rys. 3.34a, otrzymuje się następu

Image078 Tablica wartości tej funkcji jest przedstawiona na rys. 3.36a. Ponieważ rozważana funkcja j

Image079 Tablica wartości tej funkcji przedstawiona na rys. 3.38a, a rozwiązanie zadania na rys.

Image345 Implementacje funkcji (1) i (2) przedstawiono na rys. 4.394. W układach tych, jeśli żadne z

Image424 Symbol graficzny przerzutnika 123 wraz z tablicą opisującą działanie układu przedstawiono n

skanuj0241 (4) łożysk przedstawiono na rys. 10.23. Niedopuszczalne jest zdejmowanie łożysk przez bez

img028 (16) - 104.- - R.6.121. Rozwiązanie Zad.6.121 przedstawiono na rys.R.6.13. Rys.R.6.13 Tablica

skanuj0007 (246) poprzecznego belki. Wymiar) belki rozpatrywanej w niniejszym ćwiczeniu podano na r

skanuj0156 (11) 292 B. Cieślar Rys. 7.12.2 Rozwiązanie Składowe stanu naprężenia przedstawiono na ry

skanuj0241 (4) łożysk przedstawiono na rys. 10.23. Niedopuszczalne jest zdejmowanie łożysk przez bez

skanuj0378 dzie identycznie jak sprzęgła samonastawne kłowe, przedstawione na rys. 14.8 Różnica pole

więcej podobnych podstron