128 129

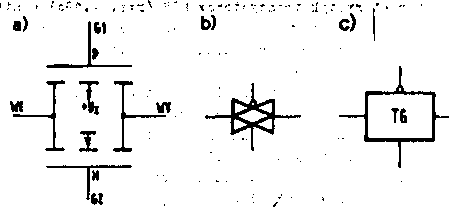

Rys. 4.25. Schemat (a) .1 spotykane symbole (b), (c) bramki transmisyjnej ny 1 dlatego omawiamy Ją oddzielnie,, ale tylko w.aspekcie zaatosowad cyfrowych.

Schemat 1 spotykane symbole bramki transmisyjnej podane są na rys. 4.25^ Bramka składa alf z dwóch komplementarnych tranzystorów KOS połączonych równolegle.

|

wuiar | ||||

|

wufctt |

TS | |||

|

smóWANic | ||||

Rys. 4.26. Dwukierunkowy klucz zbudowany przy utyciu bramki transmisyjnej CMOS

Bramka rozłącza wejście 1 wyjście (oporność przejścia > 10^2 ), jeżeli °Gf = Uz oraz Uq2 = 0. Połączenia wejścia z wyjściem następuje, gdy = 0 oraz

%2 = Uz (oporność przejścia rzędu kilkuset & ). Jeżeli napięcie wejściowe jest

bliskie U^, przewodzi tranzystor PMOS. Tranzystor HMOS jest wtedy odcięty, gdyż

%S<0OT oraz aDS < u03r z k*51®1. PrzJ napięciu wejściowym bliskim zera przewodzi tranzystor NMOS, zaś PMOS. Jest odcięty.

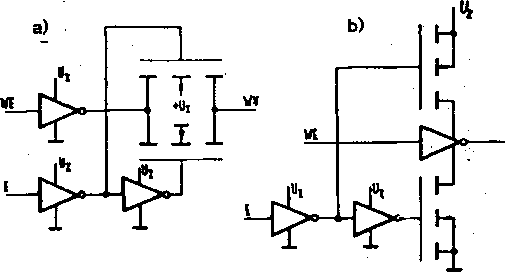

• Sterując bramką transmisyjną poprzez inwertor, otrzymujemy dwukierunkowy wyłącznik bezstykowy (Bllateral Swltch), w którym pojęcie wejścia 1 wyjścia jest czysto umowne (rys. 4-.26).

4.2.7. Bramka trójstanowa

Umieszczając na wyjściu dowolnego elementu logicznego CMOS bramkę transmisyjną otrzymujemy element trójstanowy (TRI-STATE). Tego typu rozwiązanie w zastosowaniu do inwertora pokazano na rys. 4.27a. Ten sam efekt można również uzyskać poprzez sterowaną separację danego elementu od linii zasilających, jak na rys. 4.27b. Sterowanie elementami separującymi odbywa się tutaj poprzez dwa lńwertory połączone kaskadowo, a nie jeden jak na rys. 4.26. Ma to na celu zagwarantowanie wejściu zezwalającemu (Siable) obciążalności wejściowej równej 1 (na rys. 4.26 wejśoie sterujące ma fan-ln = 1.5).

o

-W:

Rys. 4.27. Inwestor CMOS TRI-STATE: a) z branką transmisyjną, b) z separacją od linii zasilających

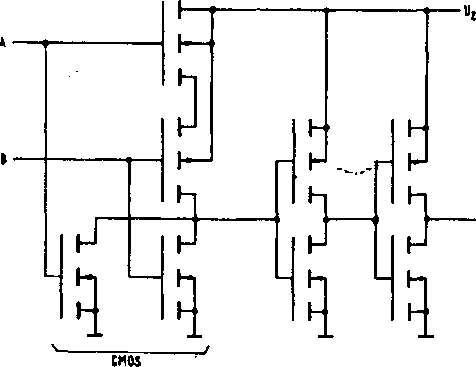

4.2.8. Układy LOCMOS

Dalszym krokiem w doskonaleniu układów scalonych KOS było wprowadzenie układów LOCMOS (Locally Ozidised CMOS) równoważnych funkcjonalnie i końcówko wo układom CMOS serii 4000.

'---—_(

LOCHO}

Rys. 4.28. Dwuwejściowa bramka NOR LOCMOS

Wyszukiwarka

Podobne podstrony:

128 129 ua Rys. 4.25. Schemat (a) i spotykane symbole (b), (c) bramki transmisyjnej ny 1 dlatego oma

69277 ksiazka(198) Rys. 8-25. Schemat sprysklwacza szyb: 1 - zbiorniczek dla płynu; 2 - pompka sprys

Rys. 7.25. Schemat obciążenia przęseł mostu drogowego do ustalania siły hamowania a)

CCF20111125�017 (2) 4.4. Silnik bocznikowy. Rys. 25. Schemat połączeń silnika bocznikowego W obwodzi

2 (1128) Rys. 25: Schemat montażowy odbiornika radiowego ZODIAK

73138 Img00167 171 >a V 2 3 - Rys. 3.25-1. Schemat warstwowej diody germanowej:

M Feld TBM153 4.1. Przecinanie prętów walcowanych, ciągnionych, kształtowników oraz blach153 RYS. 4.

Photo0002 3 A Rys. 7.25. Schemat rotacyjnej sprężarki łopatkowej 1 — kadiub sprężarki z kanałami wod

368 2 8. TURBOGENERATORY I UKŁADY ELEKTRYCZNE W ELEKTROWNIACH PAROWYCH Rys. 8.25. Schemat układu ele

DSCF2105 (2) 1 Schemat układu do wzorcowania siłomierza przedstawiono na rys. 2.25. Rys,. 2.25. Sche

wdk 4 Rys, 25 Schemat ujmowania wody z potoku górskiego za pomocą studni kopanej / — studnia, 2 - o

OMiUP t2 Gorski(4 Kurs rzeczywisty Rys. 7.25. Schemat blokowy procesu sterowania statkiem sygnału sp

Img00167 171 >a V 2 3 - Rys. 3.25-1. Schemat warstwowej diody germanowej: i — k

Img00167 171 >a V 2 3 - Rys. 3.25-1. Schemat warstwowej diody germanowej: i — k

34 (448) 36 amyloza glikogen Rys. 25. Schematy fragmentów cząsteczek podstawowych

więcej podobnych podstron