157 3

310

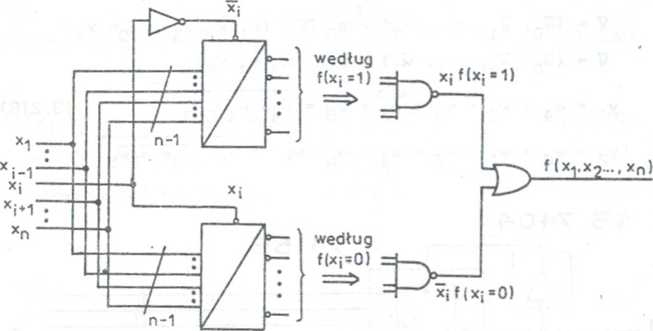

Rys. 3.96. Realizacja układów kombinacyjnych na dekoderach/demultiplekserach według dekompozycji Shannona

W podsumowaniu warto zauważyć, że zarówno multiplekserów jak i dekoderów/demultiplekserów - jako modułów w procesie syntezy układów kombinacyjnych - nie należy stasować bezkrytycznie, lecz każdorazowo powinno się rozważyć opłacalność tego typu rozwiązania. Pamiętając, że z jednej strony konfiguracje z powyższymi modułami mogą mieć takie ząlety jak: jednorodność układowa, mniejsza liczba wymaganych układów scalonyah, większa niezawodność (bo mrfiejsza liczba połączeń „zewnętrznych), możliwość programowania zewnętrznego i łatwe diagnozowanie z pgwodu regularności połączeń, to z drugiej strony mają także i wady takie jak: wyżśza cena rynkowa i możliwość wystąpienia hazardu (patrz rozdz. 3.10).

Stosowanie multiplekserów i dekoderów/demultiplekserów nie w pełni podlega formalnym regułom i osiągnięty rezultat w dużym stopniu może zależeć od wprawy i spostrzegawczości projektanta. W sczególności dotyczy to przypadków zdekomportowanej realizacji funkcji.

Ponadto, o czym warto pamiętać, efektywne metody realizacji układów kombinacyjnych jednowyjściowych na bazie multiplekserów nie przenoszą się niestety na przypadek układów wieIowyjściowyćh. W tym ostatnim, rozwiązania » multiplekserowe wymagają oddzielnej realizacji poszczególnych funkcji, c’-» szczególnie w przypadku większej liczby funkcji (wyjść), przekreśl? sensowność tego typu rozwiązania.

3.7. Projektowanie układów kombinacyjnych z wykorzystaniem cyfrowych układów LSI

3.7.1. Układy z pamięciami stałymi

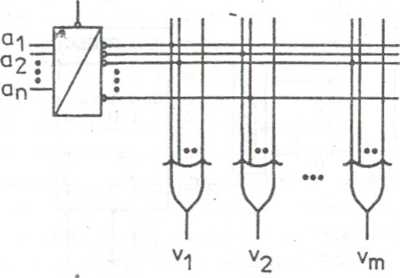

Dekoder w połączeniu z bramkami sumującymi odpowiednie wyjścia realizuje funkcje przełączające bezpośrednio na podstawie ich tabel wartości (zbiorów jedynek bądź zer funkcji - rozdz. 3.6.2). Elementem, który działa w identyczny sposób, ale nie wymaga już żadnych dodatkowych bramek (zazwyczaj) jest pamięć stała ROM (PROM, EPROM, EAPROM - patrz rozdz. 2.5.5), czyli pamięć z której możliwy jest

a)

b)

Rys. 3.97. Pamięć stała: a) schemat funkcjonalny,' b) uproszczone

oznaczenia matrycy połączeń

Wyszukiwarka

Podobne podstrony:

9.Sposoby opisu i realizacji układów kombinacyjnych. 10. Przerzutniki monostabilne oraz bistabilne

proces skrawania toczenie A-A RYS. 1.5. Schemat realizacji procesu skrawania na przykładzie toczenia

MG 86 V VParametry czasowe układów kombinacyjnych Układ cyfrowy nie może odpowiadać na zmianę sygna

291 [1024x768] 300 ROZTWORY I RÓWNOWAGI FAZOWF.Równowagi ciecz—paradla układów dwuskładnikowych Na r

80 (102) 30 a impulsu w jednym z trzech pierwszych układów (pokazanych na rys. 41) zależy od kąta mi

87 (96) 172 Ze względu na rozrywanie blach w przekroju 1-1 (rys. 11.36) należy spełnić warunek

15 (107) W przeciwieństwie do układów kombinacyjnych, stan na wyjściu układu sekwencyjnego w określo

88053 skanuj0022 (96) Rys. 4.387. Konwerter kodu +3 Graya na kod 1 z 10 kolektorem i dopuszczalnym n

mech2 166 339 .330 339 .330 Warianty układów pokazano na rys. 246-248, a dane do obliczeó w tabeli 3

mech2 166 339 .330 339 .330 Warianty układów pokazano na rys. 246-248, a dane do obliczeó w tabeli 3

127 3 248 Rys. 7.6. Zespół 1: a) standardowy segment sieci działań, b) realizacja układowa czyi i A

128 2 250b) Rys. 7.7. Zespól 2A: a) standardowe segmenty sieci działań, b) realizacja układowa 1 •

132 2 258 Rys. 7 realizacja układowa Eliminując występowanie dwóch adresów lokalnych w jednej

147 3 2S8 / y1 = SG, y2 = SD. Xj = m0, x2 = mi * x3 d x4 = c0’ x5 = C1‘ (7.64) Realizacja układowa

więcej podobnych podstron