wykl01

Architektura komputerów

Dr inż. Zbigniew Lach

konsultacje: środa, 10:00-11:00 piątek, 14:00-15:00

Literatura

• CHALK B.S., Organizacja i architektura komputera, Warszawa, WNT, 1998

• BIERNAT J., Architektura komputerÓN, Wrocław, Oficyna Wydawnicza Politechniki Wrocławskiej, 2002 (wyd. III).

' Ą. -I ić:.i W . Omamiacie i architektura systemu ■ 11 ■ l 'i wary dna, W NT, 2003

• KOMOROWSKI W., Architektura komputerÓN, Wrocław, Oficyna Wydawnicza Politechniki Wrocławskiej, 1986

Literatura dodatkowa

• SILBERSCHATZ A., GALVIN P.B., Podstawy systemów operacyjnych, Warszawa, WNT, 2000.

• POJĘCIE ORGANIZACJI I ARCHITEKTURY KOMPUTERA

• STRUKTURY POŁĄCZEŃ WEWNĘTRZNYCH

• PAMIĘĆ GŁÓWNA, PODRĘCZNA

• PRZERWANIA, BEZPOŚREDNI DOSTĘP DO PAMIĘCI

• ARCHITEKTURY PROCESRÓW

• SYSTEMY WIELOPROCESOROWE

• SYSTEMY O ZREDUKOWANEJ LICZBIE ROZKAZÓW

• PRZETWARZANIE RÓWNOLEGŁE I WEKTOROWE

• URZĄDZENIA WEJŚCIA-WYJŚCIA, INTERFEJSY

• PAMIĘĆ ZEWNĘTRZNA

Komputer = urządzenie tutom* tyczne przetwtnąjąee dtne według programu.

Podstawowe cechy komputer*;

- uniwersalność (ten sam sprzęt realizuje różne programy przetwarzania)

- elastyczność (łatwa zmiana fisnkcji przez wymianą programu)

- zdolność podejmowania decyzji _

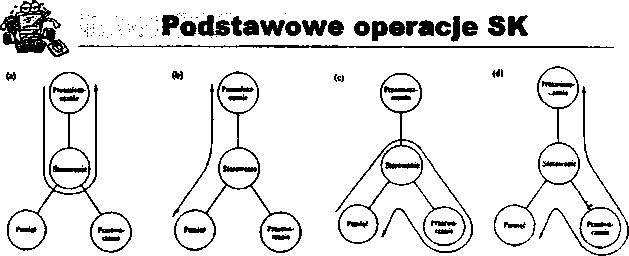

Cztery mołlh-» rnrtoąfo fsneracil systemu komputerowego:

< i System k. = urządzenie do przenoszenia danych,

< i System k. = urządzenie do przechowywania danych,

I i System k. = urządzenie obejmującego przetwarzanie denych przechowywanych,

< I System k. = urządzenie przetwerzające dane przychodzące z otoczenia i

przochowywene

Podstawowe funkcje, któm sits

I i przetwarzanie danych; ii przechowywanie denych;

* i przenoszenie denych;

* i sterowanie.

Postulaty von Neumanna;

4 £ Po pierwsze, ponieważ urządzenie to jest przede wszystkim komputerem, najczęściej będzie wykonyweło elementarne operacje arytmetyczne -dodawanie, odejmowanie, mnożenie I dzielenie (+, -, x, i). Jest więc rozsądne, że powinno posiadać wyspecjalizowane „organy" do wykony,v tych operacji.

Obecnie każdym przypadku Istnieje centralna, arytmetyczna część urządzenia, co oznacza występowanie pierwszej specyficznej części komputera; CA,

4 (• Po druoia. logiczne sterowanie urządzeniem, to znaczy odpowiednie szeregowenie jego operacji, może być nejefaktywniej reeiizowane przez centralny organ sterujący. Jeśli urządzenie me być elastyczne, to znaczy możliwie uniwersalne, należy rozróżniać epacyficzne rozkezy związane z określonym problemem I ogólne „orgeny" sterujące dbejące o wykonanie tych rozkazów - czymkolwiek by one nie były. Te pierwsze muszą być w jakiś sposób przachowywene; te drugie - reprezentowane przez określone działające części urządzenia.

Przez sterowanie centralne rozumiemy tylko tę ostatnią funkcję, a „orgeny", które ją reeiizują, tworzą drugą SBecyfiCitią gęść. urządzenia: £&

Po trzecie, jakiekolwiek urządzenie, które ma wykonywać długie i skompiikowene sekwencje działań (w szczególności obliczenia), musi mieć odpowiednio dułą pamięć... Rozkazów klsrujących rozwiązywaniem skomplikowanego problemu może być bardzo dużo, zwłaszcza wtedy, gdy kod jest przypadkowy (a tak jest w większości przypadków). Muszą one być pamiętane... W każdej sytuacji całkowita pamięć stanowi trzecia, specyficzna cześć urządzenia; M.

Trzy specyficzne części CA, CC oraz M odpowiedają neuronom skojarzeniowym w systemie nerwowym czlowieke. Pozostają do przedyskutowenie równoważniki neuronów sensorycznych (doprowadzających) i motorycznych (odprowadzających). Są to organy wejście i wyjścia naszego urządńnia. Urządzenie musi mieć możliwość utrzymywania kontaktu z wejściem i wyjściem z pomocą specjalistycznego narzędzie. Narzędzie to będzie nazywane zewnętrznym narzędziem rejestrującym urządzenia: R.

Koncepcja von Neumanna

Architektura von Neumanne wykorzystuje trzy kluczowe zasady:

41 Dane i rozkazy są przechowywane w tej samej pamięci umożliwiającej zapis i odczyt

< I Zawartość tej pamięci może być adresowana przez wskazanie miejsca, bez względu na rodzaj zawartych tam denych.

41 Wykonywanie rozkazów następuje w sposób szeregowy (z wyjątkiem określonych, szczególnych przypadków), rozkaz po rozkazie.

WNIOSEK

Cały program test szeregiem (sekwencją) kroków. W każdym z tych kroków jest wykonywane ne danych pewna operacja arytmetyczna lub logiczna.

Dla każdego kroku jest wymagany nowy zestaw sygnałów sterujących.

-j f- Po czwarta, urządzenie musi być wyposażone w organy przenoszące ... informację z R do swoich specyficznych części C i M. „Organy" te stanowią jego wejście, a więc czwarta, specyficzna cześć: I. Zobaczymy, że najlepiej jest dokonywać wszystkich przeniesień z R (poprzez I) do M, a nigdy bezpośrednio do C...

Ą f- Po piąte, urządzenie musi mieć „orgeny" służące do przenoszenia ... ze swoich specyficznych części CIH do R. Organy te tworzą jego wyjście, a więc oiata specyficzna cześć: O. Zobaczymy, że znśw najlepiej Jast dokonywać wszystkich transferów z M (poprzez O) do R, nigdy zaś bezpośrednio z C...

Umiejscowienie części maszyny von Neumana;

< > System k. = urządzenie do przenoszenia danych (a),

< i System k. - urządzenie do przechowywania danych (b),

< I System k. = urządzenie obejmującego przetwarzanie danych

przechowywanych (c),

I i System k. = urządzenie przetwarzające dane przychodzące z otoczenia i przechowywane (d).

Cztery możliwe rodzaje operacji systemu komputerowego:

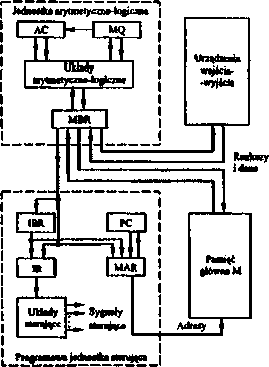

Przykład architektury wg. von Neumana

Główne składniki strukturalne komputera wo. von Neumana:

Rejestrator

Urządzenie wejścia - wyjścia

Jednostka arytmetyczno - logiczna

Pamięć

główna

Programowa

jednostka

sterulaca

Organizacja i architektura

Przy opisywaniu systemów komputerowych często czynione jest rozróżnienie między architektury komputera a jego organizacją. Chociaż precyzyjne zdefiniowanie tych pojęć jest trudne, jednak w literaturze istnieje zgoda co do zagadnień, których dotyczą.

-Jf- Architektura komputera odnosi się do tych atrybutów systemu, które są widzialne dla programisty. Atrybuty te mają bezpośredni wpływ na logiczne wykonywanie programu.

Przykładami atrybutów architektury są np. : lista rozkazów, i i:: i j bitów wykorzystywanych do prezentacji różnych typów danych (np. liczb czy znaków), mechanizmy wejścia-wyjścia oraz metody adresowania ,>.■;! ;■ r- i.

■Jfc- Organizacja komputera odnosi się do jednostek wykonawczych i ich połączeń, które stanowią realizację specyfikacji typu architektury.

Do atrybutów organizacyjnych należą rozwiązania sprzętowi niewidzialne dla programisty, takie jak sygnały sterujące, interfejsy między komputerem a urządzeniami peryferyjnymi oraz wykorzystywana technologia pamięci.

Przykład: struktura IAS - cz.l

Jednostka sterująca, jak i ALU zawierają miejsca pamięci zwane rejestrami:

fi Reiestr buforowy pamięci

(ang. memory buffer register - MBR). Zawiera słowo, która ma być przechowywane w pamięci, lub też jest wykorzystywany do pobierania słów z pamięci.

O Reiestr adresowy pamięci

(ang. memory address register - MAR). Określa adres w pamięci dotyczący słowa, które ma być zapisane w rejestrze MBR lub z niego odczytane.

O Reiestr rozkazów

(ang. instruction register - IR). Zawiera 8-bitowy kod operacyjny rozkazu, który jest wykonywany.

O Buforowy relestr rozkazów

(ang. instruction buffer register - IBR). Jest wykorzystywany do czasowego przechowywenie podręcznego rozkezu pochodzącego ze słowa w pamięci.

O Licznik programu

(ang. program counter - PC).

Zawiera adres następnej pary

rozkazów, która ma być pobrana z pamięci.

O Akumulator (ACJ I rejestr mnoźenia-dzlelenia

(ang. multlpller-quotler - MQ). Wykorzystywane do czasowego

przechowywania argumentów i

wyników operacji prowadzonych przez ALU.

JMftettlta centrala*

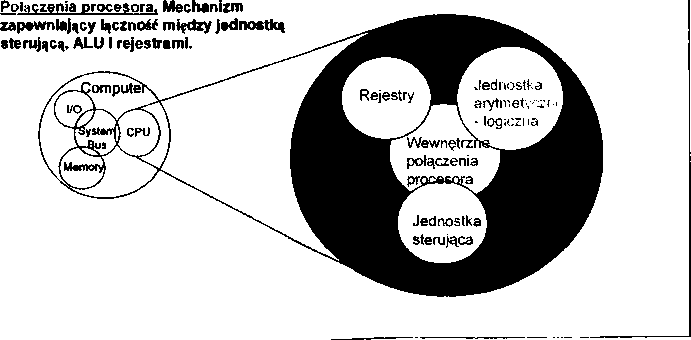

Struktura systemu komputerowego

Istnieją cztery główne składniki strukturalne komputera:

t i Jednostka centralna fCPUt. Steruje ona działaniem komputera i realizuje jego funkcję przetwerzania danych (tzw. procesor).

O Pamięć główna. Przechowuję dane.

4 i Weiścia-wyiście. Przenosi dane między komputerem a jego otoczeniem zewnętrznym.

4 i Połągęnia systemy. Mechanizmy zapewniające łączność między procesorem, pamięcią główną a wejśdem-wyjśclem.

Architektura SK

Architektura współczesnych systemów komputerowych

Struktura systemu komputerowego

Cztery główne składniki strukturalne komputera:

Struktura systemu komputerowego

Crtery główne składniki strukturalna komputera!

CPU

|

i «n |

i mak i |

|

r»n |

| MBK | |

|

tsa |

| UD AK | |

|

|uobk| |

l/O Mndule

aczenie pojęcia programu

Memory

rc m Prufnui cwiakr 1K ■ łutrerilim rrgfcter MAK ■ Mcmor) aMrtu regfcdcr MBK ■ Muwr> buffer rcgiUer M)AK* V0 addlreu npatcr BOBU* UOtralfcrftghfcr

Wprowadzenie pojęcia „program” wynika z założenia, że zamiast zmieniać połączenia w sprzęcie, znacznie łatwiej jest jedynie doprowadzić do tego sprzętu nową sekwencję kodów. Każdy kod jest w rezultacie rozkazem, zaś odpowiednia część urządzenia interpretuje każdy rozkaz i generuje sygnety sterujące. W celu odróżnienie tej nowej metody programowania sekwencja kodów lub rozkazów nazywana jest oprogramowaniem (ang. software).

Podstawowy zestaw elementów opisu współczesnego systemu komputerowego

Struktura CPU

Istnieją cztery główne składniki katdei jednostki centralnej;

i I Jednostka sterująca. Steruje działaniem procesora I przez to komputera

O

O

O

Jednostka arvtmetvczno-loaiczna (ALU). Realizuje funkcję przetwarzania danych przez komputer.

Rejestry. Realizują wewnętrzne przechowywanie danych w procesorze.

Działanie systemu komputerowego

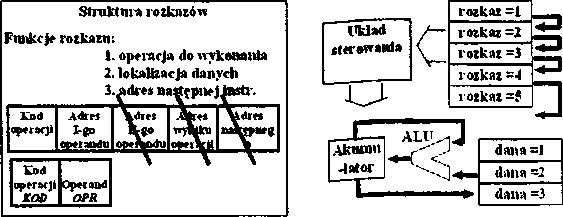

Podstawowym zadaniem komputera jest wykonywanie prooramu. Program przeznaczony do wykonania składa się z zestawu rozkazów przechowywanych w pamięci. Jednostka centralna realizuje pracę, wykonując rozkazy wyszczególnione w programie.

relcn Oyde taccutc ( yefe

Najprostsze jest rozpatrywanie przetwarzania rozkazów w

dwóch krokach: procesor _

odczytuje (pobiera) rozkaz z pamięci, a następnie wykonuje go.

Pobieranie rozkazu jest powszechną operacją, dotyczy każdego rozkazu i polega na odczytaniu rozkazu z pamięd.

Wykonywanie rozkazu może zawierać kilka operacji i zależy od natury rozkazu.

Przetwarzanie wymagane dia pojedynczego rozkazu jest nazywane tykiem m»ta>u.

rozkazu

•J f- procesor pobiera rozkaz z pamięci

i f procesor interpretuje rozkaz i przeprowadza wymagane działanie. Ogólnie działania te można podzielić na cztery kategorie:

O Procesor-pamieć. Dane mogą być przenoszone z procesora do pamięci iub z pamięci do procesora.

O Procesor-weiśde-wyjście. Dane mogą być przenoszone z otoczenia iub do niego, przez przenoszenie ich między procesorem a modułem wejścia—wyjścia.

O Przetwarzanie danych. Procesor może wykonywać pewne operacje arytmetyczne iub logiczne na danych.

O Sterowanie. Rozkaz może określać, że sekwencja wykonywania ma być zmieniona.

■J (• Wykonywanie rozkazów może zawierać kombinacje tych działań.

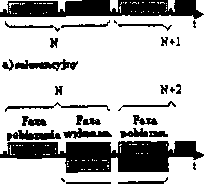

Cykl rozkazu

Cykl rozkazu

J!m Fm Fam

polkkzuiiaw^nMm iMUam.

N+l

a) z f npoUmoiiun

■jfc. Na początku każdego cyklu rozkazu procesor pobiera rozkaz z pamląci. W typowym procesorze do śledzenia, który rozkaz ma być pobrany, służy rejestr zwany licznikiem programu (PC). Jeśli procesor nie otrzyma innego polecenia, to powoduje inkrementację licznika PC po każdym pobraniu rozkazu I wykonuje następny rozkaz w ciągu

^ Pobrany rozkaz jest następnie ładowany do rejestru w procesorze zwanego rejestrem rozkazu (IR). Rozkaz ten ma formą kodu binarnago określającego działanie, które ma podjąć procesor. Procesor Interpretuje rozkaz i przeprowadza wymagane działanie.

Przykład działania SK - cz.l

Załgjęnlą:

< > Procesor zawiera akumulator (AC) służący do czasowego

przechowywania danych.

I > Zarówno rozkazy, jak i dane są słowami 16-bitowymi.

< > Pamięć jest zorganizowana przy użyciu pozycji (iub słów) 16-bitowych.

Format rozkazu wskazuje, że występuje 2* =16 różnych kodów operacji, a liczba słów w pamięci możliwych do bezpośredniego zaadresowania wynosi 212 = 4096 (4 K).

A 1 Kod opcnsji j Atkes ~ |

(b) format liczby całkowitej;

(c) wewnętrzne rejestry

Licaak todtwów (PC) - •drei rozkazu R4«atr rodaafrw <1R) *•wykonywany rozkaz AkuiimlłóOf (AC) *■ tymcaaowe przechowywanie

(d) częściowa lista kodów operacji

D 0001-ŁaddACspamt«ęl OOiO-ZłpittACwpwm^d 010l • Dodjy z pamięci do AC

Leoenda:

Mwintry

CK R^tcrii

CPt: RckIsIlts

|

MU\ |

1 0 4 0 |

1 I) 0| IV |

łDO |

19 4 0 |

* 0 0| Vi | ||||

|

Wl |

TTTT |

1 |

AC |

1l>I |

< y .i i |

1) 11 1) ^ |

AC | ||

|

w |

2 0 4 1 |

19 4 0 |

IK |

łl)„! |

2 0 4 1 |

1 9 4 (1 |

!K | ||

|

j | |||||||||

|

040 |

0 0 0 * |

[J_0 0 | MAR |

940 |

(I 0 U 1 |

J |

940 1 MAR | |||

|

941 |

Ó (1 0 2 |

•Ul |

0 0 U 2 | ||||||

|

SlŁ’p I |

Step 2 | ||||||||

|

M amury |

C PI Rcgisim |

‘McnMłrj |

CPt: Ki>|>i!.li'r« | ||||||

|

UKI |

[040 |

1 0 IIIV |

400 |

19 4 0 |

.i u m*. | ||||

|

MW |

5 V 4 | |

(1 (i O 1 |

AC |

101 |

ś y 4 i |

0 (i 0 5 |

a‘ | ||

|

vi2 |

2 9 4 1 |

5 9 4 1 |

IK |

w: |

2 V 4 I |

( |

5 9 4 1 | ||

|

'MCI |

0 (10 1 |

1301| MAR |

940 |

0 0 U 4 |

*' - c—- | ||||

|

y-łt |

0 0*2 |

•Ul |

U 0 (i 2 | ||||||

|

9 4 11 MAK | |||||||||

|

Sap * |

Sk'p4 | ||||||||

|

Mvrrmry |

C l*l Rrehtrrs |

MfiTMin |

OH Renisurs | ||||||

|

MKI |

19 4 0 |

1 0 21IV |

100 |

i y 4 o |

4 0 21 IM. | ||||

|

VII |

nrrT |

0 9 0 5 |

AC |

401 |

TTTTT |

0 O 0 5 |

AC | ||

|

V>2 |

2 U A 1 |

—» |

2 V 4 1 |

IK |

M>2 |

2 0 4 1 |

2 9 4 1 |

IK | |

|

\ | |||||||||

|

040 |

0 0 0 5 |

302I MAR |

940 |

0 0 0 1 |

94 1 : MAR | ||||

|

04 i |

0 0 0 2 |

‘Ul |

II 0 rl i | ||||||

Stop 5

■Sicpli

Licznik rozkazów (PC)

■ adres rozkazu

Rejestr rozkazów (IR)

■ wykonywany rozkaz

Akumulator (AC)

= tymczasowe przechowywanie

0001

= ładuj AC z pamięci 0010

a zapisz AC w pamięci 0101

= dodaj z pamięci do AC

Stany cyklu rozkazu

Obliczanie adresu rozkazu dat). Określenie adresu następnego rozkazu przeznaczonego do wykonania. Zwykle polega to na dodaniu ustalonej liczby do adresu poprzedniego rozkazu. Jeśli na przykład każdy rozkaz zawiera 16 bitów, a organizacja pamięci przewiduje słowa 16-bitowe, to dodaje się 1 do poprzedniego adresu. Jeśli w pamięci przewidziano bezpośrednie adresowanie 8-bitowych bajtów, to dodaje się 2 do poprzedniego adresu.

Pobieranie rozkazu Hf). Wczytanie rozkazu z pamięci do procesora.

Dekodowanie ooeracll rozkazu (iod). Analizowanie rozkazu w celu określenia rodzaju operacji, które ma byś przeprowadzona, oraz argumentu (argumentów).

Obliczanie adresu argumentu foac). Określanie adresu argumentu, jeśli operacja odnosi się do argumentu znajdującego się w pamięci iub dostępnego przez wejście-wyjście.

Pobieranie argumentu (of). Pobranie argumentu z pamięci lub z we-wy.

Operacja na danych Ido). Przeprowadzenie operacji wskazanej w rozkazie.

•J Przechowanie argumentu fos). Zaplsenle wyniku w pamięci iub skierowanie go do wejścia-wyjścia.

Graf stanów cyklu rozkazu

Dla danego cyklu rozkazu pewne stany mogą być zerowe (mogą nie występować), Inne zaś mogą występować częściej niż raz.

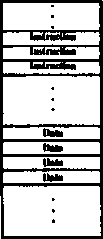

Mernorr

CPt

ImlrudiM*

l*4rudi«ii

1. MAR <-PC, PCi-PC+l

2. 1R+4>AXE (KOD)

3. MAR <-PC, PC<-PC+J

4. MBRl<-DAXE (OPRrf

5. MAR <-PC, PC<-PC+1

6. MBR„<-I)AXE (OPRrf *. M\R<-MBR

S. A<-DANE

u

Praktycznie we wszystkich komputerach przewidziano mechanizm, za pomocą którego inne moduły (wejśde-wyjście, pamięć) mogą przerwać normalne przetwarzanie danych przez procesor.

( y )

|

ł | ||

|

Pobierz nutępoy rozkaz |

Cykl pobierania | |

|

1 Y |

1 | |

|

Wyknuy rozkaz |

Cykl wykonywania | |

|

Prtcfwtoia | ||

|

ńHćSówAhe..... |

(Przerwania | |

|

łdazwolooe | ||

|

Sprawdź, | ||

|

czy nie ma przerwania; przetwórz |

Cykl pizefwaaia | |

|

przerwanie | ||

Przerwania

^ Przy wykorzystaniu przerwań procesor może być angażowany w wykonywanie innych rozkazów w czasie, gdy jest realizowana operacja wejćcia-wyjśda.

j t Program użytkowy nie musi zawierać jakiegoś specjalnego kodu w związku z przerwaniami; procesor i system operacyjny są odpowiedzialne za zawieszenie programu użytkowego, a następnie powodują powrót do tego samego punktu.

3 £• Aby dostosować się do przerwań, do cyklu rozkazu jest dodawany cykl przerwania

sekwencyjne przetwarzanie przerwań przetwarzanie zagnieżdżonych przerwań

Architektura SK

Uwagi uzupełniające

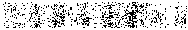

hierarchiczna

Komputer jest złożonym systemem hierarchicznym System hierarchiczny jest układem wzajemnie powiązanych podsystemów, z których każdy również ma strukturą hierarchiczną, od poziomu najwyższego aż do osiągnięcia najniższego poziomu - podsystemu elementarnego.

•J £ Hierarchiczna struktura złożonych systemów ma podstawowe znaczenie zarówno dla projektowania, jak i ich opisu.

•J £ Na każdym poziomie system obejmuje zespól składników i ich wzajemne zależności.

-) Na każdym poziomie zachowanie zależy jedynie od uproszczonych, abstrakcyjnych własności następnego i/lub poprzedniego poziomu.

■J £ Na każdym poziomie należy określić strukturę i funkcje składników systemu przy czym:

Struktura to sposób wzajemnego powiązania składników.

Punkcie określają działanie poszczególnych składników jako części struktury.

Cztery poziomy, opisu SK - cz I

Opis olobalneł struktury systemu

l i definiuje całościowo strukturę systemu komputerowego il definiuje główne składniki struktury O procesory (> moduły kontrolne O moduły pamięci (p strukturę połączeń wewnętrznych

< l opisy są „statyczne' z zastosowaniem podejścia typu "biack box'

Opis pwlornw procesora

< ł definiuje właściwości architektury

O interfejsy O zestaw Instrukcji O reprezentacja danych

< I bardziej szczegółowa definicja poszczególnych

składników

C 3 Interfejs (powiązanie)

Opis poziomu rejestrów

definiuje wewnętrzne operacje elementów z poziomu procesora

11 definiuje elementy podstawowe struktury poziomu opisu:

() rejestry

() liczniki

() pamięci

() jednostki arytmetyczno logiczne (> sygnały synchronizujące

O elementy konwencjonalnej logiki kombinacyjnej

Opis poziomu bramek logicznych

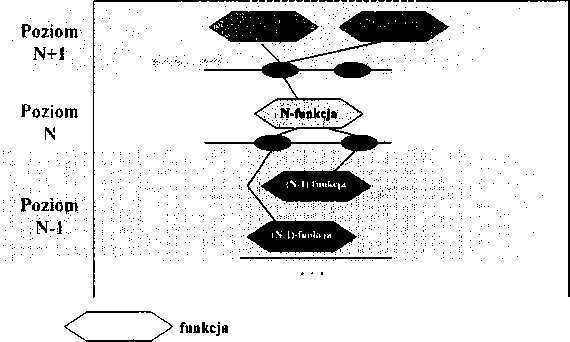

Taksonomia Flynna - cz. I

Taksonomia Fiynna (ogłoszona w 1966)

Jest najpopularniejszą i najbardziej ogólna metodą opisu systemów komputerowych należących do klasy opisów globalnych, lej podstawowe cechy jest wykorzystanie przy opisie podejścia blokowego.

Dowolny system komputerowy można zakwalifikować do jednej z czterech kategorii:

9 SISD: Single instruction streem, single data stream

• SIMD: Single instruction stream, muitiple data streams

• MIMD: Muitiple instruction streams, multipie data streams

• MISD: Multipie instruction streams, single data stream

? " Taksonomia Flynna - cz. III

Irsmiciion DalJ

MIMD: Multipie instniction streams, multipie data streams

MISD: Multipie instruction streams, single data stream

Taksonomia Flynna - cz. II

SISD: Single instruction stream, single data stream

Data

ln&iructK>n DaU

|

Ccntrol |

5»łrcam |

Procctfor | |

|

Lnu |

SIMDi Single instruction stream, multipie data streams

Ocena wydajności SK

U

Przepustowość pamięci (ang. Memory bandwidth) jest maksymalną wartością, wyrażoną w bitach na sekundą, z jaką informacje mogą być transmitowane z lub do głównej pamięci

Jednostka MIPS (ang. mllllons of Instructionsper second)

Znormalizowana jednostka MIPS. Jako referencji zwykło się używać maszyny VAX 11-780 1 MIP

f«wi? MiPS

WmRiifwnai

UmatawMaaiM

IAP3 Hut

Jednostka MFLOPS (ang. mllllons of floating point operations per second)

Zaliczenie przedmiotu

31 Obowiązuje forma zaliczenia: ■J £- Terminy kolokwiów:

1. 27 listopada

2. 22 stycznia

^ 51 punktów na 100 - ocena zalicząjąca

Wykład 2

Połączenia systemu komputerowego

Struktura pttfąc^eń ^ cz. I

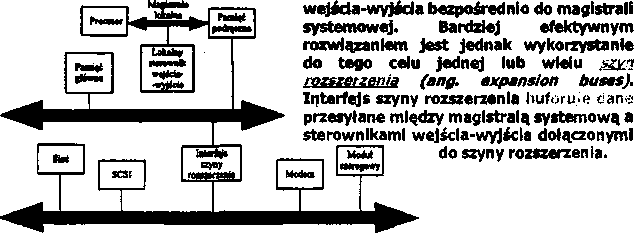

Komputer jest zestawem zespołów lub modułów trzech podstawowych typów (procesor/ pamięć, wejście-wyjście), które komunikują się wzajemnie. W rezultacie komputer jest siecią obejmującą podstawowe moduły. Muszą więc istnieć ścieżki łączące moduły.

* Zbiór ścieżek łączących moduły jest nazywany struktura połączeń. Projektowanie tej struktury zależy od wymiany, która musi zachodzić między modułami.

Pamięć-

|

Rcnel |

Memory .V Words |

|

Writc _ | |

|

Addrcss ^ |

o II Ul III |

|

\-i 11 mj.ii | |

|

Datii ) | |

Moduł pamięci składa się zwykle z N słów o jednakowej długości. Każde słowo ma przypisany jednoznaczny adres numeryczny (0, I, ..., N - 1).

-- Słowo może być odczytane z pamięci

/ lub do niej zapisane. Rodzaj operacji jest wskazywany przez sygnały sterujące .czytaj* lub „zapisz”. Lokacja, której dotyczy operacja, jest wskazywana przez adres.

Struktura syśtehhu komputerowego

Cztery ołówne składniki strukturalne komputera:

|

Rnul _ |

I/O Module |

|

Wpite | |

|

-► | |

|

Address ) |

.1/ Ports |

|

liilrrnal \ | |

|

Dala > | |

|

i:\lcrnal \ | |

|

Dillrt > |

litłcrual

Dała

Kslrrnal

IKihi

Intrrrapi

SignaU

>

>

>

Moduł weiścia-wyiścia.

Istnieją dwie operacje: zapisu i odczytu. Ponadto moduł wejścia-wyjścia może sterować więcej niż jednym urządzeniem zewnętrznym. Możemy określić każdy z interfejsów z urządzeniem zewnętrznym jako port i nadać każdemu z nich jednoznaczny adres (np. O, I1). Istnieją poza tym zewnętrzne ścieżki danych służące do wprowadzania i wyprowadzania danych z urządzenia zewnętrznego. Wreszcie moduł wejścia-wyjścia może wysyłać sygnały przerwania do procesora.

Procesor.

Procesor wczytuje rozkazy i dane, wysyła dane po przetworzeniu i posługuje się sygnałami sterującymi do sterowania całą pracą systemu. Otrzymuje też sygnały przerwania.

Struktura połączeń - cz. III

Struktura połączeń musi umożliwiać przesyłanie danych:

O Ż oantied do procesora. Procesor odczytuje z pamięci rozkazy lub jednostki danych.

O Z procesora do oamled. Procesor zapisuje jednostki danych w pamięci.

i» Z urządzeń walida-wyiida do procesora. Procesor odczytuje dane z urządzenia wejścia-wyjścia za pośrednictwem modułu wejścia-wyjścia.

< 1 2 procesora do weHda-wyUda. Procesor wysyła dane do urządzenia wejścia-wyjścia.

i 1 Z urządzeń we1śda-wv1icla do oamled tub na odwrót W tych dwóch przypadkach zezwala się modułowi wejścia-wyjścia na bezpośrednią wymianę danych z pamięcią, bez pośrednictwa procesora, przy wykorzystaniu bezpośredniego dostępu do pamięci (DMA).

Struktura magistrali - cz. I

Unie zawarte w magistrali systemowej można podzielić na trzy grupy funkcjonalne: linie danych, adresów I sterowania. Ponadto mogą występować linie służące do zasilania dołączonych modułów.

Działanie magistrali jest następujące. Jeśli jeden z modułów zamierza wysłać dane do drugiego, to musi wykonać dwie rzeczy:

»*£L. (1) uzyskać dostęp do magistrali

(2) przekazać dane za pośrednictwem magistrali.

Jeśli natomiast zamierza uzyskać dane z Innego modułu, to musi:

(1) uzyskać dostęp do magistrali

(2) przekazać zapotrzebowanie do tego modułu przez odpowiednie linie sterowania I adresowe. Musi następnie czekać, aż ten moduł wyśle dane.

u

Magistrala jest drogą zapewniającą komunikacją między urządzeniami.

Główną cechą charakterystyczną magistrali jest to, że jest ona współdzielonym nośnikiem transmisji (ang. shared transmission medium).

Do magistrali dołącza się wieli! urządzeń, a sygnały wysyłane przez którekolwiek z nich mogą być odbierane przez wszystkie pozostałe urządzenia. Jeśli dwa urządzenia nadawałyby w tym samym czasie, ich sygnały nakładałyby się I ulegały zakłócaniu. W oaiwm i u; może

więc nadawać tylko jedno urządzenie.

Magistrala łącząca główne zespoły komputera (procesor, pamięć, wejścia-wyjście) nazywana jest magistralą systemową. Najczęściej spotykane struktury połączeń komputera wykorzystują jedną lub więcej magistral systemowych.

Magistrala systemowa składa się zwykle z 50 do 100 oddzielnych linii. Każdej linii jest przypisane określone znaczenie lub funkcja.

Struktura magistrali - cz. II

)t Urue.jjn.oydi są ścieżkami służącymi do przenoszenia danych między modułami systemu. Wszystkie te linie łącznie są określane jako danych (ang. data bus). Liczba linii określa szerokość tej szyny. W danym momencie każda linia może przenosić tylko I bit Szerokość szyny danych jest kluczowym czynnikiem określającym wydajność całego systemu.

) (. Linie adresowe są wykorzystywane do określania źródła lub miejsca przeznaczenia danych przesyłanych magistralą. Szerokość szyny adresowej determinuje maksymalną możliwą pojemność pami > .i systemu. Ponadto linie adresowe są również używane do adresowania portów wejścia-wyjścia. Najczęściej najbardziej znaczące bity służą do wybrania określonego modułu na magistrali, natomiast najmniej znaczące bity określają lokację w pamięci lub port wejścia—wyjścia wewnątrz modułu.

[

Unie sterowania używa slą do sterowania dostępem do linii danych i linii adresowych, a także do sterowenla Ich wykorzystaniem. Ponieważ linie danych I adresowe służą wszystkim zespołom, musi istnieć sposób sterowania Ich używaniem. Sygnały sterujące przekazywane między modułami systemu zawierają zarówno r:> !(.<;:>, jak i :iri rs>> , czas (taktujące). Sygnały czasowe określają ważsiMĆ liaaydi Sygnały io,'k.; precyzują operacje, które mają być przeprowadzone.

Linie sterowania magistrali

Typowe llnl« sterowania to linie;

♦ Zapis w garniec!. Sprawia, że dane z magistrali zostają zapisane pod określonym adresem.

< * Odczyt a pamięci. Sprawia, że dane spod określonego adresu są umieszczane

w magistrali.

< ► Zaote do welśda-WYiśda, Sprawia, że dane z magistrali są kierowane do

zaadresowenego portu wejścia-wyjścia.

< 1 Odczyta weiłda-wylida. Sprawia, że dane z zaadresowanego portu wejścia-

wyjścia są umieszczane na magistrali.

11 Potwierdzenie przesyłania (transfer ACK). Wskazuje, że dane zostały przyjęte z magistrali lub na niej umieszczone.

* > Zapotrzebowanie na magistrale (bus reąuest). Wskazuje, że moduł zgłasza

zapotrzebowanie na przejęde sterowania magistralą.

O Przydział magistrali (bus grant). Wskazuje, że moduł otrzymuje prawo korzystania z magistrali.

O jadanie przerwania (intenupt reąuest). Wskazuje, że przerwanie jest zgłoszone.

0 Potwierdzenie przerwanie (Intenupt ACK). Potwierdza, że zgłoszone przerwanie zostało rozpoznane.

1 > Zeear. Wykorzystywany do synchronizowania operacji.

i I Zerowanie (reset). Ustawia wszystkie moduły w stanie początkowym.

; Problem wydajności połączenia

|

"i.•inmj.ii -.u |

*.....^ ' | |

|

Sv. I<4«..i!:4;. M.t.-wa:*. |

. kiliA^l X -Si M>;>i St SI .n!ł !•: *■>! | |

|

V _____ |

Możliwe Jest podłączenie sterowników

Lokalna magistrala łącząca procesor I pamięć podręczną. Może ona wspomagać jedno lub więcej urządzeń lokalnych. Sterownik pamięci podręcznej łączy tę pamięć nie tylko do magistrali lokalnej, ale również do magistrali systemowej, do której są dołączone wszystkie moduły pamięci głównej. Wykorzystanie struktury pamięci podręcznej uwalnia procesor od potrzeby częstego dostępu do pamięci głównej. Dzięki temu pamięć główna może być przesunięta z magistrat lojalnej do systemowej. W ten sposób wejście-wyjście komunikuje się z pamięcią główną przez magistralę systemową, nie kolidując z działalnością procesora.

Magistrala lokalna łączy procesor ze sterownikiem pamięci podręcznej, który z kolei Jest podłączony do magistrali systemową)

współpracującej z pamięcią główną. Sterownik pamięci podręcznej jest zintegrowany z mostem (urządzeniem buforującym) łączącym z magistralą szybką. Wolniejsze urządzenia nadal są obsługiwane przez szynę rozszerzenia z Interfejsem buforującym ruch między szyną rozszerzenia a szybką magistralą._

Zaletą tego rozwiązania jest to, łe szybka magistrala śdślej sprzęga procesor z urządzeniami wąjśda-wyjśda o wysokich wymaganiach, a jednocześnie jest niezależna od procesora. Dzięki temu mogą być tolerowane różnice szybkości procesora i szybkiej magistrali, a takie różne definicje linii sygnałowych.

Typy transferów

f Adria { j (głmwył>V) |

D««

cykli

Opcntj* opln

r-

i

O

J2

’i:*L

Operują odczy*

|

:h ' |

( : | ||

|

L "" |

T |

Otfccyf danych |

2*pte d*nyth |

|

Operami* fśayisadjflkitjwzpłt | |||

|

j Adra |

4*reb |

I Odczyt | |

|

OpmtJa«d«9lp»pUt | |||

|

| Adres |

Osa* |

Ohm |

Om* |

U.

OjMcjiaśc^M

Rodzaje magistral

•H Unie magistralowe mogą być podzielone na dwa rodzaje:

wyspecjalizowane (eng. dedicated)I n»uli: plekscwmię.

f- Unio wysnecłaliipuana jest tnval« przypisana albo jednej funkcji, albo fizycznie okręconym zespołom komputera. Przykładem specjalizacji funkcjonalnej jest zastosowanie oddzielnych, specjalistycznych linii adresów I danych, co jest powszechne w wielu meglstralach.

•J {• Adresy i dane lassa być transmitowane prm *n sa.n .«*< i! '! przy wykorzystaniu linii sterowania określającej ważność adresu (ang. Adress Valld). W tym przypadku każdy moduł ma do dyspozycji określony odcinek czasu na skoplowenle adresu I stwierdzenie, czy jest modułem edresowanym. Adres Jest następnie usuwany z magistrali, a te same połączenia magistralowe są wykorzystywane do przenoszenia danych odczytywanych lub zapisywanych. Ta właśnie metoda używania tych samych linii do wielu celów jest znana jako (ang. time mu/tiptexlng).

i t Sneriallzacia fizyczna (ang. physicaldedlcation) odnosi się do używanja wielu magistral, z których każda łączy tylko określoną grupę modułów. Typowym przykładem jest zastosowanie magistrali wejścia-wyjścia do łączenia wszystkich modułów wejścia-wyjścia.

Arbitraż dostępu do magistrali

We wszystkich systemach, z wyjątkiem najprostszych, więcej niż jeden moduł może potrzebować przejęcia sterowania magistralą.

W określonym czasie tylko jeden moduł może transmitować przez magistralę

Możliwe metody można z grubsza podzielić na:

O Scentralizowali?:, w takim układzie istnieje jedno urządzenie, zwane sterownikiem magistrali lub arbitrem, które jest odpowiedzialne za przydział czasu ne magistrali. Urządzenie to może być oddzielnym modułem lub częścią procesora.

O f ozj: roszone, w takim układzie centralny sterownik nie występuje. Każdy moduł zawiera układy logiczne sterujące dostępem, a moduły współdziałają korzystając z magistrali.

W obu metodach arbitrażu celem jest n/y: ic-r zer ie jednego — albo procesora, albo modułu wejścia-wyjścia - jako Urządzenie nadrzędne (master) może następnie Inicjować transfer danych z Innym urządzeniem, które w tym określonym przesyłaniu gra rolę podrzędną (ang. stave).

Koordynacja czasowa (ang. timing) odnosi się do sposobu, w jaki koordynowane są zdarzenia na magistrali.

Arbitraż synchroniczny

Przy koordynacji synchronicznej występowanie zdarzeń na magistrali jest wyznaczone przez zegar. Magistrala zawiera linię zegarową, którą zegar transmituje regularną sekwencję kolejno zmieniających się zer I jedynek, o takim samym czasie trwania. Cykl zmian linii zegarowej (1-0) jest nazywany cyklem zegara lub cyklem magistrali i określa przedział czasowy. Wszystkie Inne urządzenia dołączone do magistrali mogą odczytywać stan linii zegarowej, a wszystkie zdarzenia rozpoczynają się równocześnie z cyklem zegara.

Addms

Ulic*

Outu

l.iiica

Ack»otvlc<lK« | I

ISA fana. Industrlal Standard Architecturel

8-bitowa magistrala ISA Pierwsze utycie • PC-XT Złącze 62 stykowe Częstotliwość zegara 4.77 MHz 8 linii danych

20 linii adresowych (1 MB pamięci)

6 linii przerwań 2 kanały DMA

16-bltowa magistrala ISA

|

CPU | ||

|

Niemoty | ||

Bu* «lrivcn and glut logie

T

ISA Bas

Keyboard

Bu* 3>lots

Pierwsze utycie - PC-AT oraz Intel 80286 Złącze rozszerzone o dodatkowe 36 styków Częstotliwość zegara 8.33 MHz 16 linii danych

24 linie adresowe (16 MB pamięci)

11 linii przerwań 6 kanałów DMA

Arbitraż asynchroniczny

Przy koordynacji asynchroniczne? występowanie zdarzeń na magistrali jest zaieżne od zdarzenia poprzedzającego. W prostym przykładzie pokazanym na rysunku procesor umieszcza sygnały adresu I odczytu na magistrali. Po pewnym czasie wymaganym do ustabilizowania sygnałów, wysyła sygnał synchronizacji nadrzędnej (master sync - MSYN), wskazując na obecność ważnych sygnałów adresu I sterowania. Moduł pamięci reaguje, wysyłając dane oraz sygnał synchronizacji podrzędnej (s!ave sync - SSYN), wskazujący na odpowiedź.

i > pierwsze użycie w roku 1988 I ł Częstotliwość zegara 8.33 MHz ił 24/32 linii adresowych ił 16/32 linii danych ił kompatybilna z ISA

VESA Video Local Bus

i ł pierwsze użycie w roku 1989 < ł Szybkość zależna od procesora i ł 24/32 linii adresowych i ł 32/64 linii danych i ł współpracowała z ISA lub EISA

|

MSYN | |

-\ | ||

|

SSł N |

H |

4 | |

|

KbuI | | |||

|

Acłdruwi 1 1 .!■■<•« 1 |

k | ||

|

Dulu |

y_ |

b_ | |

I '

ifSSKBiśSIlw

*

PCI (ang. Peripheral Component Interface)

<> pierwsze użyde w roku 1990/ specyfikacja PCI 2.0 w roku 1993 I > częstotliwość zegara 33 MHz (niezależna od procesora)

< I 64 linie adresowe I danych (muHipleksowane) - przy 33 MHz daje to przepustowośd 264 MB/a lub 2/112 Gbtt/s

Architektura typu Desktop

Architektura typu Serwer

Magistrala PCI - struktura - cz. II

Ponadto specyfikacja PCI określa 50 opcjonalnych linii sygnałowych, podzielonych na następujące grupy:

< > Wyprowadzenia przerwania. Są one przewidziane dla urządzeń PCI, które muszą generować zapotrzebowanie na obsługę. Tak jak w przypadku wy-prowadzeń arbitrażowych nie są one wspólne. Każde urządzenie PCI dysponuje własną linią lub liniami przerwań łączącymi ze sterownikiem przerwań.

I) Wyprowadzenia obsługi pamięci podręcznej. Są one wykorzystywane do obsługi pamlęd podręcznych zawartych w procesorach I Innych urządzeniach PCI. Umożliwiają stosowanie protokołu podglądania (snoopy) pamlęd podręcznej.

II Wyprowadzenia rozszerzenia magistrali 64-bitowej. Należą do nich 32 linie multipleksowane adresów i danych. W połączeniu z obowiązującymi liniami adresów I danych tworzą 64-bitową magistralę adresów i danych. Inne linie z tej grupy są używane do interpretowania I określania ważnośd linii sygnałowych przenoszących dane I adresy. Występują tu też dwie linie umożliwiające dwóm urządzeniom PCI uzgodnienie użycia szerokości 64-bitowej.

11 Wyprowadzenia testowania granic JTAG. Unie te umożliwiają realizację procedur testowania określonych w normie IEEE 149.1.

Magistrala PCI - struktura - cz, I

Magistrala PCI może być konfigurowana Jako magistrala 32- lub óó-biruws.

Specyfikacja definiuje 50 linii sygnałowych. Można Je podzielić na następujące

grupy funkcjonalnet

O Wyprowadzenia systemowe. Należą do nich wyprowadzenia zegara I zerowania (reset).

0 Wyprowadzenia adresu i danych. Należą do nich 32 linie multipleksowa iv> adresów I danych. Pozostałe linie w tej grupie są wykorzystywane do Interpretowania I określania ważności linii sygnałowych przenoszących adresy I dane.

1 I Wyprowadzenia sterowania Interfejsu. Służą do koordynowania transakcji I

współdziałania między jednostkami Inicjującymi a docelowymi.

ił Wyprowadzenia arbitrażowe. W przeciwieństwie do pozostałych linii sygnałowych magistrali PCI nie są one liniami współdzielonymi. Każda jednostka nadrzędna PCI ma własną parę linii arbitrażowych, które łączą ją bezpośrednio z arbitrem magistrali PCI.

i I Wyprowadzenia informujące o błędach. Wykorzystywane do informowania o błędach parzystości I Innych.

Działanie magistrali odbywa się w formie transakcji między Inicjatorem (modułem nadrzędnym) a celem (modułem podrzędnym). Gdy Inicjator domaga się sterowania magistralą, określa typ transakcji, która ma być przeprowadzona. Podczas fazy adresu transakcji do sygnalizowania typu transakcji są używane linie C/BE. Rozkazy są następujące:

O potwierdzenie przerwania - Jest rozkazem odczytu przeznaczonym dla urządzenia, które działa jako sterownik przerwań na magistrali KI.

0 cvkl specjalny - jest rozkazem używanym przez inicjatora w celu rozgłoszenia wiadomości przeznaczonych dla jednego lub więcej celów.

O odczyt weiścia-wyiścia. zapis wełścla-wylścia - są używane do przenoszenia danych między Inicjatorem a sterownikiem wejścia-wyjścia. Każde urządzenie wejścia-wyjścia ma własną przestrzeń adresowa. Unie adresowe służą do wskazywania określonego urządzenia oraz do sprecyzowania danych, któro mają być wymienione z tym urządzeniem.

O cykl podwóineoo adresu • jest wykorzystywany przez inicjatora do wskazania, że stosuje on adresowanie 64-bNowe.

. Magistrala PCI - rozkazy - cz. il

0 Odczyt pamięci, linia odczytu pamięci, zwielokrotniony odczyt pamięci, zapis w pamięci, zapis w pamięci i unieważnienie - rozkazy odczytu i zapisu w pamięci są stosowane do precyzowania przesyłania porcji danych (burst of data) trwającego przez jeden lub więcej cykli zegarowych. Interpretacja tych rozkazów zależy od tego, czy sterownik pamięci na magistrali PCI realizuje protokół Pd przeznaczony do przesyłania danych między pamięcią główną a pamięcią podręczną.

1 I odczyt konflouracłi. zapis konfiguracji - dwa rozkazy konfiguracyjne

umożliwiają Inicjatorowi odczytanie i zaktualizowanie parametrów konfiguracji w urządzeniu dołączonym do magistrali Pd. Każde urządzenie Pd może zawierać do 256 rejestrów wewnętrznych, które są wykorzystywane do konfigurowania tego urządzenia podczas Inicjowania systemu.

- arbitraż - cz. I

Magistrala PCI wykorzystuje scentralizowany, synchroniczny rodzaj arbitrażu, w którym każdy moduł nadrzędny ma przypisane unikatowe sygnały zapotrzebowania (REQ) i udostępniania (grant- GNT).

Odpowiednie linie sygnałowe są podłączone do centralnego arbitra, a dostęp do magistrali jest uzyskiwany przez zgodne zgłoszenie zapotrzebowania I udostępniania.

Specyfikacja Pd nie dyktuje szczególnego algorytmu arbitrażu.

Możliwe rozwiązania można podzielić na następujące grupy:

! .pierwszy zgłoszony - pierwszy obsłużony" rozwiązanie cykliczne (round-robin) rozwiązania bazujące na priorytetach

Magistrala PCi - przesył danych

Każde przesyłanie danych magistralą PCI Jest pojedynczą transakcją składającą sią z jednej fazy adresowej oraz jednej lub wielu faz danych.

i i i i i i i i i

■d1 —■■■■■ ■■ ■ Biu TumkUmi 1 1 ----►

Wszystkie zdarzenia są synchronizowane przez opadające zbocza

Impulsów zegarowych, które występują w środku każdego cyklu zegara. Urządzenia magistrali badają linie magistrali w czasie narastania Impulsów zegarowych, na początku cyklu magistrali.

Wyszukiwarka

Podobne podstrony:

Dr inż. Rafał ŁużnyF1 p.109; PN: 10:00-12:00, PT: 11:15-13:15 1 Uwodornienie benze

Recenzenci: mgr inż. Janusz Jasek mgr Janusz Salmanowicz Konsultacja: dr inż. Zbigniew

Recenzenci: mgr inż. Włodzimierz Dymek mgr Czesław Nowak Konsultacja: dr inż. Zbigniew

Systemy wbudowaneSystemy Wbudowane Dr inż. Mariusz Fraś• Konsultacje ■

Modelowanie matematyczne dr inż. Zbigniew Tarapata Wykład nr 5: Modele teorii gier

Modelowanie matematyczne dr inż. Zbigniew Tarapata Wykład nr 5: Modele teorii gier

Modelowanie matematyczne dr inż. Zbigniew Tarapata Wykład nr 5: Modele teorii gier

Modelowanie matematyczne dr inż. Zbigniew Tarapata Wykład nr 5: Modele teorii

Modelowanie matematyczne dr inż. Zbigniew Tarapata Wykład nr 5: Modele teorii

Modelowanie matematyczne dr inż. Zbigniew Tarapata Wykład nr 5: Modele teorii

Modelowanie matematyczne dr inż. Zbigniew Tarapata Wykład nr 5: Modele teorii

więcej podobnych podstron