Laboratorium elektronika

|

Karpisz Dariusz Hefner Sławomir Kocoń Sebastian Koleżyński Jacek Kaszuba Stanisław Janeczko Radosław |

|||

|

Nazwiska i imiona studentów |

|||

Ćwiczenie numer 8 Temat: Badanie bramek CMOS |

WIEiK |

32a |

5 |

|

|

Wydział |

Grupa |

Zespół |

|

|

|

|

||

|

Data |

Ocena |

||

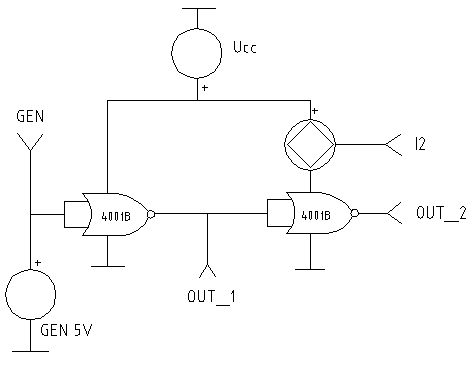

1. Badanie bramek NOR CMOS.

a) układ pomiarowy.

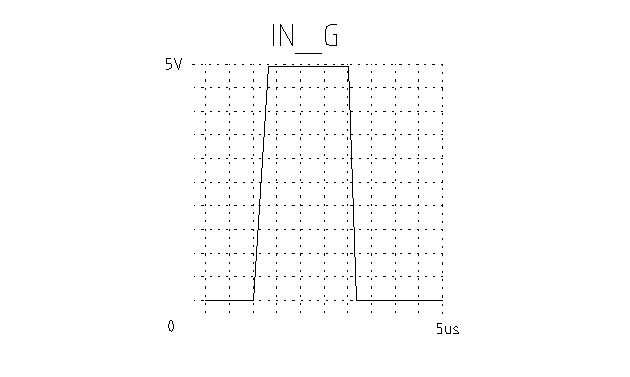

b) wykresy czasowe

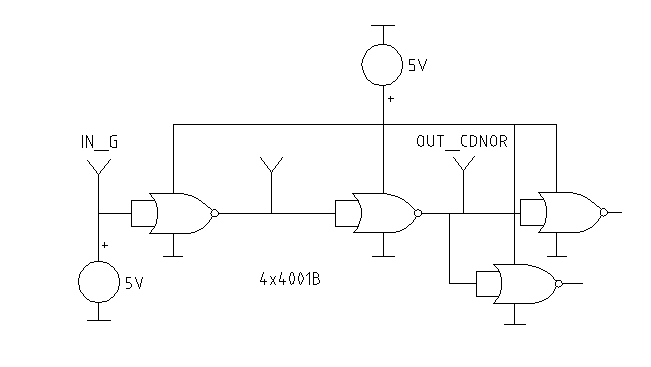

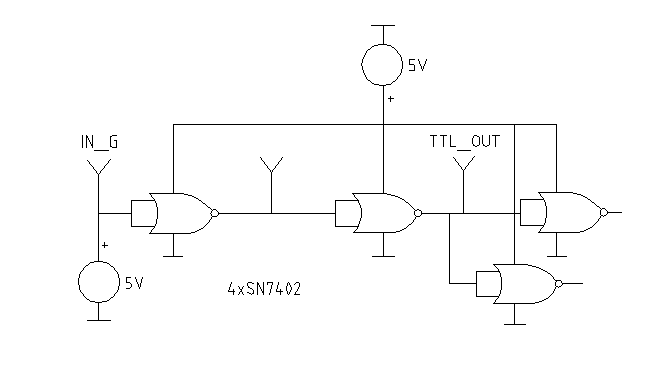

2. Porównanie bramek TTL i CMOS.

a) układ pomiarowy

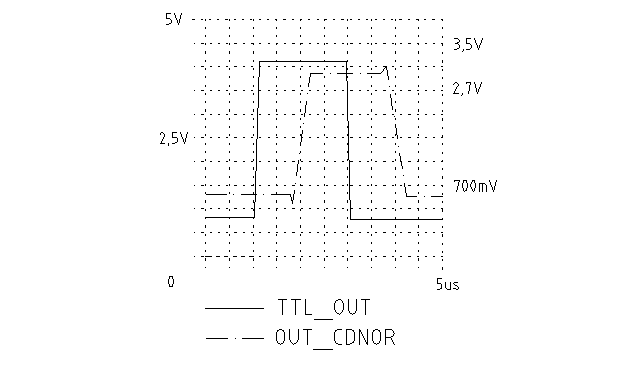

b) wykresy czasowe

3. Wnioski.

Bramki CMOS charakteryzują się szerokim zakresem napięć zasilania oraz zwieraniem wyjścia do masy lub napięcia zasilania. Należy jednak zauważyć, że charakterystyka przełączania bramki CMOS wykazuje obszary liniowe wraz ze wzrostem napięcia zasilania. Zauważmy, że w punkcie pierwszym ćwiczenia w obszarze 3÷8μs przy narastającym UCC , nastąpiło przełączenie bramki NOR przy napięciach progowych tranzystorów MOSFET z kanałem n i p. W tym obszarze oba tranzystory są w stanie nasycenia i płynie duży prąd IDD. Mimo, że bramka CMOS praktycznie nie pobiera prądu w stanie statycznym to przy przełączaniu moc chwilowa jest znaczna. Ma to duże znaczenie przy zwiększaniu częstotliwości przełączania.

Porównując działanie bramki NOR TTL i NOR CMOS możemy stwierdzić, że mimo iż bramka CMOS przełącza od 0V do UCC to jednak czas propagacji jest znaczny i nie nadaje się ona do przełączania sygnałów szybkich. Możemy również zaobserwować powstające przy przełączaniu. Bramka TTL przełącza prawie zgodnie z impulsem zegarowym jednak jej poziomy napięć wyjściowych są ustalone w ścisłych granicach. Dlatego bramki TTL najlepiej stosować do systemów szybkich, natomiast bramki CMOS do systemów wolniejszych, narażonych na zakłócenia i wymagających wyższych napięć zasilania (np. systemów sterowania).

8

UCC [V]

12

10

t [ms]

t [ms]

5

U GEN [V]

t [ms]

10

12

3

8

![]()

2

10

t [ms]

10

3

8

10

![]()

Wyszukiwarka

Podobne podstrony:

MIERNI~1, LABORATORIUM MIERNICTWA ELEKTRYCZNEGO

04 - Przetworniki c-a, miernictwo-Šw.2, Laboratorium Miernictwa Elektronicznego

uklady czasowe, Laboratorium Miernictwa Elektrycznego

04 - Przetworniki c-a, Cw2miern2 - Piotrek, Laboratorium Miernictwa Elektronicznego

Ujemne sprzężenia zwrotne, Ujemne sprzężenia zwrotne, Laboratorium Miernictwa Elektrycznego

C - Statystyczna analiza wyników pomiarów, Lab C e, Laboratorium miernictwa elektronicznego

mier k 18, LABORATORIUM MIERNICTWA ELEKTRYCZNEGO

Miernictwo - Ćw. 3, Automatyka i elektronika, Miernictwo Elektroniczne - Laboratorium, Miernictwo El

C - Statystyczna analiza wyników pomiarów, Lab C g, Laboratorium Miernictwa Elektronicznego

A - Błędy graniczne narzędzi pomiarowych, Cw 1, Laboratorium Miernictwa Elektronicznego

cmos, CMOS, Laboratorium Elektroniki

Laboratorium z podstaw Miernictwa Elektronicznego4

Laboratorium Pomiarów Elektrycznych spr 4, PWR, MIERNICTWO EL. - LABOLATORIUM

Laboratorium Pomiarów Elektrycznych spr 2, PWR, MIERNICTWO EL. - LABOLATORIUM

Uklady scalone CMOS z serii 4000, Elektronika, Noty aplikacyjne

właściwości statyczne termometrów elektrycznych, Laboratorium, Miernictwo przemysłowe

więcej podobnych podstron