6931258584

http ://lay er. uci. agh. edu. pl/ maglay/wrona

1.2 WYMIENNOŚĆ BRAMEK

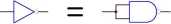

Przy projektowaniu układów cyfrowych należy mieć na uwadze, że za pomocą pewnych rodzajów bramek można utworzyć inne. Na przykład, jeżeli potrzebna jest bramka AND, a mamy do dyspozycji połowę układu ‘00 (cztery dwuwejściowe bramki NAND), możemy zastosować kombinację. Mówiąc ogólnie, wielokrotne użycie jakiejkolwiek bramki odwracającej (np. NAND) pozwala zrealizować dowolną funkcję kombinacyjną. Nie jest to prawdą dla bramek nieodwracających, ponieważ nie można za ich pomocą zrealizować inwertera.

a)

b)

Rys. 1.1 Sposób przedstawienia inwertera za pomocą bramki NAND (a) oraz bramki AND za pomocą dwóch bramek NAND (b)

1.3 MIEJSCE SYMBOLU NEGACJI STANU

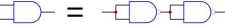

Wyjście bramki AND jest w stanie H, jeżeli oba wejścia są w stanie H. Jeżeli H oznacza „prawdę” to na wyjściu bramki otrzymuje się sygnał „ prawda” tylko wtedy, gdy do obu wejść doprowadzono sygnał „prawda”. Innymi słowy bramka AND wykonuje funkcje AND w logice dodatniej. Podobnie można określić funkcje bramki OR. Co się dzieje, gdy prawda oznacza stan niski? Na wyjściu bramki AND ustala się stan L, gdy którekolwiek z wejść jest w stanie L - to jest funkcja OR! Podobnie, na wyjściu bramki OR ustala się stan L tylko wtedy, gdy oba wejścia są w stanie L -to jest funkcja AND! Można się w tym pogubić. Istnieją dwa sposoby uporania się z tym problemem. Pierwsza metoda polega na wybieraniu bramek, które dawałyby żądany efekt na wyjściu. Jeśli np. chcemy dowiedzieć się, czy którykolwiek z trzech sygnałów wejściowych jest w stanie niskim, użyjemy 3-wejściowej bramki NAND (metoda ta czasem nie sprawdza się).

Rys. 1.2 Trójwejściowa bramka NAND

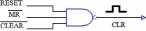

Drugą metodą uporania się z problemem sygnałów aktywnych w stanie niskim jest posługiwanie się symbolem negacji stanu. Jeżeli bramka wykonuje funkcję OR w logice ujemnej, to rysujemy ją tak jak na rys. 1.3. Kółeczko narysowane na wejściu lub wyjściu oznacza negację lub innymi słowy aktywność stanem niski

Rys. 1.3 Trójwejściowa bramka OR w logice ujemnej

6

Wyszukiwarka

Podobne podstrony:

http ://lay er. uci. agh. edu. pl/ maglay/wrona4. UKŁADY CYFROWE RODZINY TTL Układy TTL (Transistior

http ://lay er. uci. agh .edu.pl/ maglay/wrona 3.2. MOC STRAT Moc strat P układu określa się jako P=

http: //I ay er. uci. agh. edu. pl/ maglay/wrona1. SYMBOLE PODSTAWOWYCH BRAMEK, ICH TABELE PRAWDY OR

http ://lay er. uci. agh. edu. pl/magl ay/wrona/ charakterze źródła pobudzającego, jednak my zajmuje

http ://lay er. uci. agh. edu. pl/magl ay/wrona/8. Przykładowe zadania Zadanie 1 BLD Dane:teg Rg = 5

http: //I ay er .uci. agh. edu. pl/maglay/wrona/ obwodów drukowanych na dwustronnych laminatach z ży

http ://l ay er. uci. agh. edu. pl/ maglay/wrona sów jest mniejszy od czasu propagacji sygnału w bra

http ://l ay er. uci. agh. edu. pl/ maglay/wrona gorszym przypadku określa największą amplitudę sygn

http ://l ay er. uci.agh.edu. pl/maglay/wrona 3.4. ZGODNOŚĆ ŁĄCZENIOWA I OBCIĄŻALNOŚĆ System cyfrowy

http: //I ay er. uci. agh. edu. pl/ maglay/wrona Seria Technologia izolacji złączowej z domieszkow

http ://l ay er. uci. agh. edu. pl/ maglay/wrona 4.1.1.1. Stan włączenia (niski stan na wyjściu bram

http ://l ay er. uci. agh. edu. pl/ maglay/wrona że zapewnić poziom L również dla większych prądów

http ://l ay er. uci. agh. edu. pl/maglay/wrona minąć procesy przejściowe w układzie bramki, to

http ://l ay er. uci. agh. edu. pl/maglay/wrona 5.4.1. Bramki NAND i

http ://l ay er. uci. agh. edu. pl/ maglay/wrona2. PODSTAWOWE OKREŚLENIA I KLASYFIKACJE CYFROWYCH UK

http ://l ay er. uci. agh. edu. pl/ maglay/wrona3. ZASADNICZE PARAMETRY CYFROWYCH UKŁADÓW SCALONYCH

http: //I ay er. uci. agh. edu. pl/magl ay/wrona/ a = 0,3[dB/o[/w] = ?dB <=> a = y[2 t = l / v

http: ll ay er. uci. agh .edu.pl/magl ay/wrona/u,(0) Rys. 8 Schemat zastępczy obwodów wejściowych li

http: ll ay er. u ci. agh .edu.pl/maglay/wrona/ Oś pionowa jest osią czasu, oś pozioma jest osią odl

więcej podobnych podstron