6931258576

http ://l ay er. uci. agh. edu. pl/ maglay/wrona

że zapewnić poziom L również dla większych prądów obciążenia, lecz wówczas napięcie wyjściowe Uol wzrasta.

4.1.1.2. Stan wyłączenia (stan wysoki na wyjściu)

Rys. 4.6. Schematy zastępcze bramki NA ND w stanie wyłączenia

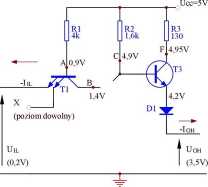

Gdy choćby na jednym z wejść bramki jest poziom L, wówczas bramka jest wyłączona i na jej wyjściu jest poziom H. Tranzystor Tl znajduje się w nasyceniu, tranzystory T2 i T4 nie przewodzą, a T3 pracuje liniowo jako wtórnik emiterowy. Jak widać na rys.4.6, w stanie wyłączenia zarówno prąd wejściowy Iil, jak i wyjściowy (obciążenia) Ioh wypływają z bramki.

Napięcie na wyjściu bramki może być określone jako:

U- = U„ -U-,-UD, -

p, '

gdzie:

Ube3 - napięcie baza - emiter tranzystora T3,

Udi - napięcie przewodzenia diody Dl,

P3 - współczynnik wzmocnienia prądowego tranzystora T3.

Po podstawieniu otrzymujemy typową wartość napięcia na wyjściu: UoHtyp =5 -0,7-0,7-0,1=3,5V. Przy założeniu, że wyjście analizowanej bramki jest przyłączone do dziesięciu wejść innych bramek z tej samej serii, maksymalny prąd obciążenia wynosi IoHma.\= -0,4mA. Bramka może być bardziej obciążona, ale wówczas napięcie wyjściowe Uoh staje się odpowiednio mniejsze (rys. 4.7). Aby utrzymać bramkę w stanie wyłączenia, największe napięcie wejściowe w stanie niskim L musi być wystarczająco małe, aby zapewnić gwarantowany poziom wysoki H na wyjściu. Przyjmuje się Uil-max=0,8V. Przy zwarciu wejść bramki całkowity prąd wejściowy pozostaje praktycznie taki sam, nie zależnie od liczby wejść bramki na których jest poziom logiczny niski.

17

Wyszukiwarka

Podobne podstrony:

http: //I ay er .uci. agh. edu. pl/maglay/wrona/ obwodów drukowanych na dwustronnych laminatach z ży

http ://l ay er. uci. agh. edu. pl/ maglay/wrona sów jest mniejszy od czasu propagacji sygnału w bra

http ://l ay er. uci. agh. edu. pl/ maglay/wrona gorszym przypadku określa największą amplitudę sygn

http ://l ay er. uci.agh.edu. pl/maglay/wrona 3.4. ZGODNOŚĆ ŁĄCZENIOWA I OBCIĄŻALNOŚĆ System cyfrowy

http: //I ay er. uci. agh. edu. pl/ maglay/wrona Seria Technologia izolacji złączowej z domieszkow

http ://l ay er. uci. agh. edu. pl/ maglay/wrona 4.1.1.1. Stan włączenia (niski stan na wyjściu bram

http ://l ay er. uci. agh. edu. pl/maglay/wrona minąć procesy przejściowe w układzie bramki, to

http ://l ay er. uci. agh. edu. pl/maglay/wrona 5.4.1. Bramki NAND i

http: //I ay er. uci. agh. edu. pl/ maglay/wrona1. SYMBOLE PODSTAWOWYCH BRAMEK, ICH TABELE PRAWDY OR

http ://l ay er. uci. agh. edu. pl/ maglay/wrona2. PODSTAWOWE OKREŚLENIA I KLASYFIKACJE CYFROWYCH UK

http ://l ay er. uci. agh. edu. pl/ maglay/wrona3. ZASADNICZE PARAMETRY CYFROWYCH UKŁADÓW SCALONYCH

http ://lay er. uci. agh .edu.pl/ maglay/wrona 3.2. MOC STRAT Moc strat P układu określa się jako P=

http: ll ay er. u ci. agh .edu.pl/maglay/wrona/ Oś pionowa jest osią czasu, oś pozioma jest osią odl

http: ll ay er. u ci. agh .edu.pl/maglay/wrona/ Zatem: = (23) Aby wyznaczyć napięc

http: //I ay er. uci. agh. edu. pl/magl ay/wrona/ a = 0,3[dB/o[/w] = ?dB <=> a = y[2 t = l / v

http: ll ay er. u ci. agh .edu.pl/maglay/wrona/2. Schemat zastępczy linii długiej przedstawiony za p

http: ll ay er. u ci. agh .edu.pl/maglay/wrona/ Należy zauważyć więc, że linie długą można rozpatryw

http ://lay er. uci. agh. edu. pl/ maglay/wrona4. UKŁADY CYFROWE RODZINY TTL Układy TTL (Transistior

http ://lay er. uci. agh. edu. pl/ maglay/wrona1.2 WYMIENNOŚĆ BRAMEK Przy projektowaniu układów cyfr

więcej podobnych podstron