6931258575

http ://l ay er. uci. agh. edu. pl/ maglay/wrona 4.1.1.1. Stan włączenia (niski stan na wyjściu bramki)

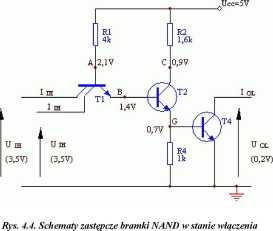

W stanie włączenia na obydwu wejściach bramki jest poziom H (wartość typowa Uih=3,5V), co powoduje, że na wyjściu bramki jest poziom L. Tranzystory T2 i T4 są w stanie nasycenia, T3 jest odcięty, a Tl pracuje w trybie inwersyjnym (rys. 4.4). W trybie inwersyjnym do każdego z wejść tranzystora Tl wpływa prąd, którego maksymalna wartość określona przez wytwórców (dla najgorszych warunków pracy) nie może przekroczyć 40pA. Typowa wartość napięcia na wyjściu w stanie L wynosi UouyP=0,2V i jest napięciem nasycenia UcEsat tranzystora T4. W stanie włączenia zarówno prąd wejściowy Iih, jak i wyjściowy (obciążenia) Iol w istocie wpływają do bramki. Wyjście bramki stanowi „zlew”, do którego wpływają prądy obciążenia, dostarczane przez przyłączone do tego wyjścia inne bramki.

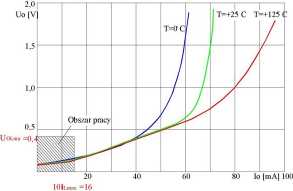

Rys. -4.5 Charakterystyki wyjściowe podstawowej bramki TTL w stanie włączenia dla UCC=5V, Um=2,4V

Z rys. 4.5 wynika iż maksymalny prąd, który może wpłynąć do wyjścia bramki wynosi 16mA. Jest on wystarczający do przyłączenia dziesięciu bramek TTL z serii standardowej. Wyjście bramki mo-

16

Wyszukiwarka

Podobne podstrony:

http: //I ay er .uci. agh. edu. pl/maglay/wrona/ obwodów drukowanych na dwustronnych laminatach z ży

http ://l ay er. uci. agh. edu. pl/ maglay/wrona sów jest mniejszy od czasu propagacji sygnału w bra

http ://l ay er. uci. agh. edu. pl/ maglay/wrona gorszym przypadku określa największą amplitudę sygn

http ://l ay er. uci.agh.edu. pl/maglay/wrona 3.4. ZGODNOŚĆ ŁĄCZENIOWA I OBCIĄŻALNOŚĆ System cyfrowy

http: //I ay er. uci. agh. edu. pl/ maglay/wrona Seria Technologia izolacji złączowej z domieszkow

http ://l ay er. uci. agh. edu. pl/ maglay/wrona że zapewnić poziom L również dla większych prądów

http ://l ay er. uci. agh. edu. pl/maglay/wrona minąć procesy przejściowe w układzie bramki, to

http ://l ay er. uci. agh. edu. pl/maglay/wrona 5.4.1. Bramki NAND i

http: //I ay er. uci. agh. edu. pl/ maglay/wrona1. SYMBOLE PODSTAWOWYCH BRAMEK, ICH TABELE PRAWDY OR

http ://l ay er. uci. agh. edu. pl/ maglay/wrona2. PODSTAWOWE OKREŚLENIA I KLASYFIKACJE CYFROWYCH UK

http ://l ay er. uci. agh. edu. pl/ maglay/wrona3. ZASADNICZE PARAMETRY CYFROWYCH UKŁADÓW SCALONYCH

http ://lay er. uci. agh .edu.pl/ maglay/wrona 3.2. MOC STRAT Moc strat P układu określa się jako P=

http: ll ay er. u ci. agh .edu.pl/maglay/wrona/ Oś pionowa jest osią czasu, oś pozioma jest osią odl

http: ll ay er. u ci. agh .edu.pl/maglay/wrona/ Zatem: = (23) Aby wyznaczyć napięc

http: //I ay er. uci. agh. edu. pl/magl ay/wrona/ a = 0,3[dB/o[/w] = ?dB <=> a = y[2 t = l / v

http: ll ay er. u ci. agh .edu.pl/maglay/wrona/2. Schemat zastępczy linii długiej przedstawiony za p

http: ll ay er. u ci. agh .edu.pl/maglay/wrona/ Należy zauważyć więc, że linie długą można rozpatryw

http ://lay er. uci. agh. edu. pl/ maglay/wrona4. UKŁADY CYFROWE RODZINY TTL Układy TTL (Transistior

http ://lay er. uci. agh. edu. pl/ maglay/wrona1.2 WYMIENNOŚĆ BRAMEK Przy projektowaniu układów cyfr

więcej podobnych podstron