IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -1-

Ćwiczenie 6

Komunikacja z komputerem (łącze RS232)

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -2-

1. Cel ćwiczenia

Celem ćwiczenia jest zapoznanie się z portem szeregowym UART mikrokontrolera rodziny

MCS’51 oraz sposobem oprogramowywania tego portu.

2. Opis portu szeregowego RS – 232

RS-232 jest magistralą komunikacyjną przeznaczoną do szeregowej transmisji danych.

Najbardziej popularna wersja tego standardu, RS-232C pozwala na transfer na odległość nie

przekraczającą 15 m z szybkością do 20 kbit/s.

2.1. Standard RS – 232

Standard określa nazwy styków złącza oraz przypisane im sygnały a także specyfikację

elektryczną obwodów wewnętrznych. Standard ten definiuje normy wtyczek i kabli portów

szeregowych typu COM. Specyfikacja napięcia definiuje "1" logiczną jako napięcie -3V do -

15V, zaś "0" to napięcie +3V do +15V. Poziom napięcia wyjściowego natomiast może

przyjmować wartości -12V, -10V, +10V, +12V.

Full-duplex oznacza że można jednocześnie odbierać i wysyłać, half-duplex nie może robić

obu tych rzeczy naraz

2.2. Protokoły transmisji danych

Asynchroniczny: każdy bajt jest przesyłany niezależnie, i jest poprzedzony bitem START, po

którym są przesyłane jest do 9 bitów danych, po nich opcjonalnie bit parzystości (do wyboru:

tak, by łączna ilość jedynek w danych i tym bicie była parzysta (Even Parity), albo

nieparzysta (Odd Parity), i na koniec bit STOP.

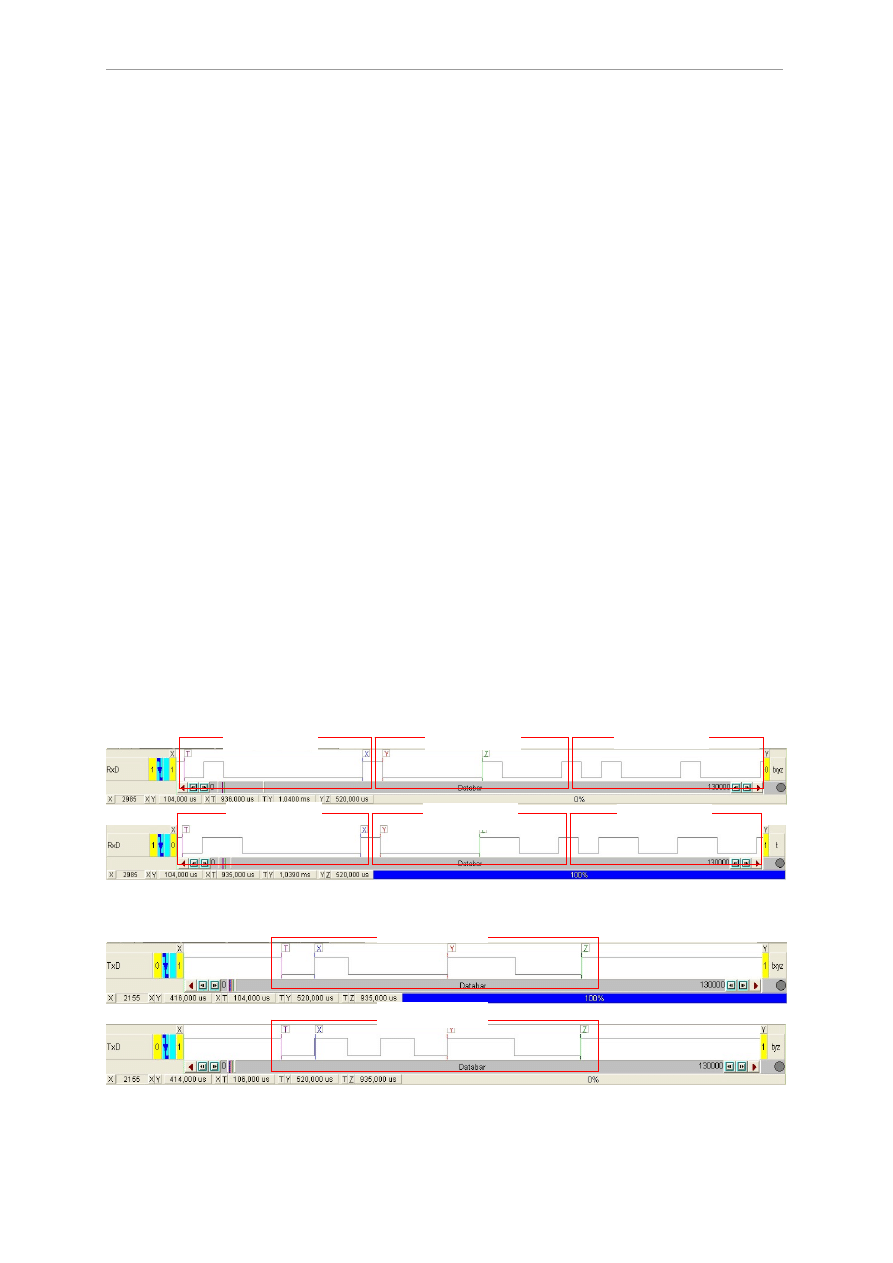

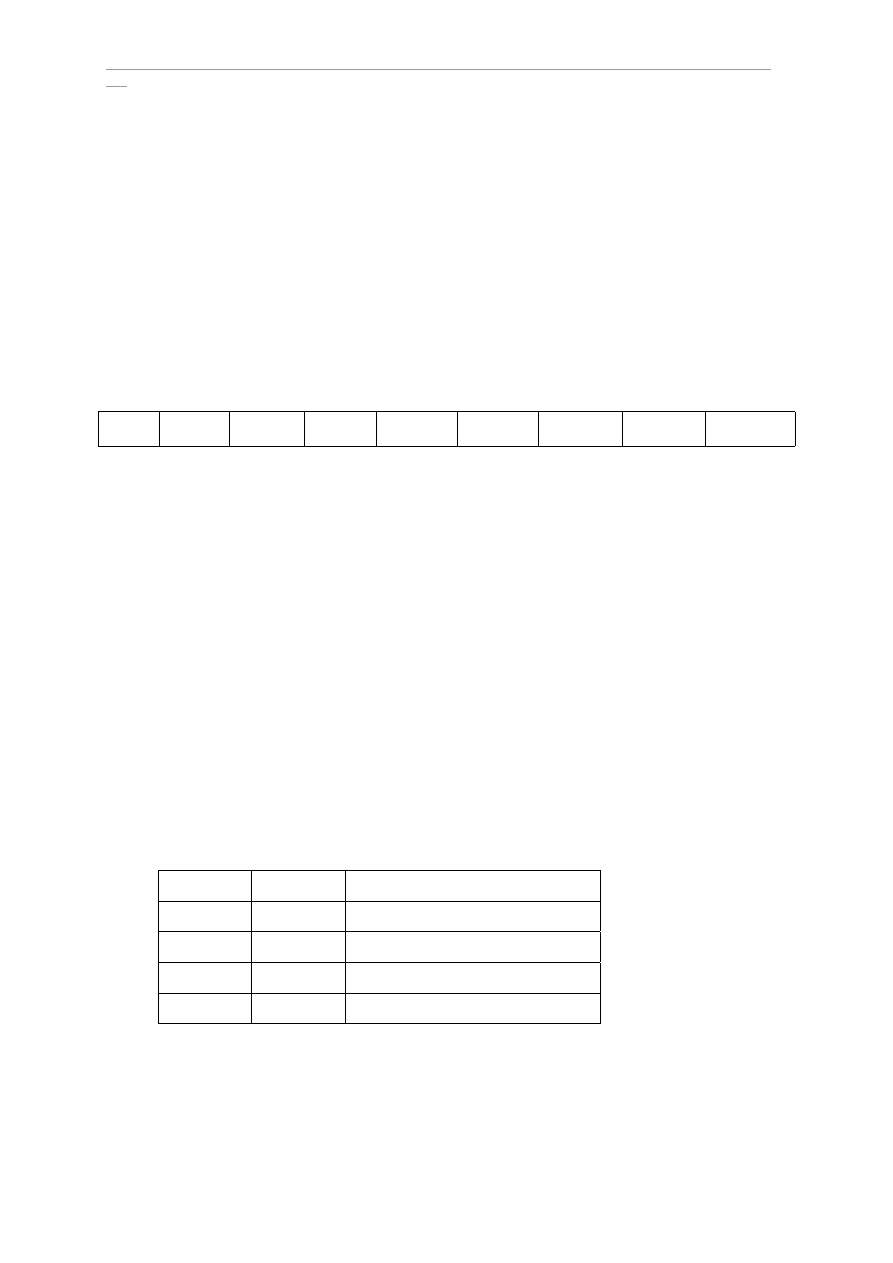

Podczas wykonywania ćwiczenia wykorzystywać będziemy tryb asynchroniczny. Na rys. 1. i

2. przedstawiono przykładową transmisję danych. Rys. 1. przedstawia sytuację w której

zestaw dydaktyczny odebrał dane – linia RxD (z rys. 3.), rys. 2. to sytuacja w której nadajemy

(do komputera) – linia TxD (z rys. 3.). Zaznaczono ramki na których widoczne są bity

START/STOP, widać też iż dane są wysyłane poczynając od bitu najmniej znaczącego –

MSB.

a)

b)

Rys. 1. Odbieramy linią RxD: a) 01h 10h 11h, b) 03h 30h 33h.

a)

b)

Rys. 2. Wysyłamy linią TxD: a)31h, b) 35h.

Synchroniczny: modem podaje sygnały TxC i RxC, a terminal wysyła - TxD lub odbiera -

RxD kolejne bity danych. Aby ustalić przy odbieraniu, gdzie jest granica bajtów, dane są

ramka 01h

ramka 10h

ramka 11h

ramka 03h

ramka 30h

ramka 33h

ramka 31h

ramka 35h

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -3-

poprzedzone serią bajtów, po których następuje znak rozpoczynający pakiet danych i kolejne

bajty, bez możliwości "zaczekania".

2.3. UART0 mikrokontrolera C8051F060

Mikrokontroler C8051F060 posiada zintegrowany układ UART0 umożliwiający szeregowe

przesyłanie informacji (8-bitowych słów danych) liniami portu P0: RX0 (P0.1 - wejście

szeregowe) i TX0 (P0.0 - wyjście szeregowe). Zamiana postaci danych z równoległej na

szeregową i odwrotnie oraz sterowanie wysyłaniem słowa odbywa się automatycznie. Dane

odebrane przez port szeregowy są zapisywane do rejestru wejściowego transmisji szeregowej,

dane wysyłane są pobierane z rejestru wyjściowego transmisji szeregowej.

Programista ma dostęp do portu szeregowego poprzez odpowiednie rejestry specjalne: Serial

Control (SCON0) oraz Serial Data Buffer (SBUF0). Oba rejestry umieszczono na stronie

UART0_PAGE.(zestawienie wszystkich stron SFR_PAGE znajduje się w załączniku A)

Instrukcja odczytu z rejestru SBUF0 (dokładny opis znajduje się w załączniku B) odwołuje

się do rejestru odbiornika, natomiast instrukcja zapisu do rejestru SBUF0 odwołuje się do

rejestru nadajnika (rejestr nadajnika nie jest widoczny podczas „debugowania” programu).

Port szeregowy UART0 może pracować w jednym z czterech trybów (jeden synchroniczny, 3

asynchroniczne). Tryb pracy jest wybierany poprzez nadanie odpowiedniej wartości bitom

SM01 i SM00 rejestru SCON0 (SCON0.7 i SCON0.6, dokładny opis znajduje się w

załączniku B). Podstawowe parametry trybów pracy przedstawiono w tabeli 1.

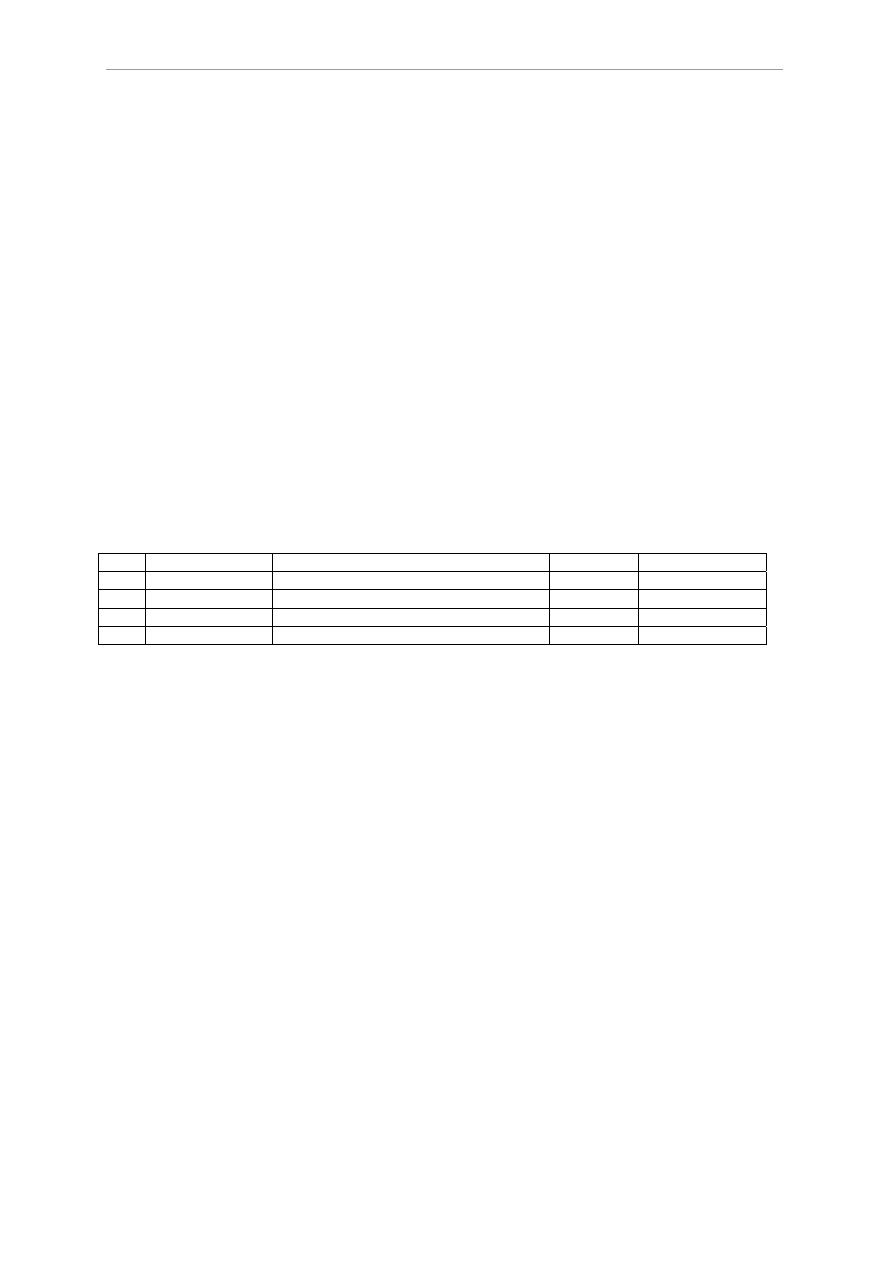

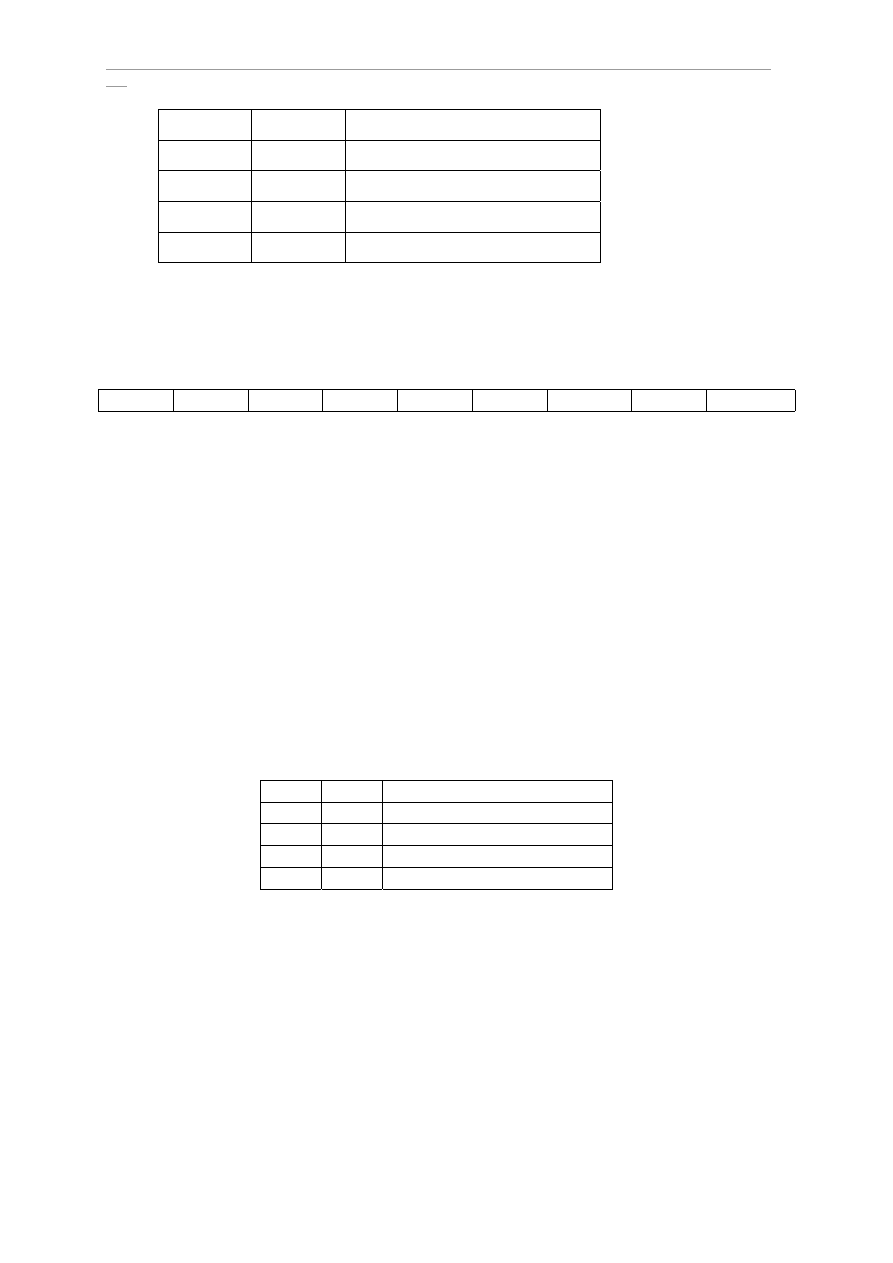

Tabela 1. Tryby pracy układu UART.

Tryb Synchronizacja

Zegar

Bity danych

Bity startu/stopu

0 Synchroniczny

SYSCLK/12

8

brak

1 Asynchroniczny Przepełnienie licznika T1, T2, T3, lub T4

8

1 start, 1 stop

2

Asynchroniczny

SYSCLK/32 lub SYSCLK/64

9

1 start, 1 stop

3 Asynchroniczny Przepełnienie licznika T1, T2, T3, lub T4

9

1 start, 1 stop

UART0 jest źródłem dwóch przerwań: Transmit Interrupt Flag TI0 (SCON0.1) jest ustawiany

po zakończeniu wysyłania bajtu danych, natomiast Receive Interrupt Flag RI0 (SCON0.0)

jest ustawiany po zakończeniu odbioru bajtu danych. Wskaźniki przerwań nie są zerowane

sprzętowo po przejściu do procedury obsługi przerwania. Dzięki temu programista może

sprawdzić wewnątrz procedury, z którym przerwaniem ma do czynienia. Przed wyjściem z

procedury obsługi przerwania wskaźniki przerwań muszą być wyzerowane.

2.3.0. Tryb 0: 8 bitów, synchroniczny, stała szybkość przesyłu

W tym trybie dane są wysyłane i odbierane przez wyprowadzenie RX0. Wyprowadzenie TX0

przesyła sygnał taktujący (zarówno do odbioru jak i wysyłania).

Wysyłanie danych rozpoczyna się po wykonaniu instrukcji zapisu do rejestru SBUF0.

Wysyłanych jest 8 bitów danych (najpierw najmłodszy). Po wysłaniu ósmego bitu ustawiany

jest wskaźnik TI0. Odbiór danych rozpoczyna się kiedy bit Receive Enable REN0 (SCON.4)

jest ustawiony, a wskaźnik RI0 wyzerowany. Jeden takt zegara po przyjęciu ósmego bitu

wskaźnik RI0 jest ustawiany i odbiór zostaje przerwany aż do wyzerowania wskaźnika RI0.

Przerwanie zostanie zgłoszone (o ile zostało uaktywnione), jeżeli ustawiony jest przynajmniej

jeden z bitów RI0 i TI0.

W trybie 0 częstotliwość przesyłu wynosi SYSCLK/12. W tym trybie wyprowadzenie RX0

jest skonfigurowane jako otwarty dren, potrzebny jest więc zazwyczaj zewnętrzny rezystor

podciągający (pull up).

2.3.1. Tryb 1: 8 bitów, asynchroniczny, regulowana szybkość przesyłu

Tryb 1 zapewnia standardową, asynchroniczną komunikację, przy czym przesył 8 bitów

danych w rzeczywistości wymaga przesłania 10 bitów: bit startu, 8 bitów danych (najpierw

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -4-

najmłodszy), bit stopu. Dane są wysyłane przez wyprowadzenie TX0, a przyjmowane przez

wyprowadzenie RX0. Podczas odbioru 8 bitów danych jest zapisywanych w rejestrze

odbiornika SBUF0, a bit stopu jest zapisywany w RB80 (SCON0.2).

Wysyłanie danych rozpoczyna się po wykonaniu instrukcji zapisu do rejestru nadajnika

SBUF0. Po zakończeniu wysyłania ustawiany jest wskaźnik TI0. Odbiór może się rozpocząć

w dowolnym momencie po ustawieniu bitu REN0. Po odebraniu bitu stopu bajt danych

zostaje przepisany do rejestru odbiornika SBUF0, o ile spełnione są następujące warunki:

a) RI0 = 0, b) bit stopu =1, jeżeli SM20 (SCON0.5) = 1.

Jeżeli powyższe warunki są spełnione, odebrany bajt danych zostanie przepisany do rejestru

odbiornika SBUF0, a bit stopu do bitu RB80 oraz zostanie ustawiony wskaźnik RI0. Jeżeli

warunki te nie są spełnione, nie następuje zapis do SBUF0 i RB80, a wskaźnik RI0 nie

zostaje ustawiony.

Przerwanie (o ile zostało uaktywnione) jest zgłaszane, jeżeli przynajmniej jeden z bitów RI0 i

TI0 jest ustawiony.

Szybkość przesyłu danych jest funkcją przepełnienia licznika T1 (w 8 bitowym trybie

automatycznego przeładowania – 8 bit Auto-Reload Mode) albo liczników T2, T3 lub T4 (w

trybie automatycznego przeładowania – Auto Reload Mode). Częstotliwość zegara można

ustawić oddzielnie dla wysyłania i odbioru danych.

Wybór licznika, który będzie określał szybkość przesyłu danych, następuje poprzez nadanie

odpowiednich wartości bitom S0RCLK0 i S0RCLK1 (SSTA0.0 i SSTA0.1) w przypadku

odbioru danych oraz bitom S0TCLK0 i S0TCLK1 (SSTA0.2 i SSTA0.3) w przypadku

wysyłania danych. Bity te znajdują się w rejestrze specjalnym SSTA0 (strona

UART0_PAGE).

Jeżeli szybkość przesyłu jest określona przez licznik T1, wartość bitu SMOD0 (SSTA0.4)

decyduje o tym, czy częstotliwość z jaką licznik T1 się przepełnia jest dzielona przez 2.

Jeżeli SMOD0=0:

Częstotliwość przesyłu

1

_

_

32

1

T

nia

przepelnie

osc

czestotliw

⋅

=

(1)

Jeżeli SMOD0=1:

Częstotliwość przesyłu

1

_

_

16

1

T

nia

przepelnie

osc

czestotliw

⋅

=

(2)

Częstotliwość przepełnienia licznika T1 jest określona przez zegar taktujący T1CLK oraz

przez wartość zapisaną do rejestru TH1:

Częstotliwość przepełnienia T1

1

256

1

TH

CLK

T

−

=

(3)

Licznik T1 może być taktowany przez jeden z 5 sygnałów zegarowych. Wybór sygnału

taktującego następuje poprzez nadanie odpowiedniej wartości bitom T1 Clock Select T1M i

Clock Scale (SCA1 - SCA0) w rejestrze specjalnym CKCON.

Jeżeli częstotliwość przesyłu jest określona przez licznik T2, T3 lub T4, oblicza się ją

następująco:

Częstotliwość przesyłu

4

,

3

,

2

_

_

16

1

=

⋅

=

n

gdzie

Tn

nia

przepelnie

osc

czestotliw

(4)

Częstotliwość przepełnienia licznika T

N

(n=2, 3, 4) jest określona przez zegar taktujący

TCKLn oraz przez wartość zapisaną do rejestru RCAPn:

Częstotliwość przepełnienia Tn

RCAPn

TnCLK

−

=

65536

(5)

Liczniki T2, T3 i T4 mogą być taktowane przez: zegar systemowy, zegar systemowy dzielony

przez 12 lub zewnętrzny sygnał zegarowy dzielony przez 8.

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -5-

2.3.2. Tryb 2: 9 bitów, asynchroniczny, stała szybkość przesyłu

W trybie 2 wysłanie bajtu danych w rzeczywistości wymaga przesyłu 11 bitów: bitu startu, 8

bitów danych (najpierw najmłodszy), programowalnego 9-tego bitu danych oraz bitu stopu.

W trakcie transmisji 9-ty bit danych jest określony przez wartość bitu TB80 (SCON0.3). W

trakcie odbioru 9-ty bit danych jest zapisywany do bitu RB80 (SCON0.3), a bit stopu jest

ignorowany.

Transmisja danych rozpoczyna się po wykonaniu instrukcji zapisu do rejestru SBUF0. Po

zakończeniu wysyłania (w trakcie wysyłania bitu stopu) ustawiany jest wskaźnik TI0

(SCON0.1). Odbiór może się rozpocząć w dowolnym momencie po ustawieniu bitu REN0

(SCON0.4). Po otrzymaniu bitu stopu bajt danych jest zapisywany do rejestru odbiornika

SBUF0 pod warunkiem, że RI0=0 oraz, że spełnione są następujące warunki: albo SM20=0,

albo SM20=1 oraz 9-ty bit danych jest równy ‘1’, a otrzymany adres jest zgodny z adresem

UART0 (ten problem wyjaśnimy później).

Jeżeli powyższe warunki są spełnione, 8 bitów danych jest zapisywanych w SBUF0, a 9-ty bit

trafia do RB80. Ustawiany jest wskaźnik przerwania RI0. Jeżeli warunki nie są spełnione, nie

następuje zapis od SBUF0 i RB80, nie jest też ustawiany wskaźnik RI0.

Przerwanie zostanie zgłoszone (o ile zostało uaktywnione), jeżeli przynajmniej jeden z bitów

RI0 i TI0 ma wartość ‘1’.

Szybkość przesyłu danych jest określona przez wartość bitu SMOD0 w rejestrze specjalnym

SSTA0, zgodnie z poniższym wzorem:

Częstotliwość przesyłu

64

2

0

SYSCLK

SMOD

⋅

=

(6)

2.3.3. Tryb 3: 9 bitów, asynchroniczny, regulowana szybkość przesyłu

W trybie 2 używany jest protokół transmisji z trybu 2, a szybkość przesyłu jest określana tak

jak w trybie 1. Wysłanie 8 bitów danych wymaga przesyłu 11 bitów: bitu startu, 8 bitów

danych (najpierw najmłodszy), programowalnego 9-tego bitu danych oraz bitu stopu.

Szybkość przesyłu jest określona przez szybkość, z jaką przepełnia się licznik T1, T2, T3 lub

T4. Możliwa jest komunikacja wieloprocesorowa oraz sprzętowe rozpoznawanie adresów.

3. Obsługa zestawu dydaktycznego EXTB-060/02

3.1. konfiguracja płyty C8051F06X-DK

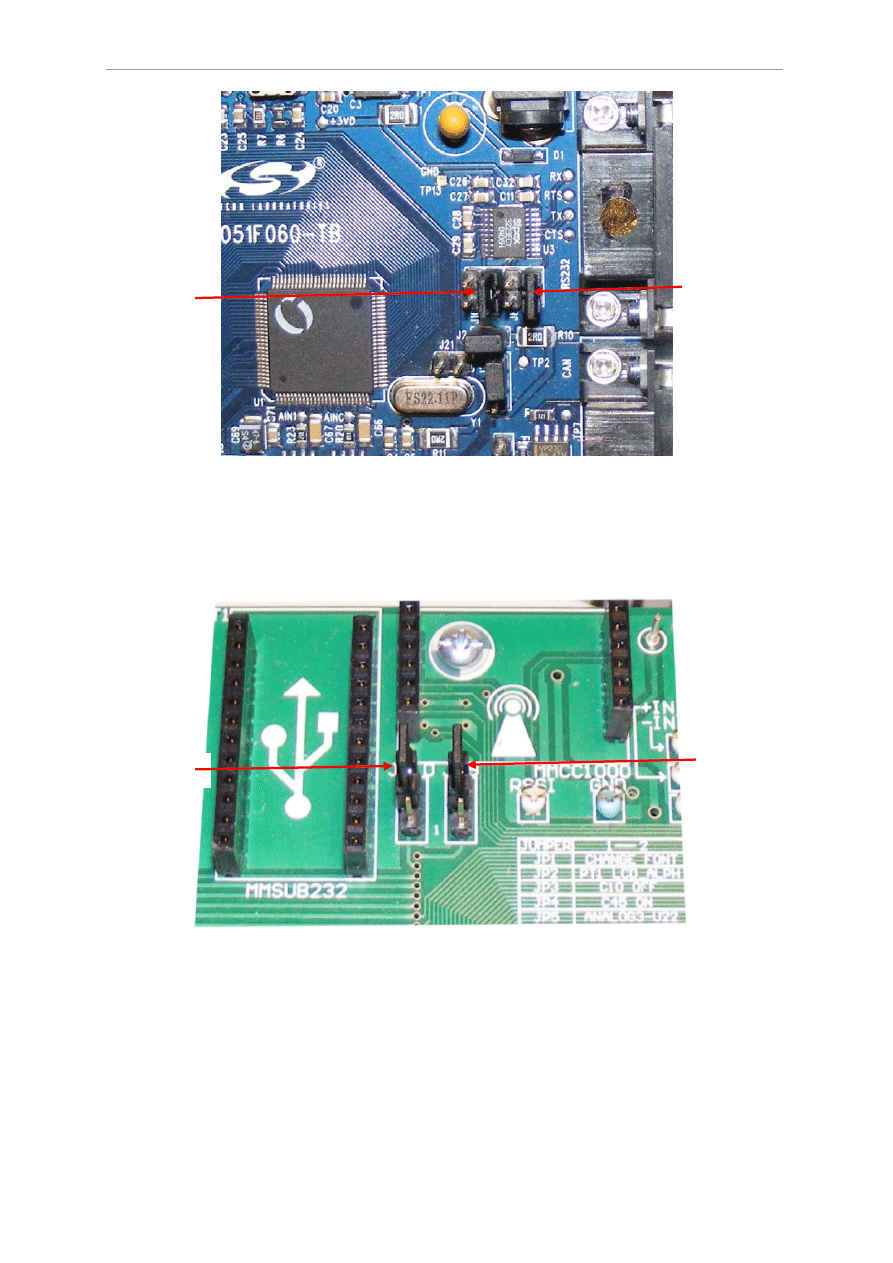

Aby możliwa była praca w portem RS-232 zestawu dydaktycznego należy zadbać bylinie

TxD i RxD były włączone, zgodnie z rys. 3.

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -6-

Rys. 3. Konfiguracja płyty C8051F06X-DK.

3.2. Konfiguracja płyty EXTB-060/02

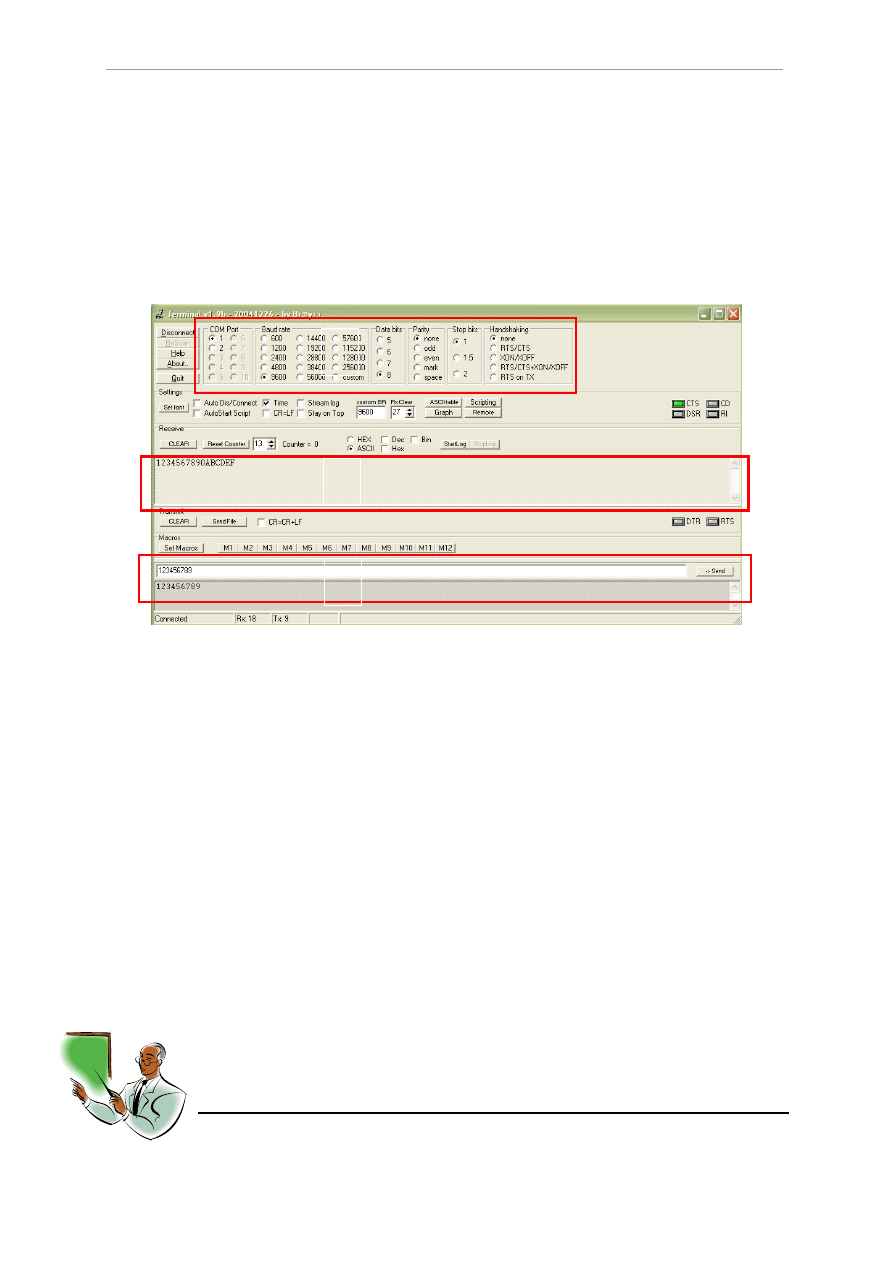

Linie TxD i RxD należy odłączyć od dodatkowych peryferiów na płycie EXTB-060/02,

zgodnie z rys.4.

Rys. 4. Konfiguracja płyty EXTB-060/02.

4. Konfiguracja portu szeregowego

Port szeregowy UART0 będzie pracować w trybie 1 z

szybkością przesyłu równą 9600 bps. Szybkość przesyłu (odbiór i nadawanie) danych będzie

określona przez licznik T1.

Na początku należy podłączyć wykorzystywane zasoby mikrokontrolera do określonych

wyprowadzeń. W tym celu w programie zamieszczamy następujące instrukcje:

mov SFRPAGE,

#CONFIG_PAGE

mov

P1MDIN,

#0E0H

; wybranie czterech wejść analogowych (ADC2)

zwora JP10

linia TxD

linia RxD

linia RxD

zwora JP9

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -7-

mov

P0MDOUT,

#01H;

; konfiguracja wyprowadzenia TX0 jako push-pull

setb

P0.1

; konfiguracja RX0 jako wejścia

mov

XBR0,

#004H

;

włączenie portu szeregowego UART0

mov

XBR2,

#040H

;

włączenie krosownicy

Należy również wyłączyć watchdog:

mov WDTCN,

#0DEH

mov WDTCN, #0ADH

Konfiguracja portu szeregowego polega na zapisie odpowiedniej wartości do rejestru

SCON0:

Wybieramy

tryb

1

⇒

SM00 = 0, SM10 = 1;

Rezygnujemy z kontroli bitu stopu

⇒

SM20 = 0;

Uaktywniamy

odbiór

znaków

⇒

REN0 = 1;

Zerujemy 9-ty bit danych odbieranych i nadawanych

⇒

RB80 = 0, TB80 = 0;

Zerujemy wskaźniki

przerwania

⇒

TI0 = 0, RI0 = 0;

Odwołanie do rejestru SCON0 wymaga wybrania właściwej strony SFR_PAGE

(UART0_PAGE). W rejestrze SSTA0 pozostawiamy wartość domyślną.

5. Określenie szybkości przesyłu danych

Określenie szybkości przesyłu danych wymaga skonfigurowania licznika T1, tj. zapisania

odpowiednich wartości do rejestrów: TCON, TMOD, CKCON oraz TH1. Odwołanie do tych

rejestrów wymaga wybrania właściwej strony SFR (TIMER01_PAGE).

Rejestr TCON:

Uruchamiamy

licznik

⇒

TR1 = 1;

Pozostałe bity rejestru są równe ‘0’

Rejestr TMOD:

W rejestrze tym za licznik T1 odpowiadają 4 starsze bity, cztery młodsze określają sposób

pracy licznika T0.

Wyłączamy zewnętrzne bramkowanie zliczania

⇒

GATE1 = 0;

Wybieramy zliczanie impulsów wewn. zegara

⇒

C/T1 = 0;

Wybieramy tryb pracy UART jako 2

⇒

T1M1=1, T1M0 = 0;

Rejestr CKCON:

Licznik T1 będzie taktowany zegarem systemowym

⇒

T1M = 1;

Pozostałe bity są równe ‘0’

Zgodnie z założeniem, że szybkość transmisji wynosi 9600 bps, do rejestru TH1 należy

wpisać wartość 0F6H.

6. Konfiguracja systemu przerwań

Należy uaktywnić przerwanie portu szeregowego UART0.

W rejestrze IE należy ustawić bit EA (maska globalna) oraz bit ES0. Pozostałe bity mają być

równe ‘0’ w przypadku gdy korzystamy z ADC2 należy pamiętać o bicie . Adres procedury

obsługi przerwania portu UART0 wynosi 0x23h. Przed wyjściem z procedury obsługi

przerwania należy wyzerować bity TI0 oraz RI0.

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -8-

7. Program terminala portu RS - 232

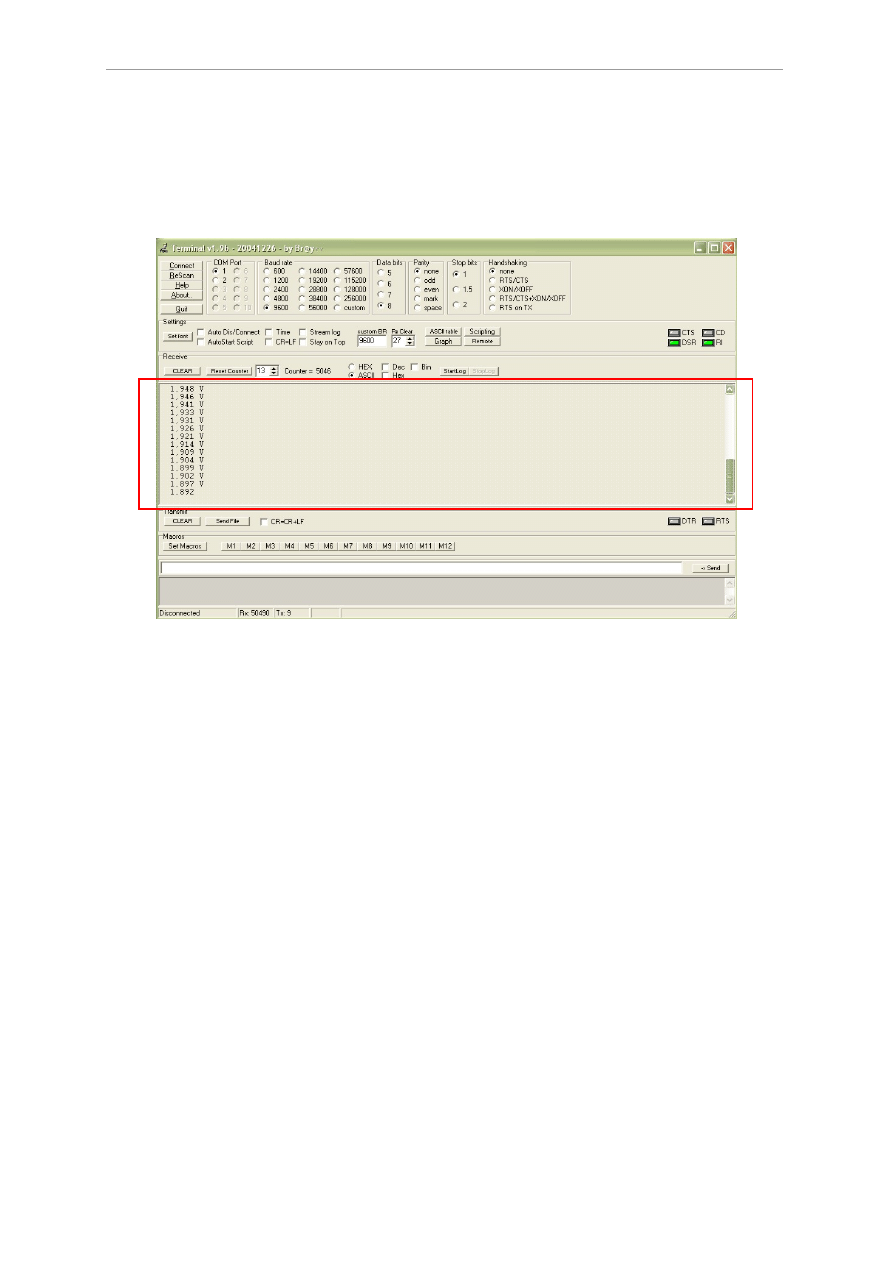

Do obsługi komputerowego portu RS - 232 należy użyć programu terminala. Na początku

trzeba skonfigurować port, w tym celu należy w oknie A z rys. 5. wybrać: port 1, prędkość

transmisji 9600, 8 bitów danych, brak parzystości, 1 bit stopu oraz brak sprzętowego

„handshakingu”. Następnym krokiem jest włączenie portu – CONNECT. Dane odebrane z

portu widoczne będą w oknie - B odbiornika. Okienko nadajnika – C, służy do wpisywania

danych do wysłania. Domyślnie wszystkie znaki wysyłane są jako znaki ASCII, gdy jednak

chcemy wysłać daną HEX należy poprzedzić ja znakiem ‘$’. Przykładowo aby wysłać daną

31h należy z oknie nadajnika wpisać ‘$31’ i nacisnąć SEND.

Rys. 5. Program terminala portu RS-232.

8. Zadanie do wykonania

A. Sprawdzian wejściowy ( 2pkt )

Przed przystąpieniem do realizacji ćwiczenia przeprowadzony zostanie krótki (ok. 10 min.)

sprawdzian wejściowy ze znajomości asemblera. Podczas pisania dopuszczalne jest

korzystanie z listy instrukcji asemblera.

B. Zadanie 1 ( 5 pkt )

Wykorzystując uprzednio napisany program obsługujący klawiaturę i wyświetlacz

ciekłokrystaliczny zrealizować dwukierunkową komunikację systemu uruchomieniowego z

komputerem poprzez port szeregowy. Na początku program użytkownika przesyła do

komputera napis początkowy (zdefiniowany przez użytkownika). Napis ten pojawi się na

ekranie komputera, w oknie terminala portu RS, zgodnie z rys. 5.

Po wyświetleniu napisu początkowego program użytkownika przechodzi do normalnego

trybu komunikacji, tj. znaki wprowadzone z klawiatury komputera PC mają być wyświetlone

na wyświetlaczu LCD systemu uruchomieniowego, natomiast znaki wprowadzone z

klawiatury systemu mają być wyświetlone zarówno na wyświetlaczu LCD, jak i na ekranie

komputera.

_________________________________________________________________

Wysyłanie napisu początkowego napisu zorganizować w taki sposób, że

pierwszy znak napisu zapisywany jest do rejestru SBUF0 w programie

głównym, natomiast wszystkie pozostałe w procedurze obsługi przerwania.

A

B

C

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -9-

B. Zadanie 2 ( 3 pkt )

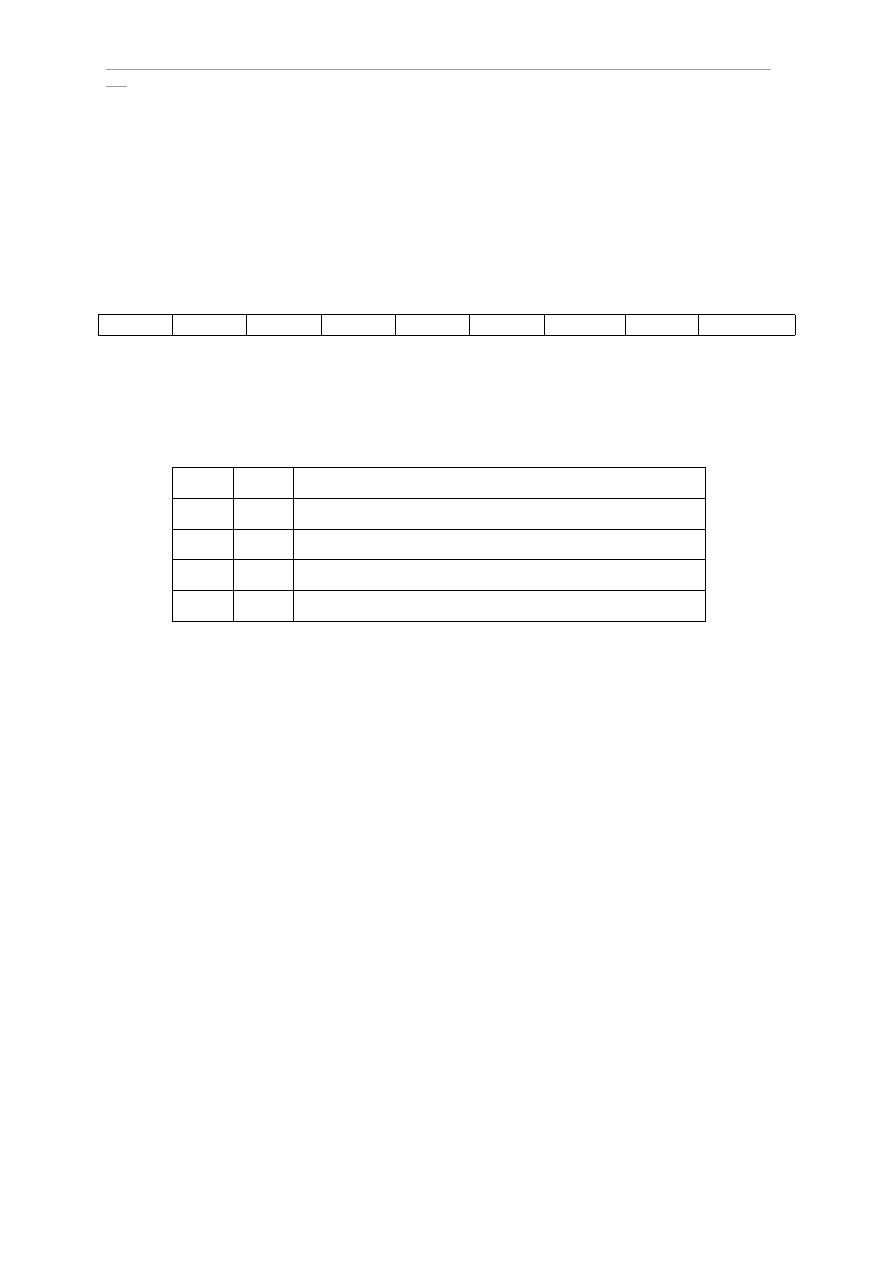

Wykorzystując uprzednio napisany program obsługujący przetwornik analogowo-cyfrowy

ADC2 i wyświetlacz ciekłokrystaliczny napisać program do wysyłania wyniku pomiaru

napięcia (w postaci dziesiętnej) do terminala poprzez port szeregowy. Po wysłaniu jednego

wyniku należy przejść do następnej linii (terminala), zgodnie z rys. 6. Wynik powinien się

również pojawić na wyświetlaczu LCD.

Rys. 6. Wynik pracy programu spełniającego warunek B.

Należy pamiętać o odpowiednim skonfigurowaniu przetwornika ADC2 oraz o uaktywnieniu

jego przerwania.

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -

10-

Załącznik A

Zestawienie definicji stron rejestrów specjalnych SFRPAGE, umieszczonych w pliku

nagłówkowym: C8051F060.INC.

CONFIG_PAGE

EQU 0FH ; SYSTEM AND PORT CONFIGURATION PAGE

LEGACY_PAGE

EQU 00H ; LEGACY SFR PAGE

TIMER01_PAGE

EQU 00H ; TIMER 0 AND TIMER 1

CPT0_PAGE

EQU 01H ; COMPARATOR 0

CPT1_PAGE

EQU 02H ; COMPARATOR 1

CPT2_PAGE

EQU 03H ; COMPARATOR 2

UART0_PAGE

EQU 00H ; UART 0

UART1_PAGE

EQU 01H ; UART 1

SPI0_PAGE

EQU 00H ; SPI 0

EMI0_PAGE

EQU 00H ; EXTERNAL MEMORY INTERFACE

ADC0_PAGE

EQU 00H ; ADC 0

ADC1_PAGE

EQU 01H ; ADC 1

ADC2_PAGE

EQU 02H ; ADC 2

SMB0_PAGE

EQU 00H ; SMBUS 0

TMR2_PAGE

EQU 00H ; TIMER 2

TMR3_PAGE

EQU 01H ; TIMER 3

TMR4_PAGE

EQU 02H ; TIMER 4

DAC0_PAGE

EQU 00H ; DAC 0

DAC1_PAGE

EQU 01H ; DAC 1

PCA0_PAGE

EQU 00H ; PCA 0

DMA0_PAGE

EQU 03H ; DMA 0

CAN0_PAGE

EQU 01H ; CAN 0

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -

11-

Załącznik B

Rejestry specjalne mikrokontrolera C8051F060

Rejestr SCON0 – konfiguracja portu szeregowego UART0

Strona SFR: UART0_PAGE (00h)

Adres: 0x98 (dostępny bitowo)

R/W R/W R/W R/W R/W R/W R/W R/W

Po zerowaniu

SM00 SM01 SM20 REN0 TB80 RB80 TI0

TR0 00000000

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bity 7 – 6: SM00-SM01 – wybór trybu pracy portu szeregowego UART0

Zapis: powoduje wybór trybu pracy zgodnie z poniższą tabelą

Odczyt: zwraca aktualny tryb pracy portu szeregowego zgodnie z poniższą tabelą

SM00 SM10 Tryb

pracy

0

0

Tryb 0: synchroniczny

0

1

Tryb 1: asynchroniczny, 8-bitowy, zmienna szybkość

1

0

Tryb 2: asynchroniczny, 9-bitowy, stała szybkość

1

1

Tryb 3: asynchroniczny, 9-bitowy, zmienna szybkość

Bit 5:

SM20 – aktywacja komunikacji wieloprocesorowej (funkcja tego bitu zależy od

trybu pracy)

Tryb 0: bez znaczenia

Tryb 1: sprawdzanie poprawnego bitu stopu

0 – poziom logiczny bitu stopu jest ignorowany

1 – bit RI0 ustawiany i przerwanie zgłaszane tylko wtedy, kiedy bit

stopu ma poziom logiczny ‘1’

Tryby 2 i 3: aktywacja komunikacji wieloprocesorowej

0 – poziom logiczny dziewiątego bitu ignorowany

1 – bit RI0 ustawiany i przerwanie zgłaszane tylko wtedy, kiedy

dziewiąty bit ma poziom logiczny ‘1’.

Bit 4:

REN0 (Receive ENable) – aktywacja odbioru

0 – odbiór wyłączony

1 – odbiór włączony

Bit 3:

TB80 – 9-ty bit danych wysyłanych. Nie jest używany w trybach 0 i 1. W trybach

2 i 3 logiczny poziom tego bitu jest przypisywany 9-temu bitowi danych

wysyłanych

Bit 2:

RB80 – 9-ty bit danych odbieranych. Nie jest używany w trybie 0. W trybie 1

bitowi temu przypisuje się poziom logiczny bitu stopu. W trybach 2 i 3 temu

bitowi przypisywany jest logiczny poziom 9-tego bitu danych odbieranych

Bit 1:

TI0 (Transmit Interrupt Flag) – wskaźnik przerwania po zakończeniu transmisji

(ustawiany sprzętowo po wysłaniu 8-go bitu w trybie 0 lub na początku bitu stopu

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -

12-

w pozostałych trybach). Jeżeli przerwanie związane z portem szeregowym jest

uaktywnione, ustawienie tego bitu powoduje przejście do procedury obsługi

przerwania portu szeregowego UART0. Bit musi być zerowany programowo

Bit 0:

RI0 (Receive Interrupt Flag) – wskaźnik przerwania po zakończeniu odbioru

(ustawiany sprzętowo po przyjęciu bajtu danych przez UART0). Jeżeli

przerwanie związane z portem szeregowym jest uaktywnione, ustawienie tego

bitu powoduje przejście do procedury obsługi przerwania portu szeregowego

UART0. Bit musi być zerowany programowo.

Rejestr SSTA0 – rejestr statusu i wyboru zegara

Strona SFR: UART0_PAGE (00h)

Adres: 0x91

R/W R/W R/W R/W R/W

R/W

R/W

R/W

Po zerowaniu

FE0 RXOV0

TXCOL0

SMOD0 S0TCLK

1

S0TCLK

0

S0RCLK1

S0RCLK

0

00000000

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit 7:

FE0 (Frame Error) – sygnalizacja błędnego bitu stopu

0 – bit stopu poprawny

1 – bit stopu błędny

Bit 6:

RXOV0 (Receive Overrun Flag) – sygnalizacja utraty poprzednio odebranych

danych na skutek zapisu nowych danych do bufora odbiornika przed odczytem

danych odebranych poprzednio

0 – dane odebrane poprzednio nie zostały utracone

1 – dane odebrane poprzednio zostały utracone

Bit 5:

TXCOL0 (Transmit Collision Flag) – sygnalizacja błędu transmisji polegającego

na zapisie do rejestru nadajnika w trakcie wysyłania wcześniejszych danych

0 – nie nastąpił błąd transmisji

1 – nastąpił błąd transmisji

Bit 4:

SMOD0 – podwajanie szybkości transmisji/odbioru

0 – dane przesyłane/odbierane z normalną szybkością

1 – dane przesyłane/odbierane z szybkością dwu-krotnie wyższą

Bity 3 – 2: wybór zegara taktującego wysyłanie danych

S0TCLK1

S0TCLK0

Zegar

0 0

Licznik

T1

0 1

Przepełnienie licznika T2

1 0

Przepełnienie licznika T3

1 1

Przepełnienie licznika T4

Bity 1 – 0: wybór zegara taktującego odbiór danych

IMiO PW, LPTM, Ćwiczenie 6, Komunikacja z komputerem -

13-

S0RCLK1

S0RCLK0

Zegar

0 0

Licznik

T1

0 1

Przepełnienie licznika T2

1 0

Przepełnienie licznika T3

1 1

Przepełnienie licznika T4

Rejestr CKCON: wybiera sygnał taktujący liczniki T1 i T0

Strona SFR: UART0_PAGE (00h)

Adres: 0x8E

R/W R/W R/W R/W R/W R/W R/W R/W

Po zerowaniu

– – –

T1M

T0M

–

SCA1

SCA0

00000000

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bity 7-5: nieużywane – odczyt: 000H, zapis – bez znaczenia

Bit 4:

T1M: Timer 1 Clock selekt – wybór sygnału taktującego licznik T1 (wartość T1M

jest ignorowana, jeżeli C/T1=1, czyli licznik zlicza impulsy zewnętrzne, a nie

takty zegara):

0 – licznik T1 jest taktowany sygnałem określonym przez bity SCA1 i SCA0

1 – licznik T1 jest taktowany zegarem systemowym

Bit 3:

T0M: Timer 0 Clock selekt – wybór sygnału taktującego licznik T0 (wartość T0M

jest ignorowana, jeżeli C/T0=1, czyli jeżeli licznik zlicza impulsy zewnętrzne, a

nie takty zegara):

0 – licznik T0 jest taktowany sygnałem określonym przez bity SCA1 i SCA0

1 – licznik T0 jest taktowany zegarem systemowym

Bit 2:

nieużywany – odczyt: 0H, zapis: bez znaczenia

Bity 1-0: SCA1-SCA0: dzielnik sygnału taktującego zgodnie z poniższą tabelą:

SCA1

SCA0

Sygnał taktujący

0

0

Zegar

systemowy/12

0

1

Zegar

systemowy/4

1

0

Zegar

systemowy/48

1

1

Sygnał zewnętrzny/8

*

*

Sygnał zewnętrzny dzielony przez 8 jest synchronizowany z zegarem systemowym. Jego

częstotliwość musi być nie wyższa niż częstotliwość zegara systemowego.

Wyszukiwarka

Podobne podstrony:

3 ćwiczenia BADANIE asfaltów

Ćwiczenie7

Cwiczenia 2

Ćwiczenia V

metody redukcji odpadów miejskich ćwiczenia

Ćwiczenia1 Elektroforeza

cwiczenia 9 kryzys

Ćwiczenia 1, cz 1

Ćwiczenie 8

9 ćwiczenie 2014

Cwiczenie 1

Ćwiczenie 2 Polska w europejskim systemie bezpieczeństwa

11 CWICZENIE 1 SEMESTR LETNIid 12747 ppt

więcej podobnych podstron