Badanie liczników asynchronicznych

Wszystkie grafiki, zdjęcia, programy oraz treść instrukcji podlegają ochronie prawnej na mocy ustawy o prawie autorskim. Używanie ich w jakikolwiek sposób bez uprzedniego,

pisemnego zezwolenia wydanego przez AGH jest zabronione i może spowodować pociągnięcie do odpowiedzialności cywilnej i karnej w maksymalnym zakresie dopuszczalnym przez

prawo.

1

Badanie liczników asynchronicznych - Ćwiczenie 4

1. Cel ćwiczenia

Zapoznanie się z podstawowymi strukturami liczników asynchronicznych szeregowych

modulo N, zliczających w przód i w tył oraz zasadą ich działania.

2. Wykaz przyrządów

• zestaw laboratoryjny (generator przebiegu prostokątnego + zasilacz + częstościomierz),

• oscyloskop 2-kanałowy z pamięcią,

• komputer + drukarka.

3. Przedmiot badań

• uniwersalne płytki montażowe z układami scalonymi:

9

UCY 7400 (cztery dwuwejściowe bramki NAND) – 1 szt.

9

UCY 7420 (dwie czterowejściowe bramki NAND) – 1 szt.

9

UCY 7474 (dwa przerzutniki typu D z wejściami do ustawiania i zerowania) – 2 szt.

9

UCY 7476 (dwa przerzutniki typu JK z wejściami do ustawiania i zerowania) – 2 szt.

4. Wprowadzenie teoretyczne

Licznikiem nazywamy sekwencyjny układ cyfrowy służący do zliczania i pamiętania

liczby impulsów podawanych w określonym przedziale czasu na jego wejście zliczające.

Oprócz wejścia dla impulsów zliczanych, licznik ma zazwyczaj wejście ustawiające jego stan

początkowy asynchronicznie względem impulsów zliczanych lub synchronicznie z nimi.

Liczbę stanów przyjmowanych przez licznik w jednym cyklu nazywa się długością cyklu lub

pojemnością licznika. Długość cyklu licznika zależy od liczby przerzutników wchodzących w

skład licznika. Jeżeli licznik zawiera N przerzutników, to jego pojemność, zależna od

sprzężeń logicznych między poszczególnymi przerzutnikami, zawierać się będzie w

przedziale P = <1,

N

2 >. W układach liczników najczęściej stosuje się przerzutniki D i JK.

W zależności od sposobu łączenia przerzutników otrzymujemy liczniki szeregowe

(asynchroniczne) lub równoległe (synchroniczne). Liczniki szeregowe są prostsze w budowie

od liczników równoległych, lecz szeregowe działanie przerzutników sprawia, że ustalenie się

nowej liczby w liczniku następuje po czasie dłuższym niż w liczniku równoległym. Dzieje się

tak dlatego, że zmiana stanu kolejnego przerzutnika odbywa się pod wpływem zmiany stanu

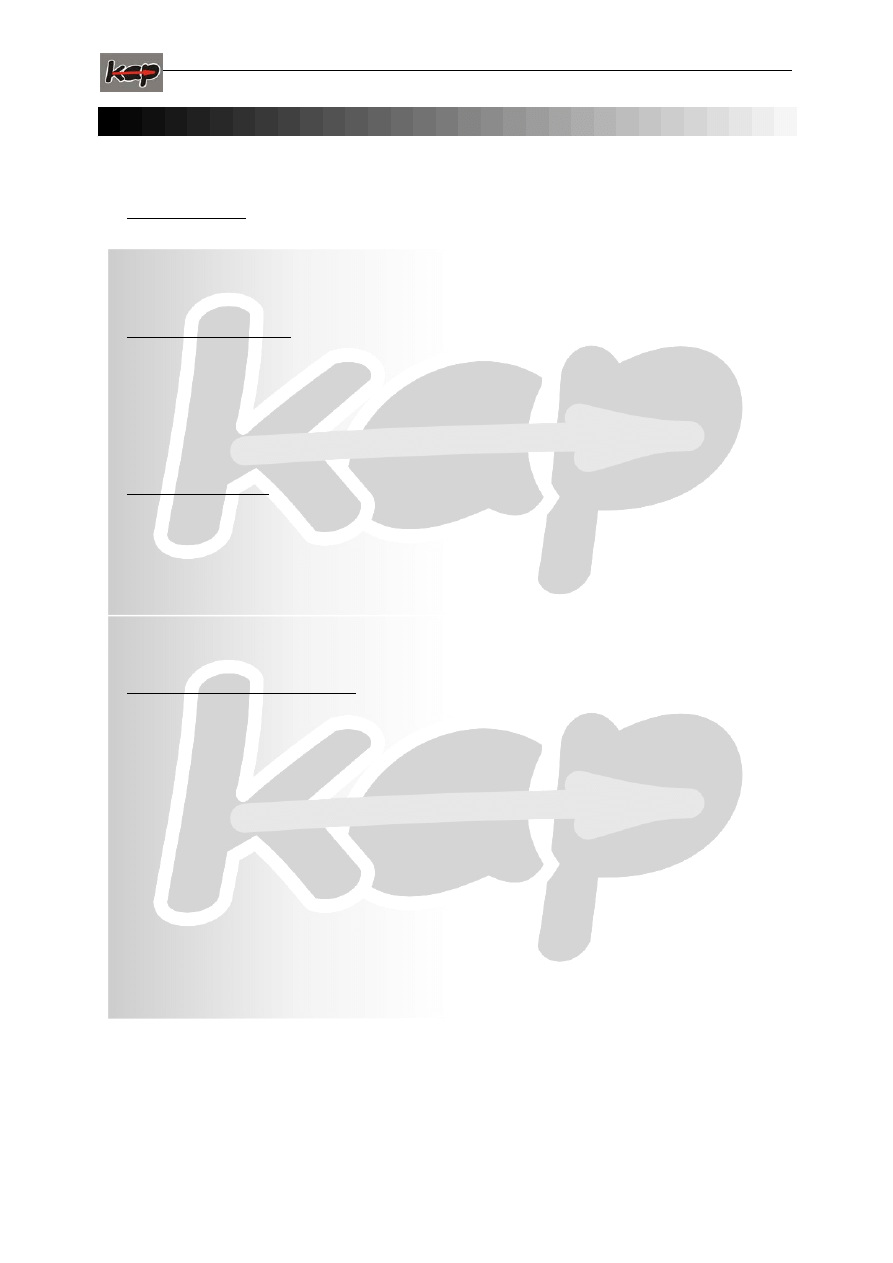

przerzutnika poprzedniego. Najprostszym przykładem licznika szeregowego jest kaskada np.

trzech szeregowo połączonych przerzutników typu JK, pokazana na rysunku 1a i pracująca

zgodnie z przebiegami czasowymi z rysunku 1b.

Badanie liczników asynchronicznych

Wszystkie grafiki, zdjęcia, programy oraz treść instrukcji podlegają ochronie prawnej na mocy ustawy o prawie autorskim. Używanie ich w jakikolwiek sposób bez uprzedniego,

pisemnego zezwolenia wydanego przez AGH jest zabronione i może spowodować pociągnięcie do odpowiedzialności cywilnej i karnej w maksymalnym zakresie dopuszczalnym przez

prawo.

2

a)

b)

Rys.1. Licznik szeregowy zliczający w przód o pojemności 8 (modulo 8)

a) schemat ideowy, b) przebiegi czasowe

Zliczane impulsy są wprowadzone na wejście zegarowe (x) pierwszego przerzutnika.

Wejścia zegarowe kolejnych przerzutników są zwarte z wyjściami Q poprzednich

przerzutników. Podanie zera logicznego na wejścia zerujące (R) przerzutników (z=0)

umożliwia asynchroniczne wyzerowanie licznika w dowolnej chwili, w czasie jego pracy.

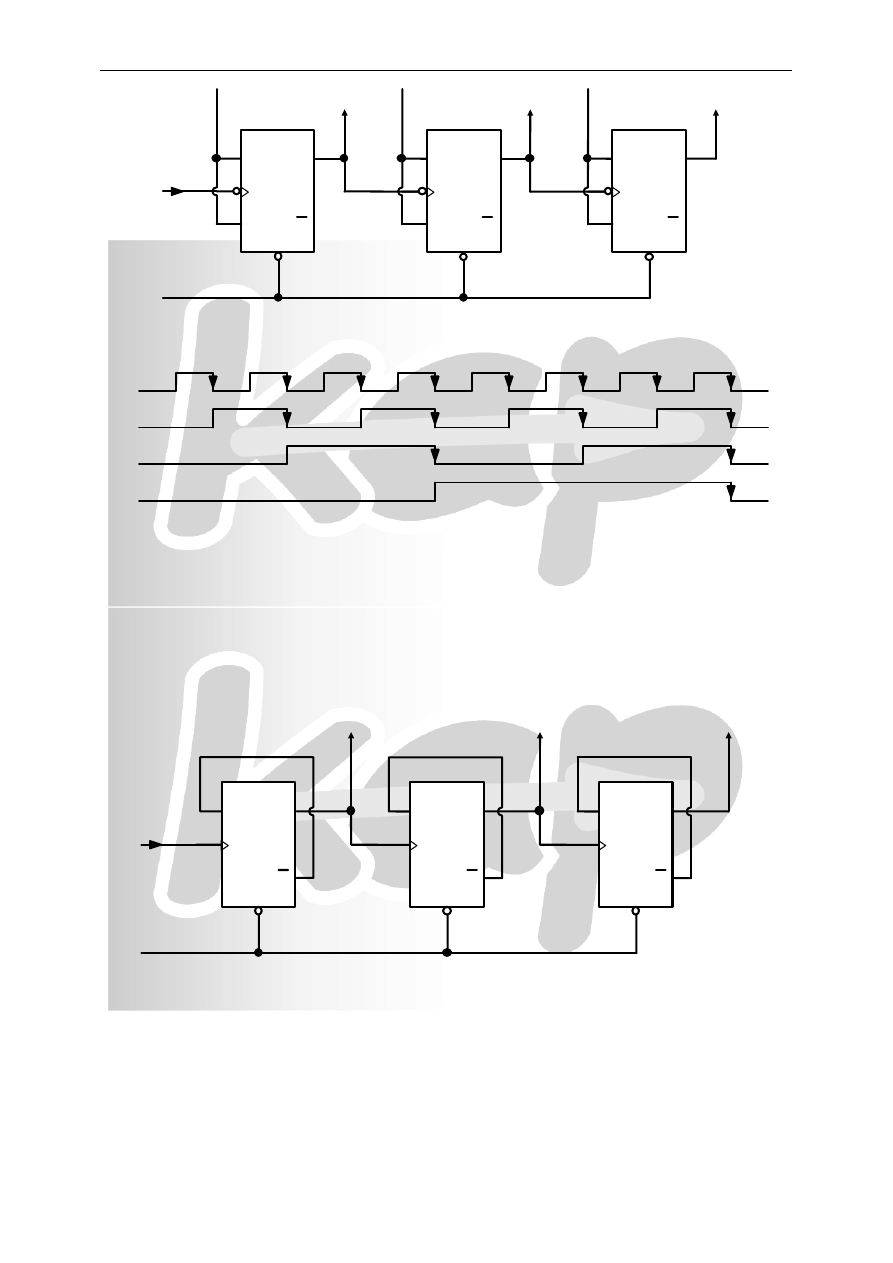

Licznik pokazany na rysunku 2 jest przykładem licznika szeregowego zliczającego w tył –

zmniejsza on swój stan wewnętrzny w takt zliczanych impulsów.

Rys.2. Licznik szeregowy zliczający w tył o pojemności 8 (modulo 8)

Omówione układy wykorzystują swoją pełną pojemność. Istnieje możliwość zmiany tej

pojemności (zmniejszenia) przez odpowiednie użycie wejść asynchronicznych (S, R). Metoda

projektowania takich liczników polega na określeniu kombinacji wartości wyjść

poszczególnych przerzutników, przy której nastąpi wyzerowanie licznika lub ustawienie stanu

wewnętrznego w czasie przerwy między kolejnymi impulsami zliczanymi.

Zmiana pojemności licznika szeregowego może odbywać się w następujący sposób:

X

J

R

Q

C

K

Q

Q

A

"1"

J

R

Q

C

K

Q

Q

B

"1"

J

R

Q

C

K

Q

Q

C

"1"

Z

Q

A

X

Q

B

Q

C

Q

C

D

R

Q

C

Q

D

R

Q

C

Q

D

R

Q

C

Q

Q

A

Q

B

Z

X

Badanie liczników asynchronicznych

Wszystkie grafiki, zdjęcia, programy oraz treść instrukcji podlegają ochronie prawnej na mocy ustawy o prawie autorskim. Używanie ich w jakikolwiek sposób bez uprzedniego,

pisemnego zezwolenia wydanego przez AGH jest zabronione i może spowodować pociągnięcie do odpowiedzialności cywilnej i karnej w maksymalnym zakresie dopuszczalnym przez

prawo.

3

• przez skrócenie cyklu pracy przy zerowym warunku początkowym,

• przez zmianę warunku początkowego,

• przez opuszczenie wybranych stanów wewnętrznych licznika (układ z tzw.

przyspieszonym cyklem pracy).

Najprostszym i najczęściej stosowanym rozwiązaniem jest układ pierwszego typu.

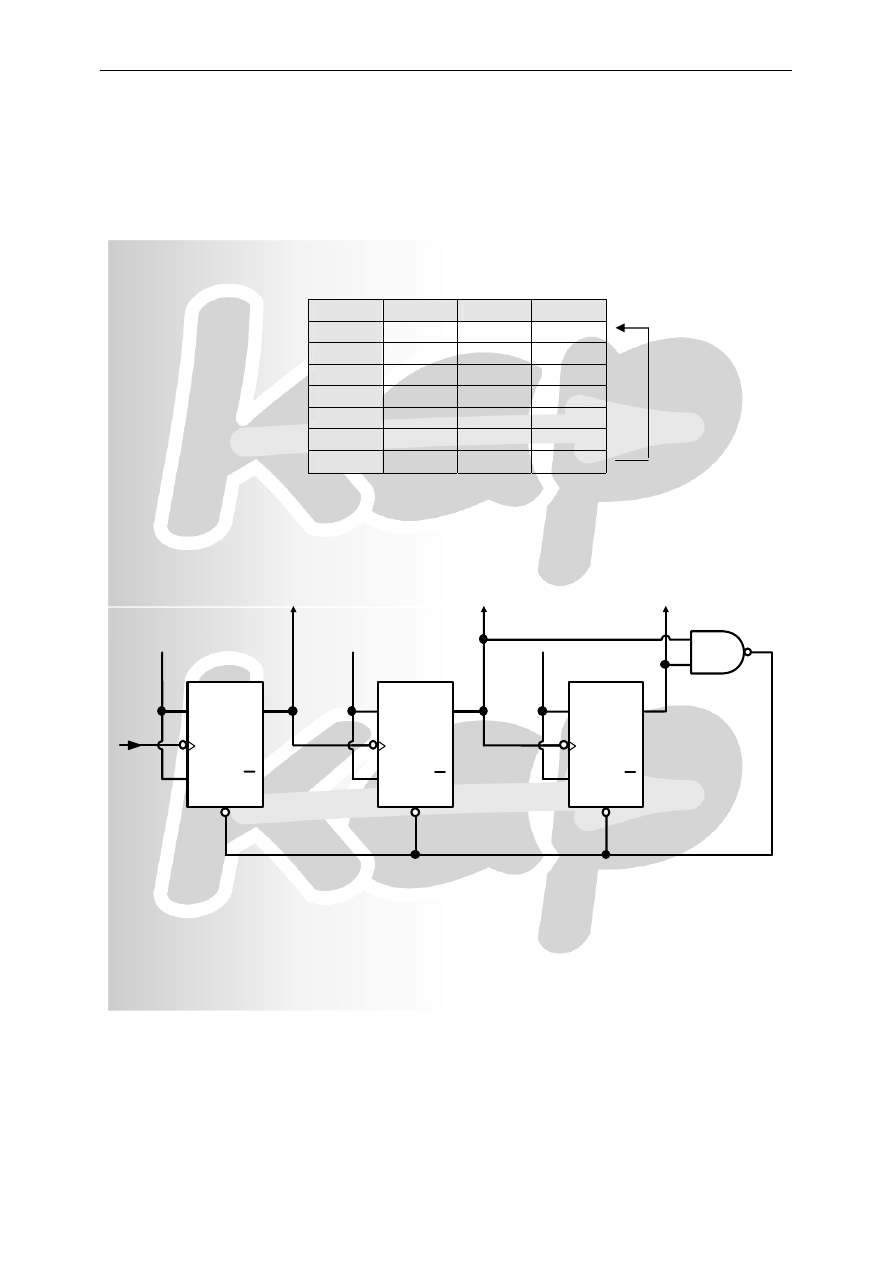

Załóżmy, że pojemność licznika P = 6 (modulo 6). Do budowy tego układu należy użyć

trzech przerzutników, a cykl pracy licznika szeregowego skrócić o dwa stany wewnętrzne. Po

zliczeniu sześciu impulsów ma nastąpić powrót do warunku początkowego Q

C

Q

B

Q

A

=000.

Pracę takiego licznika można zilustrować następującą sekwencją (tablica stanów):

x

Q

C

Q

B

Q

A

0 0 0 0

1 0 0 1

2 0 1 0

3 0 1 1

4 1 0 0

5 1 0 1

6

1

→0 1→0

0

Pozycja x oznacza numer kolejnego impulsu zliczanego. Po wprowadzeniu sześciu

impulsów licznik zostaje wyzerowany, zanim pojawi się impuls siódmy. Wartości Q

C

Q

B

=11

powinny wyzerować licznik. Licznik działający zgodnie z omówionym programem

przedstawia rysunek 3.

Rys.3. Licznik szeregowy modulo 6, zliczający w przód

Jak widać, projektowanie tego typu liczników jest bardzo proste i polega na stosowaniu

następujących zasad:

• dla zadanej pojemności P licznik zawiera n przerzutników przy warunku P ≤ 2

n

,

• łączymy n przerzutników w kaskadę o pojemności 2

n

,

• z ostatniej sekwencji stanów licznika odpowiadającej zadanej pojemności P tworzymy

sygnał sprzężenia zwrotnego zerującego licznik.

W układzie na rysunku 3, sygnały Q

C

Q

B

=11 generują wartość zero na wyjściu bramki NAND.

Sygnał ten zeruje wszystkie przerzutniki przez wejście zerujące (R).

X

J

R

Q

C

K

Q

Q

A

"1"

J

R

Q

C

K

Q

Q

B

"1"

J

R

Q

C

K

Q

Q

C

"1"

Badanie liczników asynchronicznych

Wszystkie grafiki, zdjęcia, programy oraz treść instrukcji podlegają ochronie prawnej na mocy ustawy o prawie autorskim. Używanie ich w jakikolwiek sposób bez uprzedniego,

pisemnego zezwolenia wydanego przez AGH jest zabronione i może spowodować pociągnięcie do odpowiedzialności cywilnej i karnej w maksymalnym zakresie dopuszczalnym przez

prawo.

4

5. Przebieg ćwiczenia:

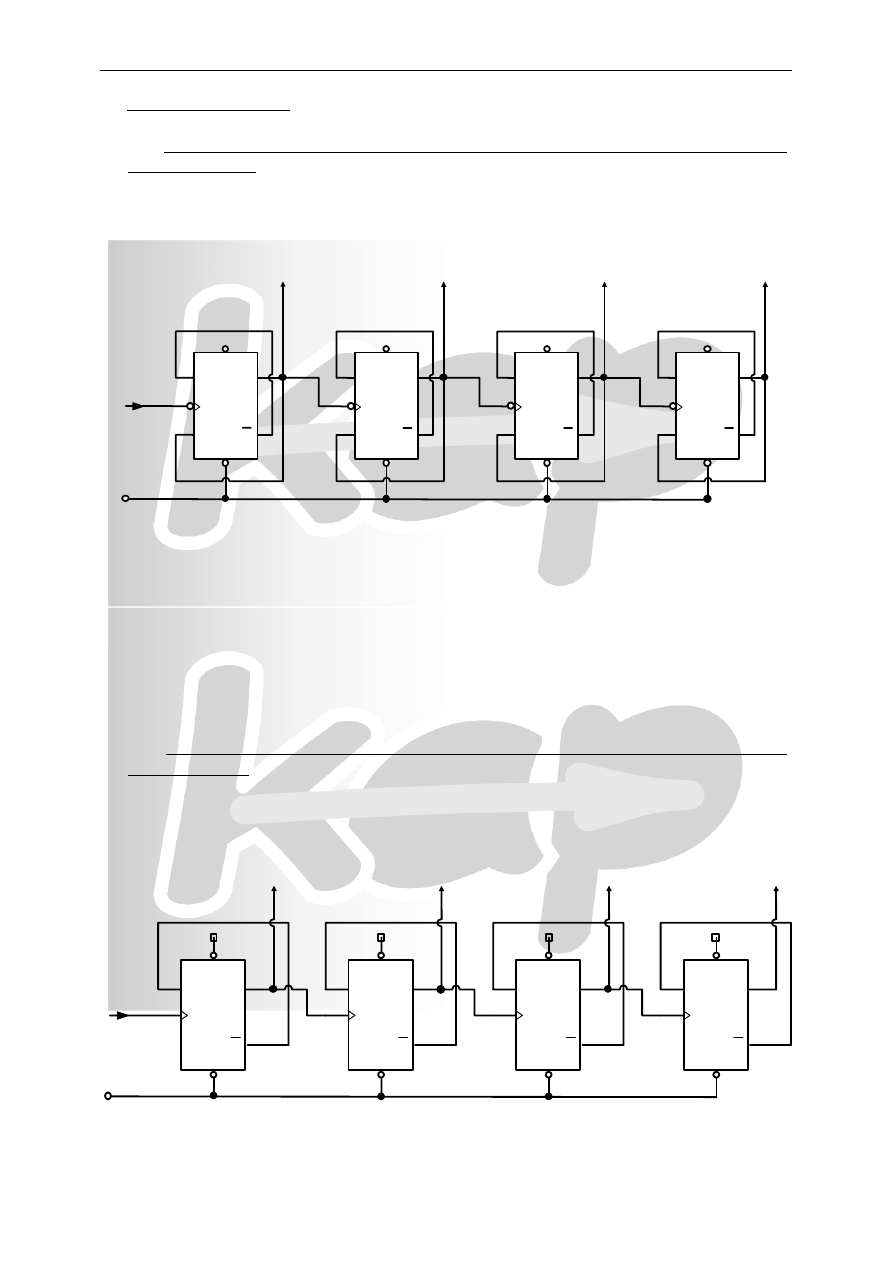

5.1. Badanie licznika szeregowego modulo 16, zliczającego w przód, zbudowanego z

przerzutników JK.

a) wykorzystując płytki montażowe z dwoma układami UCY7476 zbudować strukturę

licznika wg schematu pokazanego na rysunku 4,

Rys. 4. Licznik szeregowy modulo 16, zliczający w przód

b) na wejście zegarowe pierwszego przerzutnika podłączyć sygnał w standardzie TTL z

generatora,

c) przy pomocy oscyloskopu z pamięcią zaobserwować przebiegi napięć na wyjściach

poszczególnych przerzutników,

d) zarejestrować przebiegi na wyjściach wykorzystując do tego celu komputer z

przygotowanym oprogramowaniem,

e) zapisać tabelę stanów logicznych dla badanego licznika.

5.2. Badanie licznika szeregowego modulo 16 zliczającego w tył, zbudowanego z

przerzutników D.

a) wykorzystując płytki montażowe z dwoma układami UCY7474 zbudować strukturę

licznika wg schematu pokazanego na rysunku 5,

Rys. 5. Licznik szeregowy modulo 16, zliczający w tył

zerowanie

Sygnał z

generatora

TTL

Do oscyloskopu 2-kanałowego z pamięcią (możliwość obserwacji 4 przebiegów równocześnie)

J

R

Q

S

C

K

Q

J

R

Q

S

C

K

Q

J

R

Q

S

C

K

Q

J

R

Q

S

C

K

Q

Q

A

Q

B

Q

C

Q

D

Sygnał z

generatora

TTL

Q

D

Do oscyloskopu 2-kanałowego z pamięcią (możliwość obserwacji 4 przebiegów równocześnie)

D

R

Q

Q

S

Q

A

Q

B

D

R

Q

Q

S

D

R

Q

Q

S

Q

C

D

R

Q

Q

S

C

C

C

C

zerowanie

Badanie liczników asynchronicznych

Wszystkie grafiki, zdjęcia, programy oraz treść instrukcji podlegają ochronie prawnej na mocy ustawy o prawie autorskim. Używanie ich w jakikolwiek sposób bez uprzedniego,

pisemnego zezwolenia wydanego przez AGH jest zabronione i może spowodować pociągnięcie do odpowiedzialności cywilnej i karnej w maksymalnym zakresie dopuszczalnym przez

prawo.

5

b) na wejście zegarowe pierwszego przerzutnika podłączyć sygnał w standardzie TTL z

generatora,

c) przy pomocy oscyloskopu z pamięcią zaobserwować przebiegi napięć na wyjściach

poszczególnych przerzutników,

d) zarejestrować przebiegi na wyjściach wykorzystując do tego celu komputer z

przygotowanym oprogramowaniem,

e) zapisać tabelę stanów logicznych dla badanego licznika.

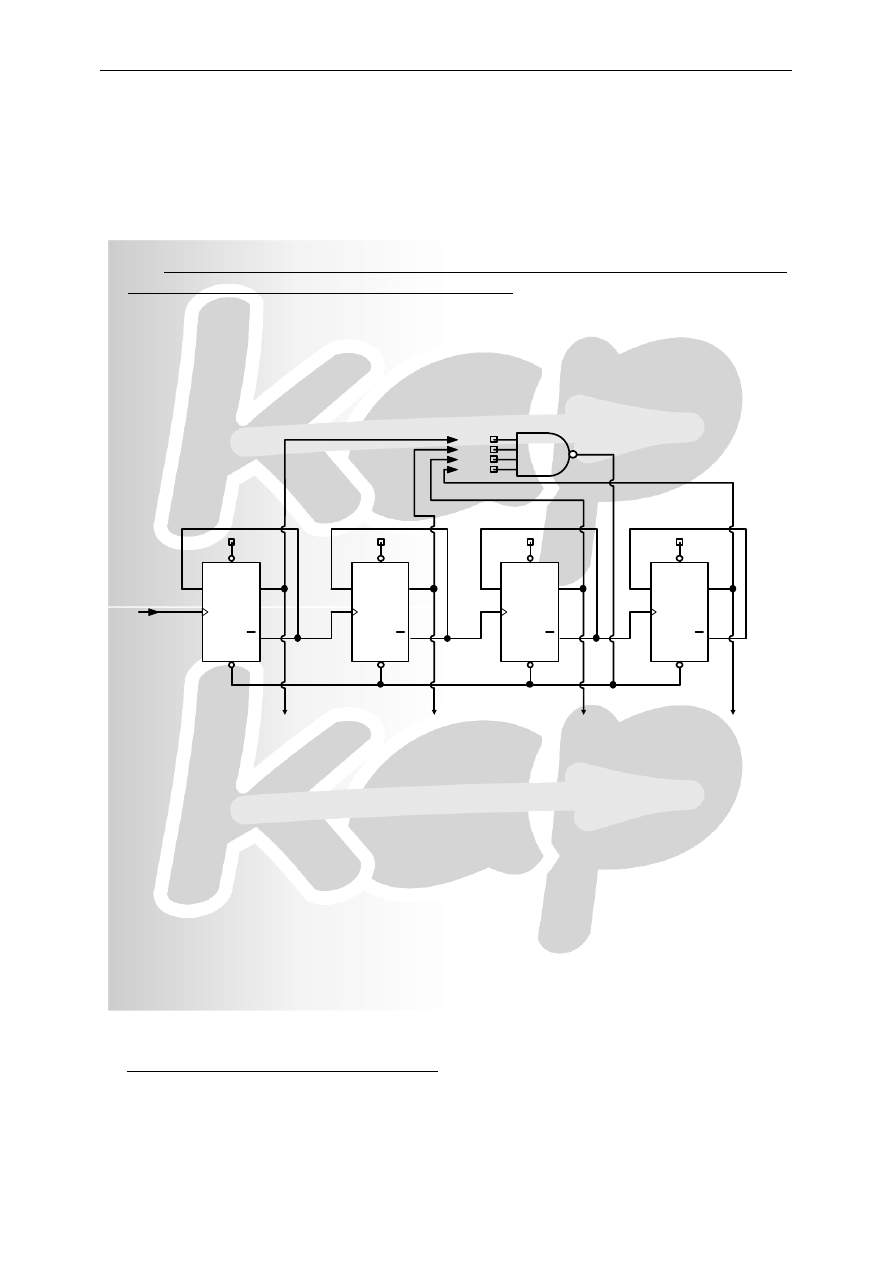

5.3. Badanie licznika szeregowego modulo N, zliczającego w przód, zbudowanego z

przerzutników D z wykorzystaniem wejść zerujących.

a) dla zadanej ilości zliczanych impulsów N zaprojektować układ ograniczający ilość

generowanych impulsów wykorzystując wejścia zerujące (R) przerzutników oraz

bramki NAND,

b) wykorzystując płytki montażowe z układami UCY 7474 i UCY 7400 (UCY 7420)

zbudować strukturę licznika wg schematu pokazanego na rysunku 6,

Rys. 6. Licznik szeregowy modulo N, zliczający w przód, zbudowany

z wykorzystaniem wejść zerujących (R)

c) na wejście zegarowe pierwszego przerzutnika podłączyć sygnał w standardzie TTL z

generatora,

d) przy pomocy oscyloskopu z pamięcią zaobserwować przebiegi napięć na wyjściach

poszczególnych przerzutników,

e) zarejestrować przebiegi na wyjściach wykorzystując do tego celu komputer z

przygotowanym oprogramowaniem,

f) zapisać tabelę stanów logicznych dla badanego licznika,

g) przy pomocy częstościomierza dokonać pomiaru częstotliwości sygnałów na wejściu

zegarowym C pierwszego przerzutnika oraz wyjściu Q

D

ostatniego przerzutnika,

h) powtórzyć punkty a) – g) dla licznika zbudowanego z przerzutników JK (UCY 7476).

6. Sprawozdanie z przebiegu ćwiczenia

Na podstawie przeprowadzonych pomiarów należy przygotować sprawozdanie, które

powinno zawierać: schemat ideowy, tabele stanów logicznych, przebiegi na wyjściach

przerzutników dla badanych układów liczników oraz wnioski końcowe.

D

R

Q

Q

S

D

R

Q

Q

S

D

R

Q

Q

S

D

R

Q

Q

S

Sygnał z

generatora

Q

A

Q

B

Q

C

Q

D

Do oscyloskopu 2-kanałowego z pamięcią (możliwość obserwacji 4 przebiegów równocześnie)

C

C

C

C

Wyszukiwarka

Podobne podstrony:

badanie licznikow asynchronicznych

Badanie maszyny asynchronicznej Nieznany

1 Badanie filtrow RC Nieznany (2)

Montowanie i badanie sieci tele Nieznany

Badanie stalych materialowych s Nieznany (2)

BADANIE STATYSTYCZNEGO CHARAKTE Nieznany

Badania aktywnosci mineralnych Nieznany

Badanie lamp metalohalogenkowyc Nieznany

Badanie parametrow charakteryzu Nieznany (2)

2 Badanie ukladow dopasowania i Nieznany

Badanie wzmacniaczy operacyjnyc Nieznany (2)

Badanie i diagnozowanie pacjent Nieznany

liczniki asynchroniczne

1 Badanie charakterystyk staty Nieznany (2)

OII05 Badanie przemian energii Nieznany

liczniki asynchroniczne nasze

Badanie licznika indukcyjnego jednofazowego

BADANIE LICZNIKA INDUKCYJNEGO 1FAZOWEGO, licznik-radzio.spr, POLITECHNIKA RADOMSKA

więcej podobnych podstron