Laboratorium

8

Temat: Pamięć RAM. Typ tablicowy (array), instrukcja loop i pętla for.

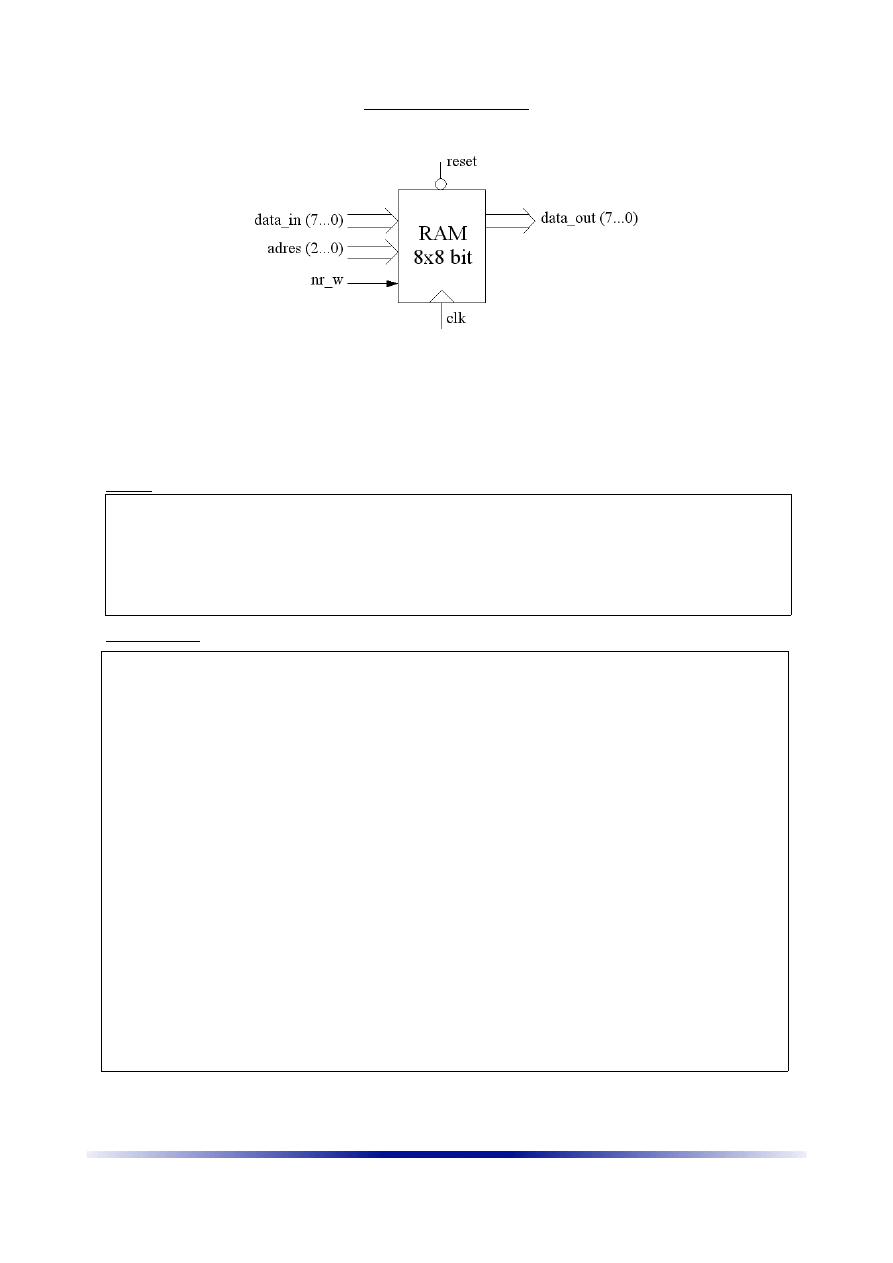

1. Układ pamięci 8x8 (8 komórek, 8 bitowych)

gdzie:data_in (7...0) – dane wejściowe

data_out (7...0) – dane wyjściowe

adres (2..0) – wejście adresowe

nr_w – wejście sterujące (zapis/odczyt)

2. Realizacja w języku VHDL (fragmenty)

entity:

architecture:

3. Zadania do realizacji:

a) Zrealizować układ pamięci, przeprowadzić symulację

Projektowanie układów VLSI

© 2005 Copyright by Tomasz Fałat

port

( clk,reset

:

in

std_logic;

-- zegar, reset

data_in

:

in

std_logic_vector (7

downto

0);

-- wejście danych

data_out

:

out

std_logic_vector (7

downto

0);

-- wyjście danych

adres

:

in

std_logic_vector (2

downto

0);

-- wejście adresowe

nr_w

:

in

std_logic);

-- kierunek transmisji danych (not read write)

-- definicja bloków pamięci, typ tablicowy (8 bloków po 8-bit std_logic_vector's)

type

rejestry

is

array

(7

downto

0)

of

std_logic_vector (7

downto

0);

signal

pamiec : rejestry;

--definicja pamięci RAM (typu rejestry)

begin

-- programowanie rejestrów (nr_w='1'):

process

(clk, reset)

begin

if

reset = '0'

then

-- zerowanie pamięci, instrukcja loop i pętla for:

for

index

in

0

to

7

loop

pamiec(index) <= "00000000";

end

loop

;

...

elsif

clk'event

and

clk ='1'

then

if

nr_w = '1'

then

-- zapis do pamięci

case

adres

is

when

"000" => pamiec(0) <= data_in;

...

else

-- odczyt pamięci

...

end prosess;

Wyszukiwarka

Podobne podstrony:

Laboratorium08-PamięćRAMTypTablicowyArrayInstrukcjaLoopIPętlaFor

Laboratorium budowy urządzeń mikrokomputerowych, Programator pamięci i mikrokomputerów jednoukładowy

03 Odświeżanie pamięci DRAMid 4244 ppt

wykład 12 pamięć

8 Dzięki za Pamięć

Kontrola badań laboratoryjnych

badania laboratoryjne 6

ROZRÓD Badanie terenowe i laboratoryjne mleka

06 pamięć proceduralna schematy, skrypty, ramyid 6150 ppt

Diagnostyka laboratoryjna chorób serca i mięśni poprzecz (2)

Pamięć

PAMIĘĆ 3

więcej podobnych podstron