Radioelektronik Audio-HiFi-Video 2/2001

Prosty uk³ad

do testowania wejæ

uk³adów cyfrowych

P

odczas prze³¹czania zestyków me-

chanicznych i elektromechanicz-

nych do³¹czonych do wejæ uk³a-

dów elektronicznych powstaj¹ nie-

po¿¹dane sygna³y elektryczne maj¹ce cha-

rakter ci¹gów w¹skich impulsów o amplitu-

dach bliskich napiêciu zasilania. Mog¹ one

w powa¿ny sposób zak³óciæ dzia³anie urz¹-

dzeñ. Aby temu zapobiec stosuje siê na

wejciach uk³adów specjalne obwody, które

powoduj¹, ¿e uk³ad reaguje na pierwszy

z powstaj¹cych impulsów, a pozosta³e nie-

po¿¹dane ignoruje. Do sprawdzenia odpor-

SYMULATOR DRGAÑ

ZESTYKÓW

zale¿ne od napiêcia na kondensatorze C2

i stopniowo narasta, ze sta³¹ czasow¹ zale¿-

n¹ od elementów C2 i R2. Stan logiczny

wyjcia bramki U2A (Ex-OR) przyjmuje war-

toæ wysok¹ jedynie wówczas, gdy stany

obu jej wejæ s¹ ró¿ne. Poniewa¿ w chwili

doprowadzenia impulsu wyzwalaj¹cego na

wejciu (1) bramki U2A wystêpowa³ stan ni-

ski, a na drugim wejciu (2) nast¹pi³a zmia-

na stanu na wysoki, to na wyjciu U2A rów-

nie¿ nast¹pi³a zmiana stanu na wysoki. Jed-

noczenie nastêpuje ³adowanie kondensa-

tora C2 i narastanie napiêcia na wejciu

bramki, które po osi¹gniêciu wartoci progo-

wej powoduje zmianê stanu jej wyjcia.

W rezultacie uzyskuje siê generacjê impul-

su prostok¹tnego o czasie trwania bliskim ilo-

czynowi C2 i R2, tutaj ok. 10 ms. W tym

czasie, napiêcie na wejciu bramki U1B ma

wartoæ odpowiadaj¹c¹ stanowi wysokie-

mu i s¹ stworzone warunki do generacji im-

pulsów w generatorze wyzwalanym utworzo-

nym z elementów U1B, C3 i R3. Czas trwa-

nia jest zale¿ny od C3 i R3, s¹ generowane

impulsy o czasie trwania ok. 1 ms. Inne sze-

rokoci impulsów i czasy trwania ich pacz-

ki mo¿na uzyskaæ stosuj¹c inne wartoci

elementów C2, R2, C3 i R3.

Ostatnim stopniem symulatora jest bramka

U2B, na której wyjciu uzyskuje siê sygna-

³y testowe symuluj¹ce drgania zestyków.

Wystêpuj¹ one przez ok. 10 ms po zainicjo-

waniu sygna³em wyzwalaj¹cym, zarówno

przy sygna³ach opadaj¹cych jak i narasta-

j¹cych.

Na rys. 3 przedstawiono p³ytkê drukowan¹

uk³adu, a na rys. 4 rozmieszczenie elemen-

tów. Do budowy modelu symulatora za-

k³óceñ wykorzystano uk³ady scalone CMOS

serii 74 HC, ale mog¹ byæ u¿yte uk³ady in-

nych rodzin CMOS, a nawet uk³ady TTL.

Nale¿y jedynie uwzglêdniæ, ¿e uk³ady TTL

nie toleruj¹ tak du¿ych rezystancji i nale¿y

je wyranie zmniejszyæ przy jednoczesnym

proporcjonalnym powiêkszeniu pojemnoci

u¿ytych kondensatorów.

(cr)

n

Rys. 3. P³ytka drukowana symulatora drgañ

zestyków (skala 1:1)

Rys. 4. Rozmieszczenie elementów na p³ytce

drukowanej symulatora drgañ zestyków

noci wejcia uk³adu cyfrowego na dzia³anie

impulsów wielokrotnych stosuje siê uk³ady,

które po doprowadzeniu sygna³u wyzwala-

j¹cego generuj¹ paczkê kilku lub kilkuna-

stu impulsów o amplitudzie równej napiêciu

zasilania badanego uk³adu.

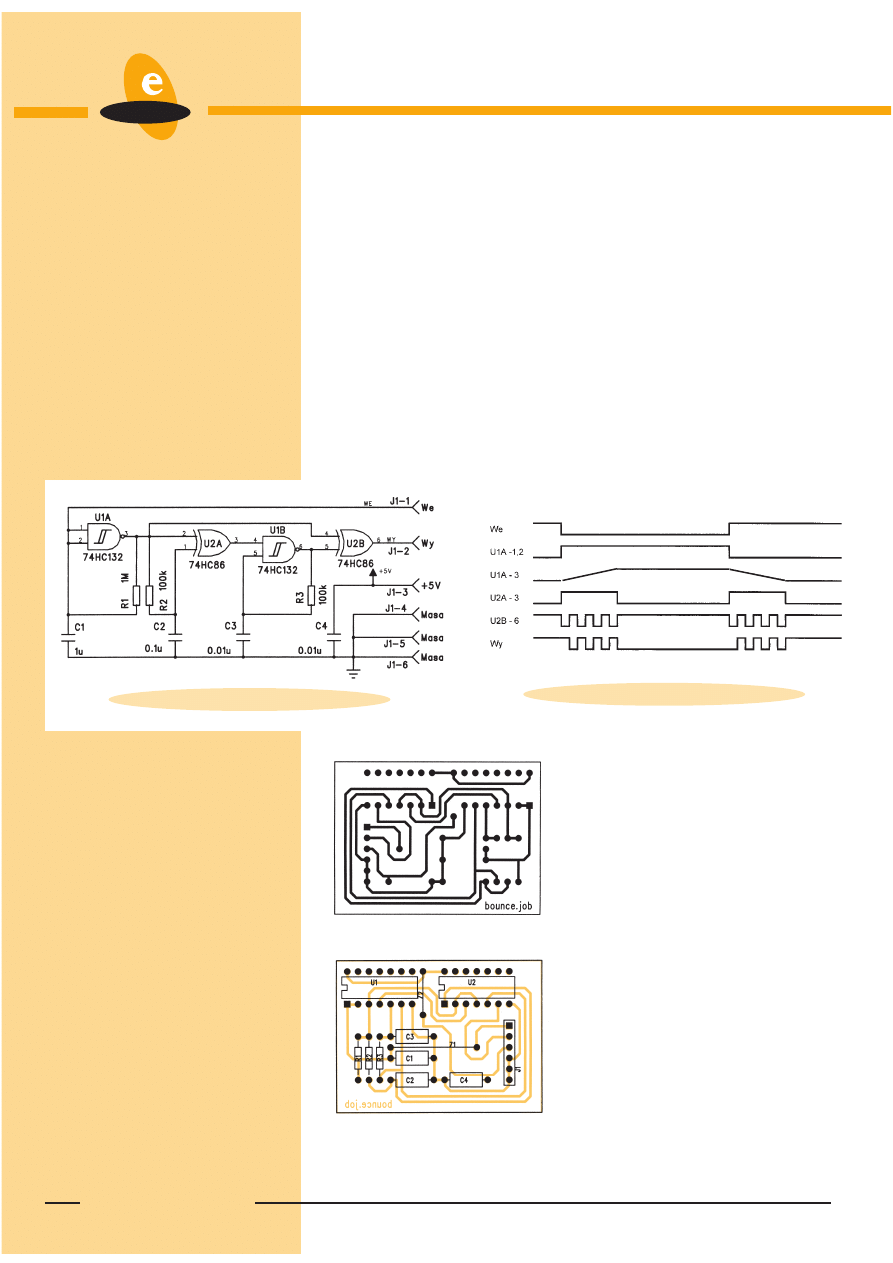

Uk³ad przedstawiony na rys. 1 symuluje sy-

gna³y powstaj¹ce w wyniku drgañ zestyków

mechanicznych, zarówno przy ich zamyka-

niu jak i otwieraniu. Na rys. 2 przedstawio-

no przebiegi wystêpuj¹ce w uk³adzie. Sygna-

³em wejciowym mo¿e byæ sygna³ o pozio-

mie wg standardu TTL, o stanie niskim lub

wysokim.

W stanie spoczynkowym, na wejciu uk³adu

(wejcia bramki U1A) wystêpuje stan logicz-

ny wymuszony przez obwód do³¹czony do

wejcia uk³adu (We), tutaj jest to stan wyso-

ki. Zmiana stanu wejcia z wysokiego pozio-

mu logicznego na niski powoduje odwrotn¹

zmianê stanu logicznego na wyjciu i jedno-

czenie na jednym z wejæ (2) bramki U2A.

Napiêcie na drugim wejciu tej bramki (1) jest

Rys. 1. Schemat symulatora drgañ zestyków

Rys. 2. Przebiegi w uk³adzie wg rys. 1

Wyszukiwarka

Podobne podstrony:

2001 02 20

2014 02 19

2001 02 Szkoła konstruktorów

2001 02 39

2001 02 28

2001 02 zaliczenie poprawkowe

2001 02 01

2001 01 19

DTR S116 2008 02 19

Anatomia Kolokwium II 2001-02, anatomia, Anatomia(1)

2013 02 19 Raport NIK

Everyday Practical Electronics 2001 02

2001 07 19 1478

2001 02 22

2001 02 43

2001 02 16

LOGISTYKA W19., Wykład 19 2001-03-19

2001-02 kolokwium 1

więcej podobnych podstron