1

Elementy cyfrowe i układy

logiczne

Wykład 10

2

2

2

2

Uszkodzenia i modele błędów

Legenda

Testowanie układów logicznych

Potrzeba testowania

Generowanie wektorów testowych dla

układów kombinacyjnych

2

3

3

3

3

Potrzeba testowania

Gdy układ logiczny lub system cyfrowy został

wyprodukowany,

wówczas

jest

niezbędne

jego

sprawdzenie w celu wykrycia wad (uszkodzeń), które

mogły powstać podczas jego wytwarzania lub później

podczas transportu i użytkowania.

(Zakładamy, że opis logiczny układu był poprawny, co

stwierdzono przez sprawdzenie za pomocą symulatora

logicznego).

4

4

4

4

Potrzeba testowania – cd.

Testowanie

układów

jest bardzo ważne

i powinno

być

zaplanowane

już

w

początkowym

etapie

projektowania, ponieważ procesy stosowane podczas

wytwarzania układów nie są doskonałe.

Celem

testowania

jest

wykrycie

wad,

tak

aby

uszkodzony układ mógł być zidentyfikowany. Wyniki

testowania mogą być zwrotnie wykorzystane na linii

produkcyjnej w celu poprawienia procesu produkcji.

3

5

5

5

5

Potrzeba testowania – cd.

Co może spowodować defekt układu?

• Układ może mieć fizyczne defekty powstające

podczas wytwarzania. Defekty te mogą zmienić

działanie układu.

• Układ może zostać uszkodzony podczas transportu.

6

6

6

6

Potrzeba testowania – cd.

Testowanie

- poważne wyzwanie intelektualne dla

konstruktorów (duża liczba możliwych uszkodzeń

układu).

Jednym

sposobem

sprawdzenia

działania

obudowanych elementów jest zastosowanie sygnałów

testowych doprowadzonych do zewnętrznych wejść

obudowanego elementu i obserwowanie sygnałów na

jego wyjściach. Jeżeli sygnały wyjściowe różnią się od

oczekiwanych,

to

przyjmujemy,

ż

e

w

układzie

występuje jakieś uszkodzenie lub wystąpił błąd

logiczny w projekcie układu.

4

7

7

7

7

Potrzeba testowania – cd.

Błąd w projekcie może być wykryty za pomocą

symulatora po zastosowaniu odpowiednich

wektorów

testowych

.

Wektory testowe

są tworzone na podstawie funkcji

jaką ma realizować układ. W celu przeanalizowania

występujących

błędów

stosuje

się

odpowiednie

wektory testowe do rozpoznania poszczególnych

błędów w układzie.

Często nie trzeba lokalizować miejsca uszkodzenia,

wystarczy tylko stwierdzenie, że w układzie występuje

usterka (chyba że celem badania są jakieś szczególne

aspekty procesu wytwarzania).

8

8

8

8

Uszkodzenia i modele błędów

Istnieje

wiele

możliwych

rodzajów

uszkodzeń

fizycznych wpływających na działanie układu.

Uszkodzenia

mogą

być

modelowane

z

uwzględnieniem wpływu, jaki mają na działanie

układu.

Modele błędów

Modele błędów

spowodowanych

uszkodzeniami

prowadzącymi

do błędów logicznych

Modele błędów

spowodowanych

uszkodzeniami

parametrycznymi

5

9

9

9

9

Modele błędów logicznych

dotyczą uszkodzeń, które

wpływają

na

funkcję

logiczną

układu

(działanie

funkcjonalne układu).

Modele błędów parametrycznych

dotyczą uszkodzeń,

które wpływają na wartości parametrów układu, takich

jak napięcie, prąd, próg przełączania i opóźnienie.

Błędy logiczne i parametryczne

10

10

10

10

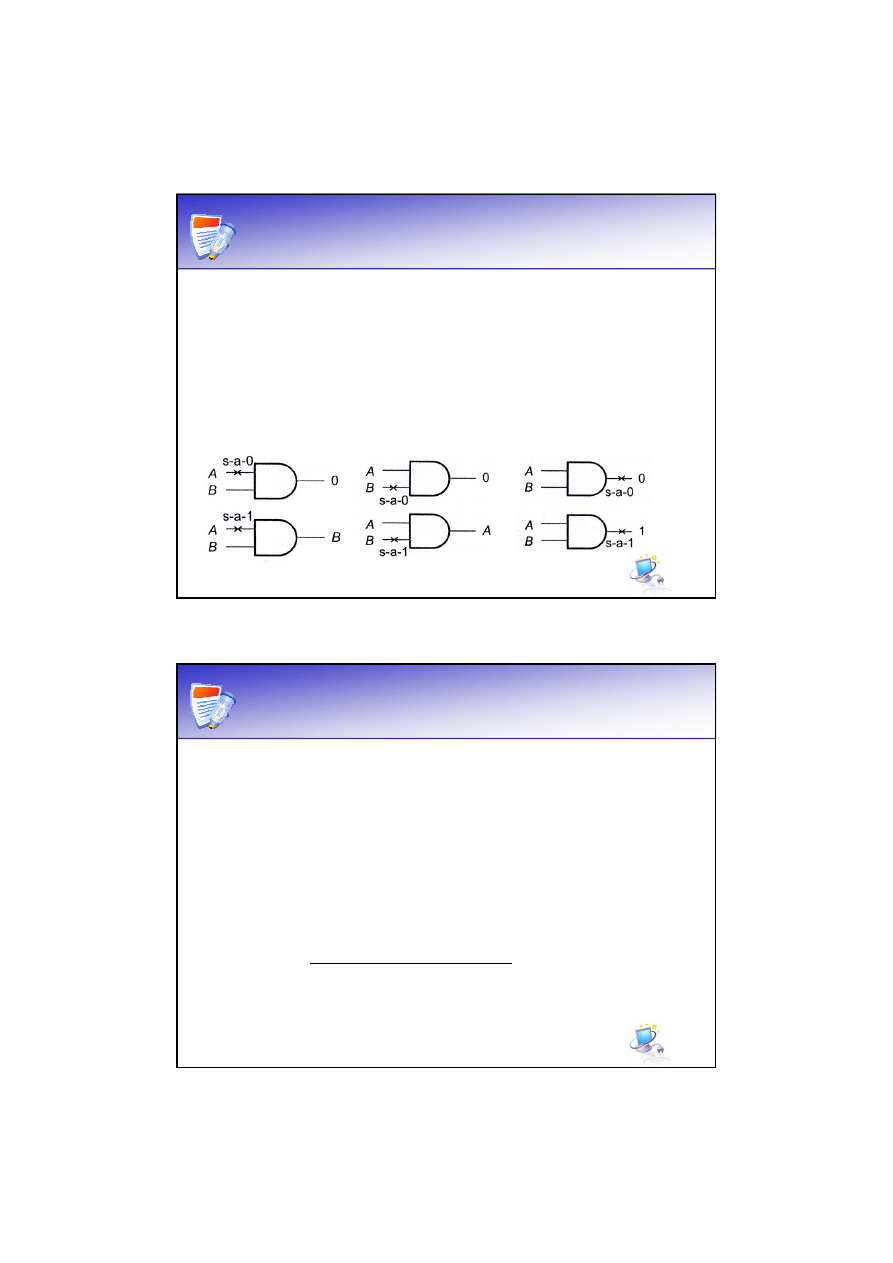

Błąd stałej wartości logicznej

Wiele

błędów

można

modelować

jako

powodujące

występowanie na ścieżce sygnałowej (na wejściu lub wyjściu

bramki) ustalonej wartości logicznej 1 lub ustalonej wartości 0.

Błąd logiczny „

sklejenia z 1

” - uszkodzenie prowadzące do

ustalonej wartości 1 na ścieżce sygnałowej (błąd „stałej 1”:

stuck-at-1, skrótowe oznaczenie s-a-1).

Błąd logiczny „

sklejenia z 0

” - uszkodzenie powodujące

ustaloną wartość 0 (błąd „stałego 0”: stuck-at-0, skrótowe

oznaczenie s-a-0 ).

6

11

11

11

11

Inne rodzaje błędów

Czasami wewnętrzne zwarcie lub rozwarcie może powodować

występowanie ustalonej wartości logicznej 0 lub ustalonej wartości 1

na wyjściu, ale częściej na wyjściu może wystąpić napięcie o

nieokreślonej wartości pośredniej.

12

12

12

12

Inne rodzaje błędów – cd.

Uszkodzenia występujące w układach logicznych CMOS, które nie

mogą być opisane modelem „sklejenia z...", są uszkodzeniami

prowadzącymi do błędów „rozwarcia” (błędy „

stuck open

").

Przy uszkodzeniu powodującym ten błąd, tranzystor zachowuje się

jak obwód trwale rozwarty (duża impedancja). To może powodować,

ż

e na wyjściu przez krótki okres (zwykle kilka milisekund)

występuje poprzednia wartość, gdy oba tranzystory wyjściowe

(push-down, ściągający i pull-up, podciągający) są wyłączane.

7

13

13

13

13

Inne rodzaje błędów – cd.

Uszkodzenie zmostkowania

- zwarcie między dwoma elementami

układu. Jego rzeczywisty wpływ na działanie bramki zależy od

technologii bramki i umiejscowienia zwarcia. Może ono zmienić

funkcję logiczną i spowodować zachowanie się bramki jak przy

błędach typu „sklejenie z..." (stuck-al-fault).

Mogą także wystąpić inne efekty, np. zmostkowanie wejścia z

wyjściem

w

kombinacyjnym

układzie

logicznym

może

spowodować, że zostanie utworzony układ sekwencyjny. Jeżeli dwa

wyjścia są zmostkowane, to wypadkowe napięcie na połączonych

razem liniach będzie zależało od wydajności prądowej bramek

wysterowujących te linie, gdy na jednej bramce jest wysoki poziom

napięcia, a na drugiej niski.

14

14

14

14

Model pojedynczego błędu

„sklejenia”

Model błędu typu „stuck-at” jest najbardziej

popularny z powodu swojej prostoty. Jest on

używany

jako

model

błędów

w

większości

symulatorów.

Rzeczywiste

uszkodzenie

powodujące

błąd

prawdopodobnie znajduje się wewnątrz bramki.

Model sklejania (stuck-at) opisuje skutki występowania

uszkodzeń fizycznych na wejściach lub wyjściach

układu.

8

15

15

15

15

Model pojedynczego błędu - cd.

Dla dwuwejściowej bramki AND możliwych jest sześć

pojedynczych błędów sklejenia (stuck-at), czyli jeden z

dwóch możliwych błędów na każdej z trzech linii.

Ogólnie, przy k liniach sygnałowych występuje 2k

różnych kombinacji pojedynczych błędów.

16

16

16

16

Model pojedynczego błędu - cd.

Przy wielokrotnych błędach występujących jednocześnie,

każda linia sygnałowa może być:

• wolna od błędów,

• „sklejona z 0” (stuck-at-0)

• „sklejona z 1” (stuck-at-l).

Dla danych k różnych linii występuje 3

k

możliwych

kombinacji trzech stanów każdej linii. Jednym z nich jest

kombinacja braku w ogóle błędów na liniach układu.

W związku z tym jest

3

k

-1

różnych kombinacji stanów

określających występowanie przynajmniej jednego błędu na

k

liniach.

9

17

17

17

17

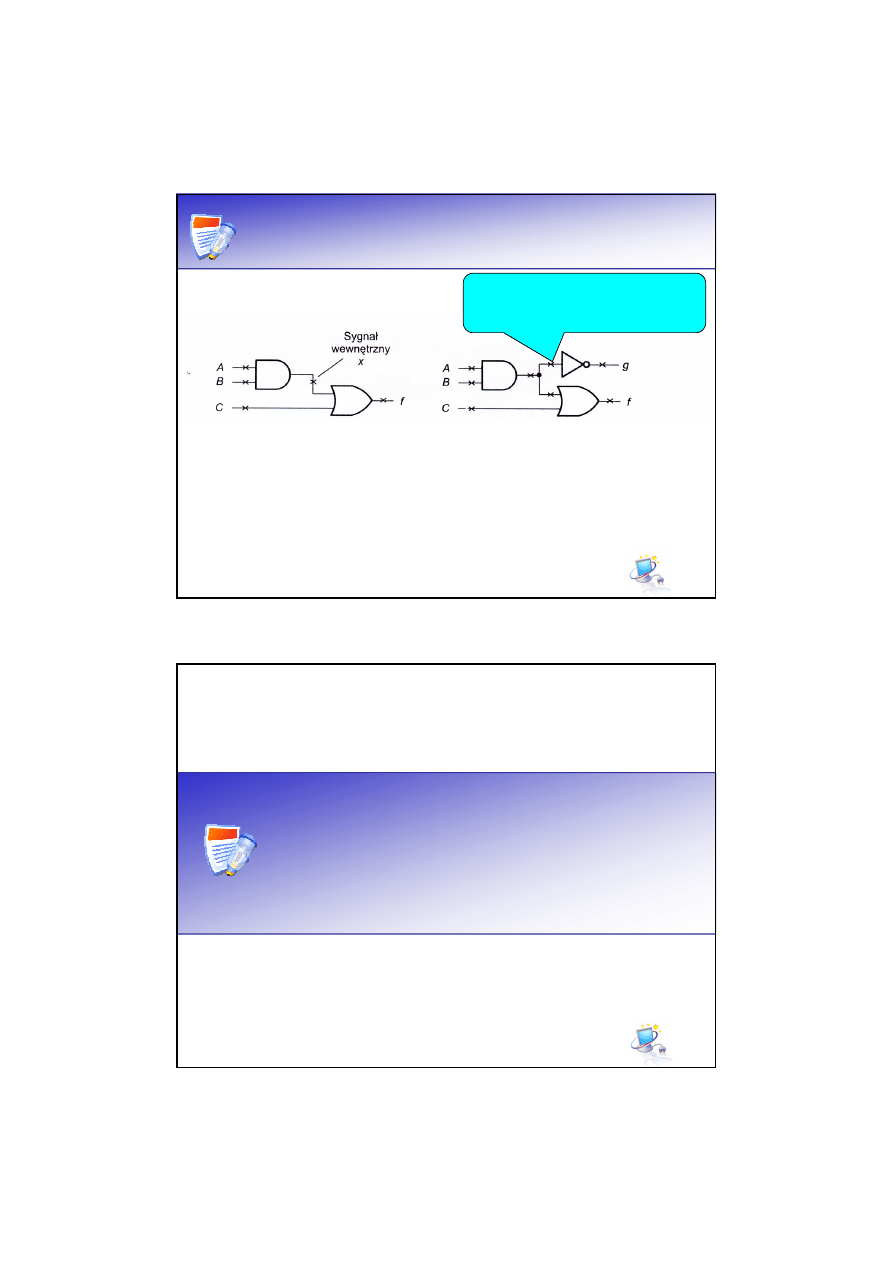

Model pojedynczego błędu - cd.

Lokalizacja błędów w prostym

układzie logicznym (5 możliwych

przypadków wystąpienia błędów:

s-a-0

lub

s-a-1,

czyli

10

możliwych pojedynczych błędów

sklejenia)

Lokalizacja błędów w układzie z

bramką AND obciążoną dwiema

innymi bramkami)

To uszkodzenie może być skutkiem

błędu na wyjściu bramki AND ale

może być też odrębnym uszkodzeniem

18

18

18

18

Generowanie wektorów

testowych dla układów

kombinacyjnych

10

19

19

19

19

Generowanie wektorów testujących

Tylko bardzo prosty układ mógłby być testowany przez

zastosowanie

wszystkich

kombinacji

wartości

sygnałów

wejściowych i porównanie otrzymywanych wartości sygnałów

wyjściowych z tablicą wartości definiującej funkcję układu.

Na przykład, dwuwejściowa bramka AND mogłaby być w pełni

przetestowana po podaniu na wejścia kombinacji wartości

sygnałów:

00

,

01

,

10

i

11

i stwierdzeniu, iż na wyjściu wystąpią

odpowiednio wartości:

0

,

0

,

0

i

1

.

Jeżeli wartości odpowiedzi różnią się w którymś przypadku, to

z całą pewnością wiemy, że w układzie wystąpiło uszkodzenie

powodujące ten błąd.

20

20

20

20

Generowanie wektorów testujących

Wektor

testowy

-

właściwe

kombinacje

wartości

sygnałów wejściowych zastosowane do wykrycia błędu.

Zbiór testów

- grupa wektorów testowych używanych do

sprawdzenia układu.

Ponieważ, wraz ze wzrostem złożoności układu zwiększa

się liczba jego wejść, więc wykorzystywanie do testowania

wszystkich kombinacji wartości sygnałów wejściowych

staje się

niepraktyczne

.

Podstawowym problemem jest więc wybranie

najmniejszej liczby wektorów testowych do wykrycia

błędów.

11

21

21

21

21

Metody tablicowe i algebraiczne

Jeżeli znana jest funkcja boolowska układu, to przez proste

porównania

funkcji

bez

uwzględniania

występowania

uszkodzeń i z uwzględnieniem występowania uszkodzeń można

wyprowadzić wyrażenia boolowskie opisujące wektory testowe.

Można to zrobić na podstawie tablicy prawdy przez zestawienie

wartości sygnałów wyjściowych z uwzględnieniem i bez

uwzględnienia uszkodzeń.

Można także wykonywać pewne przekształcenia algebraiczne

funkcji

boolowskich,

które

mogą

prowadzić

do

zbioru

odpowiednich

testów

(jak

np.

w

boolowskiej

metodzie

różnicowej).

Metody te można stosować dla bardzo małych układów.

22

22

22

22

Metoda

pobudzenia

ścieżki

Metoda pobudzenia (uaktywnienia) ścieżki

(path sensitization

method

) jest metodą odpowiednią dla bardziej złożonych układów

kombinacyjnych.

W tej metodzie stwierdza się, czy jakiś błąd występuje w danym

miejscu dzięki zastosowaniu przeciwnej wartości logicznej do

powodującej błąd w tym miejscu.

Jeżeli test jest dla błędu sklejenia z 1 (s-a-1), to stosujemy wartość

0. Jeżeli test ma wykryć błąd sklejenia z 0 (s-a-0), to stosujemy

wartość 1. Przez zastosowanie odpowiedniej wartości sygnału

wejściowego „włącza się” ścieżkę, którą dany układ przenosi błąd

uszkodzenia z miejsca jego występowania na wyjście, gdzie może

być obserwowany.

12

23

23

23

23

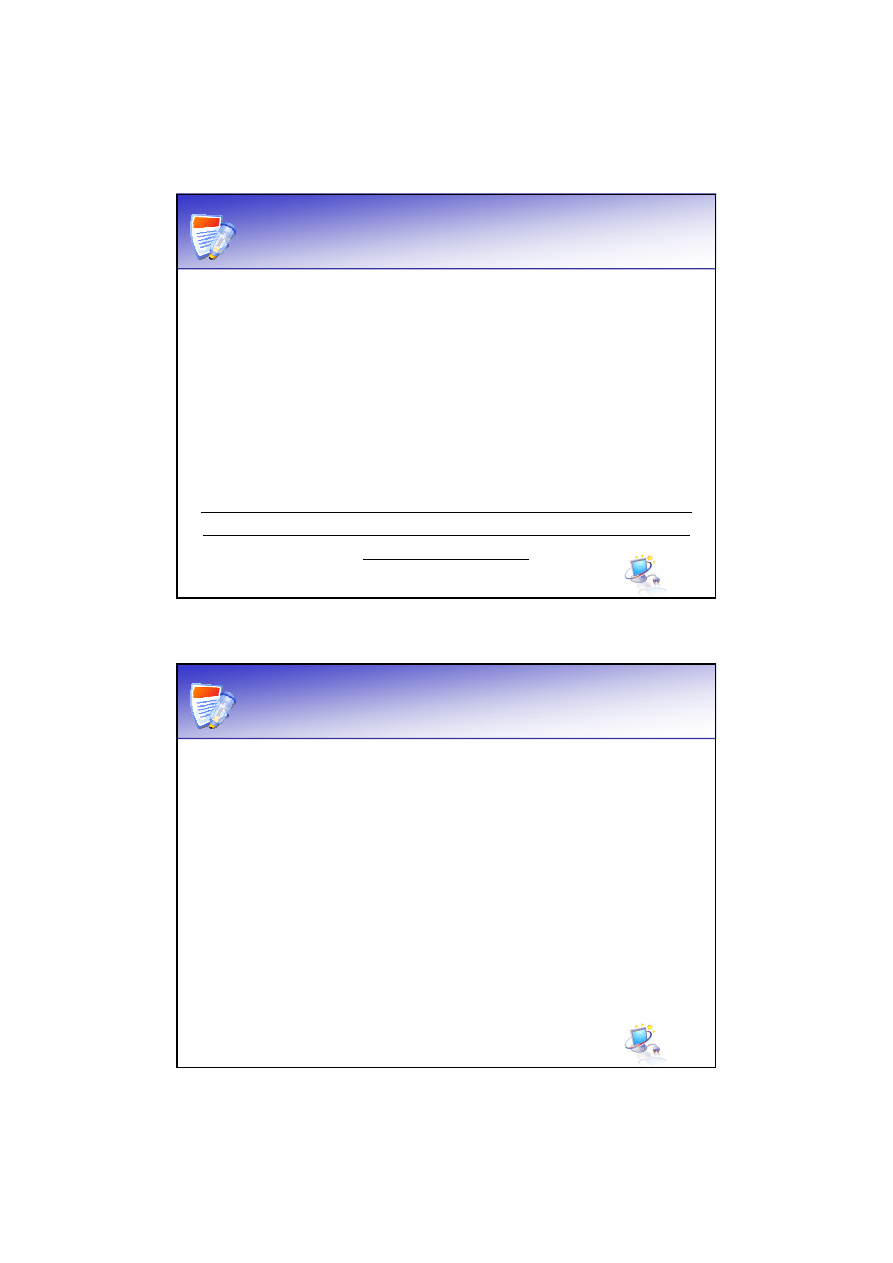

Metoda pobudzania... - przykład

Należy wykryć błąd typu s-a-0 na wyjściu bramki AND.

Wskazane miejsce błędu należy wysterować do wartości 1 (poziom

przeciwny do poziomu uszkodzenia). Można to zrealizować podając

wartość 1 na wejścia branki AND. Następnie musimy spowodować

propagację tego błędu do wyjścia, co można zrealizować podając

wartość 0 na wejście bramki OR. Wartość logiczna na wyjściu

bramki AND (tj. 0 - jeżeli jest uszkodzenie, 1 - gdy nie ma

uszkodzenia) pojawi się na wyjściu bramki OR.

24

24

24

24

W niektórych układach poziom logiczny może być odwrócony - na

przykład, przy użyciu bramek NOR zamiast bramek OR.

Dla ułatwienia opisu odpowiedzi układu zastosowano literę D do

wskazania, że sygnał wyjściowy przy niewystępowaniu błędu ma

wartość l, a przy wystąpieniu błędu w wartość 0.

Podobnie, D wskazuje, że sygnał wyjściowy ma wartość 0 przy

niewystępowaniu

uszkodzenia,

natomiast

wartość

1

przy

występowaniu uszkodzenia.

Symbole

D

i

D

pierwotnie

były

użyte

w

D

-algorytmie

(algorytmicznym sposobie otrzymywania wektorów testowych

metodą pobudzenia ścieżki), opracowanym przez Roth’a w 1967

roku.

Metoda pobudzania... – cd.

D

D

13

25

25

25

25

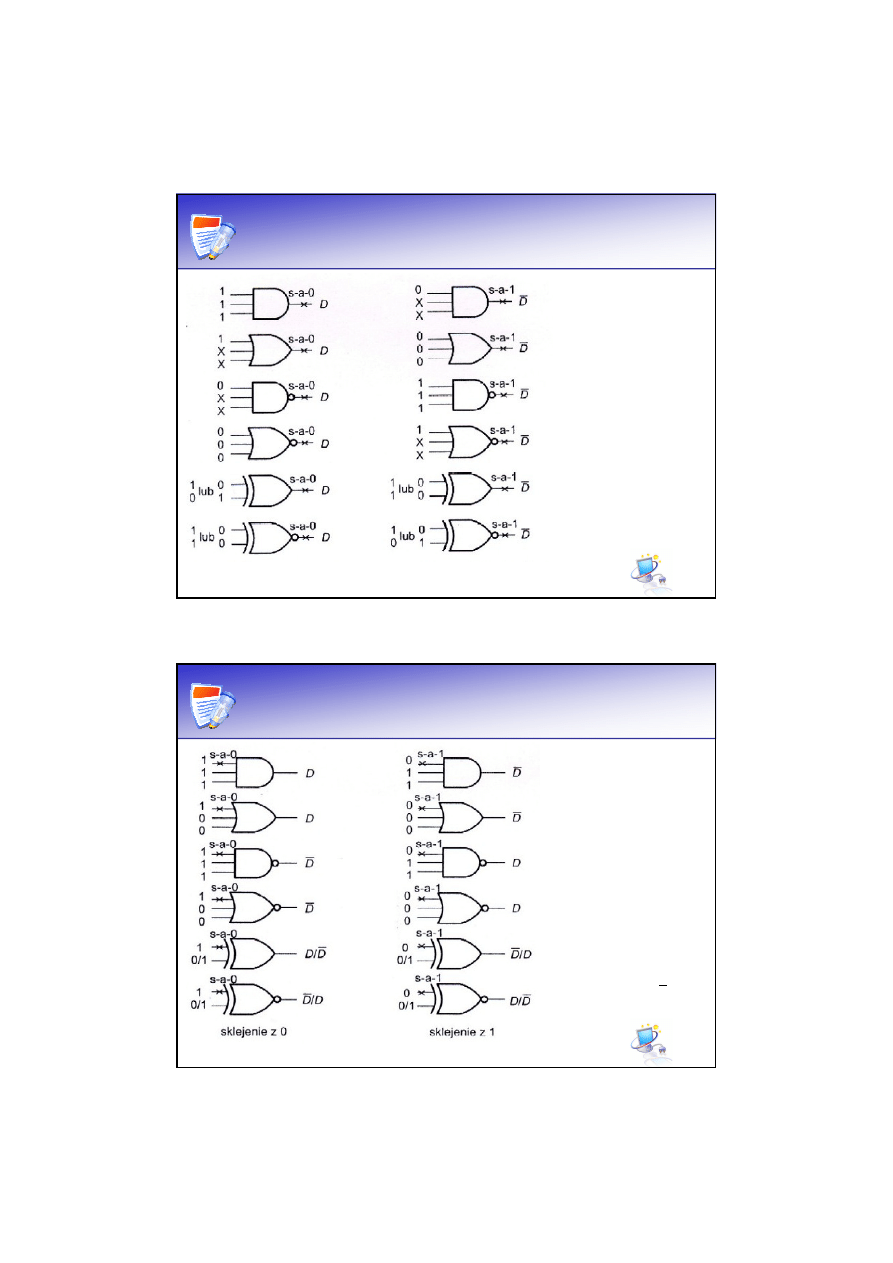

Wymuszanie wartości ...

Rysunek obrazuje wartości

sygnałów

wejściowych

wymagane, aby wymusić

na

wyjściu

każdej

z

podstawowych

bramek

wartość logiczną 0 lub l.

X - wartość nieokreślona

(don't care), czyli może

wówczas

występować

0

albo 1.

Podstawowe bramki mają

nierozróżnialne wejścia, a

więc można je zamieniać

nie

powodując

zmiany

wartości funkcji.

26

26

26

26

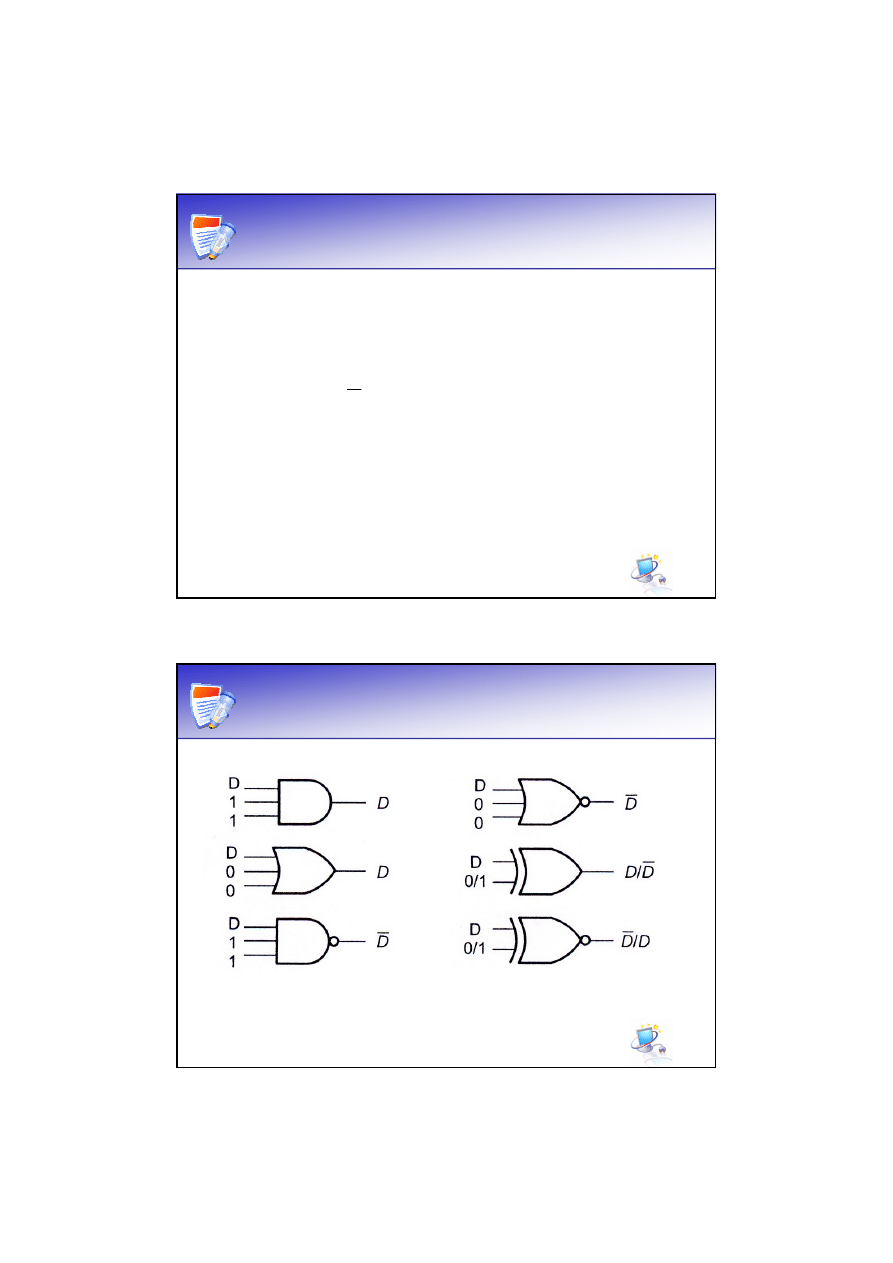

Wymuszanie odpowiednich wartości

Rysunek pokazuje wymagane

wartości sygnałów dla

podstawowych bramek, aby

nastąpiła propagacja błędów z

wejścia bramki na wyjście.

Bramki Ex-OR i Ex-NOR

mają użyteczną cechę, która

powoduje, że błąd z wejścia

jest propagowany przez

bramkę do wyjścia, niezależnie

od wartości logicznej na

pozostałym wejściu

(oczywiście, musimy wiedzieć,

czy poszukiwana wartość

odpowiedzi to D czy D).

14

27

27

27

27

Pobudzanie ścieżki

Każda bramka na ścieżce do zewnętrznego wyjścia powinna być

pobudzona.

Dla bramek podstawowych są potrzebne te same wartości sygnałów

wejściowych,

lecz

w

tym

przypadku

będzie

następowało

propagowanie D lub

.

Pobudzanie (włączanie) ścieżek jest realizowane przez zastosowanie

wartości logicznej l na wejściach bramek AND i NAND, lub przez

podanie wartości 0 na wejścia bramek OR i NOR (wyłączając

oczywiście wejście z występującym błędem). Dowolna wartość może

być natomiast zastosowana na wejściach bramek exclusive-OR i

exclusive-NOR.

D

28

28

28

28

Pobudzanie ścieżki – cd.

15

29

29

29

29

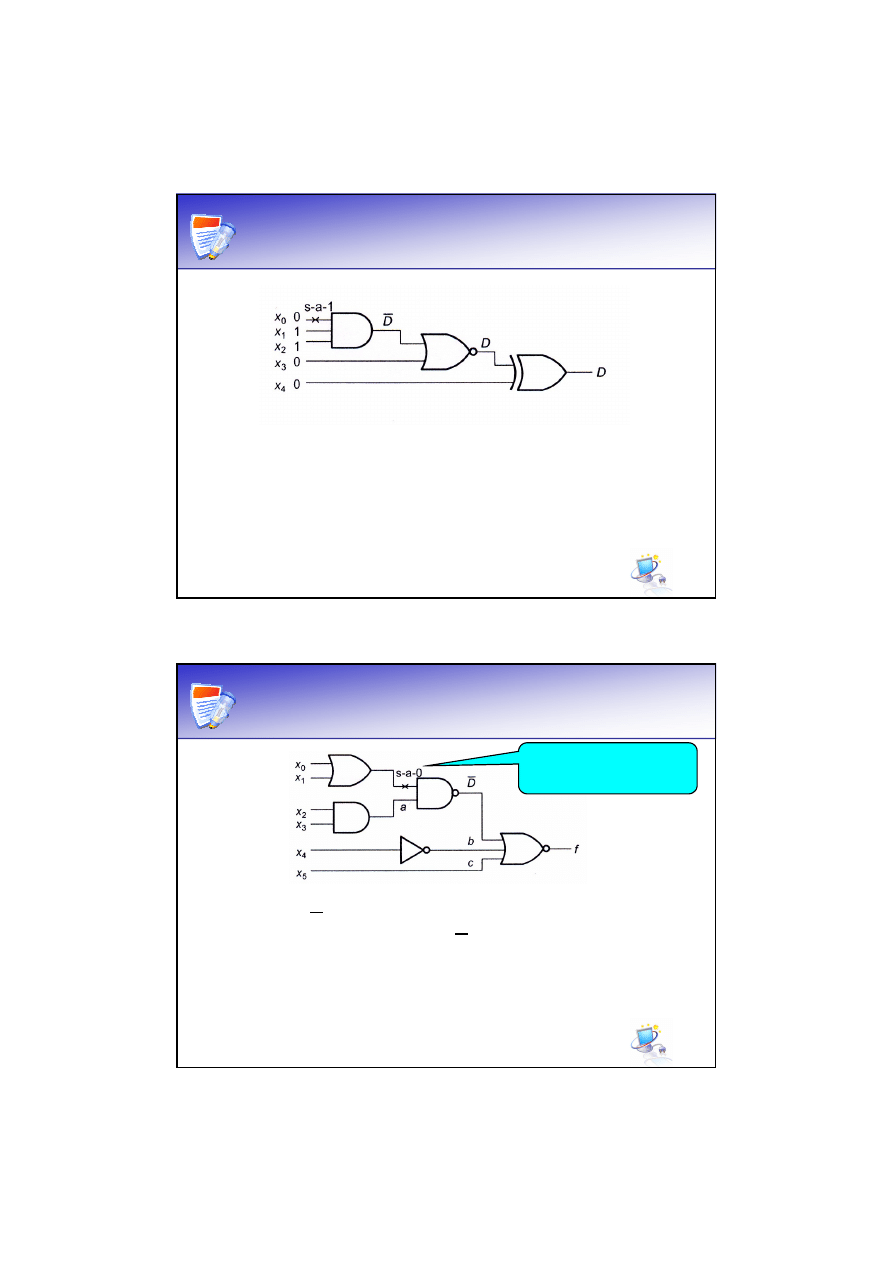

Pobudzanie ścieżki – przykład 1

Sygnałem x

0

=0 usiłujemy wymusić w miejscu występowania

błędu wartość logiczną 0. Sygnały na pozostałych wejściach

zewnętrznych

układu

powodują

pobudzenie

ś

cieżki

do

zewnętrznego wyjścia.

Jeżeli na wyjściu jest wartość l, to wiemy, że błąd nie występuje,

a gdy jest 0, oznacza to, że w układzie występuje błąd.

30

30

30

30

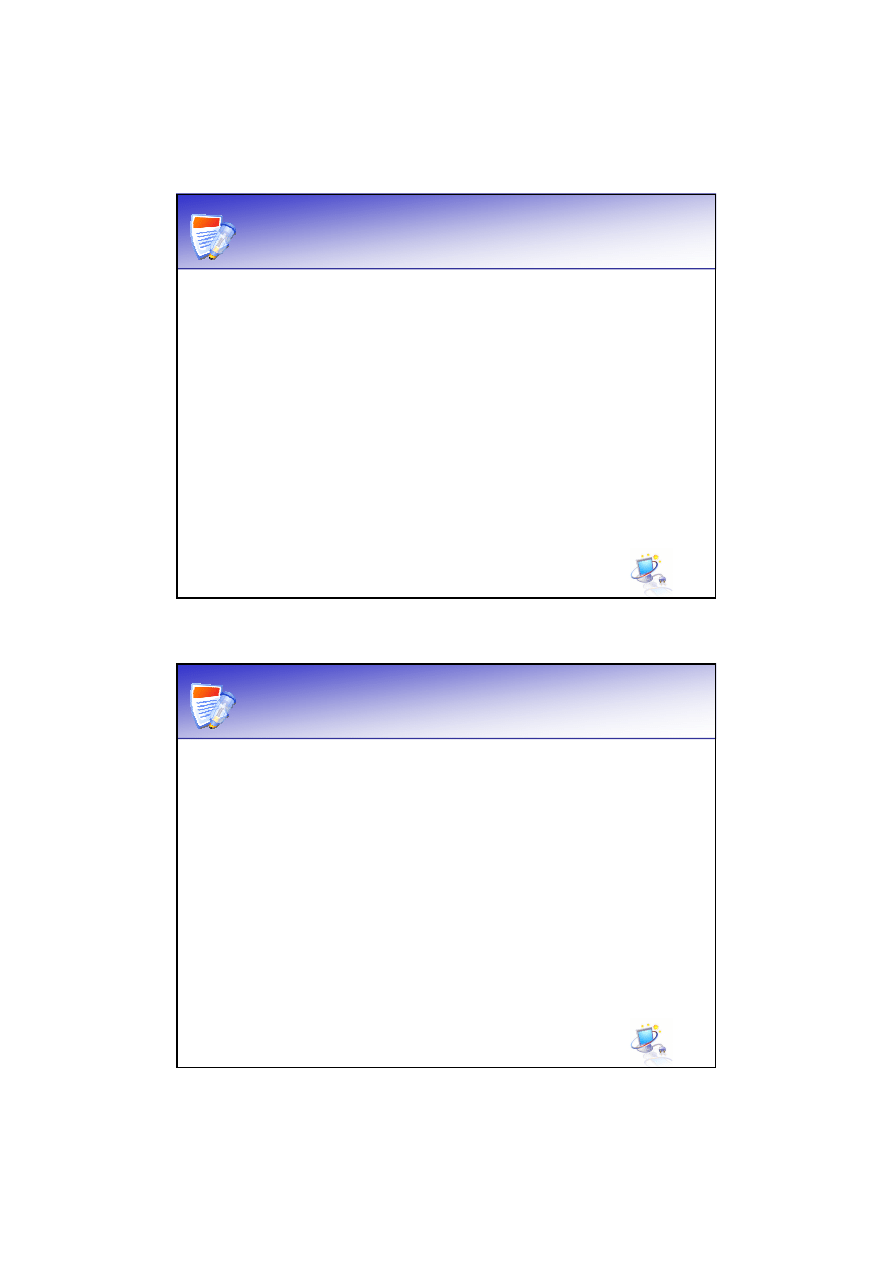

Pobudzanie ścieżki – przykład 2

Należy zapewnić: x

0

= 1 lub x

1

= 1 lub na obu wejściach x

0

=1

i x

1

=

1. Sygnał D na wyjściu bramki NAND wystąpi wówczas, gdy

punkt a=1, czyli x

2

=x

3

=1. Aby D zostało przekazane dalej na

wyjście f, należy spowodować, aby: b=0 i c=0, czyli x

4

= 1 i x

5

=0.

Stąd, wejściowy wektor testowy x

0

,x

1

,x

2

,x

3

,x

4

,x

5

może mieć postać:

011110 lub 101110 lub 111110.

Stwierdzenie błędu

sklejenia s-a-0

16

31

31

31

31

Równoważne błędy w bramce

Błędy

równoważne

,

to

takie

błędy,

które

są

wykrywane przez

te same wektory testowe

. Błędy nie

są równoważne, jeżeli istnieje co najmniej jeden

wektor testowy, który będzie wykrywał jeden z

błędów, lecz nie będzie wykrywał pozostałych.

32

32

32

32

Równoważne błędy - przykład

Przykład:

Testowana jest trójwejściowa bramka AND w celu

wykrycia błędów typu s-a-0 na wejściu.

Odpowiednim wektorem testującym jest 111, niezależnie od

wejścia, które jest sprawdzane na występowanie błędu.

Właśnie pod tym względem wszystkie błędy typu s-a-0 na

wejściach bramki AND są równoważne. Ten sam wektor

testowy 111 umożliwia także wykrycie błędu typu s-a-0 na

wyjściu. Prowadzi to do sytuacji, w której wszystkie

uszkodzenia typu s-a-0 na wejściach lub wyjściach bramki

AND są równoważne i możemy tylko stwierdzić jedno z nich.

Takim wektorem testowym nie można rozróżnić tych czterech

błędów.

17

33

33

33

33

Testowanie układów

sekwencyjnych i złożonych

systemów

34

34

34

34

Potrzeba testowania

Dotychczas rozpatrywane były proste kombinacyjne

układy logiczne. Układy sekwencyjne i złożone systemy

cyfrowe stawiają większe wymagania testowaniu.

Testowanie układów sekwencyjnych składa się zasadniczo

z dwóch etapów:

1. Układ sekwencyjny musi być przełączony do znanego

stanu.

2. Następnie układ z tego stanu musi być przełączony do

innego znanego stanu, po zastosowaniu odpowiednich

sygnałów wejściowych. Wymaga to sterowalności układu.

Obydwa stany: stan bieżący i następny muszą być możliwe

do obserwowania.

18

35

35

35

35

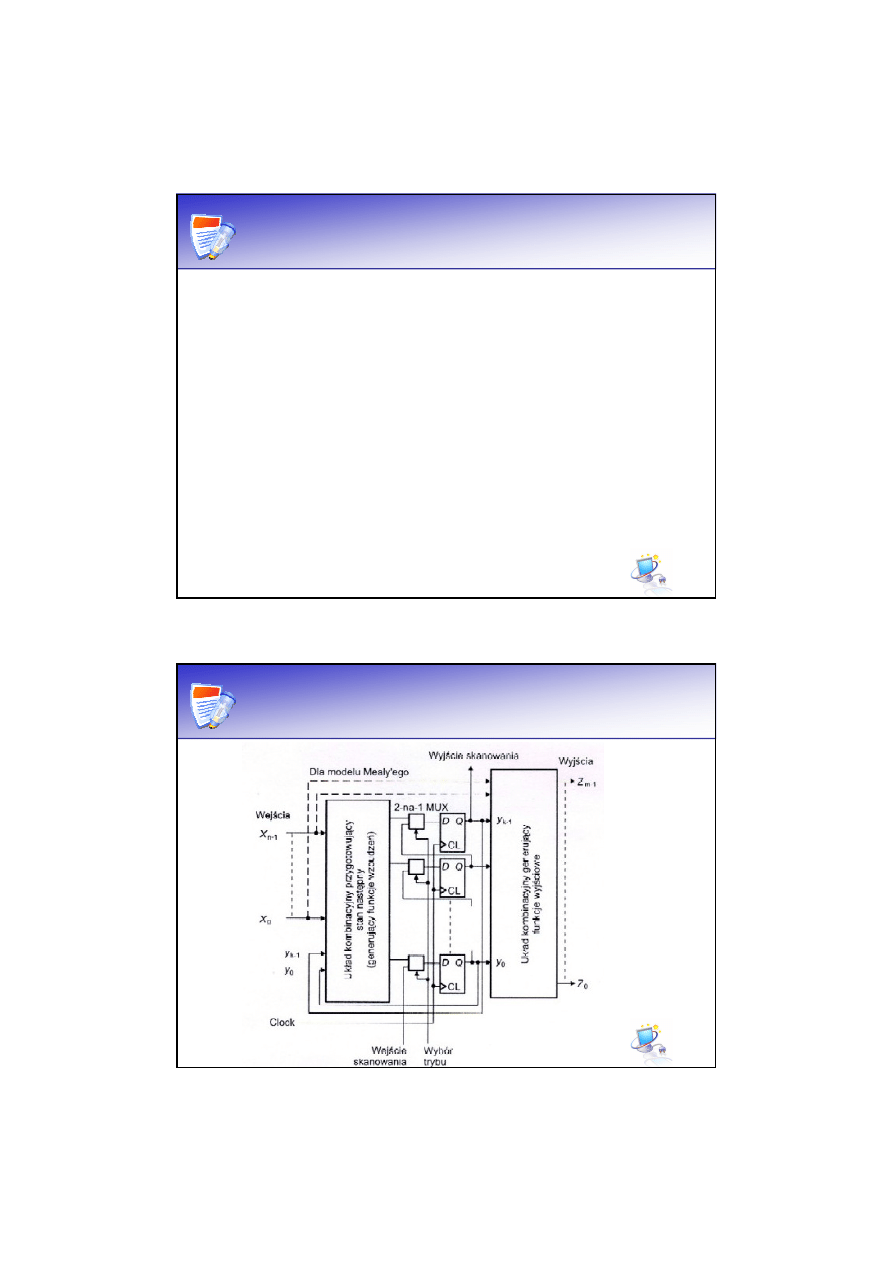

Metoda ścieżki testującej

Stosując

metodę

ś

cieżki

testującej

(skanującej)

dodajemy specjalne elementy do badanego układu, aby

umożliwić ustawianie i przełączanie przerzutników w

sposób szeregowy. Możliwe do wyboru ścieżki tworzy

się między sąsiednimi przerzutnikami tak, aby powstał

szeregowy rejestr przesuwający. Ścieżki szeregowego

wejścia i wyjścia są poprzez multipleksery dołączane do

przerzutników (tworząc z nich rejestr szeregowy) w

celu ich szeregowego zapisywania i odczytywania.

36

36

36

36

Metoda ścieżki testującej cd.

19

37

37

37

37

Wbudowane samotestowanie

W metodzie samotestowania wykorzystuje się dodatkowe

bloki logiczne wbudowane w strukturę układów, aby

skonfigurować układ do trybu testowania, wytworzyć

sekwencje testujące i umożliwić porównanie generowanych

dla nich odpowiedzi z sekwencją sygnałów wyjściowych.

Przykład:

Układ ze ścieżką testującą może być rozwinięty

w układ samotestujący poprzez wbudowanie do niego

generatora

sekwencji

dołączonego

do

wejścia

i

komparatorów

dołączonych

do

wyjścia

skanowania.

Zamiast generatora określonej sekwencji można zastosować

generator sekwencji pseudolosowej.

38

38

38

38

Testowanie krawędziowe

Metoda testowania (skanowania) krawędziowego

jest

rozszerzeniem metody ścieżki testującej na złożone

systemy realizowane w postaci układów cyfrowych.

Każdy układ scalony (chip) wykonuje się z wejściem i

wyjściem układu testowania krawędziowego, gdzie

przerzutniki

przejmują

informację

z

normalnych

wyprowadzeń

wejść

i

wyjść

oraz

tworzą

rejestr

przesuwający.

Wyjście

układu

testowania

krawędziowego jednego układu scalonego może być

dołączane

do

wejścia

testowania

krawędziowego

następnego układu scalonego, aby utworzyć jeden długi

rejestr przesuwający.

20

39

39

39

39

Koniec

Wyszukiwarka

Podobne podstrony:

Metodologia badań z logiką dr Karyłowski wykład 7 Testowalna w sposób etycznie akceptowalny

ECiUL wyklad 7

ECiUL wyklad 1

ECiUL wyklad 6

ECiUL wyklad 3

ECiUL wyklad 4

ECiUL wyklad 5

ECiUL wyklad 9 PLC

IOpr, wykład 6, testowanie

Metodologia badań z logiką dr Karyłowski wykład 7 Testowalna w sposób etycznie akceptowalny

ECiUL wyklad 7

Metodologia z elelmentami statystyki dr Izabela Krejtz wyklad 5 Testowanie hipotez Test T

Wykład 2 testowanie

pytania testowe i chemia budowlana -zestaw3, Szkoła, Pollub, SEMESTR II, chemia, wykład, testy

Pytania testowe z pierwszego wykladu

więcej podobnych podstron