1

Elementy cyfrowe i układy

logiczne

Wykład 6

2

2

2

2

Legenda

Metody programowania układów PLD

Pamięć ROM

Struktura PLA

Struktura PAL

Przykłady realizacji

Technika cyfrowa ….

2

3

4

5

6

7

8

9

18

18

18

18

Programowanie PLD – po co?

• ustanowić

lub

przerwać

połączenia

w

układzie (3 metody)

• utworzyć komórki pamiętające, tzw. LUT

(ang. Look-Up Tables) (praca własna)

• sterować

załączaniem

tranzystora

(technologie:

wymazywalna,

elektrycznie

wymazywalna, błyskowa – ang. flash) (praca

własna)

10

19

19

19

19

Metody programowania PLD

• stosowanie tzw. bezpieczników

(ang. fuse)

Przyłożenie napięcia znacznie większego od napięcia zasilającego

układ, powoduje przepalenie bezpiecznika (przerwanie połączenia).

• programowanie masek

(ang. mask programming)

Wykonywane

przez

producenta

układów

półprzewodnikowych

podczas

ostatniej

fazy

procesu

wytwarzania

struktury

półprzewodnikowej.

Połączenia

są

wykonywane

w

warstwach

metalizacji służących jako przewodniki. Struktura tych warstw jest

uzależniona od żądanej funkcji logicznej. Opłacalne tylko w

przypadku dużych ilości tego samego układu PLD.

20

20

20

20

Metody programowania PLD

• stosowanie tzw. antybezpieczników (ang. antifuse)

Element typu antifuse składa się z dwóch przewodników

położonych blisko siebie, odseparowanych materiałem mającym

wysoką rezystancję. Przed programowaniem antybezpiecznik

zachowuje się jak przerwa (ROZWARCIE)

w

obwodzie.

Przyłożenie (do obu przewodników) napięcia nieco wyższego od

napięcia zasilania powoduje, że materiał odseparowujący jest

topiony (jego rezystancja staje się bardzo mała), wobec czego

przewodzi i powstaje połączenie (ZAMKNIĘTA ścieżka).

11

21

21

21

21

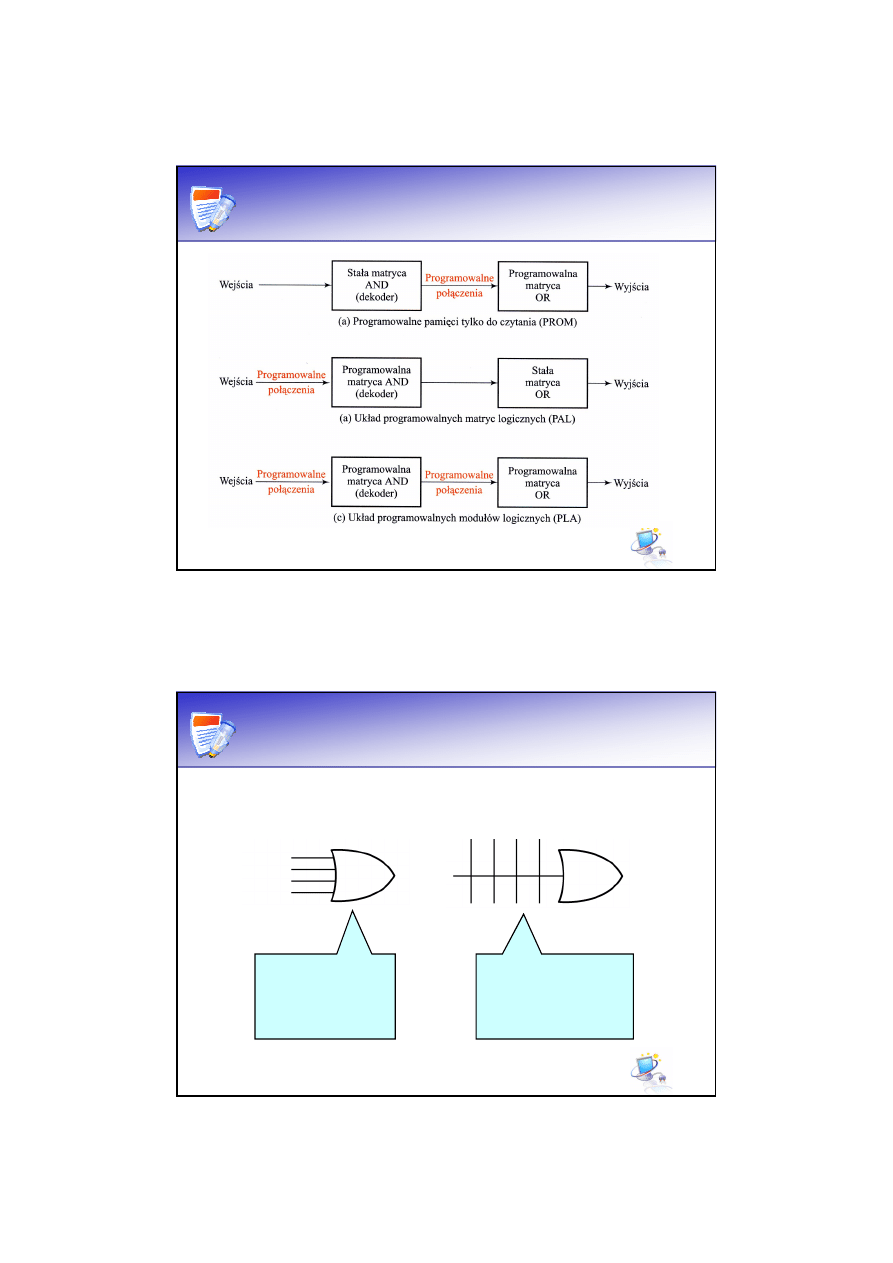

Układy PLD

Ź

ródło: „Podstawy projektowania układów logicznych i komputerów”

22

22

22

22

Symbole

konwencjonalny

w schematach

matryc logicznych

12

23

23

23

23

Pamięć ROM

Pamięć ROM

– programowalna podczas procesu produkcyjnego,

programowanie masek;

Pamięć PROM (programowalna pamięć ROM)

– programowalna

jednorazowo u użytkownika, zastosowanie bezpieczników;

Pamięć EPROM (wymazywalno-programowalna pamięć ROM)

– wymazywanie polega na naświetlaniu układu silną wiązką

promieniowania ultrafioletowego;

Pamięć EEPROM (E

2

PROM – elektrycznie wymazywalna,

programowalna pamięć ROM)

Pamięć Flash

– zmodyfikowany EEPROM.

24

24

24

24

Pamięć ROM

Pamięć ROM (a także jej odmiany) jest strukturą o 2

m

komórkach

adresowanych wektorem złożonym z k zmiennych u

1

,…, u

k

i

zawierającą słowa o długości n.

Pamięć ROM

o organizacji

2

k

x n

k

wejść

(adres)

n

wyjść

(dane)

13

25

25

25

25

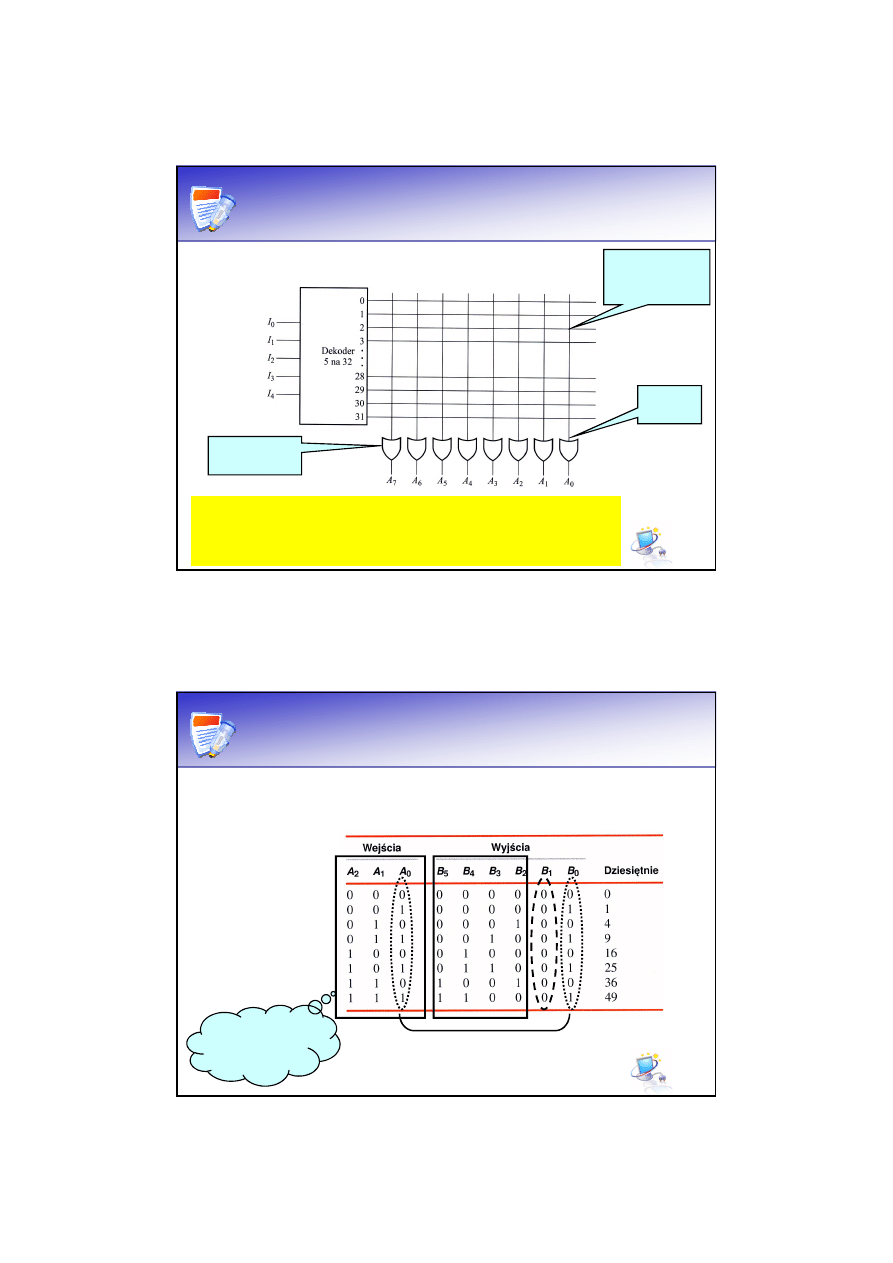

Pamięć ROM (32 x 8)

połączenia

programowalne

(bezpiecznik)

32

wejścia

Przykład:

Pamięć ROM zawiera 32 x 8 = 256

programowalnych połączeń

Pamięć ROM o organizacji 2

k

x n będzie zawierała

dekoder k na 2

k

linii oraz n bramek OR. Każda bramka

OR ma 2

k

wejść.

8 bramek OR

26

26

26

26

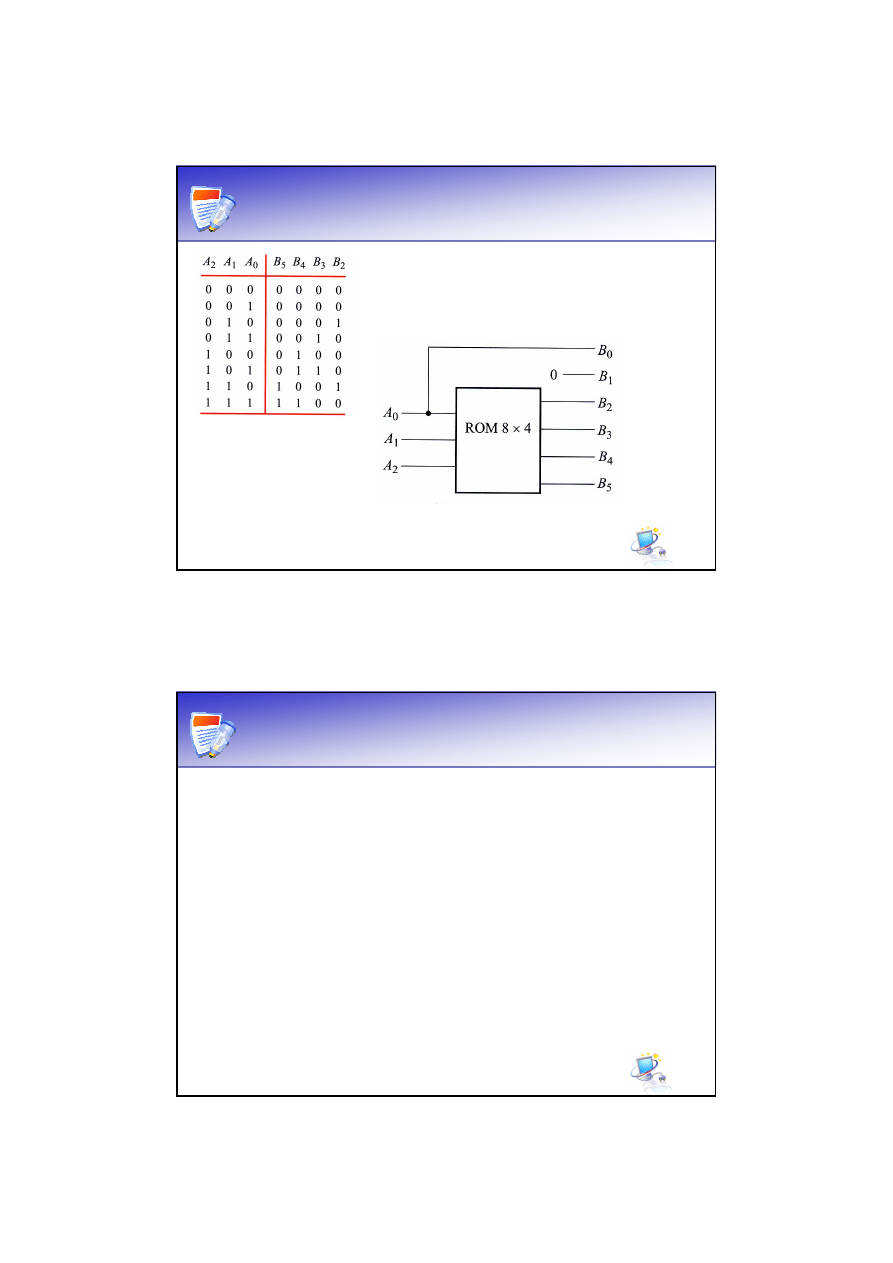

Przykład

Przykład:

Zaprojektuj układ: wejście – liczba 3-bitowa, wyjście – liczba

binarna równa kwadratowi liczby wejściowej.

ROM o 3

wejściach i

4 wyjściach

14

27

27

27

27

Pamięć ROM - przykład

28

28

28

28

Struktura PLA

Struktura

PLA

(

P

rogrammable

L

ogic

A

rray

) składa się z

programowalnej matrycy AND

oraz

programowalnej matrycy

OR.

Układy PLA nie zapewniają pełnego dekodowania zmiennych i

nie generują wszystkich mintermów. Dekoder (z pamięci ROM)

jest zastąpiony

programowalną matrycą bramek AND

, która

pozwala na generowanie iloczynów zmiennych wejściowych.

Iloczyny są wybiórczo łączone w

matrycy OR

, tworząc sumy

iloczynów.

15

29

29

29

29

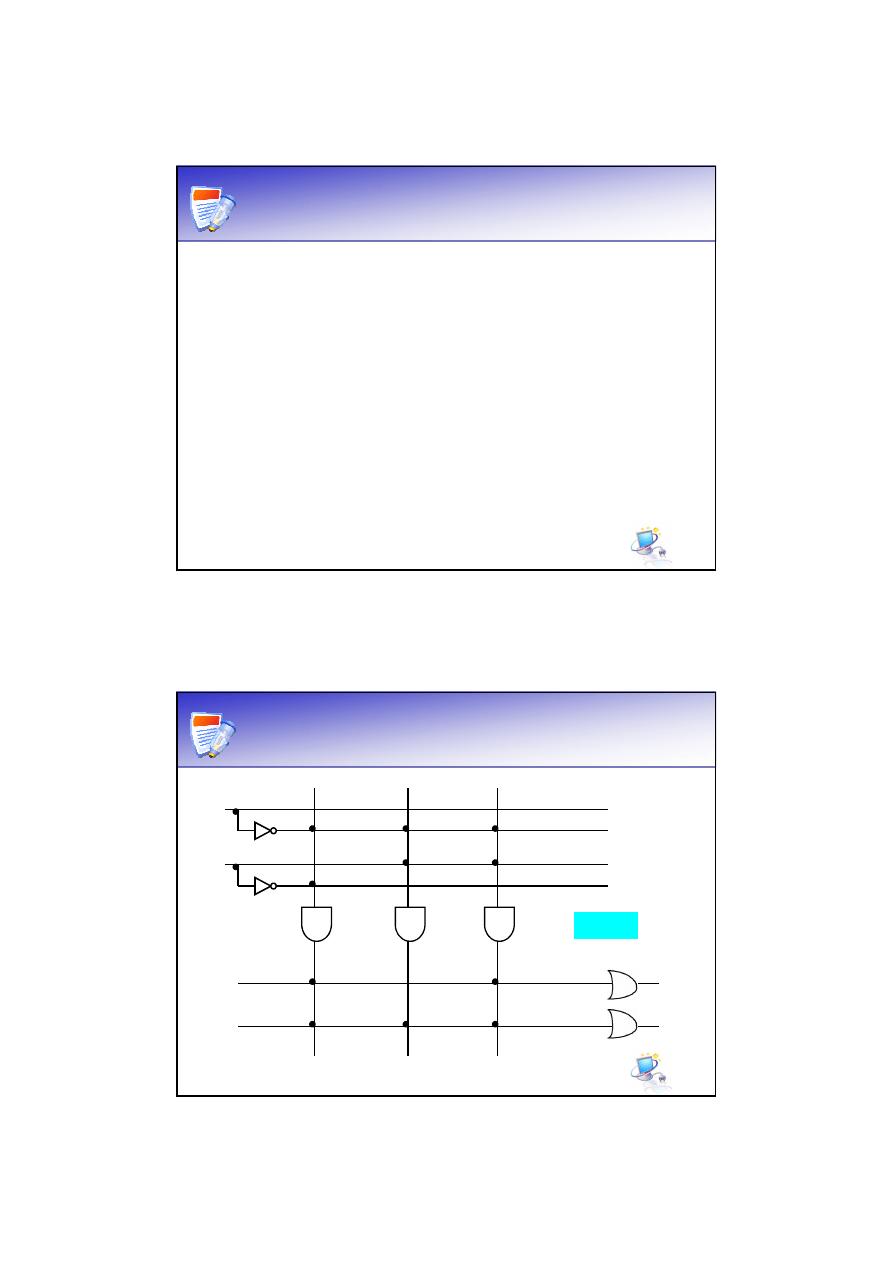

Struktura PLA

Programowalna matryca AND

umożliwia tworzenie do k

iloczynów pełnych lub niepełnych, tj. mających do m zmiennych

wejściowych u

1

,…, u

m

, prostych lub zanegowanych, przy czym k

jest zwykle znacznie mniejsze niż 2

m

. Tak więc możliwe jest

utworzenie nie wszystkich lecz tylko niektórych iloczynów.

Programowalna matryca OR

umożliwia tworzenie do r sum

złożonych z dowolnych iloczynów utworzonych z matrycy AND.

30

30

30

30

Ogólny schemat struktury PLA

. . .

. . .

u

1

u

m

.

.

y

1

y

r

Programowalna

matryca AND

Programowalna

matryca OR

k<<2

m

0

1

k-1

16

31

31

31

31

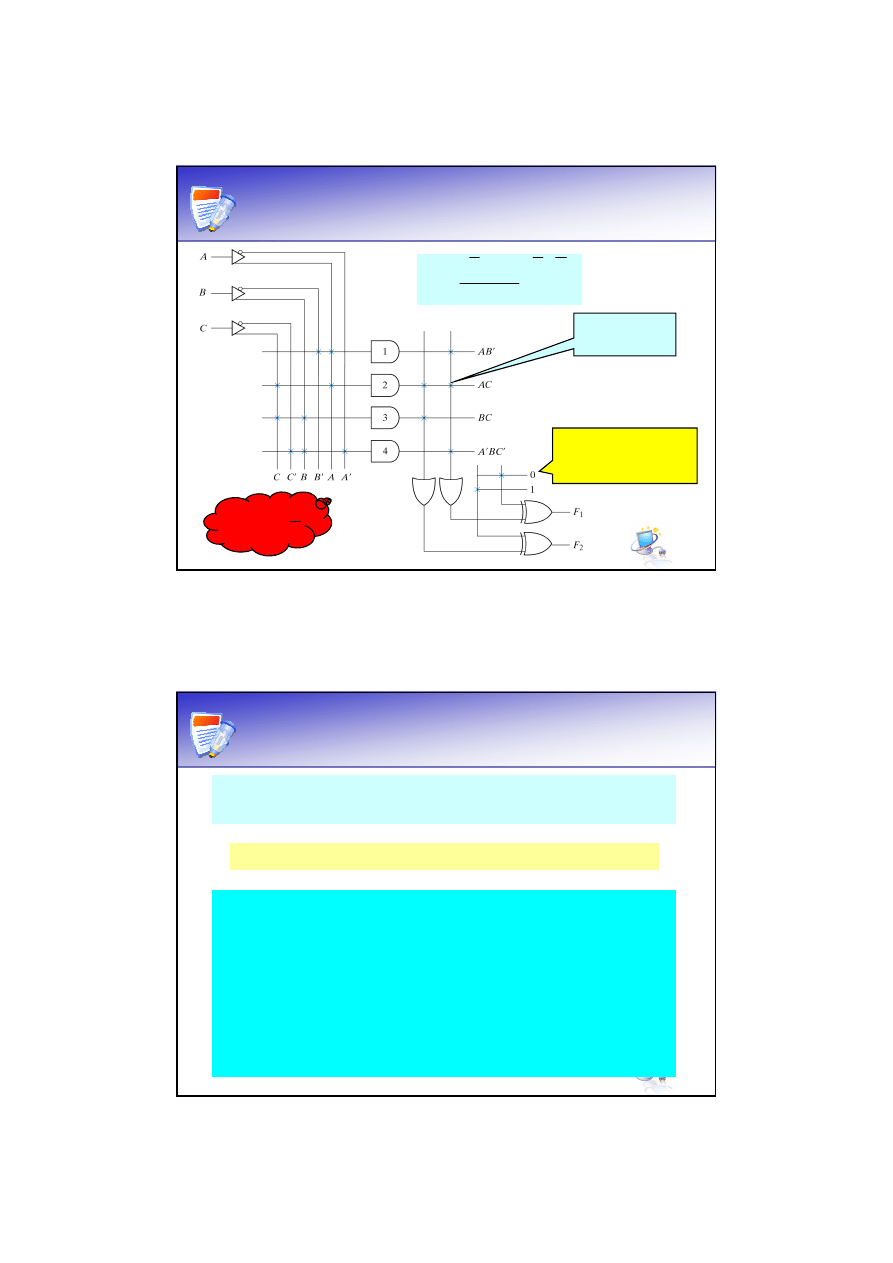

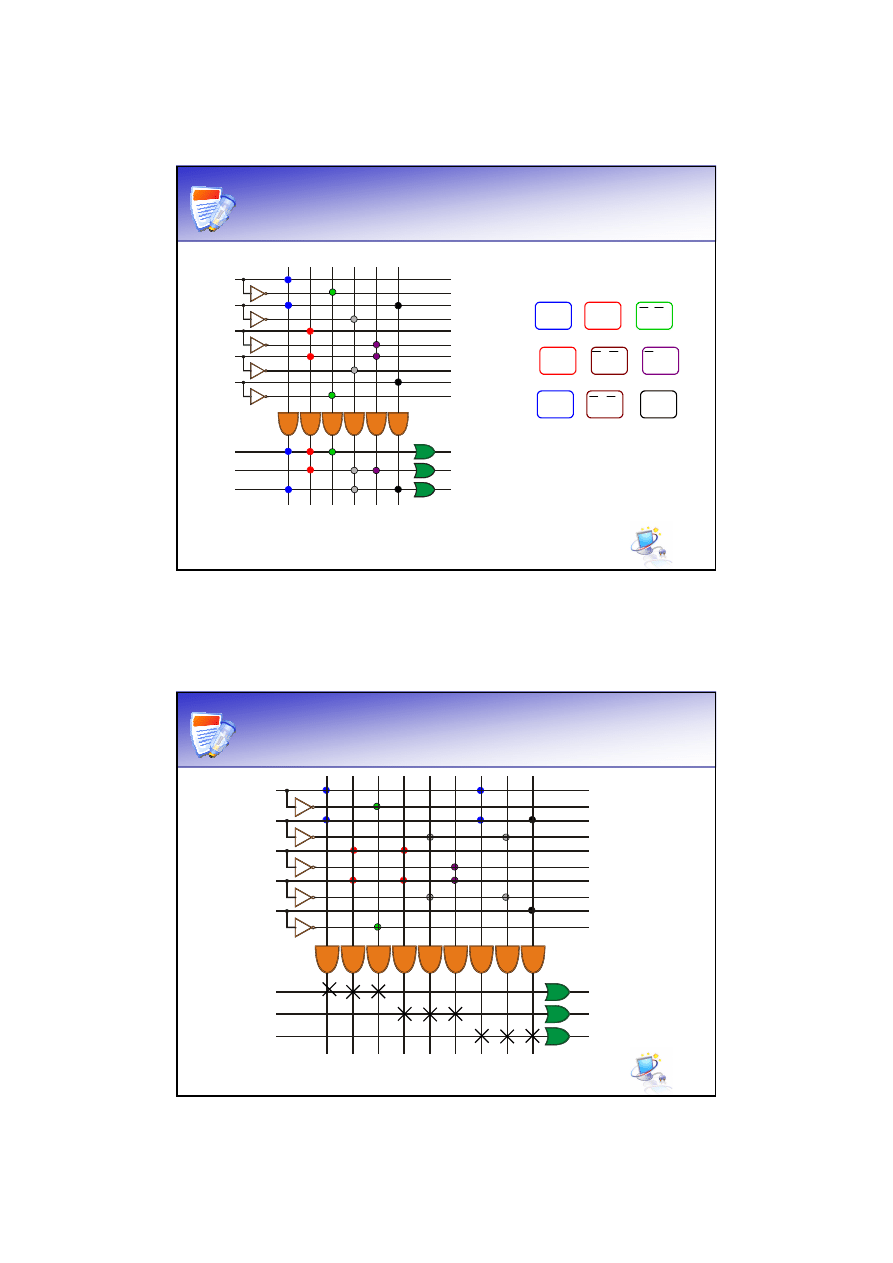

PLA - przykład

C

B

A

AC

B

A

F

+

+

=

1

BC

AC

F

+

=

2

Bezpiecznik

przewodzący

0 lub 1 aby uzyskać

wyjście proste lub

zanegowane

X

X

=

⊕ 0

X

X

=

⊕1

32

32

32

32

Struktura PLA

Rozmiar układu PLA jest określony liczbą wejść, liczbą

iloczynów oraz liczbą wyjść.

Typowy układ PLA: 16 wejść, 48 iloczynów, 8 wyjść.

W przypadku n wejść, k iloczynów oraz m wyjść wewnętrzna

struktura układu PLA składa się z n bramek typu bufor-

inwerter, k bramek typu AND, m bramek typu OR i m bramek

typu EXOR. Jest 2n x k programowalnych połączeń między

wejściami a matrycą bramek AND, k x m programowalnych

połączeń

między

matrycami

AND

i

OR

oraz

m

programowalnych połączeń dla bramek EXOR.

17

33

33

33

33

Struktura PAL

Struktura

PAL

(

P

rogrammable

A

rray

L

ogic

) złożona jest z

programowalnej matrycy AND

i

stałej matrycy OR

złożonej z

bramek OR o różnej liczbie wejść (wejścia bramek OR są

dołączone na stałe do konkretnych linii iloczynu).

Stanowi to oczywiście udogodnienie technologiczne, lecz jest

pewnym ograniczeniem możliwości struktury i prowadzi do zmian

w projektowaniu. Iloczyn wchodzący do kilku sum nie może być

teraz używany wielokrotnie, a musi być tworzony tyle razy, do ilu

bramek OR jest doprowadzany.

34

34

34

34

Struktura PGA

Kolejną z odmian jest struktura

PGA

(

P

rogrammable

G

ate

A

rray

)

złożona z bramek AND. Jest to struktura programowalna

analogiczna do wykonywanej na zamówienie struktury gate array.

Struktury PAL, PLA i PGA są realizowane także ze sprzężeniem

zwrotnym z niektórych wyjść (matrycy OR w PAL i PLA, matrycy

AND w PGA) na wejście.

Matryca

AND

Matryca

OR

We.

We/Wy

Wyj.

18

35

35

35

35

Realizacja PLA

5

2

4

2

2

1

3

4

3

4

2

4

3

2

5

1

4

3

2

1

1

x

x

x

x

x

x

y

x

x

x

x

x

x

y

x

x

x

x

x

x

y

+

+

=

+

+

=

+

+

=

y

x

y

x

y

x

x

x

1

1

2

2

3

3

4

5

36

36

36

36

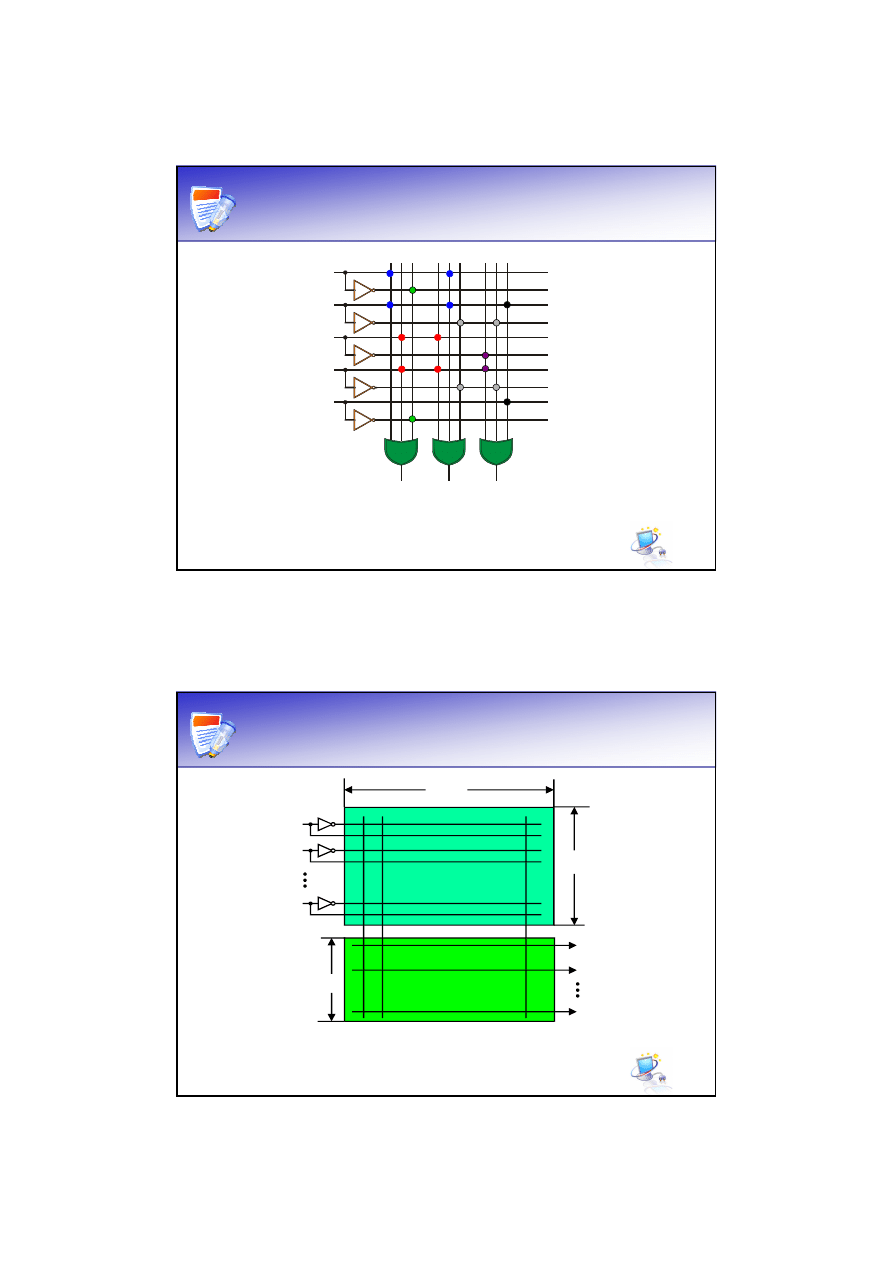

Realizacja PAL

y

x

y

x

y

x

x

x

1

1

2

2

3

3

4

5

19

37

37

37

37

Realizacja PAL

y

x

y

x

y

x

x

x

1

1

2

2

3

3

4

5

38

38

38

38

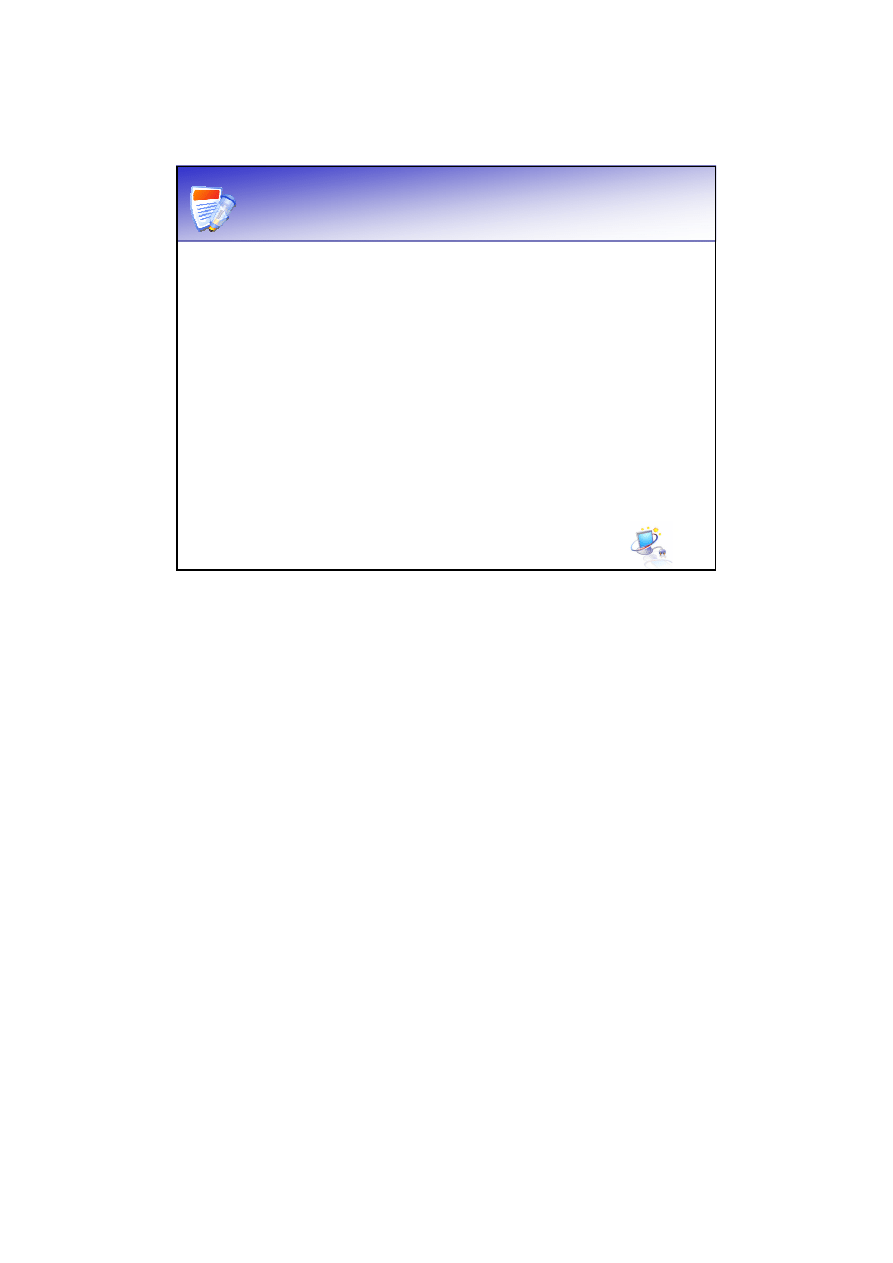

Matryce PLA - powierzchnia

krzemu

x

x

x

1

2

n

f

f

f

0

1

-1

m

AND

OR

P

2n

m

S = (2n + m) * P

20

39

39

39

39

Koniec

Dziękuję za uwagę

Wyszukiwarka

Podobne podstrony:

ECiUL wyklad 7

ECiUL wyklad 1

ECiUL wyklad 3

ECiUL wyklad 8 testowanie

ECiUL wyklad 4

ECiUL wyklad 5

ECiUL wyklad 9 PLC

ECiUL wyklad 7

Napęd Elektryczny wykład

wykład5

Psychologia wykład 1 Stres i radzenie sobie z nim zjazd B

Wykład 04

geriatria p pokarmowy wyklad materialy

ostre stany w alergologii wyklad 2003

WYKŁAD VII

Wykład 1, WPŁYW ŻYWIENIA NA ZDROWIE W RÓŻNYCH ETAPACH ŻYCIA CZŁOWIEKA

Zaburzenia nerwicowe wyklad

więcej podobnych podstron