1. Czy podane niżej funkcje logiczne można zrealizować w jednym bloku CLB układu XC4000?

• dowolna funkcja 5 zm

TAK

• dowolna funkcja 4 zm + określona funkcja 5 zm TAK

• 2 x dowolna funkcja 4 zm + dowolna funkcja 3 zm TAK

• 4 x dowolna funkcja 2 zm

NIE

• określona funkcja 10 zm

NIE

• 3 x dowolna funkcja 4zm

NIE

• określona funkcja 9 zm

TAK

Proszę wpisać TAK lub NIE

2. Uzupełnij tabelkę:

Device

System gates CLB Array (R

Total

Total distr. Total block

x C)

CLBs

RAM [bits]

RAM

[Kbits]

XC2Sxx

xxK

Proporcje 2:3

R x C CLBs*64b

R/4*Kbits

XC2S15

15K

8 x 12

96 6

144 16

XC2S30

30K

12 x18

216 13

824 24

XC2S50

50K

16 x 24

384

24 575

32

XC2S100

100K

20 x 30

600

38 400

40

XC2S150

150K

24 x 36 864 55 296

48

XC2S200

200K

28 x 42

1176 75

264 56

3. Uzupełnij poniższą tabelkę dla układ u serii SpartanII: Symbol Name

Number of

Primitive or

LUTs

Macro

(wpisać P/M)

ROM16X1

½ P

ROM32X1

1 P

RAM16X1D

1 P

RAM32X1S

1 P

RAM16X4D

4 M

RAM16X4S

2 M

RAM32X4S

4 M

RAM32X8S

8 M

4. Problemy czasowe „krótkich ścieżek” w układach, w których występuje duży skos zegara, można eliminować:

• taktując naprzemiennie przerzutniki w łańcuchu rejestru przesuwnego przeciwnymi zboczami zegara

TAK

• spowalniając szybkość narastania i opadania zboczy sygnału zegarowego

NIE

• stosując przerzutniki o zerowym czasie utrzymania tHOLD

NIE

• wydłużając czas propagacji połączeń na ścieżce zegara NIE

• stosując przerzutniki o małym czasie propagacji ClkÆQ

NIE

• wydłużając czas propagacji połączeń na ścieżce danych TAK

• stosując przerzutniki o jak najkrótszym czasie ustawiania tSET-UP

TAK?

• odwracając kierunek propagacji sygnału zegarowego w rejestrze przesuwnym przeciwnie do kierunku przesuwu TAK

• zmniejszając częstotliwość sygnału zegarowego NIE

• ustalając współczynnik wypełnienia sygnału zegarowego na dokładnie 50%

NIE

Proszę wpisać TAK lub NIE

5. Czy podane niżej funkcje logiczne można zrealizować w jednym plastrze bloku CLB

układu SpartanII?

• multiplekser 8:1

TAK

• 2 x dowolna funkcja 4 zm + dowolna funkcja 3 zm NIE

• dowolna funkcja 6 zm

NIE

• określona funkcja 9 zm

TAK

• dowolna funkcja 4 zm + określona funkcja 5 zm TAK?

Proszę wpisać TAK lub NIE

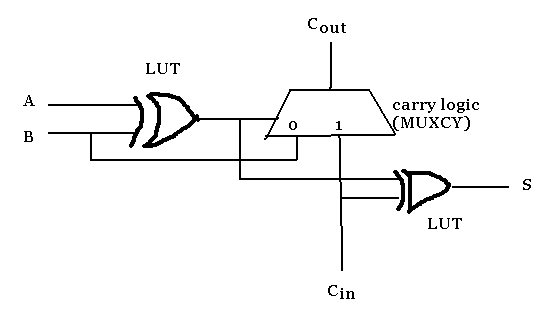

6. narysuj schemat jednobitowego sumatora pełnego ta... realizowany w bloku CLB

układów SpartanII ... dedykowanych zasobów carry logic. Zaznacz elementy carry logic (podaj ich nazwy), oraz zaznacz fragment realizowany w LUT

7. Parametry czasowe przerzutnika wejściowego D w bloku IOB wynoszą: tSET-UP=1.7ns, tHOLD=0.4ns, czas propagacji sygnału zegarowego PinC --> WeClk tPC=3.4ns, czas propagacji sygnału danych PinD --> WeD tPD=1.5ns. Uzupełnij poniższe punkty.

(zadanie proste, tylko nie wiem jak mam rozumieć pojęcie „optymalne warunki”) (a) Opóźnienie jakie powinno być dodane na ścieżce ..danych..., tak aby uzyskać optymalne warunki wpisu sygnału z PinD do przerzutnika, wynosi: tDELAY=

(b) Po dodaniu opóźnienia wymagane parametry PinD względem PinC będą wynosić tSET-UP =.............. tHOLD =..............

8. Czy podane niżej funkcje logiczne można zrealizować w jednym bloku CLB układu XC4000E? (z tego co wyczytałem to XC4000 i XC4000E mają niemal identyczne możliwości jeśli chodzi o CLB)

• dowolna funkcja 4 zm + określona funkcja 6 zm TAK

• 2 x dowolna funkcja 4 zm + dowolna funkcja 3 zm TAK

• dowolna funkcja 5 zm

TAK

• dowolna funkcja 6 zm

NIE

• określona funkcja 9 zm

TAK

Proszę wpisać TAK lub NIE

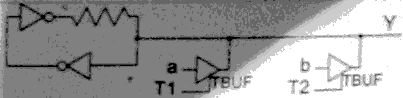

14 Uzupełnij przebieg czasowy Y (układ rodziny XC4000): a

T1

b

T2

Y

Y = a ⋅ T 1 + b ⋅ T 2

Wyszukiwarka

Podobne podstrony:

Prezentacja kwalifikacja testy

Wyklad 6 Testy zgodnosci dopasowania PL

Testy immunologiczne

Metodologia SPSS Zastosowanie komputerów Brzezicka Rotkiewicz Testy zależne

06 Testy korelacjiid 6413 ppt

wyklad 6 Testy zgodnosci dopasowania PL

W 4 biomonitoring testy rodzaje

Depresja etiol klinika studenci

BM 4 3 Testy projekcyjne

testy nieparametryczne

Niewydolność serca i nadciśnienie tętnicze klinika i pielęgnowanie

Testy Krak w

2008 04 testy odpowiedzi

więcej podobnych podstron