Marcin Kierdelewicz 3P24

Zespół 3

Projekt do ćwiczenia lab. ELiU

Bramki Cyfrowe

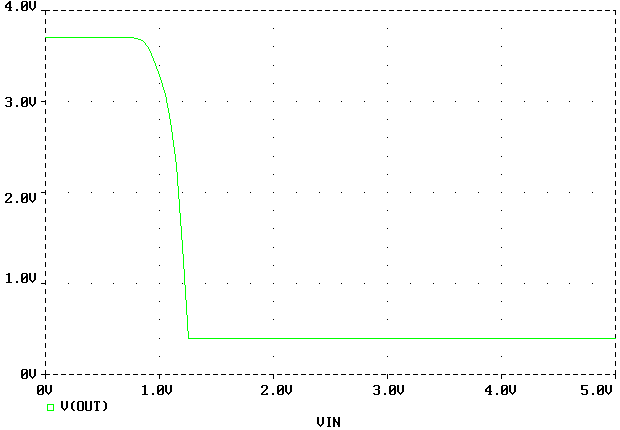

Układ inwertera 74LS04 (TTL).

Rys. 1 - Charakterystyka przejściowa układu 74LS04.

Rys. 2 - Charakterystyczne punkty.

Korzystając z charakterystyki przejściowej układu odczytuję wartości poziomów UH, UL oraz wartość napięcia progu przełączania: U punktu T. Wartości UIL max, UOL max, UOH min, UIH min to odpowiednie wartości napięć wejściowych („I”) i wyjściowych („O”) stanów niskiego („L”) i wysokiego („H”) odczytanych z charakterystyki w punktach w których wzmocnienie wynosi -1 V/V. Wartości te zamieszczam w tabeli 1.

Tabela 1.

UH |

UL |

UH - UL |

U punktu T |

NML |

NMH |

UIL max |

UOL max |

UOH min |

UIH min |

3,70V |

0,40V |

3,3V |

1,21V |

0,46V |

2,4V |

0.86V |

0,4V |

3,67V |

1,25V |

UH - logiczna „1” UL - logiczne „0” Upunkt T - napięcie progowe przełączania.

Marginesy szumowe (połączenie szeregowe) zostały obliczone według następujących wzorów:

Układ inwertera 74HCU04 (CMOS).

Rys. 3 - Charakterystyka przejściowa układu 74HCU04.

Wartości napięć odczytane z wykresu umieszczone są w tabeli 2.

Tabela 2

UH |

UL |

UH - UL |

U punktu T |

NML |

NMH |

UIL max |

UOL max |

UOH min |

UIH min |

5,0V |

0,0V |

5,0V |

2,5V |

1.6V |

1,6V |

2,04V |

0,44V |

4.6V |

2.95V |

Wartości marginesów szumowych NML i NMH obliczone zostały następująco:

3. Przebiegi wejściowe i wyjściowe bramki NAND.

Rys. 4 - Przebiegi wejściowe i wyjściowy bramki dla MNTYMXDLY = 1.

Wartości czasów opóźnień dla MNTYMXDLY = 1 :

- przy przejściu z „L” na „H”: tdLH = 52,8ns - 47,8ns ≅ 5ns

- przy przejściu z „H” na „L”: tdHL = 115ns - 112,4ns ≅2,6ns

Rys. 5 - Przebiegi wejściowe i wyjściowy bramki dla MNTYMXDLY = 2.

Wartości czasów opóźnień dla MNTYMXDLY = 2 :

- przy przejściu z „L” na „H”: tdLH = 59,3ns - 47,8ns ≅11,5ns

- przy przejściu z „H” na „L”: tdHL = 119ns - 112,4ns ≅6,6ns

Rys. 6 - Przebiegi wejściowe i wyjściowy bramki dla MNTYMXDLY = 3.

Wartości czasów opóźnień dla MNTYMXDLY = 3 :

- przy przejściu z „L” na „H”: tdLH = 70,5ns - 47,8ns ≅ 22,7ns

- przy przejściu z „H” na „L”: tdHL = 127,2ns - 112,6ns = 14,6ns

Wartości parametru MNTYMXDLY wyznaczają opóźnienia propagacji sygnału bramki.

1 - opóźnienie minimalne,

2 - opóźnienie typowe,

3 - opóźnienie maksymalne

Otrzymane wyniki czasów opóźnienia bramki NAND TTL przy trzech różnych wartościach parametru MNTYMXDLY odpowiadają czasom dla standardowej bramki NAND TTL.

4. Pomiar uśrednionego czasu propagacji.

Uśredniony czas propagacji pojedynczego inwertera można znaleźć mierząc okres generatora zbudowanego z inwerterów połączonych w szereg. Jeśli przez Tg oznaczymy okres generatora, przez k liczbę inwerterów w tym generatorze to wtedy:

tpd=

Dla pojedynczego inwertera tpd=0.5(tdHL+tdLH) = 0,5(11,5+6,6)=9,05ns (dla wartości parametru MNTYMXDLY=2), okres generatora powinien wynosić wtedy:

Tg=2tpdk= 2 * 9,05ns* 5= 90,5ns (dla 5 inwerterów).

Symulacja pliku gen_cyf.cir pomoże sprawdzić jak teoria ma się do rzeczywistosści. Jak widać na poniższym rysunku okres generatora zgadza się z obliczoną wartością Tg.( Uk --> [Author:R.D.T] ład symulowany dla MNTYMXDLY=2 )

Z dość dobrą dokładnością widzimy zgodność z obliczeniami - Tg ok. 88 ns.

7

Wyszukiwarka

Podobne podstrony:

Dane Projekt nr 1 MK

Arkusz nr 1 (liczby zespolone)

Arkusz nr 1 (liczby zespolone)

Zarządzenie pracodawcy nr... o powołaniu zespołu powypadkowego

Dane Projekt nr 1 MK

Zarządzenie pracodawcy nr o powołaniu zespołu powypadkowego

Schemat nr 30 Zespół MOP ów

Sprawozdanie z Pracowni nr. 1 , Zespół Szkół Nr 1 w Sierpcu

przerzutniki monostabilne, Zespół Szkół Elektrycznych nr 1 w Poznaniu

o-5~1, Zespół nr 3

Instrukcja do ćwiczenia(12), ZESPÓŁ SZKÓŁ Nr 9 im

Układy synchroniczne i asynchroniczne( przerzutnik typu D i zatrzask RS), Zespół Szkół Elektrycznych

m10b, Nr Zespołu

cw4agc , Nr zespołu

Teoria(21), ZESPÓŁ SZKÓŁ Nr 9 im

więcej podobnych podstron