egzamin2 3

«>

b)

c)

d)

14

n)

b)

PlWM

f* ' • tUtllłk M

I* wttuUul RN / ilnhiktrwanYin Jricktoian /hnt/ji tttna im/wi |im/utntlui IK uwm iM/ua pi /«*r/utmkii l)

Miltitnulni »i\l>U<»%« llnnlki •%vn«lirnnli /nry.»;

/4>k*/v ud c/jtau propogn* p pr/cr/utmkn

/vtlr/> od czasu puipngm ji pi/rr/ulmkii ortu liczby

prorzutittków w lic/luku

/uleży od liczliy przcrzutników

zależy od konstrukcji sprzężeń w lic/niku

Rejestr lic/ący, który zbudowany Jest z N przerzufnikow

w zależności od konstrukcji może zliczać:

N N+I.2N impulsów

<6 Mttirr Słnt i<>

k » kkkiyin /|ik»titiww»i . ja/e/tm/ynlirtt"

21

*)

b)

«)

d)

2", 2

impulsów

10", I0"'1. IG**1 impulsów

b)

c)

d)

16.

«)

b)

d)

2" impulsów

< /.a* dostępu do pamięci to:

czas od momentu podania zasilania do imnncntu gotowości

pamięci

maksymalny czas trwnnia danych na wyjściu jwinięci czas od momentu |xxlania adresu komórki do momentu uzyskaniu żądanych danych czas podtrzymania danych przez pamięć DRAM Układ z ry sunku realizuj funkcję:

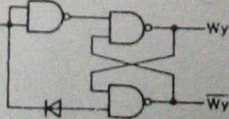

Y=A+B A+B

Y = A + B_A + B

Y = AB + AB

Y = AB + AB

o

1'r/nliltni.Kit • h■ mlil»ry»łyIta la

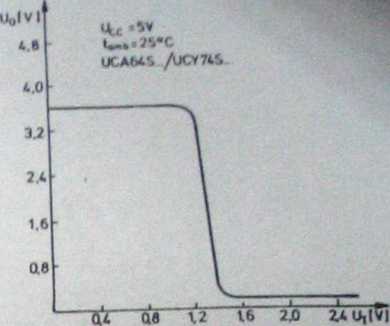

. Ii.m -ii In vu vl i uwj-U Kiwa bramki

»lun>ik(tryptyku wyjścMSMl bricmki w 4-irnr • huruklerystyka [H /<•!»* /ania tiramki [charikirryityka odporności na zakłócenia

Odświeżanie to proces:

.jiaprawiunic" przekłamanych bitów w pamięci RAM

uzupełnienia ludunku w kondensatorze pumięci dynamiezjiej

kasowanie pamięci EPROM jiromicmumi UV

icgulanic cxlcz.ytywunie tych samych danych z. pamięci w celu

sprawdzenia, czy nic uległy przeklamaiuu

Układ realizuje funkcję:

przcrzutiuka D

prz.erzuUuka T

prz.er/utiuka Schmitlu

taktowanego przerzutjuka RS

w*

b)

Bramka CMOS NAND /.awieni:

dwa tranzystory z kanałami MOS typu „n” i dwa tranzystory MOS typu „p"

dwa tranzystory npn i dwa tranzystory pup

cztery tranzystory bipolarne npn

jeden tranzystor komplementarny CMOS

Układy sprzęgające w systemach cyfrowych to:

układy wejściowe i wyjściowe

układy przeliczające kod dziesiętny na binarny

układy sumowania wprowadzanych liczb

układy zliczające impulsy wejściowe

Sekwencyjne sterowanie wyświetlaczem LED umożliwia:

uproszczenie układu przy dużej liczbie cyfr oraz ograniczenie

liczby przewodów do wyświetlacza

wyświetlenie wielu wartości liczbowych na jednym

wyświetlaczu

zmniejszenie zmęczenia wzroku osoby odczytującej znaczne zwiększenie trwałości wyświetlaczy LED Schemat przedstawia: j

zamianę przerzutmka JK w D zmianę I w RS

licznik niodulo 2 zamianę D w T

19.

u)

b)

c)

d)

b)

c)

d)

Sumator ukumulujący:

icst układem, który zamiast jednego ze składników wprowadza do sumatora wynik poprzedniego dodawania przechowuje wynik dodawania do dalszych obliczeń zawiera 3 rejestry oraz 1 swnator jednobitowy charakteryzuje się bezpośiednim połączeniem wyjść sumy ,.S" z wejściem ,A"

Generator parzystości:

generuje bit informujący, że liczba jest purzystu

generuje hit informujący o parzystej liczbie jedynek

/ liczby dodatniej tworzy ujemną

generuje bit, gdy liczba zer jest parzysta

Licznik rewonyjny:

zlicza wprzód i wstecz i może Iryć asynchroniczny lub

synchroniczny

zlicza wprzód i wstecz i może być wyłącznie synchroniczny inna nazwa licznika synchronicznego urna nazwa licznika liczącego wstecz.

S Q

Najprostszy generator przebiegu prostokątnego można zbudować z min.:

•I bramek NAND

1 bramki o charakterystyce Selim i (ta

2 bnunek i rezonatora kwarcowego I specjalnego układu scalonego np. 555 Przetworniki cyfrowo-analogowe stosują jako elementy

przetwarzające min: genenitory sterowane napięciem liczniki synchroniczne regulowane źródłu napięcia

drabinkę rezystorów R-2R Dekoder 7-scgmcntowy jest w istocie.

eiikodcnrin I z 7 dekoderem I / 7 en kodein n BCD uj transkoderem 30. Rejestr SIPO ni*::

a) wejście szeregowe i wyjście rów no s «

h) wejicic

C) wejście równolegle i wyj / i równolegle

d) wejście szeregowe i wyj-c

27.

a)

b)

c)

d) 28.

Wyszukiwarka

Podobne podstrony:

Piel psychiatryczne egzamin 14 (1) pifCKt U -T> ~ ł6o^ VT . V- ->j — $.-■> ./ — &nbs

egzamin 14 cz2 □ li (10 pki) Dla danego układu wyznaczyć macierz mas oraz macierz podatności oraz za

Piel psychiatryczne egzamin 14 (3) S.-ni ^vk< o. v.-,,yi.y <<«;/.av-.iw -roiy\Vv ><#

egzamin 14 ■’iy B w* „ .................l.-Ar.M ................ «.*»»* n. .......

2010 01 12 1451 AiłUMłkł ATcfit# ,Y(Unii.^iU auv A*n*a ttiajx»i . Mł ISBN mm* 14.HB-4. C ty WN r»N 2

2010 01 12 1501 AiłUMłkł ATcfit# ,Y(Unii.^iU auv A*n*a ttiajx»i . Mł ISBN mm* 14.HB-4. C ty WN r»N 2

2010 01 12 1632 AiłUMłkł ATcfit# ,Y(Unii.^iU auv A*n*a ttiajx»i . Mł ISBN mm* 14.HB-4. C ty WN r»N 2

2010 01 12 1640 AiłUMłkł ATcfit# ,Y(Unii.^iU auv A*n*a ttiajx»i . Mł ISBN mm* 14.HB-4. C ty WN r»N 2

2010 01 12 1652 AiłUMłkł ATcfit# ,Y(Unii.^iU auv A*n*a ttiajx»i . Mł ISBN mm* 14.HB-4. C ty WN r»N 2

2010 01 12 1706 AiłUMłkł ATcfit# ,Y(Unii.^iU auv A*n*a ttiajx»i . Mł ISBN mm* 14.HB-4. C ty WN r»N 2

2010 01 12 1818 AiłUMłkł ATcfit# ,Y(Unii.^iU auv A*n*a ttiajx»i . Mł ISBN mm* 14.HB-4. C ty WN r»N 2

więcej podobnych podstron