instalacje103

3. STEROWANIE SILNIKÓW SKOKOWYCH 88

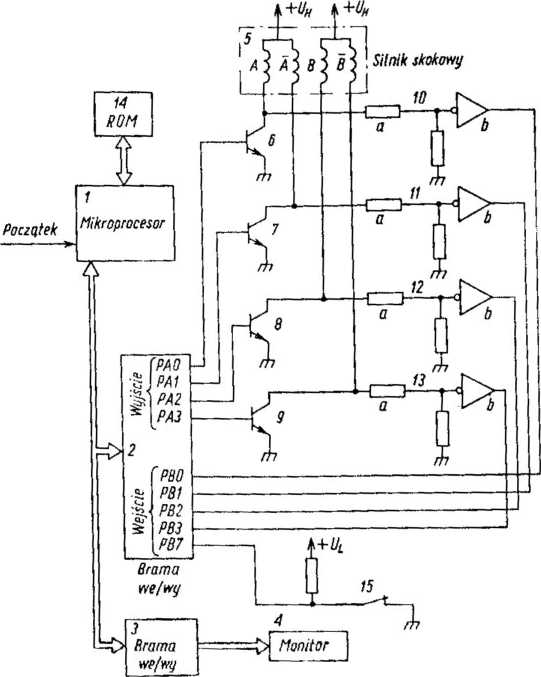

Rys. 3.17. Mikroprocesorowy układ sterowania silnika skokowego z wykrywaniem błędów

procesora /, pamięci stałej ROM (ang. Read Only Memory) 14 i bram wejście/wyjście 2, 3.

Silnik skokowy 5 ma uzwojenie dwupasmowe unipolarne, złożone z cewek A, A, B i B. Brama we/wy 2 zawiera cztery zaciski wyjściowe PAO, PA 1, 7M2 i PA2> które są przyłączone odpowiednio do baz tranzystorów mocy d, 7, # i 9.

Obwody kolektor-emiter tranzystorów są połączone w szereg z uz-wojenian i A, A, B i B i włączone na napięcie +UH, którym są zasilane odpowiednio do stanów logicznych zacisków wyjściowych bramy we/wy 2.

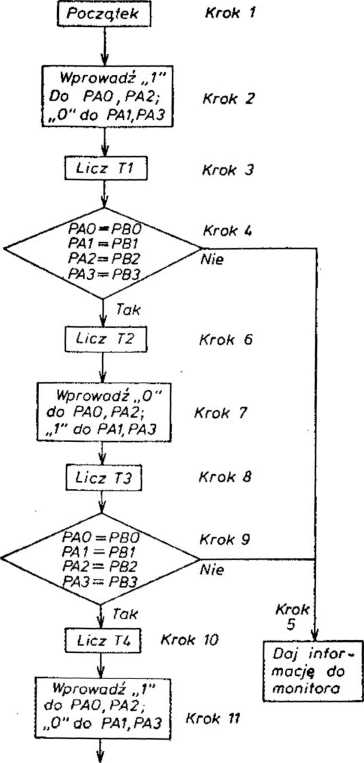

Rys. 3.18. Schemat czynności operacyjnych w programie mikrokomputera

Kolektory tranzystorów w dalszym ciągu są połączone odpowiednio z obwodami odczytującymi napięcia 10, 11, 12 i 13, a następnie z zaciskami wejściowymi PBO PB\, PB2 i PBZ bramy we/wy 2.

Pamięć stała 14 jest zaprogramowana do realizacji sekwencji przedstawionej na rys. 3.18. Po zadziałaniu wyłącznika (nic pokazanego na rysunku) impuls inicjujący realizację w czasie jest przekazany do mikroprocesora 1, powodując otrzymanie przezeń w tym samym czasie instruk-

Wyszukiwarka

Podobne podstrony:

instalacje094 X STEROWANIE SILNIKÓW SKOKOWYCH 70 Rys. 3.2. Komutacja symetryczna silnika skokowego:

instalacje098 3. STEROWANIE SILNIKÓW SKOKOWYCH 78 wartość maksymalną, to wyłącznik W (rys. 3.9b) zos

66208 instalacje154 7. ZASTOSOWANIA SILNIKÓW SKOKOWYCH 188 Rys. 7.8. Układ sterowania silnika skokow

33275 instalacje123 4. TEORIA SILNIKA SKOKOWEGO 128 Rys. 4.2J. Układ sterowania silnika skokowego z

instalacje102 3. STEROWANIE SILNIKÓW SKOKOWYCH 85 mable Read Only Memory). Na wyjściu układu PROM je

instalacje143 6. BADANIA SILNIKÓW SKOKOWYCH 166 Rys. 6.10. Układ do zdejmowania charakterystyki gran

instalacje145 6. BADANIA SILNIKÓW SKOKOWYCH 170 Rys. 6.13. Odpowiedź silnika FA-34-4-1 na skok jedno

instalacje152 7. ZASTOSOWANIA SILNIKÓW SKOKOWYCH 184 dów sterowania z silnikami skokowymi o znacznie

instalacje159 7. ZASTOSOWANIA SILNIKÓW SKOKOWYCH 198 Rys. 7.16. Schemat pracy skanera termalnego z e

instalacje161 7. ZASTOSOWANIA SILNIKÓW SKOKOWYCH 202 Rys. 7.19. Schemat automatu do badania elementó

więcej podobnych podstron