15. TRANZYSTORY POLOWE MOS

15.1. Zarys teorii tranzystorów MOS-FET

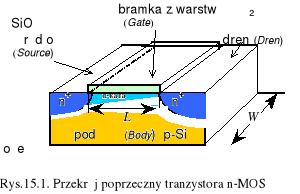

W tranzystorach polowych MOS-FET prąd płynący między źródłem a drenem w przypowierzchniowym kanale jest sterowany potencjałem elektrody bramki poprzez warstwę dielektryka - rys.15.1. Jest to prąd nośników większościowych. Kanał jest zwykle indukowany i tranzystor jest aktywny, gdy potencjał na bramce przekroczy wartość progową VT. Poniżej tej wartości przez tranzystor płyną znikome prądy przypowierzchniowe, a tranzystor znajduje się w stanie odcięcia.

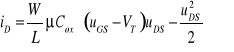

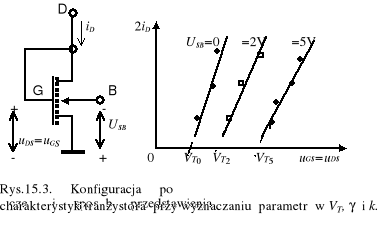

Przy stałych wartościach napięcia na bramce UGS w układzie wspólnego źródła (WS) na charakterystykach prądowych drenu w układzie współrzędnych (iD, uDS) dla napięć uDS mogą być wyszczególnione dwa zakresy: liniowy (nienasycenia) i nasycenia, rozdzielone napięciem uDS=uGS-VT (rys.15.2). W naj- prostszym opisie tranzystora prąd drenu w zakresie liniowym jest kwadratową funkcją napięcia drenu uDS

(15.1)

natomiast w zakresie nasycenia ma wartość stałą, niezależną od uDS

![]()

15.2)

gdzie: W - szerokość, a L - długość kanału, μ - ruchliwość nośników w kanale, oraz Cox - pojemność warstwy tlenkowej (izolacyjnej) bramki.

W tym najprostszym modelu tranzystora MOSFET (Sah - 1960) prąd przepływający przez kanał jest wyznaczony z równania dla składowej dryftowej transportu prądu nośników przez liniowo zawężający się kanał, powstały w obszarze ładunku przestrzennego. Jest to tzw. przybliżenie stopniowanego kanału; gdy pole elektryczne w kierunku prostopadłym do kanału jest znacz- nie większe niż natężenie pola wzdłuż kanału, w którym dryfują zaindukowane nośniki.

Pełny układ równań prądowych dla n-MOSFET-a przy niskich częstotliwościach pracy (iG=0) jest następujący:

dla uGS<VT, uDS>0 (stan odcięcia) (15.3a)

![]()

dla uGS>VT i 0<uDS<uGS -VT (15.3b)

(zakres liniowy)

![]()

dla uGS>VT i uDS>uGS - VT (15.3c)

(zakres nasycenia)

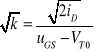

gdzie: ![]()

oraz VT0>0 dla kanału indukowanego,

zaś VT0<0 dla kanału zubożanego.

Gdzie ponadto wykorzystano tzw. parametry technologiczne tranzystorów:

k'=μCox - parametr transkonduktancyjny,

VT0 - napięcie progowe przy napięciu podłoże-źródło uBS=0,

γ - współczynnik objętościowy napięcia progowego,

λ - współczynnik modulacji długości kanału.

φ - potencjał powierzchniowy przy silnej inwersji półprzewodnika.

Dla tranzystorów p-MOSFET powyższe równania przyjmują postaci

dla uGS>VT, uDS<0 (stan odcięcia) (15.4a)

![]()

dla uGS<VT i 0>uDS>uGS -VT (15.4b)

(zakres liniowy)

![]()

dla uGS<VT i uDS<uGS - VT (15.4c)

(zakres nasycenia)

gdzie: ![]()

oraz VT0>0 dla kanału indukowanego,

zaś VT0<0 dla kanału zubożanego

Współczynniki k', γ, λ i φ są dodatnie dla obu typów kanałów. Ponadto w projektowaniu tranzystorów używany jest tzw. parametr transkonduktancyjny przyrządu, nazywany też współczynnikiem wzmocnienia

(15.5)

W modelu Shichmana-Hodgesa prąd drenu w zakresie nasycenia przy wyprowadzaniu powyższych zależności został powiązany z napięciem na drenie uDS, bowiem wraz ze wzrostem uDS powyżej UDSS (przy którym kanał traci ciągłość pomiędzy źródłem a drenem) poszerza się warstwa zubożona ładunku przestrzennego i skraca efektywna elektrycznie długość kanału L do L'. Także ze wzrostem uDS rośnie ładunek warstwy inwersyjnej w pobliżu drenu. Zależności (15.3c) i (15.4c) mają charakter empiryczny: mała wartość λ=0,1...0,01 1/V potwierdza niewielki wpływ uDS na iD w zakresie nasycenia (rys.15.2). Aby uniknąć nieciągłości na granicy obszarów liniowego i nasycenia w charakterystykach prądowych czynnik (1+λuDS) można dołączyć także do zależności dla zakresu liniowego. Wprowadza to oczywiście pewien błąd, jednakże nie znaczący w układach cyfrowych.

15.2. Metody wyznaczania parametrów charakterystycznych VT, γ, k i λ

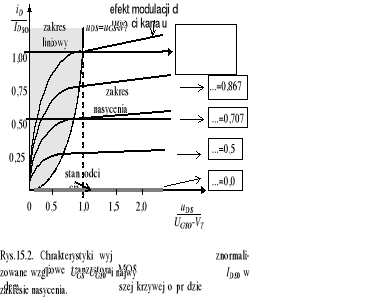

Pierwsze trzy parametry: VT, γ i k wyznaczamy z przebiegu charakterystyk przejściowych, zmierzonych dla tranzystora, w którym uGS=uDS (rys.15.3.), i przedstawionych w postaci funkcji

f(uGS=uDS) (15.6)

Z przebiegu wykresów łatwo otrzymujemy: VTO - z punktu odcięcia prądu przy iD=0 dla uSB=0, natomiast parametr k - z nachylenia prostej dla każdej stałej wartości USB, bowiem

(15.7)

oraz

(15.8)

przy czym można przyjąć, że dla tranzystorów z krzemu 2φ=0,6 V.

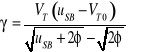

Efekt modulacji kanału określamy na podstawie pomiarów charakterystyki wyjściowej tranzystora w konfiguracji połączeń zewnętrznych jak na rys.15.4a. w sposób przedstawiony na rys.15.4b. Bowiem łatwo zauważyć, że dla każdych dwóch punktów na charakterystyce (ID,1,UD,1) i (ID,2,UD,2) mamy

(15.9)

stąd

(15.10)

15.3. Wielkosygnałowy model zastępczy tranzystora MOS-FET

Rys.15.5. przedstawia model wielkosygnałowy tranzystora MOS zaproponowany przez Shichmana i Hodgesa. W modelu tym istotna jest zależność źródła napięciowego iD od stałych napięć zewnętrznych, w tym także od napięcia pomiędzy podłożem a źródłem uBS. Diody w tym schemacie reprezentują złącza n-p pomiędzy źródłem a podłożem oraz drenem a podłożem z prądami

(15.11a)

(15.11b)

Is reprezentuje prądy upływności złącz podłożowych. rD i rS przedstawiają rezystancje drenu i źródła, które zwykle wynoszą około 50...100 om. Natomiast pojemności występujące w tym schemacie można podzielić na trzy grupy: pojemności barierowe CBD i CBS spolaryzowanych zaporowo złącz B-D i B-S, wspólne pojemności bramki CGD, CGS i CGB (ich wielkość zależy od zakresu pracy tranzystora) oraz pojemności pasożytnicze (konstruk-cyjne), niezależne od zakresu pracy.

15.4. Małosygnałowy model tranzystora MOS-FET

Tranzystory MOS są typowymi elementami układów cyfrowych. Jednakże ostatnio są one także wykorzystywane w analogowych układach scalonych jako wzmacniacze małych sygnałów. Małosygnałowy model zastępczy, niezbędny przy analizie takich układów, uzyskuje się na bazie modelu wielkosygnałowego, w którym uwzględnione są małe, linearyzowane zaburzenia parametrów wokół określonych stałych ich wartości. W wyniku różniczkowania zależności prądowo-napięciowych (15.2), (15.3) i (15.4) w stałych punktach pracy tranzystora definiujemy jego parametry małosygnałowe:

- transkonduktancję

(15.12)

- konduktancję wyjściową

(15.13)

oraz transkonduktancję, wynikającą z wpływu napięcia uBS na parametry kanału;

(15.14) Wartości tych małosygnałowych parametrów zależą od zakresu, w którym znajduje się punkt pracy tranzystora. Na przykład w zakresie nasycenia transkonduktancja gm, zgodnie zależnością (15.2), wynosi

![]()

(15.15) Zależność parametrów małosygnałowych od warunków wielkosygnałowych w powyższym wyrażeniu jest zatem wyraźna. Podobnie, korzystając z definicji (15.14) stwierdzimy że, transkonduktancja gmb wynosi

(15.16)

Jeżeli teraz skorzystamy z zależności (15.2) oraz zauważymy, że , to uzyskamy

(15.17)

gdzie η - współczynnik proporcjonalności. Ta transkonduktancja staje się ważna w przypadku, gdy wartość napięcia zmiennego uBS jest różna od zera.

Łatwo też stwierdzić, że transkonduktancja wyjściowa kanału gds jest funkcją liniową prądu drenu

(15.18)

Można także wykazać, że gds zależy od długości kanału L dla tranzystorów o krótkim kanale.

Wartości rezystancji rd i rs są porównywalne z wartościami rD i rS w modelu wielkosygnałowym z rys.15.5. Podobnie przyjmuje się, że Cgs, Cgd, Cgb, Cbd i Cbs są takie same jak CGS, CGD, CGB, CBD i CBS. Przy szacowaniu wielkości Cbd i Cbs można skorzystać z następujących przybliżeń:

(15.19)

(15.20)

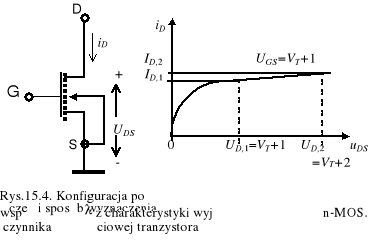

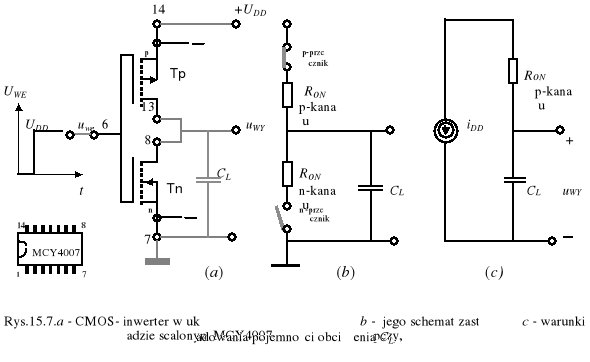

15.5. Inwerter CMOS

Oba przedstawione powyżej typy tranzystorów polowych; n-MOS i p-MOS wykonane w technologii komplementarnej CMOS na jednym podłożu tworzą tzw. inwerter CMOS - najczęściej występujący obwód w układach scalonych (rys.15.6). Jest to struktura CMOS-inwertera wykonana w n-podłożu; dla tranzystora n-MOS utworzono tzw. p-studnię dyfuzyjną, w której z kolei wdyfundowano n-obszary źródła i drenu.

Podłoża (body) każdego z tranzystorów są połączone z ich źródłami, aby zapobiec polaryzacji przepustowej złącz p-n. Bramki tranzystorów są wspólne. Na bramki w układach logicznych podawany jest sygnał wejściowy zmieniający się od logicznego zera uWE(0)≈0 do logicznej jedynki uWE(1)≈UDD. Wyjściowy sygnał jest zbierany ze wspólnych drenów tranzystorów na pojemnościowym obciążeniu CL - rys.15.7.

W układzie tym trudno jest odróżnić, który tranzystor jest sterujący, a który sterowany. Przy niskim poziomie napięcia na wejściu (logiczne 0) otwarty jest p-MOS, a n-MOS zamknięty, i na wyjściu mamy wysoki poziom napięcia (logiczna 1), bliski napięciu zasilania UDD. Przy wysokim napięciu otwarty jest n-MOS, a p-MOS zamknięty, i wyjściowe napięcie jest niskie. Jest to typowa praca inwertera, w którym p-MOS spełnia rolę zmiennego obciążenia. Zamykanie jednego tranzystora otwiera drugi - i na odwrót (stąd: push and pull inverter). Taka praca układu jest związana z faktem, że

uGS(n)+uGS(p)=UDD (15.21)

a spadek wartości uGS jednego z tranzystorów powoduje zwiększenie uGS drugiego. W efekcie charakterystyka przejściowa CMOS-inwertera wygląda jak na rys. 15.8.

Założymy na wstępie, że parametry tranzystorów są jednakowe, a prądy upływności bardzo małe. Ogólny warunek jest taki, że

VTn + VTp <UDD<UBO(n-p) (15.22)

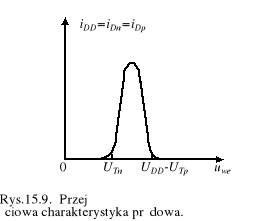

Wtedy dla uWE z zakresu 0<uWE<VTn, tranzystor n-MOS jest zamkniety, a stanowiący obciążenie p-MOS otwarty, i wyjściowe napięcie wynosi uWY=UDD=U(1). Przy zwiększaniu uWE od VTn do UDD-VTp zachodzi ciągłe zamykanie p-tranzystora, otwieranie n-tranzystora i zmniejszanie napięcia wyjściowego uWY. Przy uWE=UDD-VTp tranzystor obciążający jest zamknięty i uWY =0=U(1). Zatem oba tranzystory włączają się nieokreślonym logicznym stanie pośrednim i wówczas prąd iDD może wzrosnąć do niebezpiecznego poziomu (rys. 15.9).

Bardzo ważne w układach logicznych czasy opóźnienia, narastania i opadania sygnału zależą także od napięcia zasilania. Najprostsze formy tych zależności dla CMOS-inwertera można otrzymać przy pominięciu pojemności własnych tranzystorów, przyjmując, że na wejście podawana jest logiczna jedynka Uwe(1). Wtedy p-MOS zamyka się, a n-MOS otwiera, i na wyjściu uzyskujemy logiczną jedynkę: Uwe(1). Przy przełączaniu tego stanu na stan niski; przy Uwe(1) odwracają się stany tranzystorów, a CL zaczyna ładować się poprzez p-MOS do napięcia +UDD. Można przyjąć, że ten tranzystor pozostaje w zakresie nasycenia poprzez cały czas ładowania prądem

![]()

(15.23)

gdzie uGS= UDD. Jeżeli przyjąć, że VTp<<UDD, to

(15.24)

Zatem prąd źródła w schemacie zastępczym inwertera (rys15.7c.) wynosi

(15.25)

Jest to stały prąd ładowania pojemności obciążenia CL. Zatem

![]()

(15.26)

stąd

![]()

(15.27)

Jeżeli uwy =UDD, to stała czasowa układu t≡ wyniesie

(15.28)

Stąd wniosek, że czas narastania CMOS-inwertera jest odwrotnie proporcjonalny do napięcia zasilania UDD.

15.6. Przebieg ćwiczenia

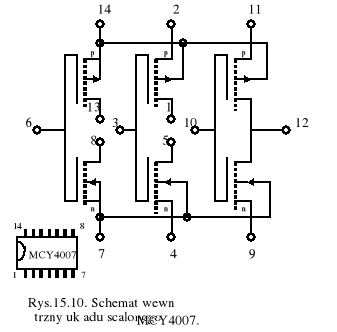

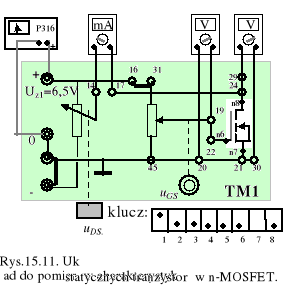

Celem ćwiczenia jest wyznaczenie charakterystyk napięciowo-prądowych tranzystorów n-MOS i p-MOS, tworzących pary komplementarne w układzie scalonym MCY74007 (rys.15.10) oraz określenie wartości parametrów elementów występujących w schemach zastępczych tych tranzystorów.

W tym celu należy:

1. W układzie pomiarowym zestawionym na module TM1 według rys.15.11. zmierzyć charakterystykę przejściową iD=iD(uGS) tranzystora n-MOS, dostępnego na wyprowadzeniach 6(G), 8 (D) i 7(S,B) układu MCY74007 w zakresie napięć dodatnich na bramce od UGS=0 do UGS= 5 V przy stałej wartości napięcia UDS=5V. Sporządzić wykres funkcji √iD=f(uGS).

2. W tym samym układzie dokonać pomiarów potrzebnych do wykreślenia charakterystyk wyjściowych iD= iD(uDS) w zakresie napięć od UDS=0 do UDS=5V przy stałych napięciach na bramce UGS=2, 2,5, 3 i 4 V.

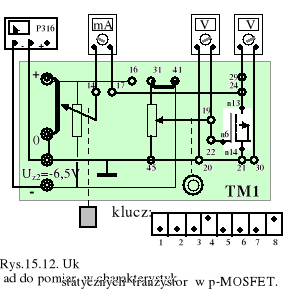

3. W układzie pomiarowym sporządzonym według rys.15.12. zmierzyć charakterystykę przejściową iD= iD(uGS) tranzystora p-MOS, dostępnego na wyprowadzeniach 6(G), 13(D) i 14(S,B) układu MCY74007. Pomiary dokonujemy przy napięciach ujemnych UDS= -5V oraz UGS=-5 do UGS= 0 V. Na podstawie zebranych wyników wykreślić zależność √iD= f(uGS).

4. Na podstawie zebranych pomiarów i przy pomocy wykresów wyznaczyć wartości parametrów elektrycznych elementów występujących w zastępczych schematach zastępczych tranzystorów oraz charakterystyczne parametry napięcia progowego VT, γ , k i λ.

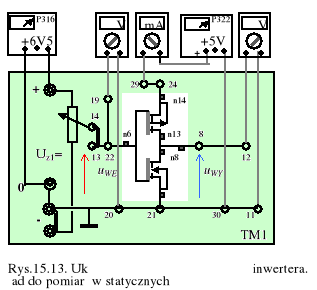

5. Zdjąć charakterystykę przejściową CMOS-inwertera z układu MCY40070N w układzie sporządzonym wg rys. 15.13. Z jej przebiegu odczytujemy wartości Uwy(1), Uwy(0) oraz Uwe(1) i Uwe(0). Wykreślić także charakterystykę prądu pobieranego przez inwerter w funkcji napięcia uWE dla dwóch wartości napięcia zasilania UDD = 5 i 10 V.

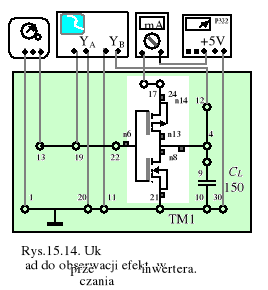

6. Obciążyć inwerter pojemnością CL =150 pF i w układzie z rys.15.14. zaobserwować na oscyloskopie przełączanie inwertera sterowanego napięciem o przebiegu prostokątnym z amplitudą Uwe(1)=5 V i częstotliwości od 100 do 500 kHz. Dokładnie odrysować przebiegi napięcia wyjściowego o czasach narastania tr i opadania tf przy zasilaniu układu 5 i 10 V. Korzystając z przedstawionych powyżej zależności oszacować i porównać z odczytami z oscyloskopu wartości tych czasów. Pamiętać, że sonda pomiarowa także stanowi dodatkowe obciążenie inwertera!

Wyszukiwarka

Podobne podstrony:

CWn12, 3 semestr, Przyrządy Półprzewodnikowe

SPIS-i-ORG 05, 3 semestr, Przyrządy Półprzewodnikowe

CW-OZNA, 3 semestr, Przyrządy Półprzewodnikowe

CWn14, 3 semestr, Przyrządy Półprzewodnikowe

CWn7, 3 semestr, Przyrządy Półprzewodnikowe

CWp13, 3 semestr, Przyrządy Półprzewodnikowe

CW7, 3 semestr, Przyrządy Półprzewodnikowe

CWL8, 3 semestr, Przyrządy Półprzewodnikowe

CW15Ub, 3 semestr, Przyrządy Półprzewodnikowe

CWn15, 3 semestr, Przyrządy Półprzewodnikowe

Cwn9VEE, 3 semestr, Przyrządy Półprzewodnikowe

CWn9, 3 semestr, Przyrządy Półprzewodnikowe

CwS1, 3 semestr, Przyrządy Półprzewodnikowe

Przyrządy półprzewodnikowe (2)

Badanie optoelektrycznych właściwości przyrządów półprzewodnikowych 5 , LABORATORIUM FIZYCZNE

Materiałoznawstwo, Badanie właściwości materiałów i przyrządów półprzewodnikowych, POLITECHNIKA LUBE

Badanie optoelektrycznych właściwości przyrządów półprzewodnikowych 1 , Pomiar pierwszy

więcej podobnych podstron