DSC04611

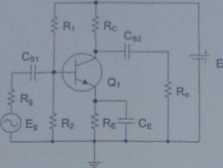

V\Vv Nementy wzmacniacza pasmowego przedstawionego na rys. ograniczają jego M-y •■-..o o»i góry, a które od dołu. Które elementy na schemacie odpowiadają za ustalenie /y uH.rn pthty wzmacniacza. Do czego służą Re i Ce-

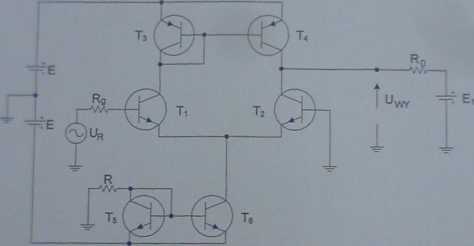

*Vmhi rolę elementów Tl, T2, T3, T4 oraz T5, T6 we wzmacniaczu różnicowym TO3»i«aiwłonym na rys.

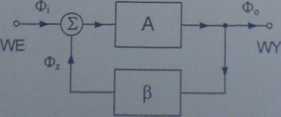

$***» jest ogólny schemat układu ze sprzężeniem zwrotnym. Czym są bloki A i p. fearanj sygnały <J>*, O0, <[>2. Podaj wzór ogólny na transmitancję takiego układu. Jak amBfmmty iloczyn AP, a jak różnicę 1-Ąp.

* komparator realizujący następującą charakterystykę przejściową Narysuj

czasowe napięcia na wejściu i wyjściu jeżeli układ jest pobudzony sygnałem ty&prfWemtoi

|

I Uwy | ||

|

+5V | ||

|

-1V | ||

|

Mwa | ||

Wyszukiwarka

Podobne podstrony:

276 (31) 27t) OHi.ICV.ANIK KONSTRUKCYJNE wzmacniacza, przedstawiono na rys. XVI 1.7. Napięcie z gene

Zadania ćwiczenia?iC zbadania z ćwiczeń Zadanie 1. W układzie wzmacniacza przedstawionym na rys. zas

Image049 Funkcję I (AND) dwóch zmiennych boolowskich przedstawiono na rys. 3.1. Każda liczba zmienny

Image050 operację sumy logicznej Y, jest przedstawiony na rys. 3.4. Napięcie baterii roz-świeci żaró

Image073 Układ służący do realizacji tej funkcji, zbudowany z bramek I (AND), LUB (OR), NIE (NOT) pr

Image075 Karnaugha. Sklejając tak, jak w tablicy przedstawionej na rys. 3.34a, otrzymuje się następu

Image078 Tablica wartości tej funkcji jest przedstawiona na rys. 3.36a. Ponieważ rozważana funkcja j

Image079 Tablica wartości tej funkcji przedstawiona na rys. 3.38a, a rozwiązanie zadania na rys.

Image098 r Bramka LUB-NIE (NOR) oraz LUB (OR) Schemat elektryczny bramki LUB-NIE — 02 przedstawiono

Image114 Przerzutnik JK-MS — 72 przedstawiono na rys. 4.53. Bramki 1 i 2 realizują funkcje K = KX*K2

Image119 czasu propagacji sygnału do stanu 0 na wyjściu od temperatury dla przerzutni-ka D przedstaw

Image161 Symbol graficzny rozpatrywanej pamięci z zaznaczeniem wszystkich linii sygnałów przedstawio

Image183 Struktura logiczna układów FPLA Schemat logiczny typowego układu FPLA przedstawiono na rys.

Image229 Schemat logiczny dekady liczącej w kodzie 8421 przedstawiono na rys. 4.230. Maksymalna częs

Image250 Schemat logiczny synchronicznego dwukierunkowego licznika dwójkowego (193) przedstawiono na

Image262 nęgo z dekad liczących 192 i nastawników dziesiętnych, zawierających enko-dery, przedstawio

Image277 oraz przebiegi napięć na wyjściu W przedstawiono na rys. 4.309. Blokadę zliczania zrealizow

więcej podobnych podstron