3132014838

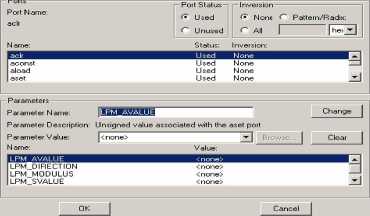

Okno konfiguracji przedstawiono na rys. 2.

2<J

Function Name: LPM_COUNTER Help on LPM_COUNTER

Rys. 7-2. Okno konfiguracji bloku LPM_Counter

Pole „Ports” umożliwia konfigurację wejść i wyjść licznika. Można włączyć („used”) lub wyłączyć („unused”) poszczególne wejścia lub wyjścia układu. Możliwa jest negacja poszczególnych sygnałów („inversion”) lub ustawienie stałych poziomów („pattern”).

Pole „Parameters” służy do ustawiania poszczególnych parametrów licznika. Po wybraniu wskaźnikiem parametru z przewijanej listy, jego nazwa pojawia się w polu „Parametr Name” i wówczas pożądaną wartość wpisujemy w polu „Parametr Value”. Wpis zatwierdzamy przyciskiem „Change”. Przycisk „Help on LPM_COUNTER” otwiera okno z pomocą w którym jest opis wszystkich parametrów.

Tabele 1 - 4 zawierają podstawowe parametry liczników LPM_Counter, rodzaje wejść, wyjść oraz opis podstawowych funkcji.

Tabela 1: Porty wejściowe licznika LPM Counter

|

Port: |

Wymagany: |

Opis: |

Komentarz: |

|

data[] |

Nie |

Równoległe wejście danych |

Port wejściowy o szerokości LPM_WIDTH. Wykorzystywany z aload lub sload. |

4

Wyszukiwarka

Podobne podstrony:

Image049 Funkcję I (AND) dwóch zmiennych boolowskich przedstawiono na rys. 3.1. Każda liczba zmienny

Image050 operację sumy logicznej Y, jest przedstawiony na rys. 3.4. Napięcie baterii roz-świeci żaró

Image073 Układ służący do realizacji tej funkcji, zbudowany z bramek I (AND), LUB (OR), NIE (NOT) pr

Image075 Karnaugha. Sklejając tak, jak w tablicy przedstawionej na rys. 3.34a, otrzymuje się następu

Image078 Tablica wartości tej funkcji jest przedstawiona na rys. 3.36a. Ponieważ rozważana funkcja j

Image079 Tablica wartości tej funkcji przedstawiona na rys. 3.38a, a rozwiązanie zadania na rys.

Image098 r Bramka LUB-NIE (NOR) oraz LUB (OR) Schemat elektryczny bramki LUB-NIE — 02 przedstawiono

Image114 Przerzutnik JK-MS — 72 przedstawiono na rys. 4.53. Bramki 1 i 2 realizują funkcje K = KX*K2

Image119 czasu propagacji sygnału do stanu 0 na wyjściu od temperatury dla przerzutni-ka D przedstaw

Image161 Symbol graficzny rozpatrywanej pamięci z zaznaczeniem wszystkich linii sygnałów przedstawio

Image183 Struktura logiczna układów FPLA Schemat logiczny typowego układu FPLA przedstawiono na rys.

Image229 Schemat logiczny dekady liczącej w kodzie 8421 przedstawiono na rys. 4.230. Maksymalna częs

Image250 Schemat logiczny synchronicznego dwukierunkowego licznika dwójkowego (193) przedstawiono na

Image262 nęgo z dekad liczących 192 i nastawników dziesiętnych, zawierających enko-dery, przedstawio

Image277 oraz przebiegi napięć na wyjściu W przedstawiono na rys. 4.309. Blokadę zliczania zrealizow

Image294 realizację operacji dodawania. Układ przedstawiony na rys. 4.335 umożliwia realizację opera

więcej podobnych podstron