1. Opisa

ć

w cyklach maszynowych sposób pobrania i wykonania rozkazu CALL ADR.

CALL ADR jest to rozkaz wywołania podprogramu, który wykonuje si

ę

w 5 cyklach maszynowych:

Cykl 1. <pobranie bajtu rozkazu>

–

na magistral

ę

adresow

ą

wysyłana jest zawarto

ść

licznika rozkazów PC

–

generowane s

ą

sygnały: pobrania rozkazu M1, dost

ę

pu do pami

ę

ci MREQ i odczytu pami

ę

ci RD w

stanie niskim

–

mniej wi

ę

cej po upłyni

ę

ciu taktu zegarowego od wygenerowania ww. sygnałów na magistrali danych

ustala si

ę

bajt rozkazu spod wskazanego przez PC adresu, który jest pobierany do rejestru rozkazów, a

nast

ę

pnie dekodowany

–

zawarto

ść

licznika rozkazów PC zwi

ę

ksza si

ę

o 1, a procesor przyst

ę

puje do wykonania rozkazu

Cykl 2. <pobranie 1. bajtu adresu ADR>

–

na magistral

ę

adresow

ą

wysyłana jest zawarto

ść

licznika rozkazów PC

–

generowane s

ą

sygnały: dost

ę

pu do pami

ę

ci MREQ i odczytu pami

ę

ci RD w stanie niskim

–

dana z magistrali danych (1. bajt adresu podprogramu) pobierane s

ą

do rejestru rozkazów

–

zawarto

ść

licznika rozkazów PC zwi

ę

ksza si

ę

o 1

Cykl 3. <pobranie 2. bajtu adresu ADR>

Przebiega analogicznie do cyklu 2. Po tym cyklu w rejestrze rozkazów znajduje si

ę

dwubajtowy adres

podprogramu ADR, a licznik rozkazów PC zawiera adres powrotu.

Cykl 4. <wysłanie na stos 1. bajtu PC>

–

na magistral

ę

adresow

ą

wysyłana jest zawarto

ść

wska

ź

nika stosu SP pomniejszonego o 1 (tak, aby

wskazywał na pust

ą

komórk

ę

pami

ę

ci)

–

generowany jest sygnał dost

ę

pu do pami

ę

ci MREQ w stanie niskim, za

ś

na magistral

ę

danych wysyłany

jest 1. bajt licznika rozkazów PC

–

po ustaleniu si

ę

zawarto

ś

ci magistrali danych (trwa to mniej wi

ę

cej takt zegarowy) procesor generuje

sygnał zapisu WR w stanie niskim i dana wpisywana jest do komórki wskazywanej przez SP

Cykl 5. <wysłanie na stos 2. bajtu PC>

Przebiega analogicznie do cyklu 4. Po tym cyklu wska

ź

nik stosu zawiera warto

ść

dwukrotnie mniejsz

ą

od tej

sprzed cyklu 4, wskazuj

ą

c na 2. bajt adresu powrotu. Pod koniec tego cyklu nast

ę

puje szybkie wpisanie

znajduj

ą

cego si

ę

w rejestrze rozkazów adresu ADR do licznika rozkazów PC i wykonanie rozkazu ko

ń

czy

si

ę

.

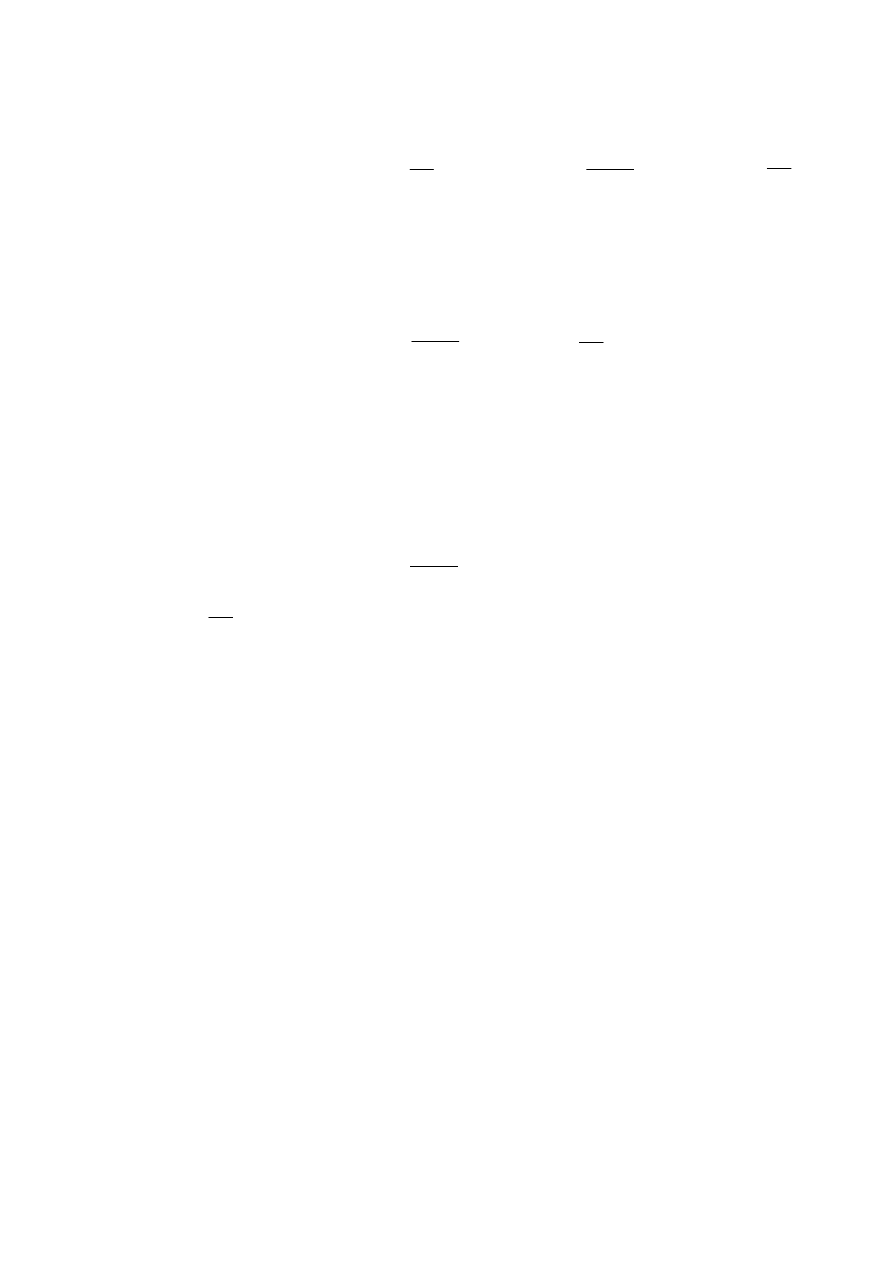

2. Narysowa

ć

schemat dekodera adresu dla karty we/wy komputera PC, na której znajduj

ą

si

ę

dwa układy 8255. Adres bazowy to 320H . Poda

ć

adresy portów dost

ę

pnych za po

ś

rednictwem tej karty.

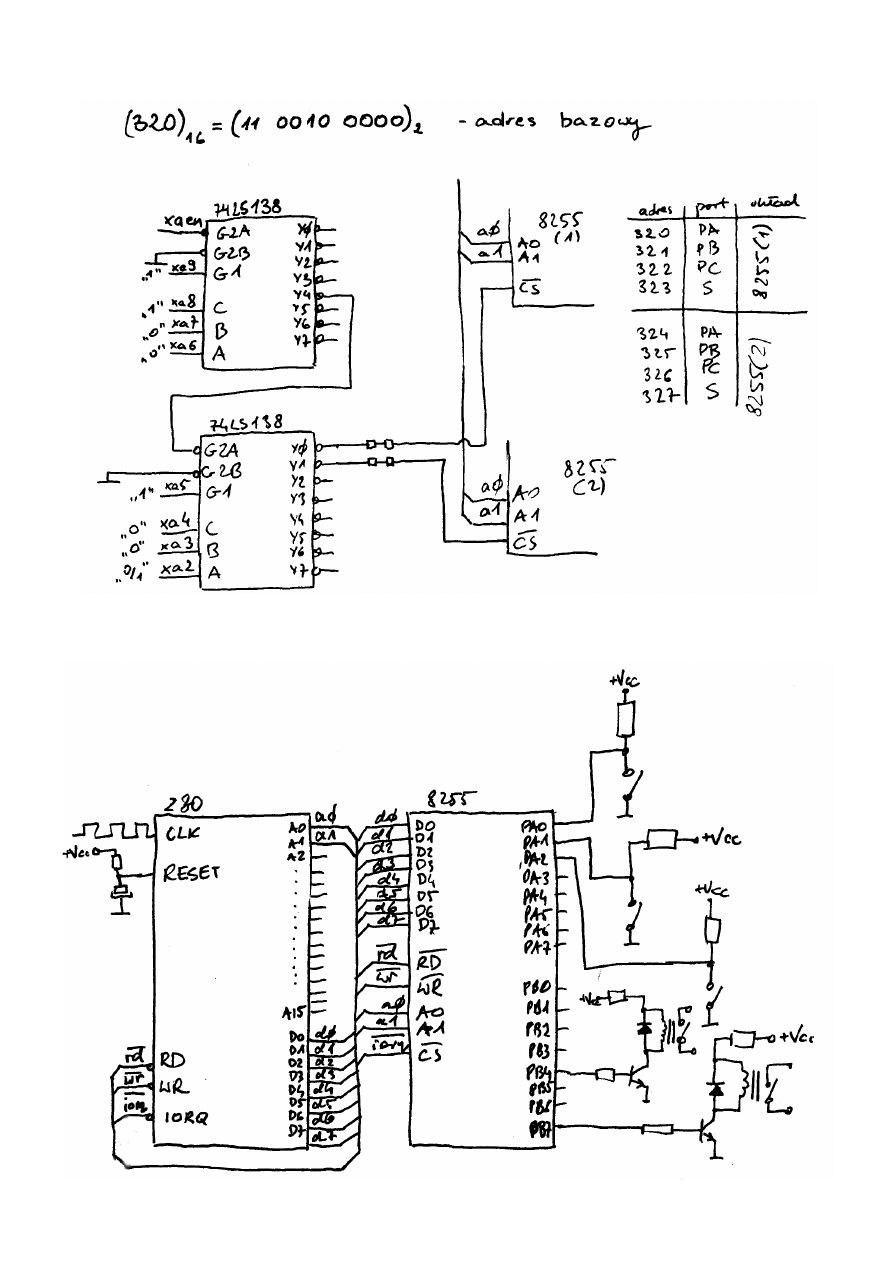

3. Narysowa

ć

schemat układu we/wy dla mikroprocesora Z80, który ma doł

ą

czone dwa elektromagnesy i

trzy przyciski.

Wyszukiwarka

Podobne podstrony:

etr2 opracowany egzamin 18czerw2008

opracowanie egzamin fizyki v1 0

Mechanika Ciał Stałych opracowanie egzamin

Materiaoznawstwo - opracowany egzamin (termin o), AGH, 5 semestr, material

Opracowanie egzamin chemia, AGH, AGH

rachunkowosc-opracowanie egzamin, zarządzanie

Maszyny egzamin opracowanie, EGZAMIN Z MASZYN LEŚNYCH

Ratownictwo Morksie opracowanie egzamin

Opracowanie egzamin

Opracowanie?NKOWOŚĆ egzamin

opracowany egzamin 13 !!!

PiEwOŚ Opracowany egzamin

!!!!OPRACOWANIE EGZAMIN!!!!id 4 Nieznany (2)

3z3, Inżynieria Środowiska, mgr 1 semestr, Uzdatnianie wody do celów przemysłowych, wykłady, opracow

opracowanie egzaminu

PAiR Opracowanie Egzamin by Yanoo

więcej podobnych podstron