Architektura Komputerów 2006

1

Struktura połączeń – cz. I

Komputer jest zestawem zespołów lub modułów trzech podstawowych

typów (procesor, pamięć, wejście-wyjście), które komunikują się

wzajemnie. W rezultacie komputer jest siecią obejmującą podstawowe

moduły. Muszą więc istnieć ścieżki łączące moduły.

Zbiór ścieżek łączących moduły jest nazywany strukturą połączeń.

Projektowanie tej struktury zależy od wymiany, która musi zachodzić

między modułami.

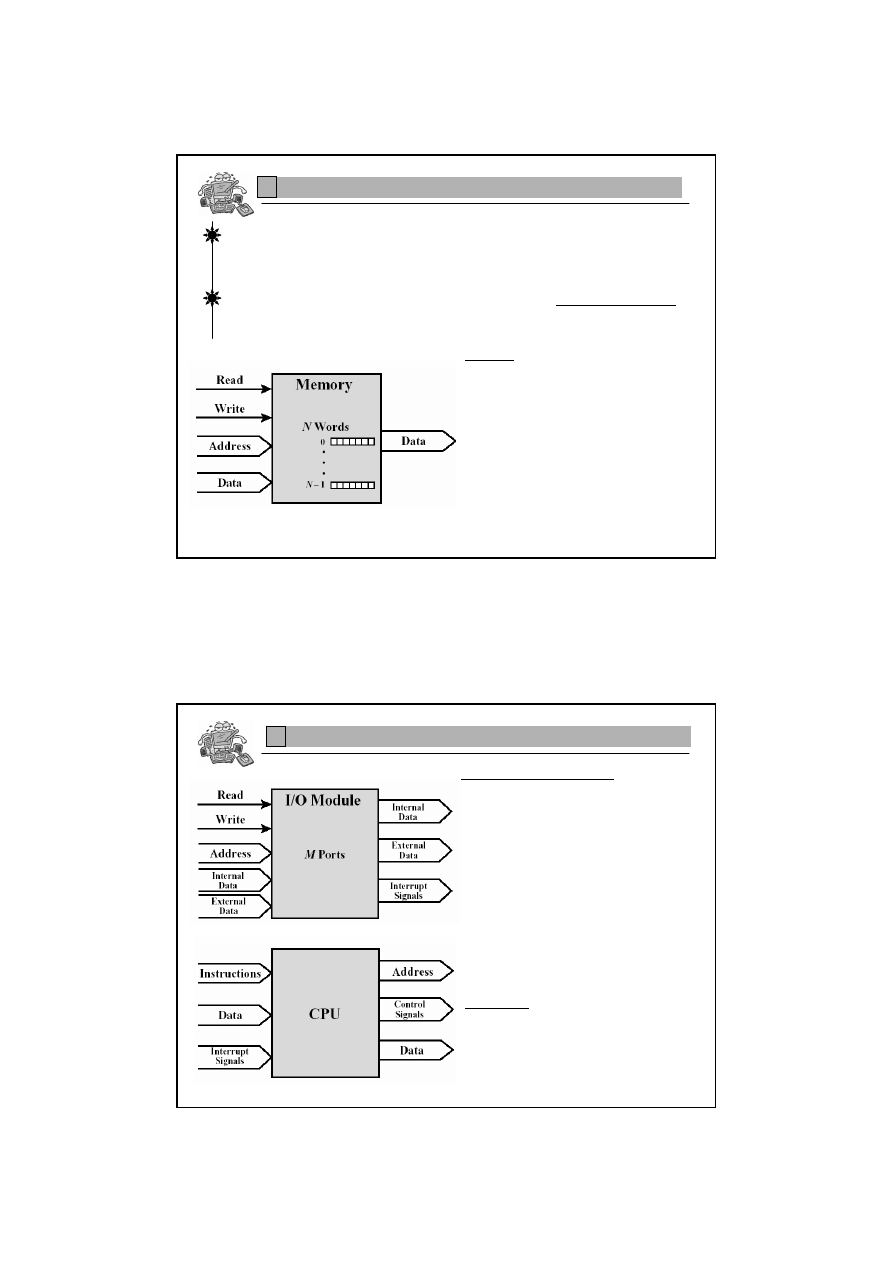

Pamięć

.

Moduł pamięci składa się zwykle z

N

słów o jednakowej długości. Każde

słowo ma przypisany jednoznaczny

adres numeryczny (0, l, ...,

N - 1).

Słowo może być odczytane z pamięci

lub do niej zapisane. Rodzaj operacji

jest

wskazywany

przez

sygnały

sterujące

„czytaj"

lub

„zapisz".

Lokacja, której dotyczy operacja, jest

wskazywana przez adres.

1

Struktura połączeń – cz. II

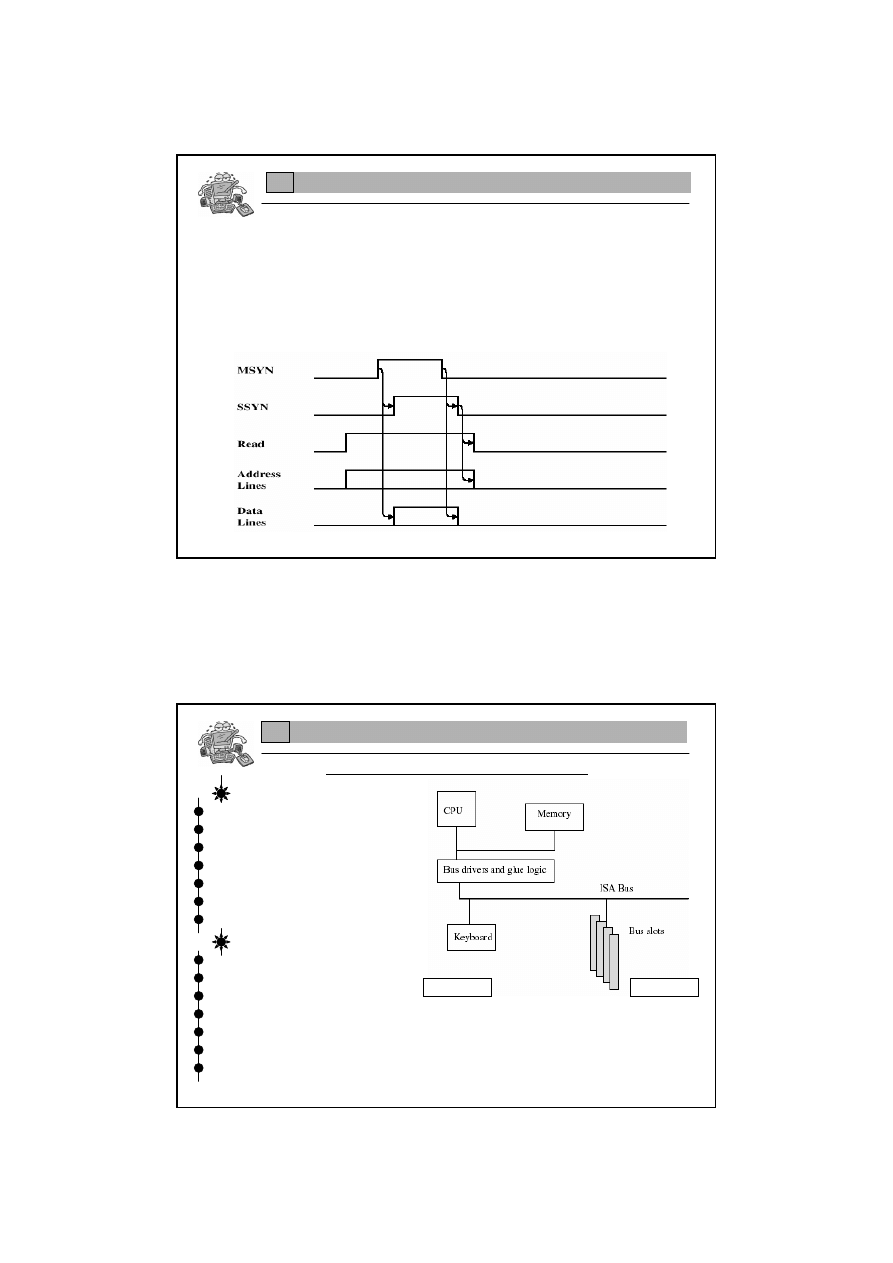

Modul wejścia-wyjścia

.

Istnieją

dwie

operacje:

zapisu

i

odczytu.

Ponadto

moduł

wejścia-

wyjścia może sterować więcej niż

jednym urządzeniem zewnętrznym.

Możemy określić każdy z interfejsów z

urządzeniem zewnętrznym jako port i

nadać każdemu z nich jednoznaczny

adres (np. O, l,...,

M- 1). Istnieją poza

tym

zewnętrzne

ścieżki

danych

służące

do

wprowadzania

i

wyprowadzania danych z urządzenia

zewnętrznego.

Wreszcie

moduł

wejścia-wyjścia może wysyłać sygnały

przerwania do procesora.

Procesor.

Procesor wczytuje rozkazy i dane,

wysyła dane po przetworzeniu i

posługuje się sygnałami sterującymi

do sterowania całą pracą systemu.

Otrzymuje też sygnały przerwania.

2

Architektura Komputerów 2006

2

Struktura połączeń – cz. III

Struktura połączeń musi umożliwiać przesyłanie danych:

Z pamięci do procesora. Procesor odczytuje z pamięci rozkazy lub

jednostki danych.

Z procesora do pamięci. Procesor zapisuje jednostki danych w pamięci.

Z urządzeń wejścia-wyjścia do procesora. Procesor odczytuje dane z

urządzenia wejścia-wyjścia za pośrednictwem modułu wejścia-wyjścia.

Z

procesora do wejścia-wyjścia. Procesor wysyła dane do urządzenia

wejścia-wyjścia.

Z

urządzeń wejścia-wyjścia do pamięci lub na odwrót. W tych dwóch

przypadkach zezwala się modułowi wejścia-wyjścia na bezpośrednią

wymianę

danych z pamięcią, bez pośrednictwa procesora, przy

wykorzystaniu bezpośredniego dostępu do pamięci (DMA).

3

Połączenia magistralowe

Magistrala jest drogą zapewniającą komunikację między urządzeniami.

Główną cechą charakterystyczną magistrali jest to, że jest ona

wspólnym nośnikiem transmisji (ang.

shared transmission medium).

Do magistrali dołącza się wiele urządzeń, a sygnały wysyłane przez

którekolwiek z nich mogą być odbierane przez wszystkie pozostałe

urządzenia. Jeśli dwa urządzenia nadawałyby w tym samym czasie, ich

sygnały nakładałyby się i ulegały zakłócaniu. W określonym czasie

może więc nadawać tylko jedno urządzenie.

Magistrala łącząca główne zespoły komputera (procesor, pamięć,

wejście-wyjście) nazywana jest magistralą systemową. Najczęściej

spotykane struktury połączeń komputera wykorzystują jedną lub

więcej magistrali systemowych.

Magistrala systemowa składa się zwykle z 50 do 100 oddzielnych linii.

Każdej linii jest przypisane określone znaczenie lub funkcja.

4

Architektura Komputerów 2006

3

Struktura magistrali – cz. I

Linie zawarte w magistrali systemowej można podzielić na trzy grupy

funkcjonalne: linie danych, adresów i sterowania. Ponadto mogą występować

linie służące do zasilania dołączonych modułów.

Działanie magistrali jest następujące. Jeśli jeden

z modułów zamierza wy-słać

dane do

drugiego, to musi wykonać dwie rzeczy:

(1) uzyskać dostęp do magistrali

(2) przekazać dane za pośrednictwem magistrali.

Jeśli natomiast zamierza uzyskać dane z innego

modułu, to musi:

(1) uzyskać dostęp do magistrali

(2) przekazać zapotrzebowanie do tego modułu

przez

odpowiednie

linie

sterowania

i

adresowe. Musi następnie czekać, aż drugi

moduł wyśle dane

.

5

Struktura magistrali – cz. II

Linie danych są ścieżkami służącymi do przenoszenia danych między

modułami systemu. Wszystkie te linie łącznie są określane jako szyna

danych (ang.

data bus). Liczba linii określa szerokość tej szyny. W danym

momencie każda linia może przenosić tylko l bit. Szerokość szyny danych

jest kluczowym czynnikiem określającym wydajność całego systemu.

Linie adresowe są wykorzystywane do określania źródła lub miejsca

przeznaczenia danych przesyłanych magistralą. Szerokość szyny adresowej

determinuje maksymalną możliwą pojemność pamięci systemu. Ponadto

linie adresowe są również używane do adresowania portów wejścia-wyjścia.

Najczęściej najbardziej znaczące bity służą do wybrania określonego modułu

na magistrali, natomiast najmniej znaczące bity określają lokację w pamięci

lub port wejścia--wyjścia wewnątrz modułu.

Linii sterowania używa się do sterowania dostępem do linii danych i linii

adresowych, a także do sterowania ich wykorzystaniem. Ponieważ linie

danych i adresowe służą

wszystkim zespołom, musi istnieć

sposób

sterowania ich używaniem. Sygnały sterujące przekazywane między

modułami systemu zawierają zarówno rozkazy, jak i informacje regulujące

czas (taktujące). Sygnały czasowe określają ważność danych i adresów.

Sygnały rozkazów precyzują operacje, które mają być przeprowadzone.

6

Architektura Komputerów 2006

4

Linie sterowania magistrali

Typowe linie sterowania to linie:

Zapis w pamięci. Sprawia, że dane z magistrali zostają zapisane pod

określonym adresem.

Odczyt z pamięci. Sprawia, że dane spod określonego adresu są umieszczane

w magistrali.

Zapis do wejścia-wyjścia. Sprawia, że dane z magistrali są kierowane do

zaadresowanego portu wejścia-wyjścia.

Odczyt z wejścia-wyjścia. Sprawia, że dane z zaadresowanego portu wejścia-

wyjścia są umieszczane na magistrali.

Potwierdzenie przesyłania (transfer ACK). Wskazuje, że dane zostały przyjęte

z magistrali lub na niej umieszczone.

Zapotrzebowanie na magistralę (bus reąuest). Wskazuje, że moduł zgłasza

zapotrzebowanie na przejęcie sterowania magistralą.

Rezygnacja z magistrali (bus grant). Wskazuje, że moduł rezygnuje ze

sterowania magistralą.

Żądanie przerwania (interrupt request). Wskazuje, że przerwanie jest

zawieszone.

Potwierdzenie przerwania

(interrupt

ACK). Potwierdza, że zawieszone

przerwanie zostało rozpoznane.

Zegar. Wykorzystywany do synchronizowania operacji.

Przywrócenie (reset). Ustawia wszystkie moduły w stanie początkowym.

7

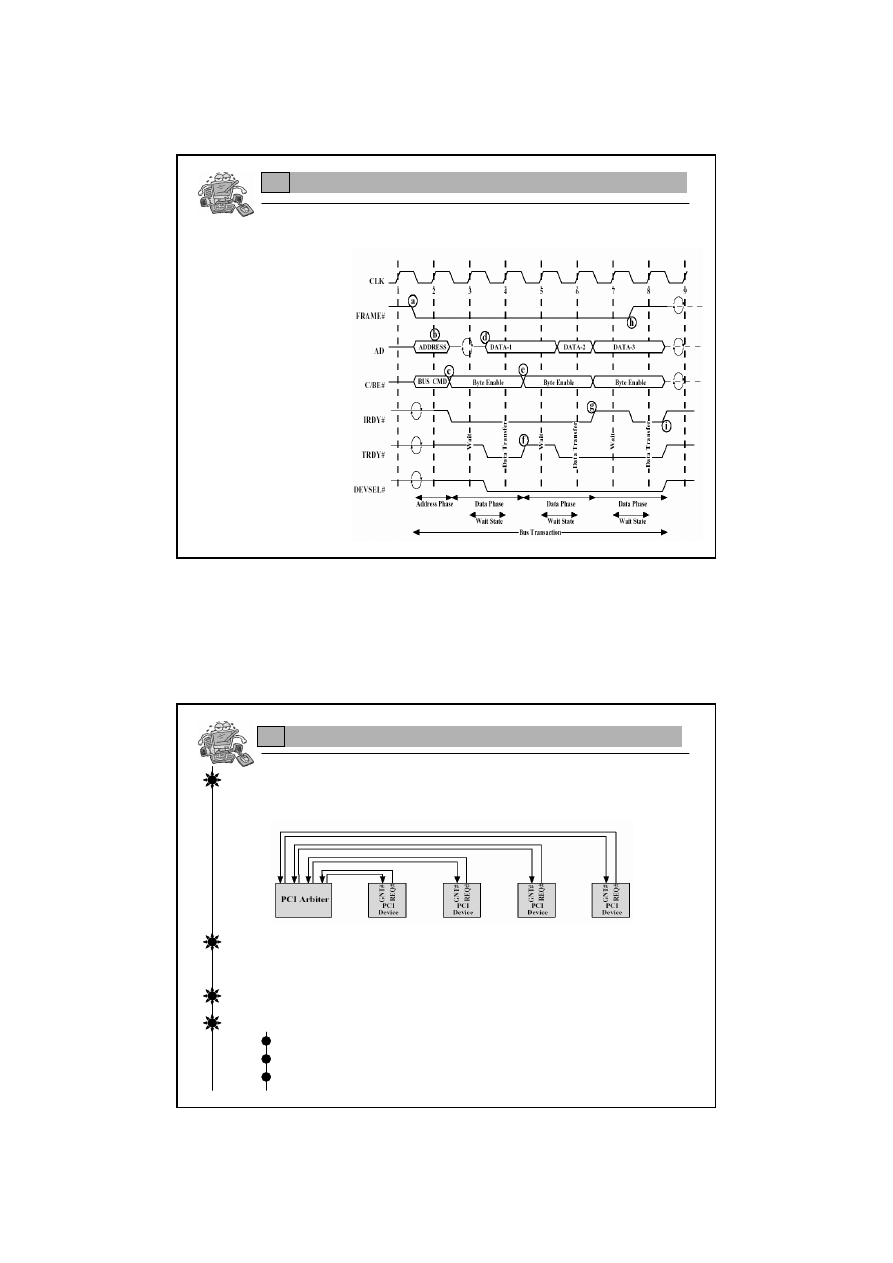

Hierarchiczna struktura

wielomagistralowa

Lokalna magistrala łącząca procesor i pamięć podręczną. Może ona wspomagać

jedno lub więcej urządzeń lokalnych. Sterownik pamięci podręcznej łączy tę

pamięć nie tylko do magistrali lokalnej, ale również do magistrali systemowej, do

której są dołączone wszystkie moduły pamięci głównej. Wykorzystanie struktury

pamięci podręcznej uwalnia procesor od potrzeby częstego dostępu do pamięci

głównej. Dzięki temu pamięć główna może być przesunięta z magistrali lokalnej

do systemowej. W ten sposób wejście-wyjście komunikuje się z pamięcią główną

przez magistralę systemową, nie kolidując z działalnością procesora.

Możliwe jest podłączenie sterowników

wejścia-wyjścia bezpośrednio do magistrali

systemowej.

Bardziej

efektywnym

rozwiązaniem jest jednak wykorzystanie

do tego celu jednej lub wielu

szyn

rozszerzenia

(ang.

expansion

buses).

Interfejs szyny rozszerzenia buforuje dane

przesyłane między magistralą systemową a

sterownikami wejścia-wyjścia dołączonymi

do szyny rozszerzenia.

8

Architektura Komputerów 2006

5

Międzypiętrowa struktura

wielomagistralowa

Magistrala

lokalna

łączy

procesor

ze

sterownikiem

pamięci podręcznej, który z

kolei

jest

podłączony

do

magistrali

systemowej

współpracującej z pamięcią

główną. Sterownik pamięci

podręcznej jest zintegrowany

z

mostem

(urządzeniem

buforującym)

łączącym

z

magistralą szybką. Wolniejsze

urządzenia

nadal

są

obsługiwane

przez

szynę

rozszerzenia

z

interfejsem

buforującym

ruch

między

szyną rozszerzenia a szybką

magistralą.

Zaletą tego rozwiązania jest to, że szybka magistrala ściślej sprzęga procesor z

urządzeniami wejścia-wyjścia o wysokich wymaganiach, a jednocześnie jest

niezależna od procesora. Dzięki temu mogą być tolerowane różnice szybkości

procesora i szybkiej magistrali, a także różne definicje linii sygnałowych.

9

Rodzaje magistrali

Linie magistralowe mogą być podzielone na dwa rodzaje: specjalistyczne

(ang.

dedicated) i multipleksowane.

Linia specjalistyczna jest trwale przypisana albo jednej funkcji, albo

fizycznie określonym zespołom komputera. Przykładem specjalizacji

funkcjonalnej jest zastosowanie oddzielnych, specjalistycznych linii

adresów i danych, co jest powszechne w wielu magistralach.

Adresy i dane mogą być transmitowane przez ten sam zespół linii przy

wykorzystaniu linii sterowania określającej ważność adresu

(ang. Adress

Valid). W tym przypadku każdy moduł mado dyspozycji określony

odcinek

czasu

na

skopiowanie

adresu

i

stwierdzenie,

czy jest modułem adresowanym. Adres jest następnie usuwany z

magistrali, a te same połączenia magistralowe są wykorzystywane do

przenoszenia danych odczytywanych lub zapisywanych. Ta właśnie

metoda używania tych samych linii do wielu celów jest znana jako

multipleksowanie czasowe (ang.

time multiplexing).

Specjalizacja fizyczna (ang.

physical dedicatiori) odnosi się do używania

wielu magistrali, z których każda łączy tylko określoną grupę modułów.

Typowym przykładem jest zastosowanie magistrali wejścia-wyjścia do

łączenia wszystkich modułów wejścia-wyjścia.

10

Architektura Komputerów 2006

6

Arbitraż dostępu do magistrali

We wszystkich systemach z wyjątkiem najprostszych więcej niż jeden

moduł może potrzebować przejęcia sterowania magistralą.

W określonym czasie tylko jeden moduł może transmitować przez

magistralę

Możliwe metody można z grubsza podzielić na:

Scentralizowane, w takim układzie istnieje jedno urządzenie,

zwane sterownikiem magistrali lub arbitrem, które jest

odpowiedzialne za przydział czasu na magistrali. Urządzenie to

może być oddzielnym modułem lub częścią procesora.

Rozproszone, w takim układzie centralny sterownik nie

występuje. Każdy moduł zawiera układy logiczne sterujące

dostępem, a moduły współdziałają korzystając z magistrali.

W obu metodach arbitrażu celem jest wyznaczenie jednego urządzenia

— albo procesora, albo modułu wejścia-wyjścia - jako nadrzędnego.

Urządzenie nadrzędne

(master) może następnie inicjować transfer

danych z innym urządzeniem, które w tym określonym przesyłaniu gra

rolę podrzędną

(ang. slave).

Koordynacja czasowa

(ang. timing) odnosi się do sposobu, w jaki

koordynowane są zdarzenia na magistrali.

11

Arbitraż synchroniczny

Przy koordynacji synchronicznej występowanie zdarzeń na magistrali jest

wyznaczone przez zegar. Magistrala zawiera linię zegarową, którą zegar

transmituje regularną sekwencję kolejno zmieniających się zer i jedynek o

takim samym czasie trwania. Pojedyncza transmisja 1-0 jest nazywana cyklem

zegara lub cyklem magistrali i określa przedział czasowy. Wszystkie inne

urządzenia dołączone do magistrali mogą odczytywać stan linii zegarowej, a

wszystkie zdarzenia rozpoczynają się równocześnie z cyklem zegara.

12

Architektura Komputerów 2006

7

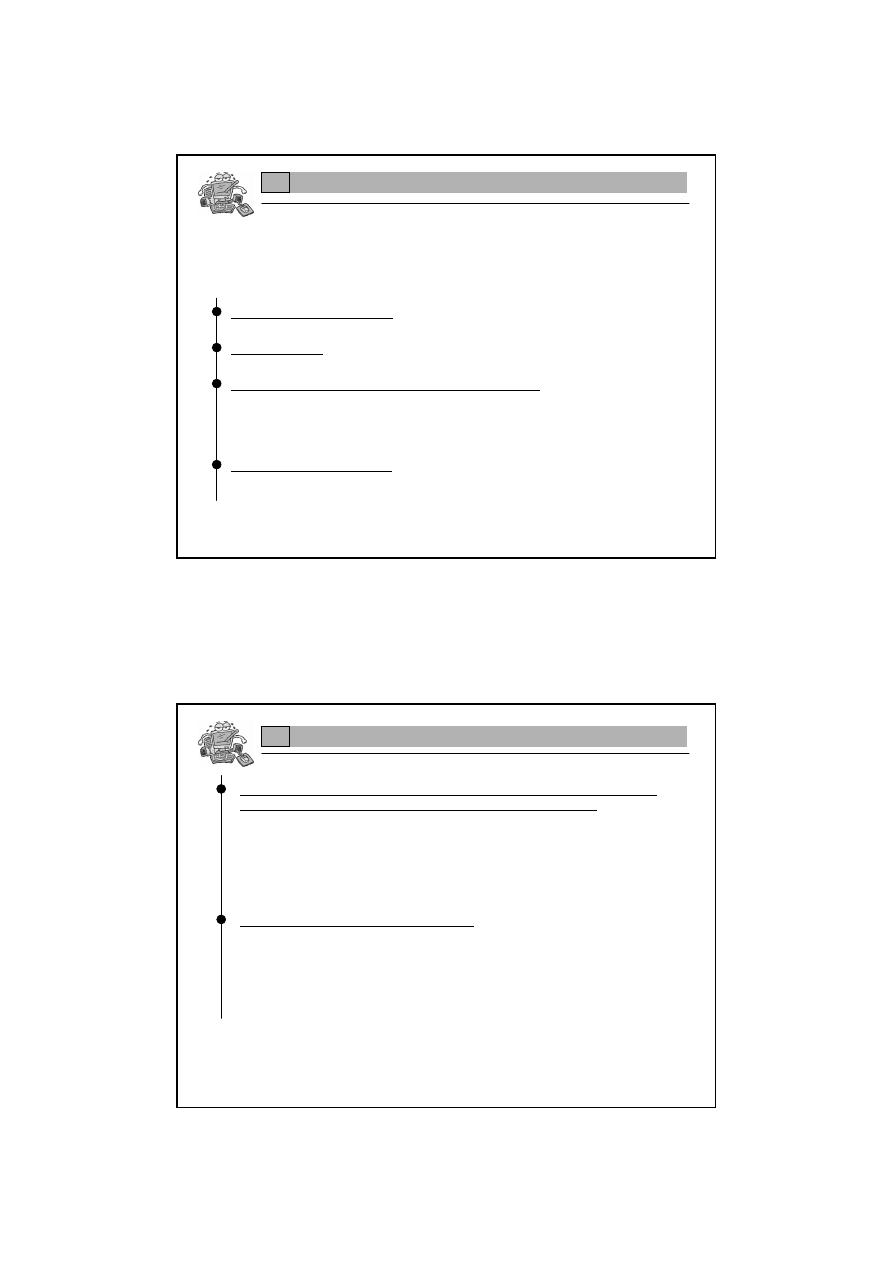

Arbitraż asynchroniczny

Przy koordynacji asynchronicznej występowanie zdarzeń na magistrali jest

zależne od zdarzenia poprzedzającego. W prostym przykładzie pokazanym na

rysunku procesor umieszcza sygnały adresu i odczytu na magistrali. Po pewnym

czasie wymaganym do ustabilizowania sygnałów, wysyła sygnał synchronizacji

nadrzędnej

(master sync - MSYN), wskazując na obecność ważnych sygnałów

adresu i sterowania. Moduł pamięci reaguje, wysyłając dane oraz sygnał

synchronizacji podrzędnej

(slave sync - SSYN), wskazujący na odpowiedź.

13

Magistrale PC - ISA

ISA (ang. Industrial Standard Architecture)

16-bitowa magistrala ISA

Pierwsze użycie - PC-XT

Złącze 62 pinowe

Częstotliwość zegara 4.77 MHz

20 linii adresowych (1 MB pamięci)

8 linii danych

6 linii przerwań

2 kanały DMA

8-bitowa magistrala ISA

Pierwsze użycie - PC-AT oraz Intel 80286

Złącze rozszerzone o dodatkowe 36 pin-y

Częstotliwość zegara 8.33 MHz

24 linie adresowe (16 MB pamięci)

16 linii danych

11 linii przerwań

6 kanałów DMA

14

Architektura Komputerów 2006

8

Magistrale PC – EISA, VLB

EISA (ang. Extended-ISA)

pierwsze użycie w roku 1988

Częstotliwość zegara 8.33 MHz

24/32 linii adresowych

16/32 linii danych

kompatybilna z ISA

VESA Video Local Bus

pierwsze użycie w roku 1989

Szybkość zależna od procesora

24/32 linii adresowych

32/64 linii danych

współpracowała z ISA lub EISA

15

Magistrale PC – PCI

PCI (ang. Peripheral Component Interface)

pierwsze użycie w roku 1990, specyfikacja PCI 2.0 w roku 1993

częstotliwość zegara 33 MHz (niezależna od procesora)

64 linie adresowe i danych (multipleksowane) – przy 33 MHz daje to

przepustowości 264 MB/s lub 2,112 Gbit/s

magistrala synchroniczna z centralnym układem arbitrażu

Architektura typu Desktop

Architektura typu Serwer

16

Architektura Komputerów 2006

9

Magistrala PCI – struktura – cz. I

Magistrala PCI może być konfigurowana jako magistrala 32- lub 64-bitowa.

Specyfikacja definiuje 50 linii sygnałowych. Można je podzielić na następujące

grupy funkcjonalne:

Wyprowadzenia systemowe. Należą do nich wyprowadzenia

zegara i

przywracania

(resef).

Wyprowadzenia adresu i danych. Należą do nich 32 linie multipleksowane

adresów i danych. Pozostałe linie w tej grupie są wykorzystywane do

interpretowania i określania ważności linii sygnałowych przenoszących

adresy i dane.

Wyprowadzenia sterowania interfejsu. Służą do koordynowania transakcji i

współdziałania między jednostkami inicjującymi a docelowymi.

Wyprowadzenia arbitrażowe. W przeciwieństwie do pozostałych linii

sygnałowych magistrali PCI nie są one liniami wspólnymi. Każda jednostka

nadrzędna PCI ma własną parę linii arbitrażowych, które łączą ją

bezpośrednio z arbitrem magistrali PCI.

Wyprowadzenia informujące o błędach. Wykorzystywane do informowania o

błędach parzystości i innych.

17

Magistrala PCI – struktura – cz. II

Ponadto specyfikacja PCI określa 50 opcjonalnych linii sygnałowych,

podzielonych na następujące grupy:

Wyprowadzenia przerwania. Są one przewidziane dla urządzeń PCI, które

muszą generować zapotrzebowanie na obsługę. Tak jak w przypadku

wy-prowadzeń arbitrażowych nie są one wspólne. Każde urządzenie PCI

dysponuje własną linią lub liniami przerwań łączącymi ze sterownikiem

przerwań.

Wyprowadzenia obsługi pamięci podręcznej. Są one wykorzystywane do

obsługi pamięci podręcznych zawartych w procesorach i innych

urządzeniach PCI. Umożliwiają

stosowanie protokołu podglądania

(snoopy) pamięci podręcznej.

Wyprowadzenia rozszerzenia magistrali 64-bitowej. Należą do nich 32

linie multipleksowane adresów i danych. W połączeniu z obowiązującymi

liniami adresów i danych tworzą 64-bitową magistralę adresów i danych.

Inne linie z tej grupy są używane do interpretowania i określania

ważności linii sygnałowych przenoszących dane i adresy. Występują tu

też dwie linie umożliwiające dwóm urządzeniom PCI uzgodnienie użycia

szerokości 64-bitowej.

Wyprowadzenia testowania granic JTAG. Linie te umożliwiają realizację

procedur testowania określonych w normie IEEE 149.1.

18

Architektura Komputerów 2006

10

Magistrala PCI – rozkazy – cz. I

Działanie magistrali odbywa się w formie transakcji między inicjatorem

(modułem nadrzędnym) a celem (modułem podrzędnym). Gdy inicjator

domaga się sterowania magistralą, określa typ transakcji, która ma być

przeprowadzona. Podczas fazy adresu transakcji do sygnalizowania typu

transakcji są używane linie C/BE. Rozkazy są następujące:

potwierdzenie przerwania - jest rozkazem odczytu przeznaczonym dla

urządzenia, które działa jako sterownik przerwań na magistrali PCI.

cykl specjalny - jest rozkazem używanym przez inicjatora w celu

rozgłoszenia wiadomości przeznaczonych dla jednego lub więcej celów.

odczyt wejścia-wyjścia,

zapis wejścia-wyjścia

-

są używane do

przenoszenia danych między inicjatorem a sterownikiem wejścia-wyjścia.

Każde urządzenie wejścia-wyjścia ma własną przestrzeń adresową. Linie

adresowe służą do wskazywania określonego urządzenia oraz do

sprecyzowania danych, które mają być wymienione z tym urządzeniem.

cykl podwójnego adresu - jest wykorzystywany przez inicjatora do

wskazania, że stosuje on adresowanie 64-bitowe.

19

Magistrala PCI – rozkazy – cz. II

odczyt pamięci, linia odczytu pamięci, zwielokrotniony odczyt

pamięci, zapis w pamięci, zapis w pamięci i unieważnienie - rozkazy

odczytu i zapisu w pamięci są stosowane do precyzowania

przesyłania porcji danych

(burst of data) trwającego przez jeden lub

więcej cykli zegarowych. Interpretacja tych rozkazów zależy od

tego, czy sterownik pamięci na magistrali PCI realizuje protokół PCI

przeznaczony do przesyłania danych między pamięcią główną a

pamięcią podręczną.

odczyt konfiguracji, zapis konfiguracji - dwa rozkazy konfiguracyjne

umożliwiają inicjatorowi odczytanie i zaktualizowanie parametrów

konfiguracji w urządzeniu dołączonym do magistrali PCI. Każde

urządzenie PCI może zawierać do 256 rejestrów wewnętrznych,

które są wykorzystywane do konfigurowania tego urządzenia

podczas inicjowania systemu.

20

Architektura Komputerów 2006

11

Magistrala PCI – przesył danych

Każde przesyłanie danych magistralą PCI jest pojedynczą transakcją

składającą się z jednej fazy adresowej oraz jednej lub wielu faz danych.

Wszystkie zdarzenia są

synchronizowane

przez

opadające

części

impulsów

zegarowych,

które

występują

w

środku

każdego

cyklu

zegara.

Urządzenia

magistrali badają

linie

magistrali

w

czasie

narastania

impulsów

zegarowych, na początku

cyklu magistrali.

21

Magistrala PCI – arbitraż – cz. I

Magistrala PCI wykorzystuje scentralizowany, synchroniczny rodzaj

arbitrażu, w którym każdy moduł nadrzędny ma przypisane unikatowe

sygnały zapotrzebowania (REQ) i udostępniania

(grant - GNT).

Odpowiednie linie sygnałowe są podłączone do centralnego arbitra, a

dostęp

do

magistrali

jest

uzyskiwany

przez

zgodne

zgłoszenie

zapotrzebowania i udostępniania.

Specyfikacja PCI nie dyktuje szczególnego algorytmu arbitrażu.

Możliwe rozwiązania można podzielić na następujące grupy:

„pierwszy zgłoszony - pierwszy obsłużony"

rozwiązanie cykliczne

(round-robin)

rozwiązania bazujące na priorytetach

22

Architektura Komputerów 2006

12

Magistrala PCI – arbitraż – cz. II

23

Wyszukiwarka

Podobne podstrony:

12 Diagramy struktur połączonych

Mikrobiologia, - na dł, LPS = endotoksyna: lipopolisacharydy inaczej heteropolimery złożone z trzech

TOMAS ČELKIS (Wilno) STAN DRÓG LĄDOWYCH I STRUKTURA SYSTEMU POŁĄCZEŃ W WIELKIM KSIĘSTWIE LITEWSKIM W

STRUKTURA TRENINGU

30 Struktury zaleznosci miedzy wskaznikami zrow rozw K Chmura

rodzaje struktur rynkowych 2

Struktura regionalna

struktura organizacyjna BTS [ www potrzebujegotowki pl ]

Polaczenia nitowe

Struktura treningu sportowego (makrocykl) szkoła PZPN

Struktura podmiotowa i przedmiotowa gospodarki

STRUKTURA I FUNKCJONOWANIE GN

Strukturalizm i stylistyka (część II)

Struktura ludności w Polsce

Połączenia gwintowe js

więcej podobnych podstron